### Design of a Power-Efficient Carbon Nanotube Field Effect Transistor (CNFET)-Based Ternary Logic Processor

### THESIS

Submitted in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY**

by

Sharvani Gadgil ID No. 2018PHXF0434H

Under the Supervision of

Dr. Chetan Kumar V

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

#### CERTIFICATE

This is to certify that the thesis titled <u>Design of a Power-Efficient Carbon Nanotube</u> <u>Field Effect Transistor (CNFET)-based Ternary Logic Processor</u>, submitted by <u>Shar-</u> <u>vani Gadgil</u> ID No <u>2018PHXF0434H</u> for award of PhD of the Institute embodies original work done by her under my supervision.

( Chetan

Signature of the Supervisor Name: Dr. Chetan Kumar V Designation: Assistant Professor Date: 27.12.2023

### DECLARATION

I, Sharvani Gadgil, declare that this written submission represents my ideas in my own words, and where others' ideas or words have been included; I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated, or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action as per the rules and regulations of the Institute.

Sharvani Gadgil

## Acknowledgments

The culmination of this thesis is attributed to a diverse group of people who have guided and supported me throughout and together with me have persisted on a challenging journey. At the onset, I would like to sincerely thank my supervisor Dr. Chetan Kumar V for being a true source of inspiration and a guiding light for this research. I would also like to thank my DAC members Dr. Syed Ershad Ahmed and Dr. Soumya J for their time and constructive feedback that helped me at every important milestone.

I express my deep sense of gratitude to BITS-Pilani, Hyderabad campus for the state of the art infrastructure which made sure the research gets all the necessary support required. In the same vein, I would like to thank the Department of EEE for their participation as a cohesive unit at various junctures. I am thankful to Goli Naga Sandesh for the help I received in the technicalities of my work.

Last but not the least, I cannot appreciate enough my daughter Sharanya who despite being a toddler understood that I am occupied with something important and supported me at the same level as my husband Rohit and my two mothers (mother-Anjali and mother-in-law-Neeta). Finally, I dedicate this work to my father Dr. S. B. Gadgil who has inspired me everyday and has been providing me the moral support throughout my PhD journey.

#### Hyderabad

#### Sharvani Gadgil

### Abstract

The interest in Multi-Valued Logic (MVL) circuits has grown over the years in view of the benefits they provide in terms of reducing the complexity of interconnects and increasing information density. Ternary logic is a subset of MVL that uses three logic levels for computation. Implementation of Ternary logic circuits necessitates transistors with different threshold voltages. This is acheived in the traditional Metal-Oxide-Semiconductor (MOS) transistors using body biasing making the design of ternary logic circuits using MOS transistors more complex. Carbon-Nanotube-Field-Effect-Transistor (CNFET) is a good alternative for ternary logic implementation where, transistors with different threshold voltages can be obtained by varying the physical dimensions of the Carbon-Nano-Tube (CNT), which acts as a conduction channel in the CNFETs.

The existing work on CNFET-based ternary logic circuit implementation focuses only on individual blocks like adders, multipliers, ALUs, memory etc but not the entire system. Hence, the primary goal of this thesis is to design a CNFET-based Ternary Logic Processor (TLP). The processor implementation requires the design of different ternary combinational and sequential logic circuits as well as ternary memory.

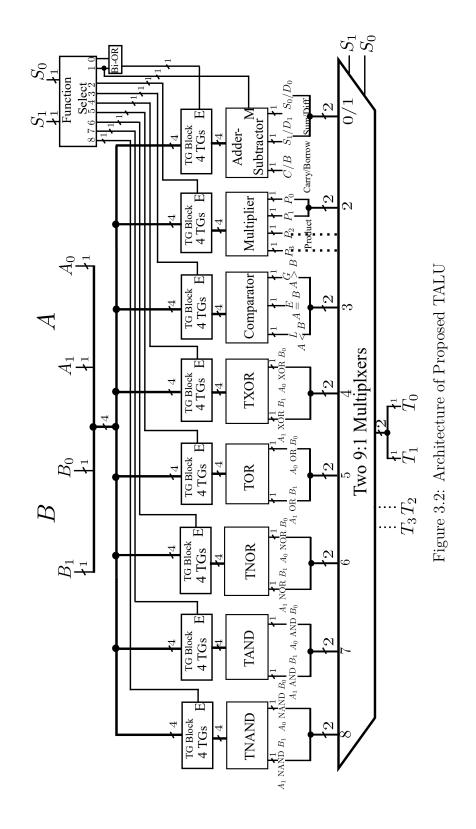

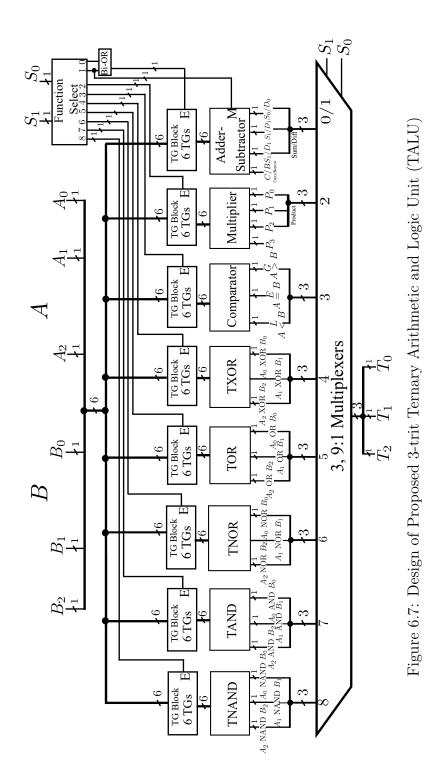

In this work, firstly, we present a new CNFET-based ternary Arithmetic-Logic-Unit (ALU) architecture. The main components of the ternary ALU are the function select block that the selects the required function the ALU should perform, the transmission gate block that connects the inputs of the ALU to its functional blocks, and the functional modules. The functional modules, which implement the arithmetic and logic functions, like the ternary adder-subtractor, multiplier and the comparator of the ternary ALU are designed using 2 : 1 multiplexers to achieve low power consumption.

The second contribution of this thesis, is novel design methodologies for implementing CNFET-based ternary sequential logic circuits, which form an integral part of a processor. In this work, different designs for D-flipflop are presented. The first flipflop design is implemented using the ternary buffer and Standard Ternary Inverter (STI). The second design is a multiplexer-based design implemented using successor-predecessor circuits. The third and fourth D-flipflop designs are hybrid designs which are a combination of buffer-based and successor-predecessor-based designs. These flipflops are further used to implement ternary synchronous and asynchronous counters.

The third contribution is the implementation of ternary SRAM cells. Three, dual supply-based ternary Static-Random-Access-Memory (SRAM) cell designs are implemented using CNFETs. Two of the proposed ternary SRAM designs are cycle-operator based and the third design is buffer-based.

The proposed designs of ALU, sequential circuits and SRAM are simulated using HSPICE and show considerable improvement in performance when they compared to their counterparts existing in literature.

Finally, a CNFET-based Ternary Logic Processor (TLP) is designed by integrating all the above designs of the ternary ALU, the ternary sequential logic circuits, and the ternary memory. To start with, an Instruction Set Architecture (ISA) is defined for this TLP that consists of instructions of the Register type, Load-store type, Immediate type, and Branch type. Based on the ISA, the architecture of the CNFET-based TLP is proposed and the transistor level designs of the TLPs' fundamental blocks like the Ternary Instruction Fetch (TIF), Ternary Register File (TRF), Ternary Arithmetic and Logic Unit (TALU) and Ternary Data Memory (TDM) are presented. Simulations are performed for the TLP and the TLPs' individual blocks and the performance parameters like the power consumption, propagation delay, and the number of CNFETs required are calculated. In addition to this, the functionality of the processor is verified using a few of the standard programs.

## Contents

| A             | Acknowledgements ii |        |                                                        |    |  |

|---------------|---------------------|--------|--------------------------------------------------------|----|--|

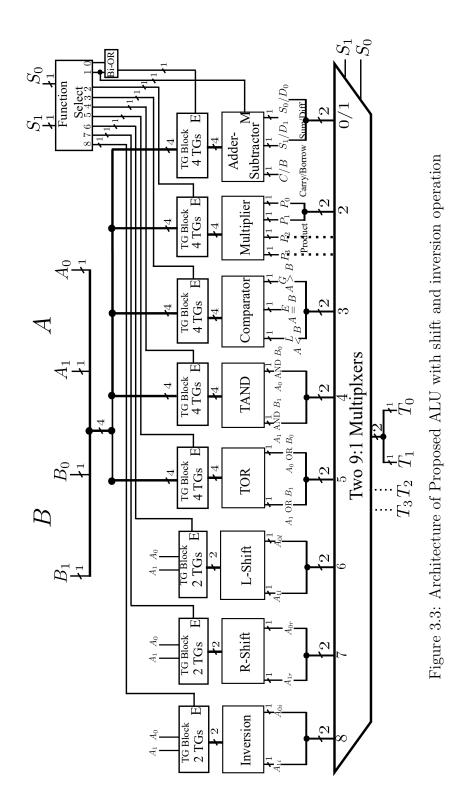

| A             | Abstract            |        |                                                        |    |  |

| C             | onter               | nts    |                                                        | vi |  |

| Li            | st of               | Table  | 5                                                      | ix |  |

| Li            | st of               | Figur  | es                                                     | xi |  |

| $\mathbf{Li}$ | st of               | Abbre  | eviations                                              | xv |  |

| 1             | Intr                | oducti | ion                                                    | 1  |  |

|               | 1.1                 | Overv  | iew & Motivation                                       | 1  |  |

|               | 1.2                 | Backg  | round                                                  | 3  |  |

|               |                     | 1.2.1  | Ternary Logic                                          | 3  |  |

|               |                     | 1.2.2  | Carbon-Nanotube Field Effect Transistor (CNFET)        | 6  |  |

|               | 1.3                 | Thesis | Outline                                                | 9  |  |

| <b>2</b>      | Rel                 | ated w | rork                                                   | 11 |  |

|               | 2.1                 | Litera | ature Review                                           | 11 |  |

|               |                     | 2.1.1  | Design of Basic Ternary Combinational Logic circuits   | 12 |  |

|               |                     | 2.1.2  | Design of Complex Ternary Combinational Logic circuits | 17 |  |

|               |                     | 2.1.3  | Design of Ternary Sequential Logic circuits            | 20 |  |

|               |                     | 2.1.4  | Design of Ternary Memories                             | 22 |  |

|               |                     | 2.1.5  | Design of a Ternary Processor                          | 24 |  |

|   | 2.2 | Resear  | rch Gaps   | and Objectives of the thesis                               | 25 |

|---|-----|---------|------------|------------------------------------------------------------|----|

| 3 | Des | ign of  | CNFET      | -Based Ternary Arithmetic and Logic Unit                   | 26 |

|   | 3.1 | Introd  | uction     |                                                            | 26 |

|   | 3.2 | Existin | ng Design  | s for TALU                                                 | 27 |

|   | 3.3 | Propo   | sed Design | n of TALU                                                  | 29 |

|   |     | 3.3.1   | Proposed   | d TALU Architecture                                        | 29 |

|   |     | 3.3.2   | Proposed   | d TALU Design and Implementation                           | 31 |

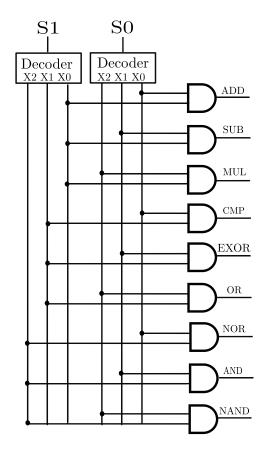

|   |     |         | 3.3.2.1    | Adder-Subtractor Module                                    | 35 |

|   |     |         | 3.3.2.2    | Multiplier Module                                          | 42 |

|   |     |         | 3.3.2.3    | Comparator Module                                          | 43 |

|   |     |         | 3.3.2.4    | Output Multiplexer module                                  | 44 |

|   | 3.4 | Simula  | ation Resu | ılts                                                       | 46 |

|   |     | 3.4.1   | Simulati   | on Environment                                             | 46 |

|   |     | 3.4.2   | Results a  | and Discussion                                             | 46 |

|   | 3.5 | Conclu  | usions     |                                                            | 54 |

| 4 | Des | ign of  | CNFET      | -Based Ternary Sequential Logic circuits                   | 55 |

|   | 4.1 | Introd  | uction     |                                                            | 55 |

|   | 4.2 | Previo  | ous Work   | on CNFET-based Ternary Sequential Logic circuits           | 56 |

|   |     | 4.2.1   | Existing   | Ternary D-flipflop designs                                 | 56 |

|   |     | 4.2.2   | Existing   | Ternary counter designs                                    | 60 |

|   | 4.3 | Propo   | sed design | ns for Ternary sequential logic circuits                   | 60 |

|   |     | 4.3.1   | Proposed   | d designs for Ternary D-flipflop circuits                  | 61 |

|   |     |         | 4.3.1.1    | Proposed designs for STI-based Ternary D-flipflop circuits | 61 |

|   |     |         | 4.3.1.2    | Proposed designs for Successor-predecessor-based Ternary   |    |

|   |     |         |            | D-flipflop circuits                                        | 63 |

|   |     |         | 4.3.1.3    | Proposed designs for Hybrid Ternary D-flipflop circuits    | 63 |

|   |     | 4.3.2   | Proposed   | d designs of Ternary counter circuits using the proposed   |    |

|   |     |         | D-flipflo  | p circuits                                                 | 65 |

|          | 4.4                  | Simula | ation Results                                                | 67  |

|----------|----------------------|--------|--------------------------------------------------------------|-----|

|          |                      | 4.4.1  | Simulation Environment                                       | 68  |

|          |                      | 4.4.2  | Results and Discussion                                       | 68  |

|          |                      |        | 4.4.2.1 STI Gate                                             | 68  |

|          |                      |        | 4.4.2.2 Ternary D-flipflop                                   | 70  |

|          |                      |        | 4.4.2.3 Ternary Counter                                      | 73  |

|          | 4.5                  | Conclu | usions                                                       | 79  |

| <b>5</b> | $\operatorname{Des}$ | ign of | CNFET-based Ternary Memory                                   | 80  |

|          | 5.1                  | Introd | uction                                                       | 80  |

|          | 5.2                  | Review | w of Ternary Memory                                          | 81  |

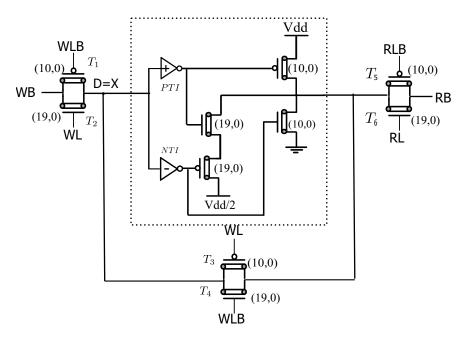

|          | 5.3                  | Propo  | sed CNFET-based Ternary SRAM                                 | 83  |

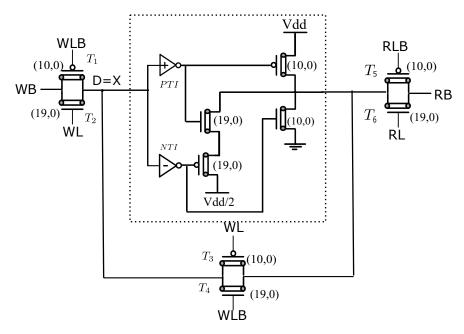

|          |                      | 5.3.1  | Proposed designs for cycle operator-based Ternary SRAM $\ .$ | 83  |

|          |                      | 5.3.2  | Proposed design for buffer-based Ternary SRAM                | 86  |

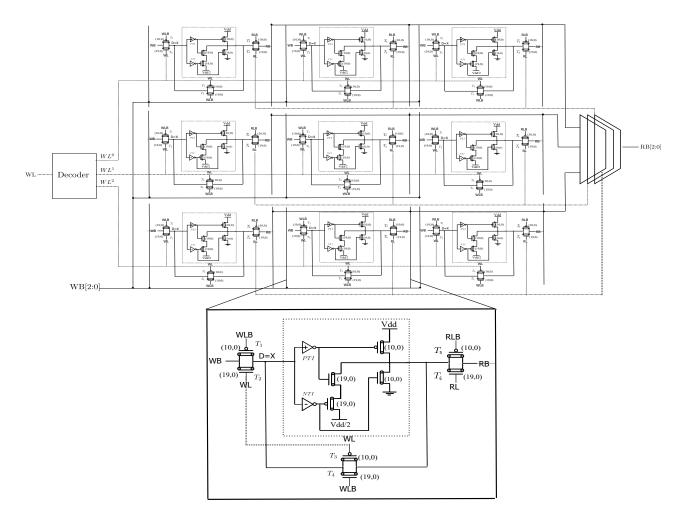

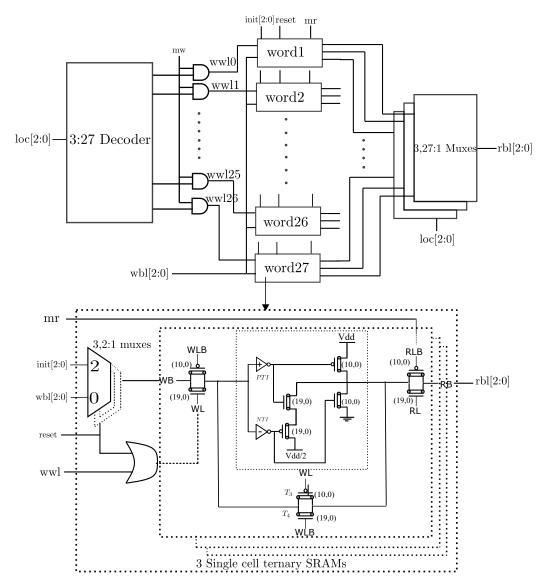

|          |                      | 5.3.3  | Proposed design for a nXn Ternary SRAM                       | 86  |

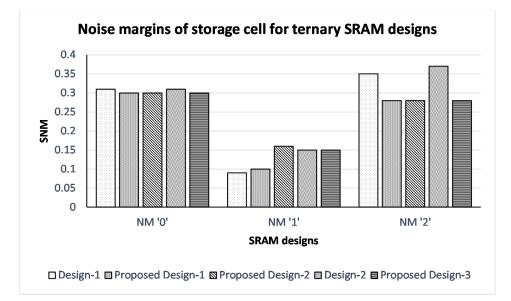

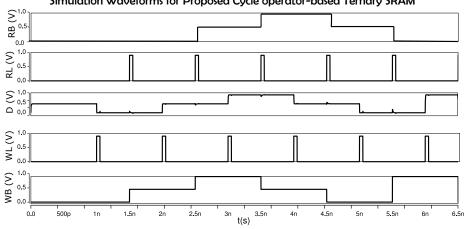

|          | 5.4                  | Simula | ation Results and Discussion                                 | 87  |

|          | 5.5                  | Conclu | usions                                                       | 94  |

| 6        | $\operatorname{Des}$ | ign of | <b>CNFET-based Ternary Logic Processor</b>                   | 95  |

|          | 6.1                  | Introd | uction                                                       | 95  |

|          | 6.2                  | Relate | ed Work                                                      | 96  |

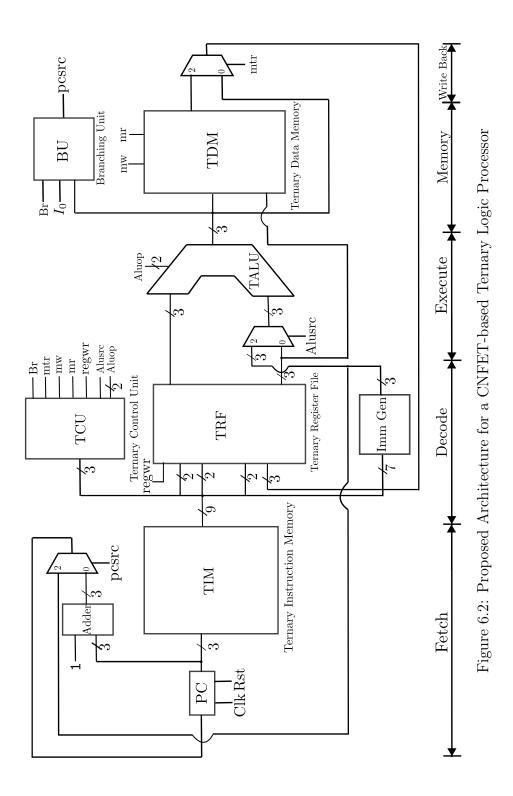

|          | 6.3                  | Propo  | sed Design of a Ternary Logic Processor                      | 97  |

|          |                      | 6.3.1  | Proposed Instruction Set Architecture                        | 98  |

|          |                      | 6.3.2  | Proposed Micro-Architecture                                  | 100 |

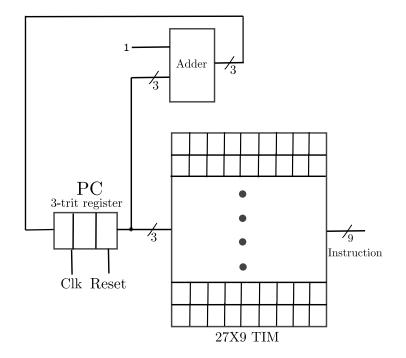

|          |                      | 6.3.3  | Proposed Design of Ternary Instruction Fetch Unit            | 103 |

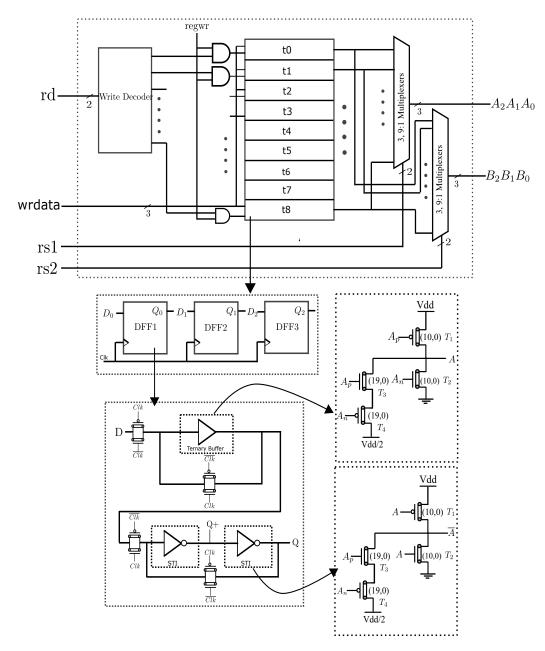

|          |                      | 6.3.4  | Proposed Design of Ternary Register File                     | 104 |

|          |                      | 6.3.5  | Proposed Design of a Ternary Arithmetic Logic Unit           | 106 |

|          |                      | 6.3.6  | Proposed Design of Ternary Data Memory                       | 107 |

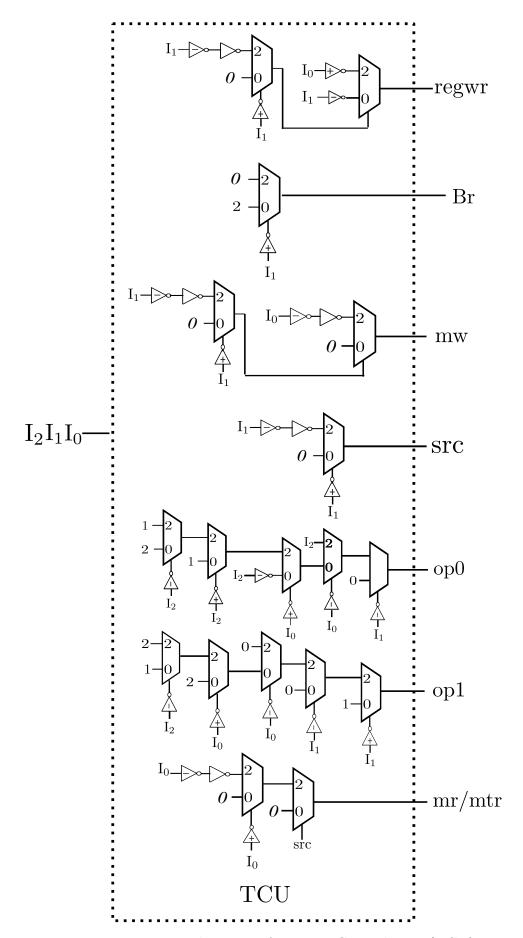

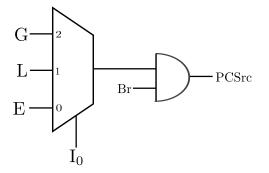

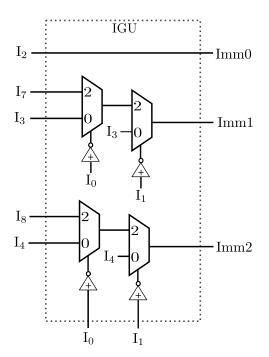

|          |                      | 6.3.7  | Proposed Design of Ternary Control Unit, Branching unit and  |     |

|          |                      |        | Immediate Generation Unit                                    | 110 |

|                  | 6.4                                 | Simulation Results |                                           |     |  |

|------------------|-------------------------------------|--------------------|-------------------------------------------|-----|--|

|                  |                                     | 6.4.1              | Simulation Environment                    | 114 |  |

|                  |                                     | 6.4.2              | Results and Discussion                    | 114 |  |

|                  |                                     |                    | 6.4.2.1 Ternary Instruction Fetch Unit    | 114 |  |

|                  |                                     |                    | 6.4.2.2 Ternary Register File             | 116 |  |

|                  |                                     |                    | 6.4.2.3 Ternary Data Memory               | 117 |  |

|                  |                                     |                    | 6.4.2.4 Ternary Arithmetic and Logic Unit | 117 |  |

|                  |                                     |                    | 6.4.2.5 Ternary Logic Processor           | 118 |  |

|                  | 6.5                                 | Conclu             | sions                                     | 122 |  |

| 7                | Con                                 | clusio             | n and Future Scope                        | 124 |  |

|                  | 7.1                                 | Conclu             | nsion                                     | 124 |  |

|                  | 7.2                                 | Future             | e Scope                                   | 125 |  |

| Bibliography 127 |                                     |                    |                                           | 127 |  |

| Re               | Related Journal Publications 137    |                    |                                           |     |  |

| Re               | Related Conference Publications 138 |                    |                                           | 138 |  |

| Bi               | ogra                                | phies              |                                           | 139 |  |

## List of Tables

| 1.1 | Ternary Inverters [5]                                                     | 4  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Logic Symbols                                                             | 5  |

| 1.3 | Truth Table for TOR and TAND                                              | 5  |

| 1.4 | Relation Between Chirality, CNT Diameter and Threshold Voltage [21]       | 8  |

| 1.5 | Technology Parameters for CNFET model in $[21, 22, 26]$                   | 9  |

| 3.1 | Truth Table for proposed TALU                                             | 31 |

| 3.2 | Unary Operators for Multiplexer based Design                              | 34 |

| 3.3 | Half Adder-Subtractor Truth Table                                         | 36 |

| 3.4 | Full Adder-Subtractor Truth Table                                         | 40 |

| 3.5 | Simulation results based Comparision of HAS                               | 47 |

| 3.6 | Simulation results based Comparision of FAS                               | 47 |

| 3.7 | Simulation results based Comparision of 1-trit Multiplier                 | 52 |

| 3.8 | Simulation results based Comparision of 2-trit Multiplier                 | 53 |

| 3.9 | Comparisions of TALU designs                                              | 53 |

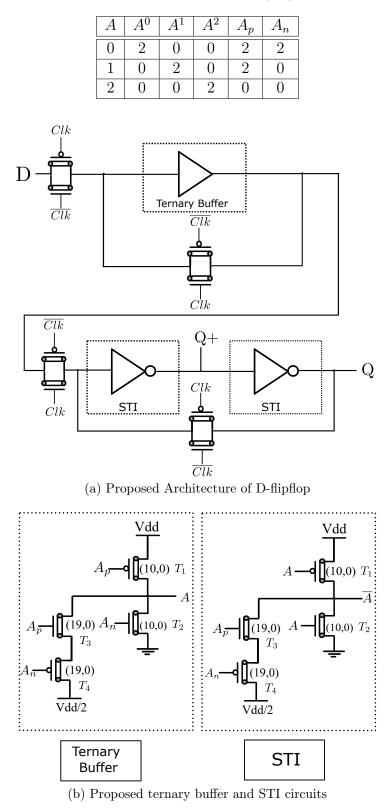

| 4.1 | Truth table for Unary operators                                           | 62 |

| 4.2 | Truth Table for next state generation logic                               | 67 |

| 4.3 | Simulation results comparision of existing and proposed STI gates $\ .$ . | 69 |

| 4.4 | Naming convention of various existing and proposed ternary D-flipflop     |    |

|     | designs                                                                   | 70 |

| 4.5 | Simulation results comparision of various existing and proposed ternary   |    |

|     | D-flipflop designs                                                        | 71 |

| 4.6 | Simulation results of proposed ternary D-flipflops with Vdd/2 genera-       |     |

|-----|-----------------------------------------------------------------------------|-----|

|     | tion path                                                                   | 72  |

| 4.7 | Simulation results comparision of various existing and proposed 3-trit      |     |

|     | ternary synchronous counter designs                                         | 78  |

| 4.8 | Simulation results comparision of various existing and proposed 3-trit      |     |

|     | ternary asynchronous counter design                                         | 78  |

| 5.1 | Truth Table for $A^1, A^2$ , $A_p$ and $A_n$                                | 81  |

| 5.2 | Read and Write power<br>(in uW) of various ternary SRAM designs $\ . \ .$ . | 88  |

| 5.3 | Leakage power<br>(in uW) of various ternary SRAM cells while storing $0$ ,  |     |

|     | 1 and 2                                                                     | 89  |

| 5.4 | Read Delay(in ps) of various ternary SRAM cells                             | 89  |

| 5.5 | Write Delay(in ps) of various ternary SRAM cells                            | 89  |

| 5.6 | CNFET count for ternary SRAM designs                                        | 94  |

| 6.1 | The proposed instructions for the Ternary Logic Processor $\ldots \ldots$   | 98  |

| 6.2 | Truth Table for control signals generation in TCU                           | 111 |

| 6.3 | Performance parameters for various blocks of TLP                            | 115 |

| 6.4 | Comparision of Simulation results for existing and proposed TRF and         |     |

|     | TDM                                                                         | 116 |

| 6.5 | Programs run on the Proposed TLP                                            | 119 |

| 6.6 | Simulation Results for Power consumed by the TLP to run benchmark           |     |

|     | programs                                                                    | 121 |

| 6.7 | CNFET count for the design of ternary processor $\hdots$                    | 122 |

| 6.8 | Comparison of Ternary vs Binary processor designs                           | 122 |

# List of Figures

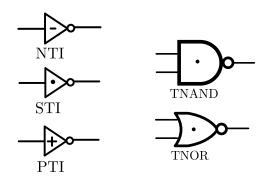

| 1.1  | Ternary inverters and basic logic gates                                             | 5  |

|------|-------------------------------------------------------------------------------------|----|

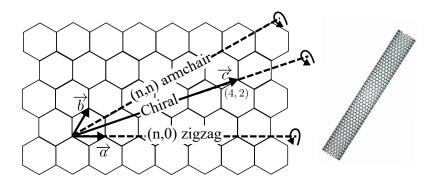

| 1.2  | Unrolled sheet of graphite and the rolled lattice structure of CNT $$               | 7  |

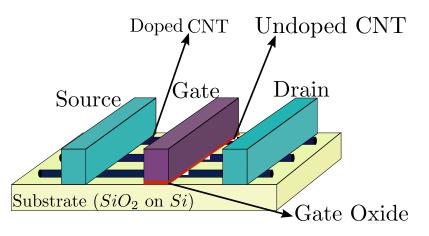

| 1.3  | Carbon-Nanotube Field Effect Transistor (CNFET) 3-D view                            | 7  |

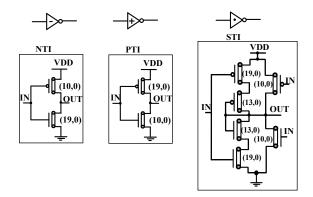

| 2.1  | Design of ternary Inverters using CNFETs                                            | 12 |

| 2.2  | Design of ternary NOR and NAND gates                                                | 12 |

| 2.3  | Approach I: Decoder-Encoder based HA [5]                                            | 13 |

| 2.4  | Ternary decoder used in Approach-1                                                  | 13 |

| 2.5  | Approach II: 3:1 Multiplexer based HA [28]                                          | 14 |

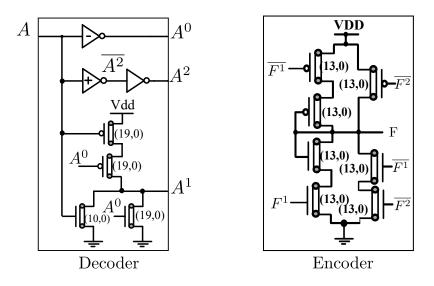

| 2.8  | Proposed decoder and encoder designs in Approach-III and Approach-IV                | 15 |

| 2.6  | Approach III: Decoderless HA [29]                                                   | 15 |

| 2.7  | Approach IV: Lowdelay decoder based HA [30]                                         | 15 |

| 2.9  | Approach V: 2:1 Multiplexer based HA [31]                                           | 16 |

| 2.10 | Approach VI: Dual supply based HA [32]                                              | 16 |

| 2.11 | Architecture of a ternary ALU first proposed [47]                                   | 19 |

| 2.12 | Design of a ternary D-flipflop using successor-predecessor circuits [57]            | 21 |

| 2.13 | CNFET-based single-cell Ternary SRAM a) basic block diagram b)                      |    |

|      | transistor-level diagram [17] $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 23 |

| 3.1  | Design and Architecture of TALU in [48]                                             | 28 |

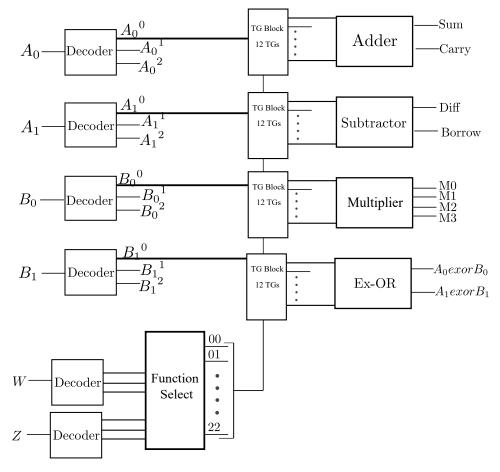

| 3.2  | Architecture of Proposed TALU                                                       | 30 |

| 3.3  | Architecture of Proposed ALU with shift and inversion operation                     | 32 |

| 3.4  | Design of Function select logic block [48]                                          | 33 |

| 3.5  | Adder-Subtractor block diagram                                                      | 35 |

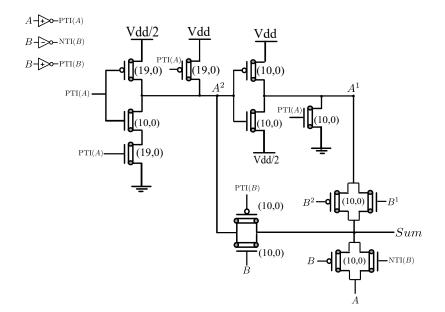

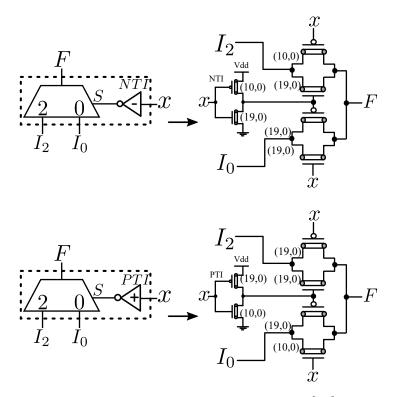

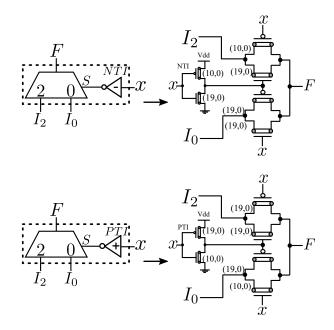

| 3.6  | NTI Mux and PTI Mux [69]                                                       | 36 |

|------|--------------------------------------------------------------------------------|----|

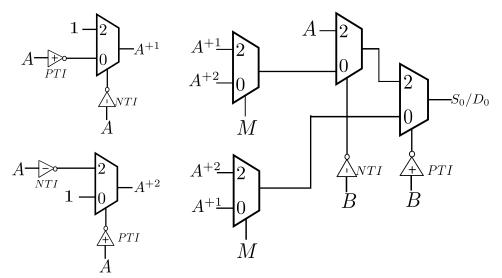

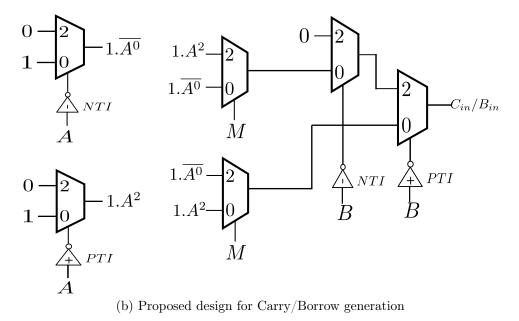

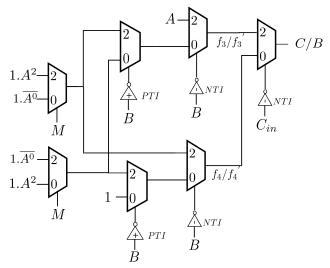

| 3.7  | Proposed design of Half Adder-Subtractor                                       | 37 |

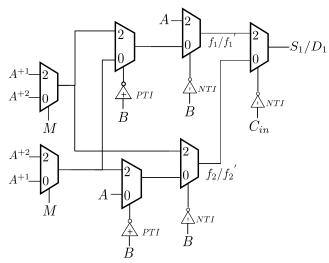

| 3.8  | Proposed design of Full Adder-subtractor                                       | 39 |

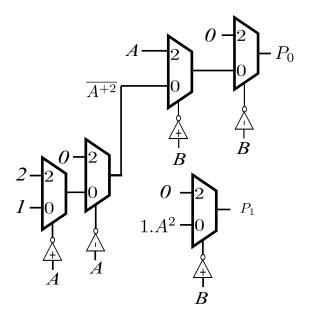

| 3.9  | Product-Multiplexer based realization                                          | 42 |

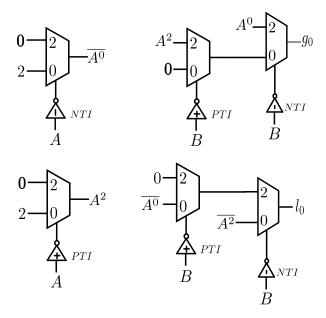

| 3.10 | Design for 2-digit Comparator                                                  | 44 |

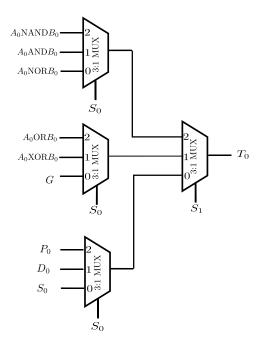

| 3.11 | Proposed Output Multiplexer design for TALU                                    | 45 |

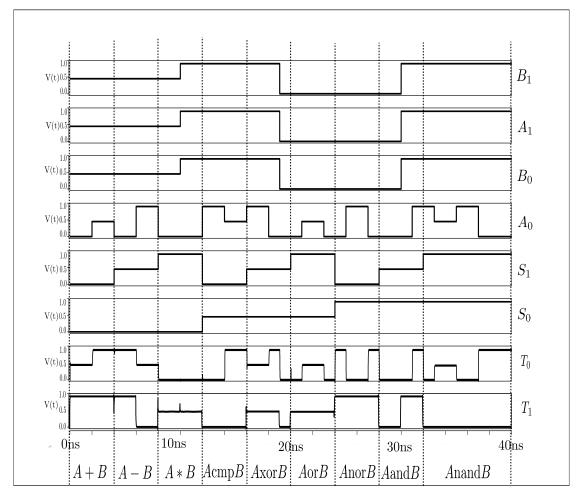

| 3.12 | Simulation waveforms for Proposed TALU design                                  | 48 |

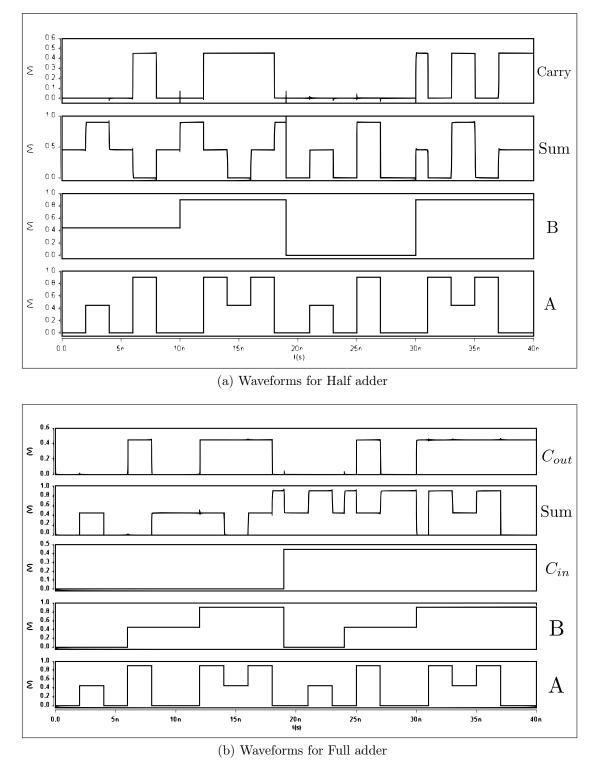

| 3.13 | Waveforms for Half Adder and Full Adder of proposed TALU                       | 49 |

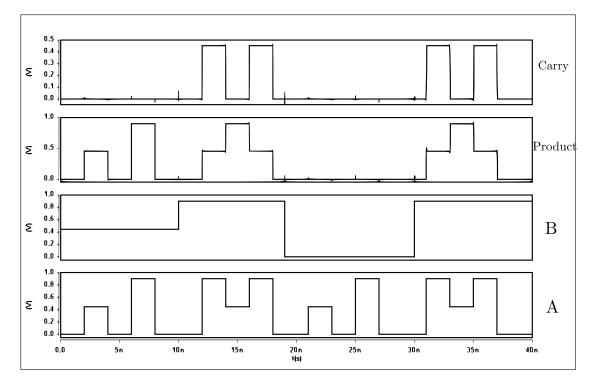

| 3.14 | Waveforms for 1-trit Multiplier                                                | 50 |

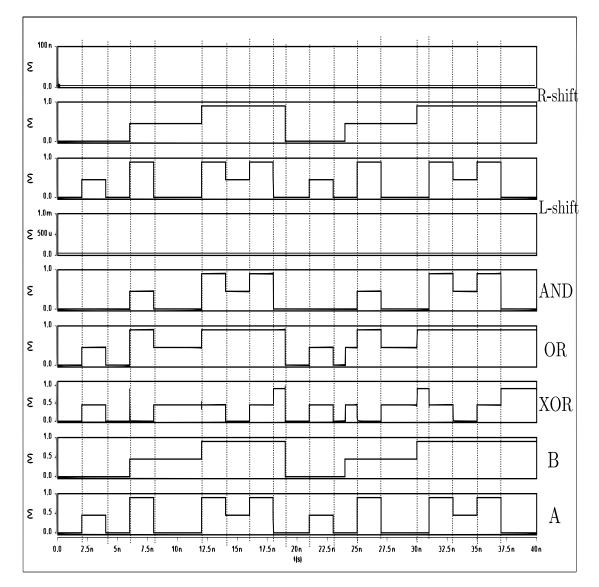

| 3.15 | Waveforms for Logic and Shift operations                                       | 51 |

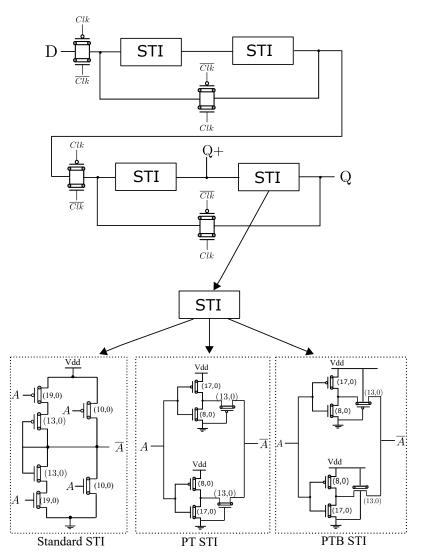

| 4.1  | Designs of Ternary D-flipflops using existing STI gate designs of a) a         |    |

|      | standard STI [5], b) a PT-STI [58] and c) a PT-STI with body effect [75]       | 58 |

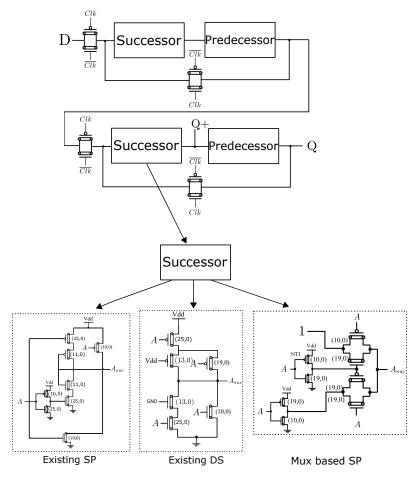

| 4.2  | Designs of Ternary D-flipflops using Successor-predecessor gate designs        |    |

|      | in a) [57], b) [73] and c) [74]                                                | 59 |

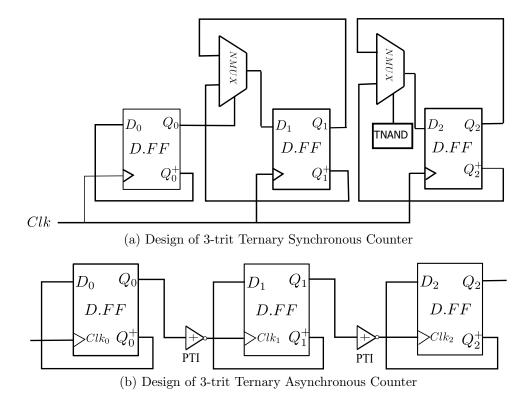

| 4.3  | Existing design of 3-trit ternary counters in [57] and [73]. $\ldots$ $\ldots$ | 59 |

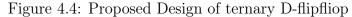

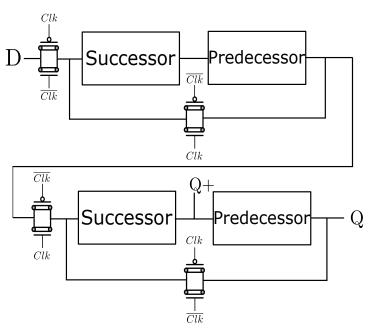

| 4.4  | Proposed Design of ternary D-flipfliop                                         | 62 |

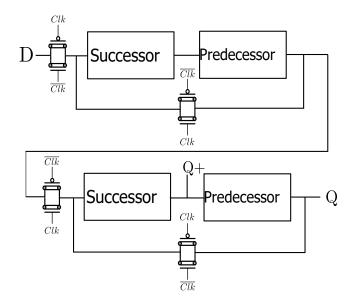

| 4.5  | Proposed Design of ternary D-flipfliop using successor-predecessor cir-        |    |

|      | cuits                                                                          | 64 |

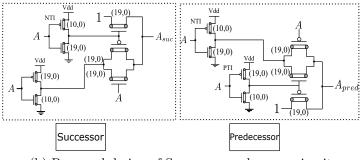

| 4.6  | Proposed hybrid designs for ternary D-flipflops                                | 65 |

| 4.7  | Proposed design of ternary asynchronous counters showing the next              |    |

|      | state generation logic                                                         | 66 |

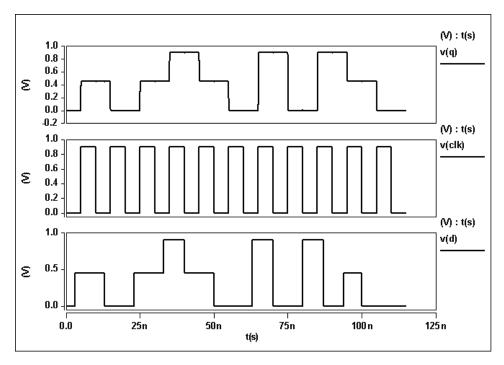

| 4.8  | Waveforms for proposed buffer-STI based ternary D-flipflop                     | 69 |

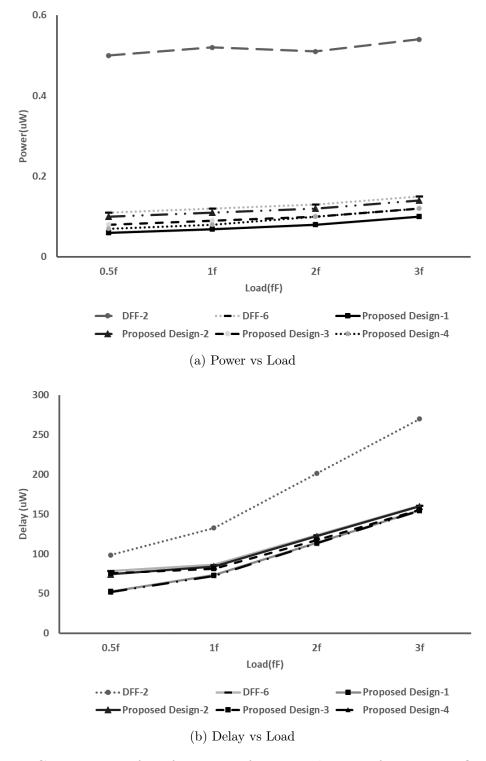

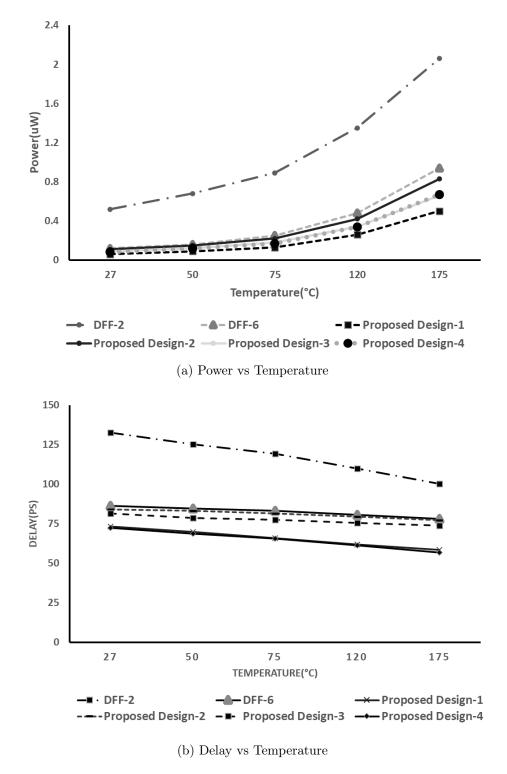

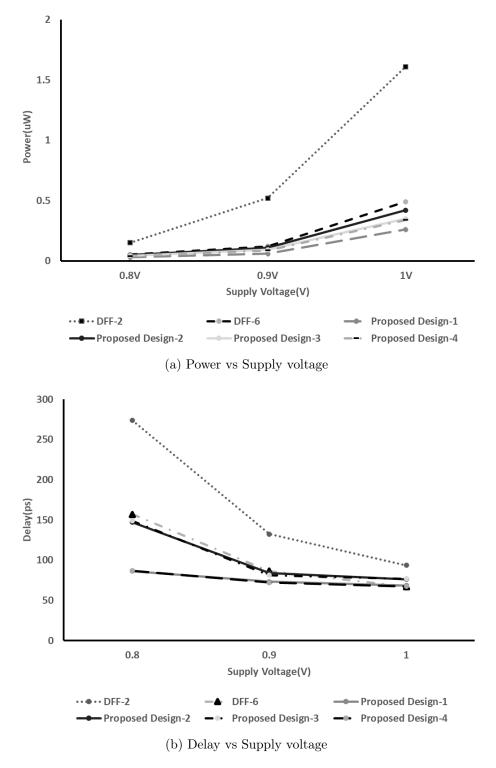

| 4.9  | Comparision of performance of various designs of ternary D-flipflop for        |    |

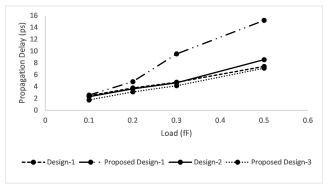

|      | variations in load in terms of a) power b) delay                               | 74 |

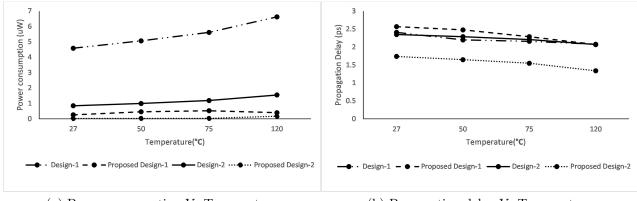

| 4.10 | Comparision of performance of various designs of ternary D-flipflop for        |    |

|      | variations in temperature in terms of a) power b) delay $\ldots \ldots \ldots$ | 75 |

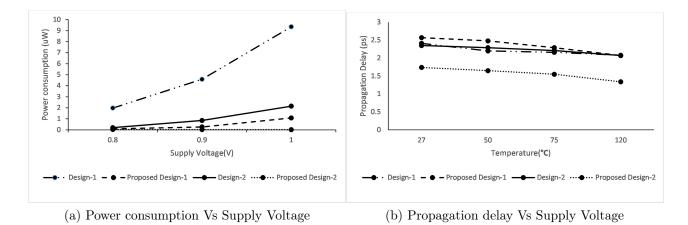

| 4.11 | Comparision of performance of various designs of ternary D-flipflop for        |    |

|      | variations in supply voltage in terms of a) power b) delay                     | 76 |

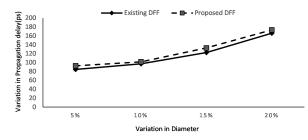

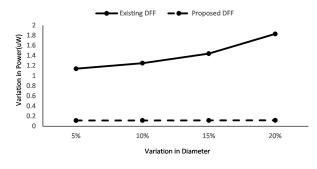

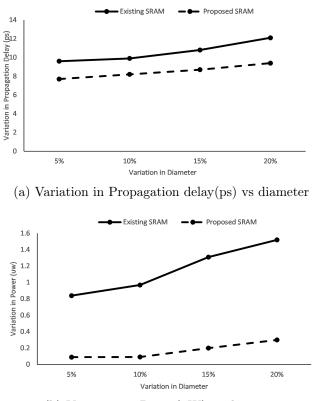

| 4.12 | Effect of variation in diameter on propagation delay and power                 | 77 |

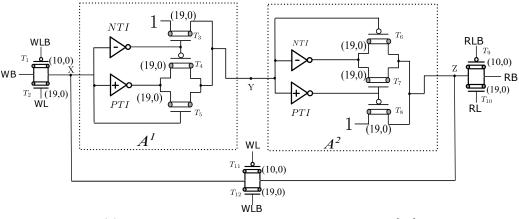

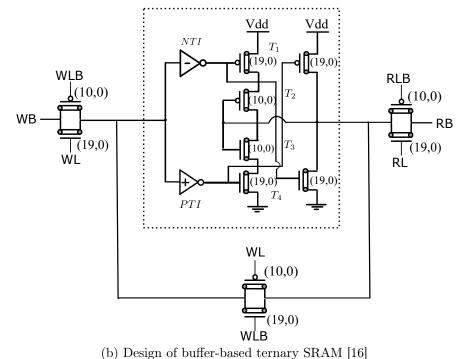

| 5.1  | Existing designs of ternary SRAM [16]                                    | 82  |

|------|--------------------------------------------------------------------------|-----|

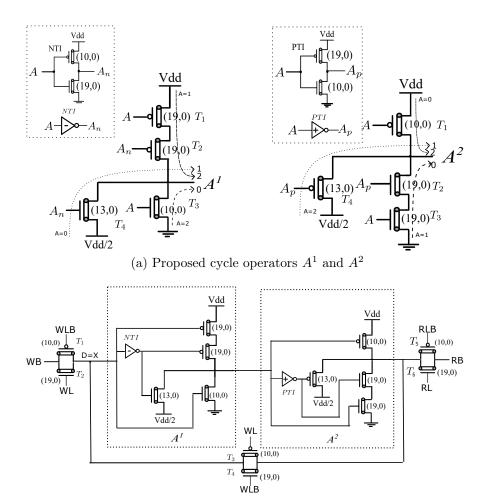

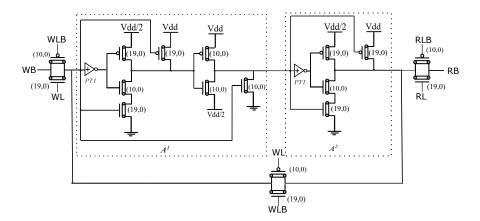

| 5.2  | Proposed cycle operators and cycle operator-based ternary SRAM de-       |     |

|      | signs                                                                    | 84  |

| 5.3  | Second proposed design of cycle operator-based ternary SRAM              | 85  |

| 5.4  | Proposed design of buffer-based ternary SRAM                             | 85  |

| 5.5  | Proposed design of a $3X3$ ternary SRAM using buffer-based SRAM cell     | 87  |

| 5.6  | Static noise margins of various existing and proposed designs of ternary |     |

|      | SRAM                                                                     | 90  |

| 5.7  | Simulation waveforms for proposed cycle operator-based ternary SRAM      | 91  |

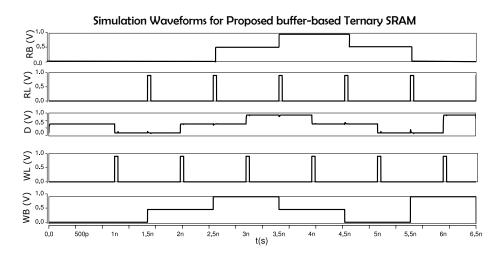

| 5.8  | Simulation waveforms for proposed buffer-based ternary SRAM              | 91  |

| 5.9  | Power and delay of proposed ternary SRAM versus existing ternary         |     |

|      | SRAM for variations in load, temperature and supply voltage              | 92  |

| 5.10 | Power and delay of proposed ternary SRAM versus existing ternary         |     |

|      | SRAM for variations in temperature                                       | 92  |

| 5.11 | Power and delay of proposed ternary SRAM versus existing ternary         |     |

|      | SRAM for variations in temperature                                       | 93  |

| 5.12 | Effect of variation in diameter on propagation delay and power           | 93  |

| 6.1  | Proposed 9-trit Instructions Format                                      | 99  |

| 6.2  | Proposed Architecture for a CNFET-based Ternary Logic Processor .        | 101 |

| 6.3  | Proposed design of Ternary Instruction Fetch Unit (TIF)                  | 103 |

| 6.4  | Design of ternary SRAM cell used in Ternary Instruction Memory [14]      | 104 |

| 6.5  | Proposed design of the Ternary Register File (TRF)                       | 105 |

| 6.6  | Design of 9:1 multiplexer using 3:1 multiplexers [12]                    | 107 |

| 6.7  | Design of Proposed 3-trit Ternary Arithmetic and Logic Unit (TALU)       | 108 |

| 6.8  | Design of 2:1 multiplexers used for the TALU [31]                        | 109 |

| 6.9  | Proposed 27X3 Ternary Data Memory built using 3-trit words $\ldots$      | 110 |

| 6.10 | Proposed Design of Ternary Control Unit (TCU)                            | 112 |

| 6.11 | Proposed Design of Branching Unit (BU)                                   | 113 |

| 6.12 | Proposed Design of Immediate Generate Unit (IGU)                         | 113 |

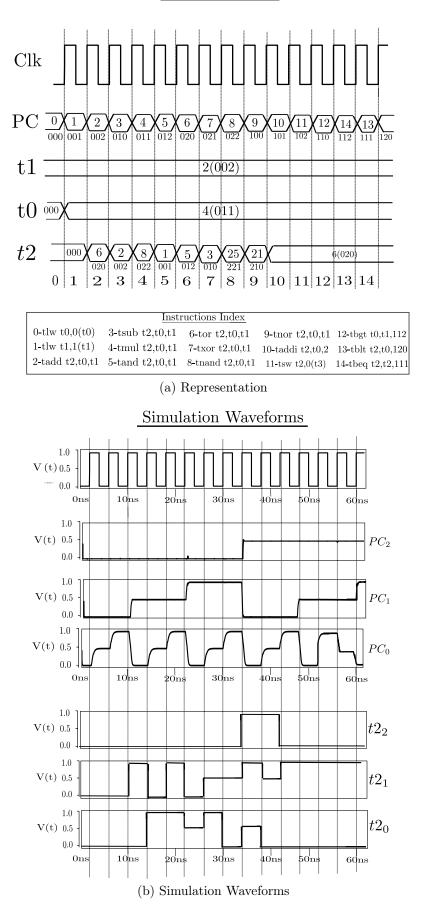

| 6.13 | Representation and the Simulation waveforms for the proposed TLP |     |

|------|------------------------------------------------------------------|-----|

|      | running Program-1 containing all instructions                    | 120 |

# Nomenclature

| ALU   | Arithmetic-Logic-Unit                   |

|-------|-----------------------------------------|

| BU    | Branching-Unit                          |

| CLA   | Carry-Lookahead-Ader                    |

| CNFET | Carbon-Nanotube-Field-Effect-Transistor |

| CNT   | Carbon-Nano-Tube                        |

| CSA   | Conditional-Sum-Adder                   |

| FAS   | Full-Adder-Subtractor                   |

| GCD   | Greatest-Common-Divisor                 |

| НА    | Half-Adder                              |

| HAS   | Half-Adder-Subtractor                   |

| IGU   | Immediate-Generate-Unit                 |

| ISA   | Instruction-Set-Architecture            |

| MIT   | Massachusetts-Institute-of-Technology   |

| MVL   | Multi-Valued-Logic                      |

| NTI   | Negative-Ternary-Inverter               |

| PC    | Program-Counter                         |

| PDP    | Power-Delay-Product                 |

|--------|-------------------------------------|

| PTI    | Positive-Ternary-Inverter           |

| RISC   | Reduced-Instruction-Set-Computer    |

| RRAM   | Resistive-Random-Access-Memory      |

| SNM    | Signal-to-Noise-Margin              |

| SRAM   | Static-Random-Access-Memory         |

| STI    | Standard-Ternary-Inverter           |

| T-SRAM | Ternary-Static-Random-Access-Memory |

| TALU   | Ternary-Arithmetic-Logic-Unit       |

| TCU    | Ternary-Control-Unit                |

| TDM    | Ternary-Data-Memory                 |

| TG     | Transmission-Gate                   |

| TIF    | Ternary-Instruction-Fetch           |

| TIM    | Ternary-Instruction-Memory          |

| TLP    | Ternary-Logic-Processor             |

| TRF    | Ternary-Register-File               |

## Chapter 1

## Introduction

### 1.1 Overview & Motivation

CMOS (Complementary Metal-Oxide-Semiconductor) technology has been the driving force behind the growth of the semiconductor industry for several decades. This technology is used in the manufacturing of integrated circuits (ICs), including microprocessors, memory chips, and other electronic devices. One of the main challenges in CMOS technology is the issues arising due to the continuous scaling of transistors. Scaling refers to the process of reducing the size of transistors and other components on an IC while improving their performance [1]. As transistors are made smaller, they can be packed more densely onto an IC, which can lead to higher performance and lower power consumption. However, as transistors are scaled down, various physical and electrical effects become more pronounced, which can make it more difficult to maintain good performance and reliability. These scaling issues have led to a slowdown in the pace of Moore's Law [2], which is the observation that the number of transistors on an IC double approximately every two years. As the demand for smaller, faster, and more energy-efficient ICs has continued to increase, researchers and engineers have been exploring a variety of post-CMOS technologies that could potentially replace or supplement CMOS technology in the future and overcome the scaling issues. Few of the new device technologies that are being studied, as an alternative to CMOS, are the CNFET (Carbon-Nanotube-Field-Effect-Transistor), the FinFET (fin-Field-EffectTransistor) and the QDGFET (Quantum-Dot-Gate-Field-Effect-Transistor).

CNFET devices have been found to be energy efficient [3] when compared to the MOSFETs for building digital logic circuits. The design of a modern RISC-based microprocessor using CNFETs by researchers at MIT [4] has ignited interest in this field of study in recent times. Along with the CNFET technology, various post-binary computing methodologies like quantum computing and Multi-valued logic computing are also being explored. Multi-valued logic uses more than two logic levels for computation. Ternary logic is a special case of MVL that uses three discrete logic levels for computation. A ternary system is better than a binary system in terms of the complexity of interconnects and information density. A ternary system requires a lesser number of bits to represent a number when compared to binary. For example, a 10-digit (N-digit) binary number needs only 6-digits ( $log_3(2^N - 1)$ ) in ternary. These advantages make ternary logic more appealing.

In order to build circuits using ternary logic, transistors with multiple threshold voltages are required. Using CMOS for building ternary circuits would require body biasing of transistors increasing the complexity of the design. In the CNFET, the channel is made up of CNTs. By changing the diameter of these CNTs, transistors with different threshold voltages can be obtained, making CNFET a viable candidate for ternary logic circuit implementation.

The goal of the thesis is to design and implement a ternary logic processor using CN-FETs (Carbon Nanotube Field-Effect Transistors) technology. Ternary logic circuits, which operate on three logic levels instead of the traditional binary (two levels), have been extensively studied and implemented using CNFETs in the past decade. Previous research papers [5–17] have explored various aspects of CNFET-based ternary logic circuits, including inverters, logic gates, arithmetic logic units (ALUs), and ternary memory. While some studies have discussed the concept of a ternary logic processor [18, 19], none have presented a transistor-level architecture employing CNFETs for such a processor.

To address this gap, the thesis proposes the utilization of ternary logic computation

coupled with CNFET technology to design and implement a CNFET-based ternary logic processor. The thesis introduces various essential ternary circuits that serve as the fundamental building blocks of the processor. The first contribution is a new architecture for a power-efficient ternary ALU (Arithmetic Logic Unit). The ALU is responsible for performing arithmetic and logical operations in the processor. The proposed architecture aims to minimize power consumption while maintaining efficient ternary computation.

Next, the thesis focuses on ternary sequential logic circuits, specifically ternary Dflip-flops. These flip-flops are essential components of the ternary register file, which stores data in the ternary processor. The design of these circuits ensures proper storage and retrieval of ternary values. Furthermore, power-efficient designs for a ternary single-cell SRAM (Static Random Access Memory) are proposed. The SRAM cells are used to construct the instruction and data memory of the processor. The designs aim to minimize power consumption while providing reliable ternary memory storage.

Finally, the thesis culminates in the design of a power-efficient CNFET-based ternary logic processor. This processor integrates all the proposed circuits, including the ternary ALU, ternary D-flip-flops, and ternary single-cell SRAM. The proposed circuits and architecture aim to achieve power efficiency and reliable ternary computation, paving the way for further advancements in ternary logic technology.

#### 1.2 Background

#### 1.2.1 Ternary Logic

Ternary logic, as the name suggests, is three valued logic that uses three logic levels for computation. The three logic levels are represented by 0,1 and 2 respectively. A function f(X) is defined as a ternary logic function mapping  $\{0, 1, 2\}^n$  to  $\{0, 1, 2\}$  where X is given by  $X_1, \ldots, X_n$ . When  $X_i, X_j \in \{0, 1, 2\}$ , the basic operations of ternary logic can be defined as:

$$X_i + X_j = max\{X_i, X_j\} \tag{1.1}$$

$$X_i \cdot X_j = \min\{X_i, X_j\} \tag{1.2}$$

$$\overline{X_i} = 2 - X_i \tag{1.3}$$

where equations (1.1), (1.2) and 1.3 indicate OR, AND and NOT operations respectively for ternary logic [5].

Inversion is an important function in Ternary Logic. The general inverter with input x and outputs y0,y1,y2 is denoted as [5]:

$$y0 = C0(x) = \begin{cases} 2, & if \ x = 0\\ 0, & if \ x \neq 0 \end{cases}$$

(1.4)

$$y1 = C1(x) = \overline{x} = 2 - x \tag{1.5}$$

$$y^{2} = C^{2}(x) = \begin{cases} 2, & \text{if } x \neq 2\\ 0, & \text{if } x = 2 \end{cases}$$

(1.6)

Hence, three ternary inverters namely, Negative Ternary Inverter (NTI), Standard Ternary Inverter (STI), and Positive Ternary Inverter (PTI) corresponding to outputs y0,y1 and y2 are defined for ternary logic. Their truth table is as shown in Table 1.1.

| Input x | NTI $(x)$ | <b>STI</b> $(x)$ | <b>PTI</b> $(x)$ |

|---------|-----------|------------------|------------------|

| 0       | 2         | 2                | 2                |

| 1       | 0         | 1                | 2                |

| 2       | 0         | 0                | 0                |

Table 1.1: Ternary Inverters [5]

| Voltage Level | Logic Value |

|---------------|-------------|

| 0             | 0           |

| Vdd/2         | 1           |

| Vdd           | 2           |

Table 1.2: Logic Symbols

| Table 1.3: Trut | h Table for TC | )R and TAND |

|-----------------|----------------|-------------|

| Α | В | A(TOR)B | A(TAND)B |

|---|---|---------|----------|

| 0 | 0 | 0       | 0        |

| 0 | 1 | 1       | 0        |

| 0 | 2 | 2       | 0        |

| 1 | 0 | 1       | 0        |

| 1 | 1 | 1       | 1        |

| 1 | 2 | 2       | 1        |

| 2 | 0 | 2       | 0        |

| 2 | 1 | 2       | 1        |

| 2 | 2 | 2       | 2        |

The logic values 0, 1 and 2 correspond to voltages 0, V dd/2 and V dd respectively as shown in Table 1.2. The truth table 1.3 for the basic ternary AND and OR functions is derived from these equations, where the OR of two ternary digits is the maximum of the two digits and the ternary AND is given by the minimum of the two digits respectively. The basic ternary NAND, NOR gates and the ternary inverters STI,PTI,NTI are represented as shown in Figure 1.1.

Transistors with different threshold voltages are required for implementation of ternary logic circuits. CNFETs are ideal for implementing ternary logic circuits since

Figure 1.1: Ternary inverters and basic logic gates

using CNFETs of different chiralities different threshold voltages can be obtained. The following section describes the CNFETs in more detail.

#### 1.2.2 Carbon-Nanotube Field Effect Transistor (CNFET)

CNFET consists of CNTs (Carbon-Nano-Tubes) that act as the channel between the two metal electrodes that are the source and the drain instead of the substrate as in the case of MOSFET. A SWCNT (single-walled carbon nanotube) is formed by rolling a sheet of graphite along a certain angle called the chirality vector of the CNT, as shown in Figure 1.2The roll-up vector is represented by C = na + mb, where'a' and 'b' are unit lattice vectors and m and n are positive integers which specify the chirality of the CNT. Based on the values of the integer pair (n, m) the SWCNTs are further classified into armchair CNT (if n = m), zigzag CNT (if n = 0 or m = 0) and chiral CNT (if m! = n! = 0). All armchair CNTs behave as conductors. On the other hand, zigzag and chiral CNTs show metallic (conducting) behavior when n = m or n-m = 3i, where i is an integer, otherwise, they show semiconducting behavior. Hence the zigzag and chiral CNTs are used in realizing a CNFET [20].

CNFETs function similarly to MOS transistors in terms of their operating principle. As depicted in Figure 1.3 this three (or four) terminal device is comprised of a semiconducting nanotube serving as a conducting channel and connecting the source and drain contacts. The gate turns the device on or off electrostatically. The drain current is directly proportional to the number of CNTs connected between the source and drain as well as their respective diameters [21, 22].

CNFETs with different chiralities have different threshold voltages. The chirality is also related to the diameter of the CNT. The gate width of CNFET can be approximated using equation below [21]:

$$W \approx \min(W_{min}, N \times S) \tag{1.7}$$

Figure 1.2: Unrolled sheet of graphite and the rolled lattice structure of CNT

Figure 1.3: Carbon-Nanotube Field Effect Transistor (CNFET) 3-D view

In equation (1.7),  $W_{min}$  is the minimum gate width, N is the number of tubes and S the distance between the centers of two adjoining CNTs under the same gate, also called as Pitch. The diameter of CNT,  $D_{CNT}$ , which depends on the chirality vector (n, m) can be calculated using equation below:

$$D_{CNT} = \frac{\sqrt{3}a_0}{\pi} (\sqrt{n^2 + m^2 + mn})$$

(1.8)

where  $a_0 = 0.142nm$  is the inter atomic distance between each carbon atom and its neighbour. The threshold voltage, which is the voltage needed to turn ON the device electrostatically via the gate, can be approximated to the first order as the half band gap and can be calculated by equation (1.9) [21].

$$V_{th} \approx \frac{E_g}{2e} = \frac{1}{\sqrt{3}} \frac{aV_{\pi}}{eD_{CNT}} = \frac{0.43}{D_{CNT}(nm)}$$

(1.9)

In the above equation,  $V_{\pi}(=3.033 eV)$  is the carbon  $\pi$  -  $\pi$  bond energy in the tight

| Chirality | Diameter<br>of CNT | Threshold Voltage<br>of N-CNFET | Threshold Voltage<br>of P-CNFET |

|-----------|--------------------|---------------------------------|---------------------------------|

| (19,0)    | 1.487 nm           | 0.289V                          | -0.289V                         |

| (17, 0)   | 1.330nm            | 0.328V                          | -0.328V                         |

| (16, 0)   | 1.253nm            | 0.348V                          | -0.348V                         |

| (14, 0)   | 1.100nm            | 0.398V                          | -0.398V                         |

| (13,0)    | 1.018nm            | 0.428V                          | -0.428V                         |

| (11, 0)   | 0.861 nm           | 0.506V                          | -0.506V                         |

| (10, 0)   | 0.783 nm           | 0.559V                          | -0.559V                         |

Table 1.4: Relation Between Chirality, CNT Diameter and Threshold Voltage [21]

bonding model, a(= 0.249nm) is the carbon-carbon atom distance and e is the unit electron charge. If the chirality vector of CNT changes then the threshold voltage of the CNFET will also change. Assuming the m value in the chirality vector is always zero, the ratio of the threshold voltages of two CNFETs with different chirality vectors can be represented by equation below:

$$\frac{V_{th1}}{V_{th2}} = \frac{D_{CNT2}}{D_{CNT1}} = \frac{n_2}{n_1} \tag{1.10}$$

Equation (1.10) shows that threshold voltage of CNFET is inversely proportional to the diameter of CNT which, as mentioned above, depends on its chirality vector. As the CNFET allows for controlling the threshold voltage by changing its CNT diameter, it is suitable for ternary logic circuit implementation.

Table 1.4 illustrates the relationship between chirality, CNT diameter, and threshold voltage as deduced from relationships given in [21]. Well-controlled CNTs are now produced using improved techniques. While it is possible to create CNFETs with any desired chirality, the CNFET-based ternary logic circuits typically uses three chiralities, namely (19,0), (13,0), and (10,0) [5].

In spite of the fact that there are numerous CNFET device models in the literature [21–25], Stanford CNFET device models reported in [26] that are based on work presented in [21, 22] have been widely used for the implementation of CNFET-based circuits. As a result, this work's models use the CNFET model. The Table 1.5lists the technology parameters of CNFET along with a short description and numerical value.

| Parameter            | Description                                        | Value         |

|----------------------|----------------------------------------------------|---------------|

| $L_{ch}$             | Physical channel length                            | 32nm          |

| $L_{geff}$           | Mean free path in the intrinsic CNT channel region | 100 <i>nm</i> |

| $L_{ss}$             | Length of doped CNT source-side extension region   | 32nm          |

| $L_{dd}$             | Length of doped CNT drain-side extension region    | 32nm          |

| $E_{fi}$             | Fermi level of the doped $S/D$ tube                | 0.6 eV        |

| K <sub>gate</sub>    | Dielectric constant of high-k top gate dielectric  | 16            |

|                      | material                                           |               |

| $T_{ox}$             | Thickness of high-k top gate dielectric material   | 4.0nm         |

| $C_{sub}$            | Coupling capacitance between the channel region    | 40pF/m        |

|                      | and the substrate                                  |               |

| $V_{fbn} \& V_{fbp}$ | Flat-band voltage for n-CNFET and p-CNFET,         | 0eV, 0eV      |

|                      | respectively                                       |               |

| L_channel            | Physical gate length                               | 32nm          |

| Pitch                | Distance between the centers of two adjacent CNTs  | 20nm          |

| $L_{eff}$            | Mean free path in $p+/n+$ doped CNT                | 15nm          |

| phi_M                | Work function of Source/Drain metal contact        | 4.6 eV        |

| phi_S                | CNT work function                                  | 4.5 eV        |

Table 1.5: Technology Parameters for CNFET model in [21, 22, 26]

HSPICE simulations are carried out using this CNFET model for ternary logic circuits like ternary ALU, D-flipflops, counters, register, and SRAM cell and performance parameters like power consumption, propagation delay and PDP are calculated. Each of these circuits are then integrated to implement a single-cycle ternary processor in HSPICE which uses this CNFET model. The outline of the work carried out in this thesis is described in the next section.

### 1.3 Thesis Outline

This thesis is organized as follows:

Chapter 2 presents in brief the literature review of the design of CNFET-based ternary logic circuits. An overview of the various design approaches for ternary logic, the basic and complex ternary combinational logic circuits, ternary sequential logic circuits and ternary memories proposed in literature till date is given. Then, based on the research gaps identified from the literature review, objectives are framed for the thesis. Chapter 3 describes the design of a ternary ALU implemented using CNFETs. The proposed ternary ALU reduces circuit complexity by eliminating few blocks of the existing ternary ALU architecture and using a 2:1 multiplexer based approach to design the functinal blocks of the TALU. The 2:1 multiplexer based design approach helps in improving the power efficiency of the overall design. A complete TALU that performs arithmetic operations like addition, subtraction, multiplication, and comparison and logic operations like Ex-OR, OR, AND, NOR and NAND is designed, simulated and is compared with the existing TALU designs for performance.

Ternary sequential circuits using CNFETs are given very meager attention in the literature. Chapter 4 talks about novel design methodologies to implement efficient ternary sequential logic circuits like ternary D-flipflops. Four new designs of ternary D-flipflops are presented. The first design is a ternary buffer and STI based design, the second design is a multiplexer based design that uses successor-predecessor circuits for designing D-flipflops. The third and fourth designs are hybrid designs. All the four presented designs show improvement in terms of circuit parameters compared to existing designs.

Memory is an important part of any system. Chapter 5 presents new power-efficient designs of a ternary SRAM cell. Two new cycle operator-based designs and one ternary buffer based design is presented.

The ternary ALU, ternary D-flipflops and ternary memory implemented in the above chapters are used to build the fundamental blocks of the processor which are in-turn used to implement the CNFET-based ternary logic processor, in Chapter 6. An instruction set architecture is proposed for this processor and the working of the processor design is checked by implementing a few programs on it. The functionality of the proposed CNFET-based ternary processor is also verified by implementing it in Simulink.

Finally, Chapter 7 sums up the work, draws conclusions from the key outcomes and lists the main contributions of the research work. The objectives for the future work are also proposed in this chapter.

### Chapter 2

## Related work

### 2.1 Literature Review

In CNFET technology, the threshold voltage is regulated by altering the diameter (i.e., Vth dependent on physical dimension) of the CNT, which in turn depends on the chirality vector, as opposed to MOS technology, where body biasing is employed to control threshold voltages. Because of this dependency, CNFETs can be used to build MVL circuits. The recent demonstration of a CNFET-based modern RISC-based (Reduced-Instruction-Set-Computer-based) processor by MIT (Massachusetts Institute of Technology) researchers [4] has rekindled interest in CNFETs, which had been diminishing in recent years due to complex manufacturing technology and reliability concerns. This processor is the conventional binary logic processor designed entirely using CNFETs, that served as the inspiration for this thesis, which endeavours to design a CNFETbased ternary logic processor.

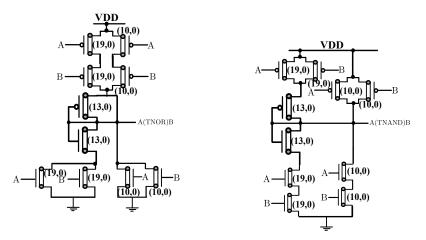

CNFETs have the potential to be useful in computations involving ternary logic. The concept of ternary logic or the use of three logic levels instead of two, dates back to the thesis presented on ternary digital systems in 1967 [27]. It presented the algebra for ternary logic and the design of basic gates. A standard STI gate design, a few logic gates like the NAND and NOR gate and a half adder, were first proposed in [5]. The design of ternary inverters NTI,STI and PTI are as shown in Figure 2.1. These designs are derived from the truth table for ternary inverters. Also, the basic ternary NOR

Figure 2.1: Design of ternary Inverters using CNFETs

Figure 2.2: Design of ternary NOR and NAND gates

and NAND gates designs are shown in Figure 2.2.

The next sub-sections describe the design of various ternary combinational, sequential and memory circuits that are available in literature so far, which is a step towards the design of a ternary logic processor.

#### 2.1.1 Design of Basic Ternary Combinational Logic circuits

The basic ternary combinational logic circuits like logic gates, STI (Standard Ternary Inverter), half adder, full adder, 1-digit multiplier and comparator are presented using CNFETs in different research papers till date. Various design approaches are used to implement the basic ternary combinational logic circuits. Six different CNFET-based ternary logic circuit design approaches can be found in literature:

- 1) Decoder-Encoder based approach

- 2) 3:1 Multiplexer-based approach

- 3) Decoderless approach

- 4) Low-power encoder approach

- 5) 2:1 Multiplexer-based approach

- 6) Dual supply based approach

Various half adder designs that are implemented using these design approaches are as presented below.

Figure 2.3: Approach I: Decoder-Encoder based HA [5]

Figure 2.4: Ternary decoder used in Approach-1

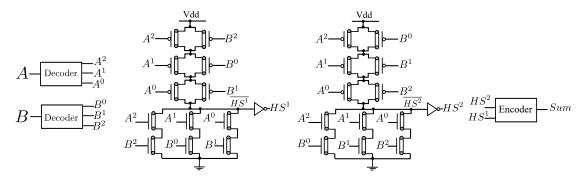

The decoder-encoder-based method [5], Approach-I, for designing ternary logic circuits can be divided into three stages. In the initial stage, a ternary decoder converts a ternary signal into mutually exclusive unary functions with two logic levels, logic 0 and logic 2. These decoder outputs can only accept logic values 2 and 0, which correspond to logic 1 and logic 0 in binary logic. In the second stage, the outputs of ternary decoders are combined using binary logic gates. The ternary decoder used in this approach in Figure 2.3 is as shown in Figure 2.4. In the third and final stage, the second stage outputs are combined using an encoder to produce the ternary outputs. A ternary encoder is made up of a level shifter and a ternary OR gate. The Figure 2.3, shows a Half Adder (HA) sum designed using the Decoder-encoder-based design approach. This approach utilises a complex encoder and a ternary decoder for each input, that results in large area and power consumption for higher operand sizes.

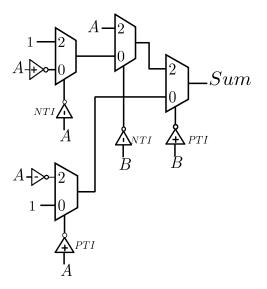

Next, the 3:1 Multiplexer approach, Approach II, as described in [28] uses unary operators and 3:1 multiplexers, for implementing ternary logic circuits. A ternary HA designed using this approach is shown in Figure 2.5. This approach has advantages in terms of power consumption when compared to Approach I but suffers from large propagation delay. Another method, Approach-III, described in [29], is a decoderless approach that uses a low power encoder and no decoders. This technique results in ternary circuits with low transistor count and hence optimised in terms of area and power. A ternay HA designed using this method is shown in Figure 2.6.

Figure 2.5: Approach II: 3:1 Multiplexer based HA [28]

Figure 2.8: Proposed decoder and encoder designs in Approach-III and Approach-IV

Figure 2.6: Approach III: Decoderless HA [29]

Figure 2.7: Approach IV: Lowdelay decoder based HA [30]

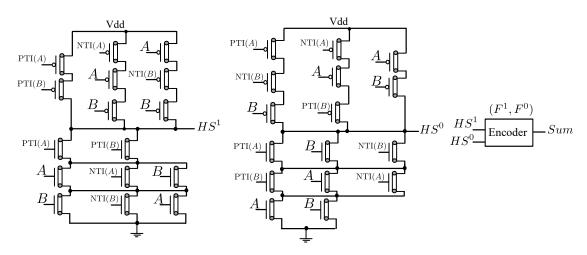

Figure 2.9: Approach V: 2:1 Multiplexer based HA [31]

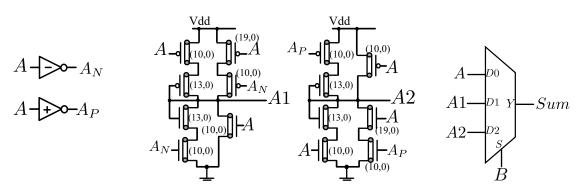

The Approach-IV, utilises a low delay decoder and the low power encoder to design energy-efficient ternary circuits. The proposed delay optimised decoder is proposed in [30]. The Figure 2.7 shows the HA Sum designed using this approach. Following this, a 2:1 multiplexer based approach, Approach V, was presented in [31], that resulted in ternary circuits which have very low power consumption. The basic idea for the origin of this approach was that the 3:1 multiplexers could be designed using 2:1 multiplexers. Hence, this approach was derived from Approach II. A ternary HA Sum implemented using this design approach is as shown in Figure 2.9. The encoder and decoder proposed in Approach-III and Approach-IV is as shown in Figure 2.8.

Figure 2.10: Approach VI: Dual supply based HA [32]

Finally, Approach-VI, is proposed recently in [32]. This approach assumes that two power supplies of Vdd and Vdd/2 are present for the implementation of ternary circuits. A HA Sum generation circuit that uses this approach is as shown in Figure 2.10. This approach utilises the unary operators of ternary system and employs two power supplies, to achieve considerable power consumptions when compared to all other existing design approaches.

Ternary full adder designs using CNTFETs are designed in [10, 28, 33–35] and multipliers are designed in [36, 37]. Some of the recent publications implementing CNFETbased basic ternary combinational circuits are discussed below.

In [38], a novel method for the design of an energy-efficient one-digit adder is proposed. The proposed design utilises ternary multiplexers to select successor and predecessor digits for output node values. This study also defines the novel ternary multiplexer, as well as the successor and predecessor cells. The successor and predecessors here are designed using the VDD/2 based design approach. A ternary full adder modeled using graphene barristors is demonstrated in [39].

The article [40] proposes a CNFET deployed Ternary Half Subtractor and Full Subtractor using unary operators. The design methodology for the implementation of 2-bit ternary comparator utilizing CNFET and resistive random access memory (RRAM) is presented in [41]. The work in [32] proposes new improved designs for ternary half adder and ternary multiplier using the VDD/2 based design approach. In [42], physical equations are used to suggest a systematic way to size transistors for a standard ternary inverter (STI). This study provides a thorough investigation to establish suitable physical parameter values for the CNFET-based STI.

#### 2.1.2 Design of Complex Ternary Combinational Logic circuits

Multi-digit adders, multi-digit multipliers and ALUs fall under the category of complex combinational logic circuits. Numerous designs of multi-digit adders have been proposed in literarture. Some of these are [8, 10, 28, 33–35]. [35] presents an efficient design of a ternary adder. This adder employs a low-complexity encoder and a fast carry generation device, that results in less propagation delay for multi-digit adders. Although the encoder used in [35] has reduced delay and complexity, it uses a lot of power.

[8] [30] presents energy-efficient single-digit and multi-digit adders. High-speed and power- efficient designs the ternary prefix adders are presented in [43]. In this paper, a technique is proposed that permits the use of the carry Propagate-Generate concept in multidigit ternary adders. CNFETs are used to implement multidigit ternary prefix adders that use binary prefix trees for payload computation. HSPICE is used to implement five variants of CNFET-based multidigit ternary adders that use distinct prefix networks for payload computation.

In [28], low-delay and low-power single-digit and multi-digit adders have been presented. Although multi-digit CSA (Conditional-Sum-Adder) and CLA (Carry-Lookahead-Ader) designs have low-propagation delays and least PDP, they have complex carry propagation path and consume large power when compared to other designs. In another paper [44], two design approaches for ternary CLA based on K-map and threshold logic methods are proposed in addition to their realization using CNTFETs only and memristor with CNTFETs. In terms of latency and area, a comparison and tradeoffs among the proposed designs are offered. In the K-map design technique, the comparison demonstrates that the transistor-only implementation is the better choice. However, in the threshold logic (TL) design, the memristor and transistor-based implementation based on memristor and transistor integration is the best.

Few multi-digit ternary multipliers are implemented recently in [45] and [46]. A novel approximate computing technique for low-power ternary multiplication is proposed in [45]. A carry-truncated ternary multiplier, error compensation circuits, and  $2 \times 2$  ternary multipliers with various accuracies are proposed here using the low-power design methodology with CNFETs. Ternary Wallace tree multipliers that reduce the number of transistors by using 4-input ternary adders are proposed in [46] to improve the performance of existing ternary multipliers. A ternary carry-select adder is also proposed to reduce the carry propagation delay, used as a carry-chain adder of the Wallace tree. The suggested multipliers were made using a custom ternary standard

Figure 2.11: Architecture of a ternary ALU first proposed [47]

cell library and a 28-nanometer complementary metal-oxide-semiconductor (CMOS) process.

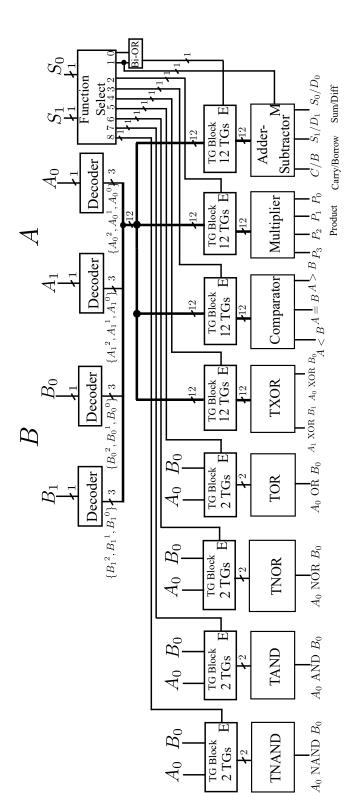

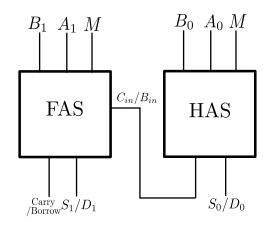

A 2-digit ternary ALU designed using CMOS technology is presented in [47]. CN-FET based Ternary ALUs (TALUs) have been designed in [48] and [11] which have an architecture similar to the one in [47] as shown in Figure 2.11. The basic architecture of the TALU consists of a decoder stage, a function select logic, a transmission gate stage and the functional modules that perform the operations, making the designs complex in terms of the number of transistors required to build the TALU. Also, these circuits use a decoder-encoder based design approach to build their functional modules which consume very high power due to the presence of VDD to Gnd paths in this approach. Another compact and enery efficient TALU design is implemented in [49]. Here, the arithmetic unit, adder and subtractor cells are combined to form a single unit. ALU functional units such as function selection unit and various processing modules are designed using efficient ternary multiplexers rather than the existing transmission gate and switching logic in [11].

#### 2.1.3 Design of Ternary Sequential Logic circuits

The concept of implementing multivalued Sequential logic circuits such as flipflops was first presented in [50]. A ternary edge triggered JKL-flipflop was proposed in [51]. Ternary sequential circuits have been given very less importance in literature so far and hence very few papers are present on this study which gives us a scope for exploring new designs in this area. Another JKL flipflop is presented in [52]. Here, a a novel design of low-power ternary Domino JKL flip—flop on the switch level is proposed. The circuit is simulated by using the Spice tool and the results show that the logic function is correct.

A novel 4-trit pulsed reversible counter is designed with Carbon Nanotube Field Effect Transistors(CNFET) in [53]. In [54], a flip-flop is proposed which captures and propagates a ternary data signal at the four boundaries of a ternary clock signal. It contains four varieties of logic gates: a ternary clock driver, a standard ternary inverter, a binary inverter, and a transmission gate. The results of an HSPICE simulation have confirmed that the power consumption of the flipflop is [55] less than that of conventional single-edge-triggered flip-flops. The work in [56] proposes a negative capacitance CNTFETs(NC-CNTFETs)-based ultra-efficient nonvolatile ternary flip-flop (FF).

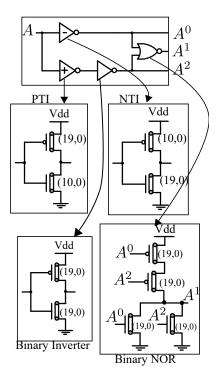

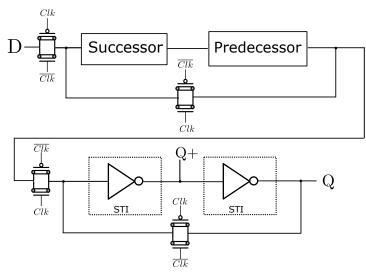

Mainly two design approaches are followed in existing CNFET-based ternary Dflipflops, one method uses STIs [58], and the other uses successor-predecessor circuits [57]. The successor circuit implements the next state logic, that is, for an input of logic '0' it outputs a logic '1' and for an input of logic '1' it outputs a logic '2'. The predecessor circuit implements the previous stage logic, that is, for an input of logic '2' it ouputs a logic '1' and for an input of logic '1' it outputs a logic '0'. Hence, the successor and predecessor circuits connected back to back act like a storage element and can be used in sequential logic circuits design. The STI-based ternary D-flipflop design is presented in [58] uses a pass transistor based STI gate implementation that

Figure 2.12: Design of a ternary D-flipflop using successor-predecessor circuits [57]

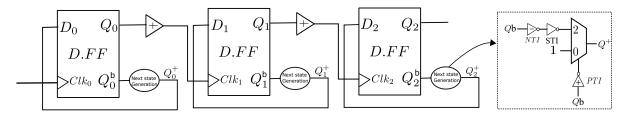

performs better than the standard STI gate in [5] in terms of power as it avoids the VDD to gnd path generation for implementating logic '1' at the output. The designs in [57] and [59] use the successor-predecessor circuits for implementing D-flipflops but these designs are complex in terms of number of CNFETs used and power consumption. Here, the designs for 3-digit ternary synchronous and asynchronous counters are also presented utilising the D-flipflop designs. And since the counter designs are made up of D-flipflops the power consumed by the ternary D-flipflop also affects the power consumed by the counters. The architecture of a successor-predecessor based ternar D-flipflop is as shown in Figure 2.12.

The design methodology for single-edge triggered ternary shift registers is presented in [60]. The D-flip-flops are designed using multiplexer-based positive and negative latches. Following this, series connection of D-flip-flops is done to build serial input serial output and parallel input serial output registers. The parallel input serial output registers are capable of operating in two modes: loading and shifting, and three configurations of AND-OR logic, NAND logic, and latch-based selection circuitry are proposed. According to simulation results, the proposed ternary shift registers reduce power consumption and energy consumption by more than 80% compared to their contemporary counterparts. Recently, a three-valued D-flip-flop (D-FF) circuit and a two-stage shift register built from InGaAs-based multiple-junction surface tunnel transistors (MJSTT) and Si-based metal-oxide-semiconductor field effect transistors (MOSFET) have been demonstrated in [55].

#### 2.1.4 Design of Ternary Memories

The design of ternary memory using the CMOS technology was presented in [61, 62]. The first ternary memory design using CNFETs was proposed in [17]. In this paper, a new design of a ternary memory cell which uses seperate read and write mechanisms is proposed. Simulation results using HSPICE have showed that the proposed CNTFET-based ternary cell performs the correct function during the read and write operations. It has also been shown that the proposed ternary cells achieve a high SNM due to the separate read and write operations, more than 90 lower standby power consumption for the "0" and "2" states and low area compared to a conventional binary CMOS implementation [17]. Back to back inverters are used in traditional memory cells as basic components of the storage element for the correct states; access transistors (such as pass or transmission gates) are commonly used to read and write from the back to back inverters. The design of the CNFET-based ternary SRAM in [17] is as shown in Figure 2.13.

Another paper in [63] proposed a novel design of a ternary SRAM cell. Unlike previous ternary cells, the proposed cell does not require a read buffer for changing the voltage level of the read bit line, because it uses additional CNTFETs to sink the bit lines to ground. By using four additional CNTFETs for ternary operation, a conventional (two-valued) sense amplifier is then used for output response [63]. The CNTFETs of the ternary cells were sized by grouping them; the chirality of the CNTFETs was modified to improve the SNM and reduce power dissipation while maintaining balanced operation. The chirality of the CNTFETs in the write and read circuits has been enhanced to minimise write/read times in a ternary CNTFET SRAM, producing considerable gains in PDP for the proposed SRAM cell.

The work in [64] proposes two new ternary CNFET-based SRAM cells. The first suggested CNFET SRAM sinks the bit lines to ground using extra CNFETs; its op-

(b) Circuit diagram

Figure 2.13: CNFET-based single-cell Ternary SRAM a) basic block diagram b) transistor-level diagram [17]

eration is nearly independent of the ternary values. The second cell incorporates the traditional voltage controller (or supply) of a binary SRAM into a ternary SRAM by adding two CNFETs to the first suggested cell. CNFET characteristics (such as size and density), performance measures (such as SNM and PDP), and write/read timings are all extensively studied and evaluated.

In [65], two ternary SRAMs with reduced delay as compared to their predecessor are proposed. Both proposed SRAMs make use of an enhanced inverter, which is a key component of SRAMs.

[15] demonstrates a read-disturb-free, ternary SRAM cell that uses 17 Carbon Nanotube Field-Effect Transistors. (CNFET). The suggested ternary SRAM cell works on two voltage levels and can store three voltage levels. The proposed SRAM is energyefficient because the Power Delay Product (PDP) is less during write and read processes than in previous designs.

A STI structure that consumes little current when the input voltage is VDD/2, is presented in [66]. In addition, a ternary SRAM cell was created by employing the storage element with back-to-back STIs and read/write schemes for ternary SRAM cells were developed. To confirm the operation stability of a ternary SRAM cell, three varieties of SNMs (Signal-to-Noise-Margins), were measured. By simulating a pre charging circuit, a ternary SRAM cell, and a write driver, write operation was implemented and the possibility of 'read' operation was demonstrated for a ternary SRAM cell.

A new ternary Static Random Access Memory (T-SRAM) cell is proposed in [67]. Carbon nanotube field-effect transistors are chosen as a proof-of-concept to verify the functionality of the suggested T-SRAM, whereas either post-CMOS or CMOS technologies can replace it. This T-SRAM greatly reduces leakage power and boosts robustness by eliminating the need to store the intermediate ternary state'svoltage level. SPICE simulation and comparison of the proposed T-SRAM with CMOS SRAMs in low-power edge AI applications reveals that it can be a promising substitute.

#### 2.1.5 Design of a Ternary Processor

The first CarbonNanotube computer was proposed in [68], which was built entirely using CNFETs. This was a binary processor that could run MIPS instructions. Then, another CNFET-based modern RISC based microprocessor was built in [4]. Taking inspiration from these demonstrations of CNFET-based binary processors, the concept of a Ternary Logic Processor is described in [18, 19]. The design and verification frameworks for a ternary logic processor are described in [18]. It shows the design and architecture of a RISC based ternary processor that operates on 9-digit long data, called ART-9 (Advanced RISC-based ternary). Although this work describes the block level architecture, the software-level framework and the hardware-level framework of a ternary processor, the complete design of the processor at the transistor level is not proposed. Another paper [19] details a VHDL-based efficient ISA for a ternary logic processor. For a 4-digit ternary processor, the proposed ISA specifies 21 instructions. This paves the way for the development of more efficient ISAs for future ternary logic processor architectures.

## 2.2 Research Gaps and Objectives of the thesis

The Research gaps were identified in the literature review described in the previous section. Designs for ternary ALU using CNFETs existing in literature consume large power and require a large number of transistors for its implementation. This is due to the complex designs where the decoders are used at the inputs and a decoder-encoder design approach is used to build the functional modules of the ALU. The decoder stage also increases the complexity of the transmission gate stage in the ALU. Also, the decoder-encoder based design approach is not power efficient. Hence, there is a need to develop an efficient design of a ternary ALU. The design of CNFET-based ternary sequential logic circuits like D-Flipflops, and counters have received very less attention in the literature. The existing D-flipflop designs are implemented using the successor and predecessor circuits for storing a logic value. These successor-predecessor circuits consume lot of power due to the VDD to Gnd paths present in their design. There is scope to develop new design techniques to implement ternary sequential logic circuits which are power efficient. Memory is a vital part of any system. The Ternary Memory block contributes significantly to the overall power consumed by a Ternary Logic Processor. The existing single-cell ternary SRAM designs are not power efficient. Hence, it is required to develop low-power designs for Ternary SRAM. The design of a CNFET-based Ternary Logic Processor at the transistor level has not been presented in literature yet. This thesis proposes the architecture and design of a 3-digit ternary logic processor built entirely using CNFETs. The functionality of this proposed ternary logic processor is also verified using standard programs. Four objectives are defined for this thesis. The first three objectives lead to the ultimate goal of this thesis, which is to design and implement a Ternary Logic Processor. The objectives are listed below:

1. Design of a 2-digit CNFET-based ternary ALU using the power-efficient 2:1 multiplexer-based design approach.

2. New design methodologies for ternary D-Flipflops and ternary counters.

- 3. Design of new power-efficient ternary single-cell SRAM.

- 4. Design of a CNFET-based Ternary Logic Processor.

## Chapter 3

# Design of CNFET-Based Ternary Arithmetic and Logic Unit

## 3.1 Introduction

A Ternary Arithmetic and Logic Unit (TALU) is the fundamental component of a ternary processor, as it is responsible for carrying out the mathematical and logical operations required by a computer program. The arithmetic operations that a TALU can perform include Ternary addition, subtraction, and multiplication. The ternary logical operations include TAND, TNAND, TOR, TNOR, TXOR, and various shift operations. The TALU retrieves the data stored in registers within the processor and performs the required operations on them. The TALU then stores the result back in the appropriate register. A computer's ALU is responsible for executing instructions and performing calculations essential to its operation. It is used in conjunction with the control unit to run the program's instructions. Without an ALU, a processor cannot perform arithmetic and logical operations, which are required for a variety of tasks, including mathematical calculations, data processing, and decision-making. Overall, the TALU plays a crucial role in the operation of a Ternary Processor and is a key factor in determining its performance capabilities.

In this chapter, we propose a new design for a TALU that is simpler in terms of area,

number of CNFETs used for design, power, and PDP (Power-Delay-Product) metrics as compared to existing TALU designs. The proposed design uses a 2:1 multiplexer based design approach for implementing the arithmetic circuits making the design energy efficient.

## 3.2 Existing Designs for TALU

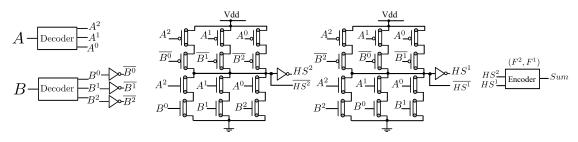

A 2-digit ALU implementation for ternary logic using CMOS technology is presented in [47]. The block diagram of the TALU consists of four main components- decoders, function select logic, transmission gates, and function processing modules. Figure 3.1 shows the architecture of a 2-digit TALU as given in [48]. This architecture is similar in all the three existing TALU designs in [47], [48], and [11]. As shown in Figure 3.1, the 2-digit binary inputs A, B, are first converted to binary form using decoders. These decoded inputs are given to the functional modules via a Transmission gate (TG) block. Each TG block is activated, depending on the values of the select lines  $S_0, S_1$ , and the inputs are connected to the corresponding functional module. This 2-digit TALU performs four arithmetic and five logic operations.

The TALU architecture shown in Figure 3.1, takes two 2-digit inputs  $A_1A_0$  and  $B_1B_0$ . Each digit/bit is represented by,  $A_i$ , where  $A_0$  represents  $0^{th}$  bit,  $A_1$  represents  $1^{st}$  bit, and so on,  $A_i$ , represents the  $i^{th}$  bit of the number A. The 4 input digits  $(A_1, A_0, B_1, B_0)$  are decoded to 3 digit outputs each by the input decoders. A ternary decoder, for an input X gives an output  $X^k$ , is defined as:

$$X^{k} = \begin{cases} 2, & if X = k \\ 0, & if X \neq k \end{cases}$$

$$(3.1)$$

So, a 12-digit wide input in the decoded form goes to the arithmetic modules like adder-subtractor, multiplier, comparator and XOR module via a TG block that has 12 TGs (one TG for each of the 12 inputs). The use of decoders and large TG blocks makes this design complex in terms of number of CNFETs required to build the

design. The logical modules in Figure 3.1, perform operations on only single digits that require only 2 TGs in the TG block. Each of the functional modules in this design is implemented using a decoder-encoder based design approach which contributes to power consumption.