# Compiler Assisted Parallelization and Optimization for Multicore Architecture

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

by

#### **D.C.KIRAN**

Under the Supervision of

Prof. S. GURUNARAYANAN

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN) INDIA 2014

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN)

### **CERTIFICATE**

This is to certify that the thesis entitled "Compiler Assisted Parallelization and Optimization for Multicore Architecture" submitted by D. C. Kiran ID. No. 2007PHXF013P for award of Ph.D. Degree of the Institute, embodies original work done by him under my supervision.

(Signature of the supervisor)

Prof. S Gurunarayanan

Professor

Date:

Department of Electrical Electronics and Instrumentation Engineering

Dean Work Integrated Learning Programmes Division

Birla Institute of Technology and Science-Pilani

Pilani – 333 031 (Rajasthan) INDIA

# **Dedication**

To my father Channaiah and mother Sulochana who believed and allowed me to achieve whatever I thought in my life.

#### Acknowledgements

Thanking my god who kept his promise by being with me throughout my research expedition, I would like to acknowledge the efforts of my supervisor Prof. S. Gurunarayanan who has been more to me than just an adviser in technical matters. A friend, a mentor, and a guide for life, he gave me the flexibility to pursue whatever I felt was appropriate, provided me with continuous guidance even beyond his areas of interest to help me work efficiently and remain focused, and gave me the ability to form a vision.

I am very thankful to Prof Janardan Prasad Misra who stepped in at the right time to work with me, and without his continuous encouragement, inspiring dedication, and organized approach to research, I couldn't have completed this thesis. He is the most sincere teacher and guide I have come across, and I consider myself extremely lucky to have gotten his attention.

Special gratitude to Prof Sudeept Mohan, the ACO course for which I was attached with him gave me a deep understanding of processor design. He has also been kind to provide useful suggestion and feedback on all part of my work.

I would like to thank Prof. B. N. Jain, Vice Chancellor, Prof. G. Raghurama, Director, Prof. S K Verma, Dean, Academic Research Division, Prof Rahul Banerjee, Head of Department, Computer Science & Information Systems, Birla Institute of Technology and Science, Pilani (BITS-Pilani), (Raj.), for giving me an opportunity for PhD program.

Further, I sincerely acknowledge the encouragement and help received from Prof Shanmuga Sundar Balasubramaniam and Prof. Navneet Goyal, at various stages of the work.

My wife N. Mehala with whom I closely shared much of my experience, especially as PhD student, the contradictions, the disappointments at innumerable paper rejections, the sporadic joyous moments at papers acceptances, probably she is the only one who understands what made this road really long, and gave me company all along.

To my son Mano Srijan who missed many stories when I worked till late night.

Over the last almost-nine enriching years at BITS Pilani, so many other people and things have been a part of this experience as well, that it is hard to choose and name only a few.

My colleagues in department and friends and the time we spent together will forever remain precious to me.

#### Abstract

# Compiler Assisted Parallelization and Optimization for Multicore Architecture

Continuous improvement of VLSI technology coupled with need for faster processing capability has led to several innovations in the field of computer architecture resulting in development of multicore processors. A multicore processor has multiple processor cores on a single chip. Each individual core has separate register file and is capable of executing complete ISA (Instruction Set Architecture). In order to exploit the computing capabilities of multicore processors, significant amount of research in the area of code parallelization and multiprocessing has been carried out. An application running on a multicore system does not guarantee the performance improvement until the application has been explicitly designed to take advantage of multicore processor. To develop an application that exploits computing capabilities of multicore, two approaches are followed. The first approach is to develop an explicitly parallel code that can be scheduled on multiple cores of a given processor and the other approach is using a compiler to extract fine grained parallelism by identifying the sets of instructions that can be executed in parallel. Current focus by researcher and programming language developers is to exploit coarse grain thread and data-level parallelism. There is very little effort from the research community toward the exploitation of compiler driven fine grained parallelism of a sequential program.

The multicore processors can be made to exploit fine grained parallelism of a given code by exposing the low level architectural details to the compiler and operating systems. Several multicore architectures are proposed and are being designed such that it supports the minimal set of operations required for executing an instruction, and other tasks including extracting the fine grained parallelism are left for compilers and run time environment. The runtime environment can manage resource allocation, extracting

parallel constructs for different cores, and scheduling based on information generated by the compiler.

The challenge in achieving a performance gain from fine-grain parallelism is identification of the fine grained thread from a given single threaded application and scheduling these threads on different cores of the multicore processor.

To avoid the congestion on small shared register file as in other parallel architectures, the memory hierarchy of multicore architecture generally has private register files. The fine grained threads that are scheduled on to different cores need to be allocated registers from respective register file of the core on which they are scheduled.

To effectively utilize the potential benefits of the multi-core processor, the thesis focuses on improving performance through automated fine-grain parallelization, where a sequential program is split into parallel fine grained threads and are scheduled on to multiple cores. It is also proposed to develop register allocation strategy for fine grained threads which are scheduled on multicore processor. The register allocation is performed by considering individual register files of each core of multicore processor.

This thesis modifies the flow of current compiler by splitting the sequential program to create fine grained threads, proposes five scheduling heuristics (1 local and 4 global), and register allocating heuristics for fine grained threads which are scheduled on multiple cores. The work is evaluated using speed-up, power consumption, performance per power, communication cost, and spilling as metrics. The RAW benchmark suite is used to compare the results.

# **Table of Contents**

| List of Tables                                       | xi  |

|------------------------------------------------------|-----|

| List of Figures                                      | xii |

| List of Abbreviations                                | xv  |

| Chapter 01 Introduction                              | 17  |

| 1.1 Challenges In Multicore Environment              | 19  |

| Parallelizing The Sequential Program                 | 19  |

| Memory Management and Data Communication             | 19  |

| Register Allocation                                  | 19  |

| Memory Bandwidth                                     | 20  |

| Locality of References                               | 20  |

| Memory Contention                                    | 20  |

| Scalability                                          | 21  |

| Power Consumption                                    | 21  |

| 1.2 State Of Art of Exploiting Parallelism           | 24  |

| 1.2 Objectives and Contributions                     | 25  |

| 1.4 Organization of Thesis                           | 26  |

| Chapter 02 Literature Survey                         | 28  |

| 2.1 Parallel Architectures, ILP & Compiler           | 28  |

| 2.2 Background Of Instruction Scheduling             | 31  |

| 2.3 Scheduler Requirement for Multicore Architecture | 35  |

| 2.4 Survey On Register Allocation                    | 37  |

| 2.5 Recent Developments                              | 42  |

| 2.5 Conclusion                                       | 46  |

| Chapter 03 Experimental Framework                    | 47  |

| 3.1 Multicore Architecture                           | 47  |

| 3.2 Compiler                                         | 48  |

| 3.3 Benchmarks                                       | 51  |

| 3.2 Experimental Evaluation                                             | 52 |

|-------------------------------------------------------------------------|----|

| Chapter 04 Compiler Optimization and Support for Multicore Architecture | 54 |

| 4.1 Fine Grain Thread Extractor                                         | 55 |

| 4.2 Scheduling.                                                         | 58 |

| 4.2.1 General Criteria To Create Schedule                               | 59 |

| 4.2.2 Sequential Program Execution and Its Analysis                     | 61 |

| 4.2.3 Power Optimization                                                | 62 |

| 4.3 Register Allocation                                                 | 63 |

| Chapter 05 Fine Grain Thread Extractor                                  | 67 |

| 5.1 Creating Disjoint Sub-blocks                                        | 67 |

| 5.1.1 Approach 1 To Create Disjoint Sub-blocks                          | 67 |

| 5.1.2 Approach 2 To Create Disjoint Sub-blocks                          | 69 |

| 5.2 Sub-block Dependency Graph (SDG)                                    | 71 |

| 5.2.1 Approach 1 To Create SDG                                          | 71 |

| 5.2.2 Approach 2 To Create SDG                                          | 72 |

| 5.3 Compiler Time Analysis of Approach 1 and Approach 2                 | 74 |

| Chapter 06 Intra Block Scheduling                                       | 77 |

| 6.1 Introduction to Intra Block Scheduling                              | 77 |

| 6.1.1 Sub-block Merging                                                 | 78 |

| 6.1.2 Intra Block Scheduler                                             | 81 |

| 6.2 Results                                                             | 82 |

| Chapter 07 Inter Block Scheduling                                       | 86 |

| 7.1 Height Instruction Count Based Scheduler                            | 87 |

| 7.2 Dependent Sub-block Based Scheduler                                 | 87 |

| 7.3 Maximum Dependent Sub-block Based Scheduler                         | 88 |

| 7.4 Longest Latency Sub-block Based Scheduler                           | 89 |

| 7.5 Results                                                             | 89 |

| 7.5.1 Discussion                                                        | 94 |

| 7.6 Conclusion                                                          | 97 |

| Chapter 08 Register Allocation for Multicore Processors       | 99  |

|---------------------------------------------------------------|-----|

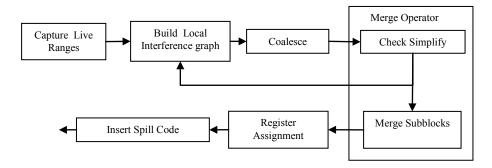

| 8.1 Integrated Scheduling and Register Allocation             | 100 |

| 8.2 Global Register Allocation                                | 102 |

| 8.2.1 Merge Operator                                          | 103 |

| 8.2.2 Observation on Number of Registers                      | 104 |

| 8.2.3 Capturing Live Variables                                | 105 |

| 8.2.4 Register Assignment                                     | 105 |

| 8.2.5 Insert Spill Code                                       | 105 |

| 8.3 Algorithm Complexity Analysis                             | 106 |

| 8.4 Results                                                   | 106 |

| 8.5 Conclusion                                                | 109 |

| Chapter 09 Achievements, Limitations, Future Work and Summary | 110 |

| 9.1 Summery of Achievement                                    | 110 |

| 9.2 Limitations                                               | 111 |

| 9.3 Future Work                                               | 112 |

| 9.4 Summary                                                   | 112 |

| Appendix A More Results on Scalability                        | 115 |

| Appendix B Preliminaries and Definitions of JackCC Compiler   | 120 |

| List of References                                            | 137 |

| List of Publication by Author                                 | 146 |

| Biography of the Candidate                                    | 149 |

| Biography of the Supervisor                                   | 149 |

# **List of Tables**

| Table I:    | Power Consumption Comparison                                 | 22  |

|-------------|--------------------------------------------------------------|-----|

| Table II:   | Scheduling Techniques For Parallel Architectures             | 33  |

| Table III:  | Comparison Of Register Allocation Approaches                 | 38  |

| Table IV:   | Pros and Cons of Various Register Allocation Approaches      | 40  |

| Table V:    | Recent Development in the Area of Multicore                  | 42  |

| Table VI:   | Raw Benchmark Suite                                          | 51  |

| Table VII:  | List of Sub-blocks Generated by MDS Scheduler                | 58  |

| Table VIII: | (a) Sub-block List Generated for Dual Core Processor         |     |

|             | (b) Hyper Sub-blocks Whose Interference Graph is K Colorable | 65  |

| Table IX:   | Sub-blocks                                                   | 65  |

| Table X:    | Number of Basic Blocks and Sub-block for the Test Cases      | 71  |

| Table XI:   | Algorithm Complexity Comparison                              |     |

|             | of Different Register Allocation Heuristics                  | 107 |

| Table XII:  | Spill Comparison of Different Register Allocation Heuristics | 107 |

| Table XIII: | Communication Cost of Intra Block, Inter Block               |     |

|             | and Integrated Schedulers.                                   | 107 |

| Table XIV:  | Files in JackCC                                              | 120 |

| Table XV:   | Supporting Files in JackCC                                   | 121 |

| Table XV:   | Abstract Data Types in Jackcc and Corresponding Files        | 121 |

| Table XVII: | Instructions Used to Generate Assembly Code by Jackcc        | 122 |

# **List of Figures**

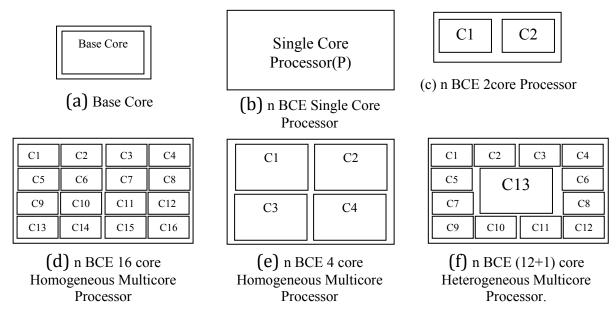

| Figure 1:  | N Base Core Equivalent Processors                                            | 18 |

|------------|------------------------------------------------------------------------------|----|

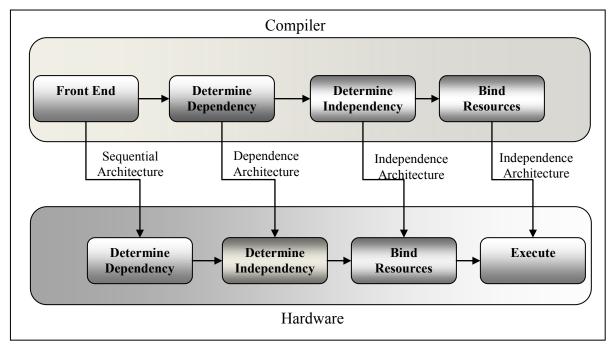

| Figure 2:  | Compiler vs Hardware Support for Exploiting ILP                              | 30 |

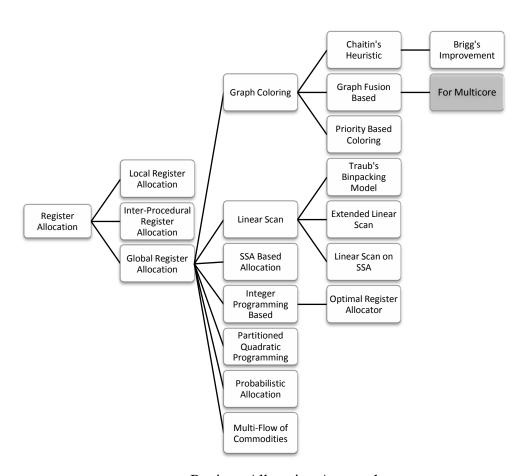

| Figure 3:  | Register Allocation Approaches                                               | 35 |

| Figure 4:  | Compiler Generated Code and Their Relation with                              |    |

|            | Architecture(Core/Processor)                                                 | 48 |

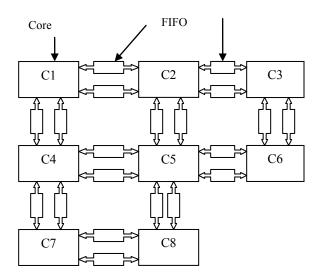

| Figure 5:  | On-chip Multiprocessors (Core) Interconnections                              | 48 |

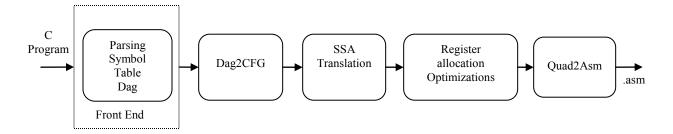

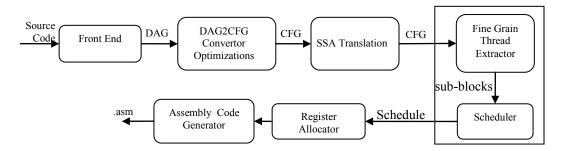

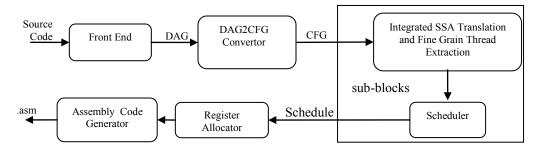

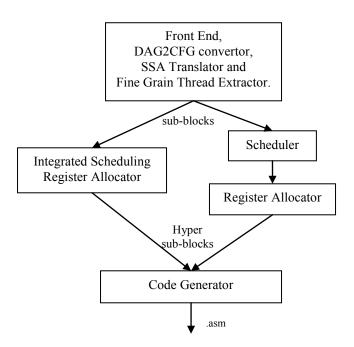

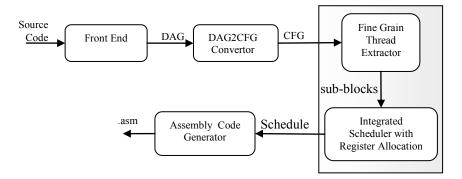

| Figure 6:  | Original Flow of Compiler                                                    | 49 |

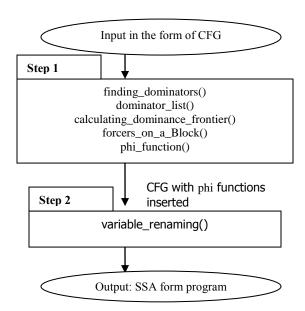

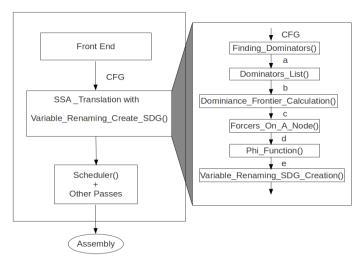

| Figure 7:  | Sequence of Functional Call in Compiler to Generate SSA form Program         | 49 |

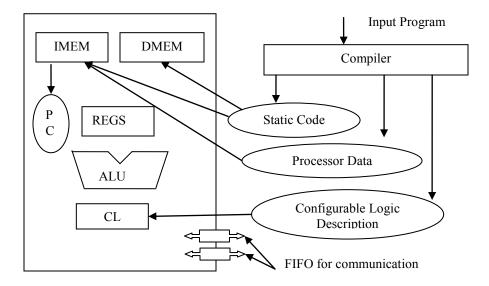

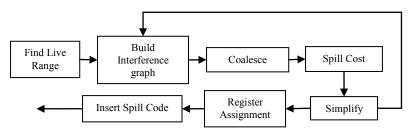

| Figure 8:  | Register Allocation Framework                                                | 50 |

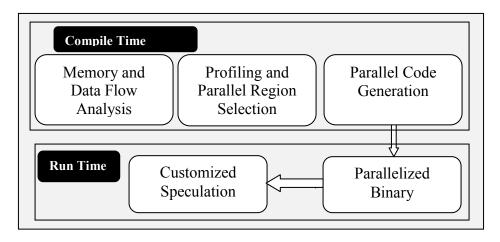

| Figure 9:  | Run Time Support                                                             | 51 |

| Figure 10: | Modified Flow of Compiler to Create Disjoint Sub-block And                   |    |

|            | to Perform Scheduling                                                        | 54 |

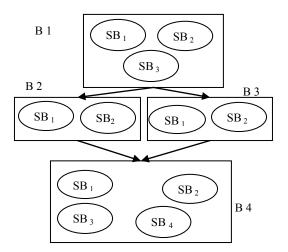

| Figure 11: | Control Flow Graph With Basic Block B <sub>p</sub> Sub-block SB <sub>i</sub> | 55 |

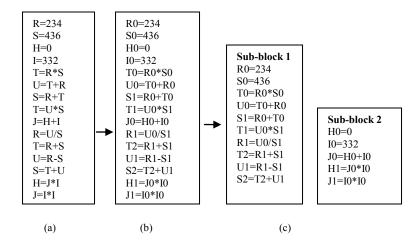

| Figure 12: | (a) Non SSA Program (b) SSA Form Program                                     |    |

|            | (c) Disjoint Sub-blocks                                                      | 56 |

| Figure 13: | (a) Sub-block Dependency Graph                                               |    |

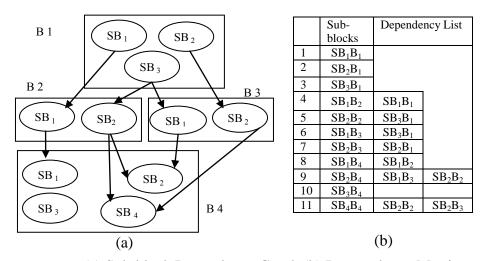

|            | (b) Dependency Matrix                                                        | 57 |

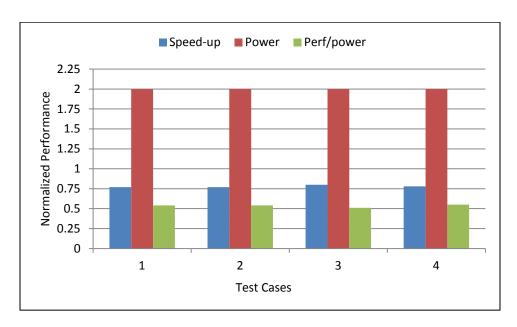

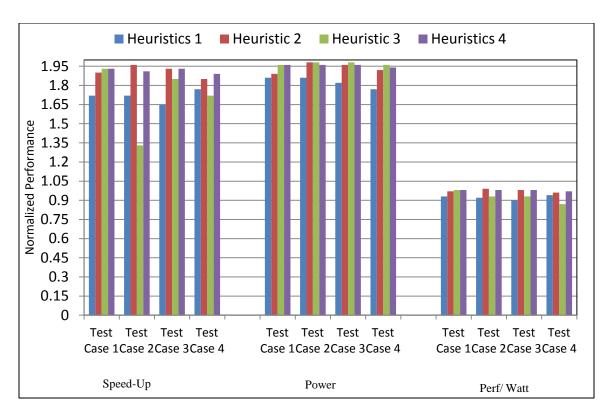

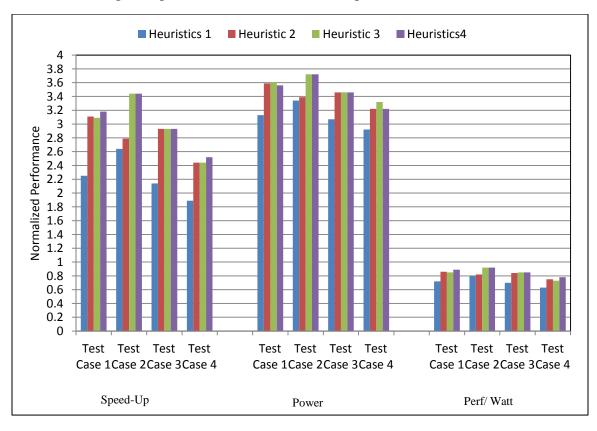

| Figure 14: | Results of Testcases Compiled by Original Jackcc                             |    |

|            | for Dual Core Processor                                                      | 61 |

| Figure 15: | Results of Testcases Compiled by Original Jackcc                             |    |

|            | for Dual Core Processor                                                      | 62 |

| Figure 16: | Power Optimization                                                           | 63 |

| Figure 17: | Modified Register Allocation Framework                                       | 64 |

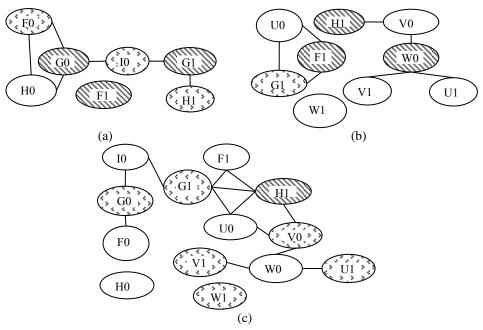

| Figure 18: | ( (a) Interference Graph of Sub-block $SB_2B_1$             |    |

|------------|-------------------------------------------------------------|----|

|            | (b) Interference Graph of Sub-block SB <sub>2</sub> B3      |    |

|            | (c) Interference Graph of Merged Sub-blocks                 | 66 |

| Figure 19: | Steps in Creating Disjoint Sub-blocks                       | 69 |

| Figure 20: | Integrated SSA Translation and Fine Grain Thread Extraction | 69 |

| Figure 21: | Modified Flow of Compiler to Create Disjoint Sub-blocks     |    |

|            | and SDG During SSA Creation                                 | 74 |

| Figure 22: | Example Sub-blocks of Basic Block B <sub>p</sub>            | 80 |

| Figure 23: | Steps In Merging Sub-blocks of Basic Block                  | 80 |

| Figure 24: | Schedules Created by Intra Block Scheduler                  | 82 |

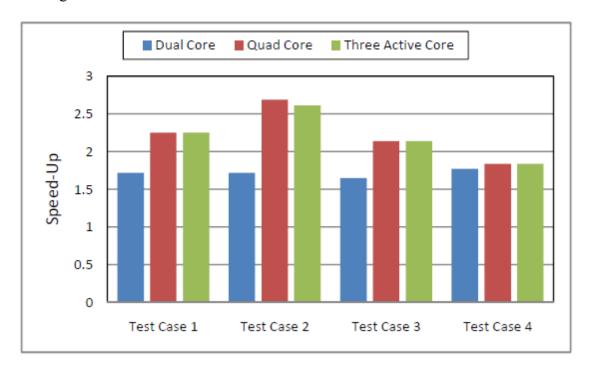

| Figure 25: | Speed-up Analysis For Intra Blocks Scheduling               | 83 |

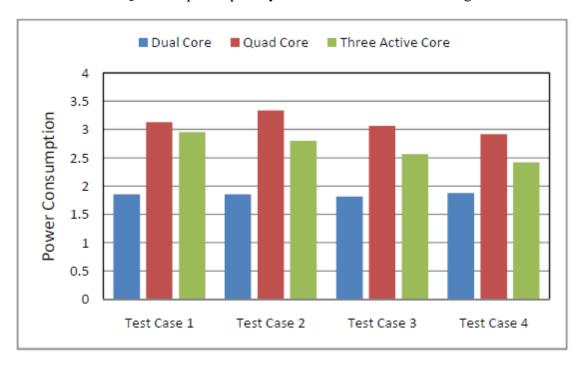

| Figure 26: | Power Analysis For Intra Blocks Scheduling                  | 83 |

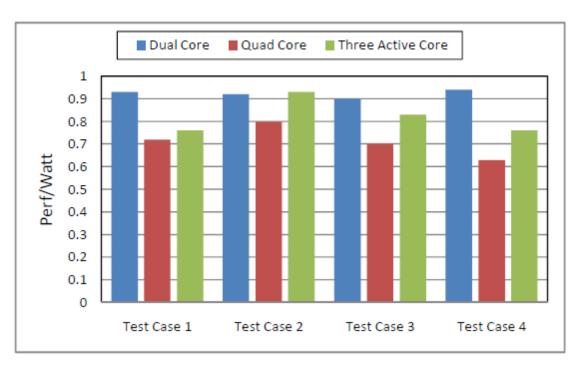

| Figure 27: | Performance Per Power Analysis For Intra Blocks Scheduling  | 84 |

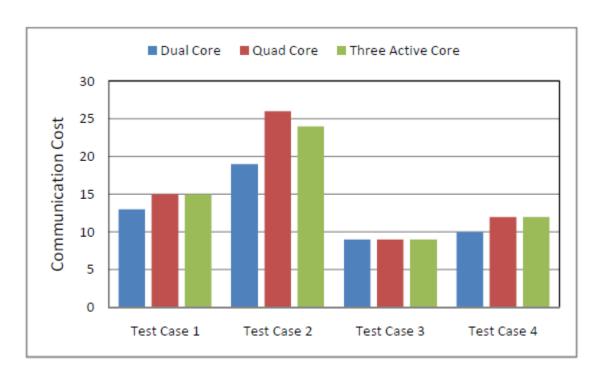

| Figure 28: | Communication Cost For Intra Blocks Scheduling              | 84 |

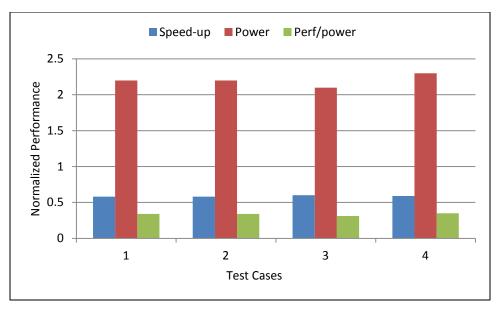

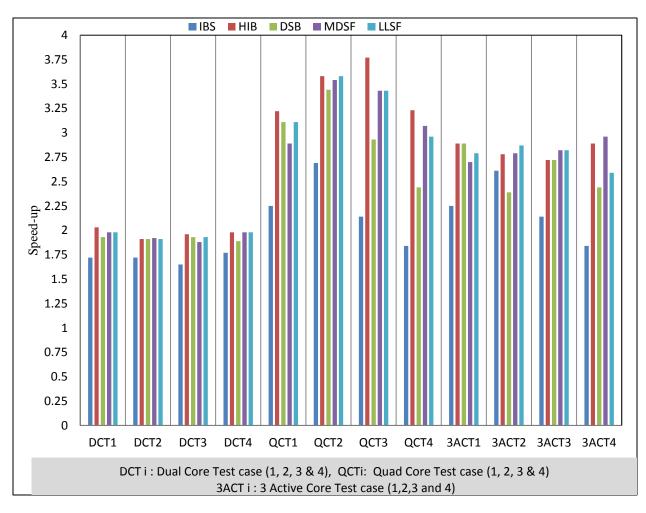

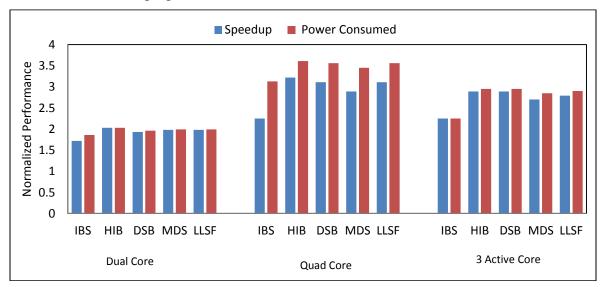

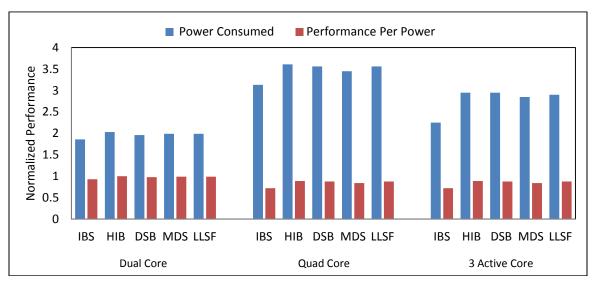

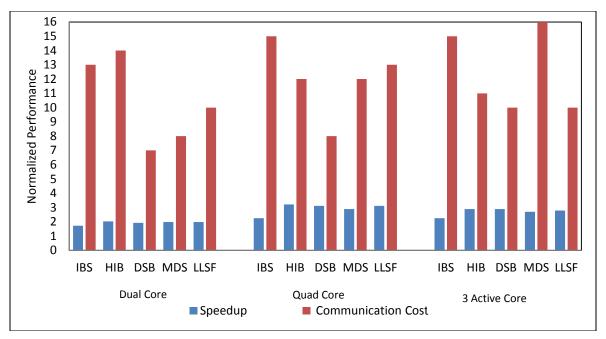

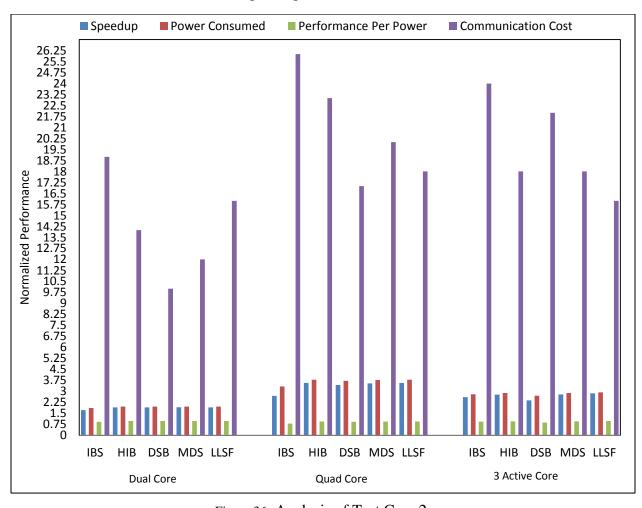

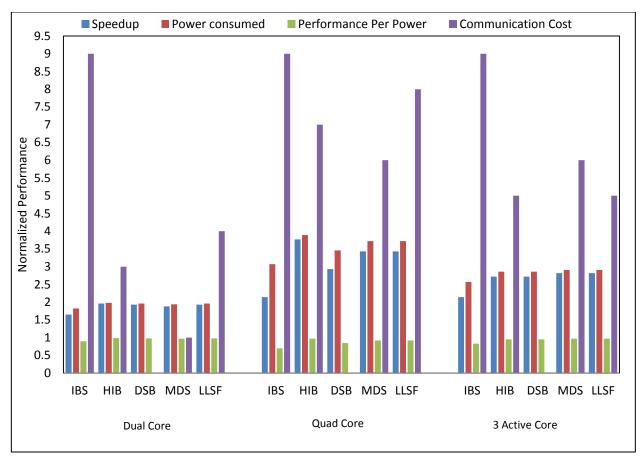

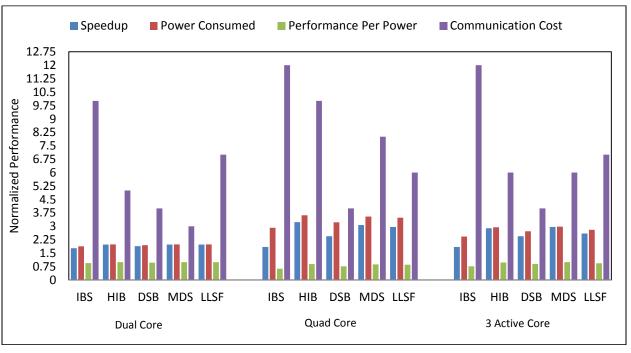

| Figure 29: | Speed-up Analysis For Inter Blocks Schedulers               | 91 |

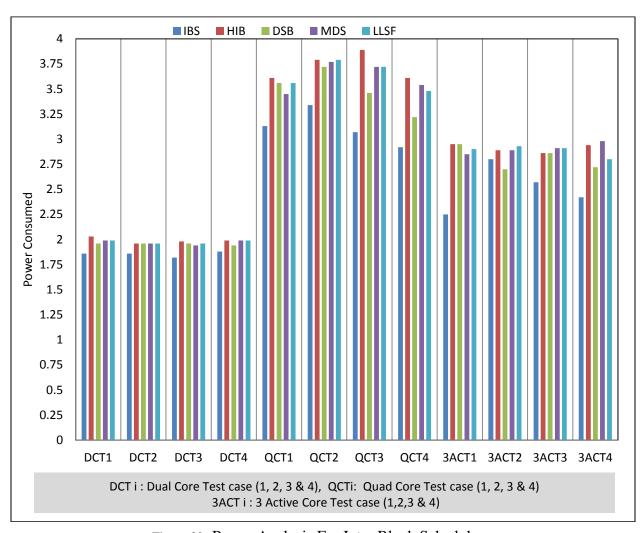

| Figure 30: | Power Analysis For Inter Blocks Schedulers                  | 92 |

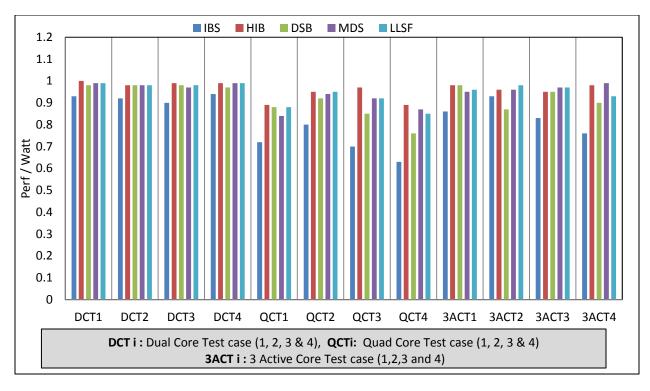

| Figure 31: | Performance Per Power Analysis For Inter Blocks Schedulers  | 93 |

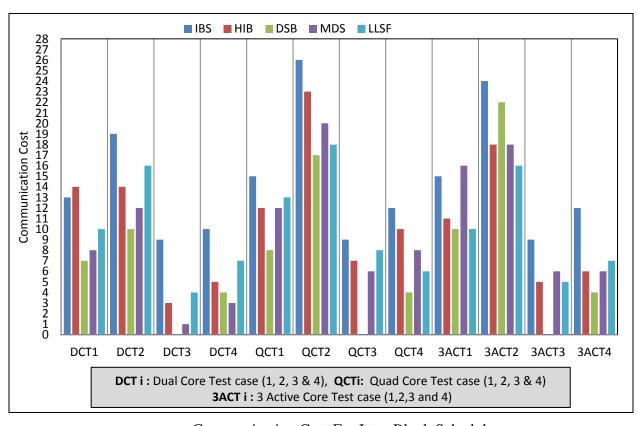

| Figure 32: | Communication Cost For Inter Blocks Schedulers              | 93 |

| Figure 33: | Speed-up vs Power Consumed                                  | 94 |

| Figure 34: | Power Vs Performance per Power                              | 94 |

| Figure 35: | Speed-up vs Communication Cost                              | 95 |

| Figure 36: | Analysis Of Test Case 2                                     | 95 |

| Figure 37: | Analysis Of Test Case 3                                     | 95 |

| Figure 38: | Analysis Of Test Case 4                                     | 96 |

| Figure 39: | Proposed Register Allocation Heuristics                     | 99 |

| Figure 40: | Modified Flow of Compiler to Integrate Scheduler and Register  Allocation |

|------------|---------------------------------------------------------------------------|

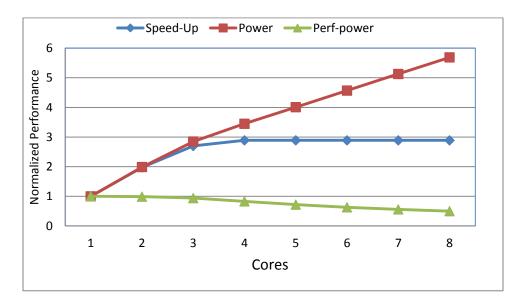

| Figure 41: | Speed-up, Power and Perf/power Comparison on Dual Core108                 |

| Figure 42: | Speed-up, Power and Perf/power Comparison on Quad Core108                 |

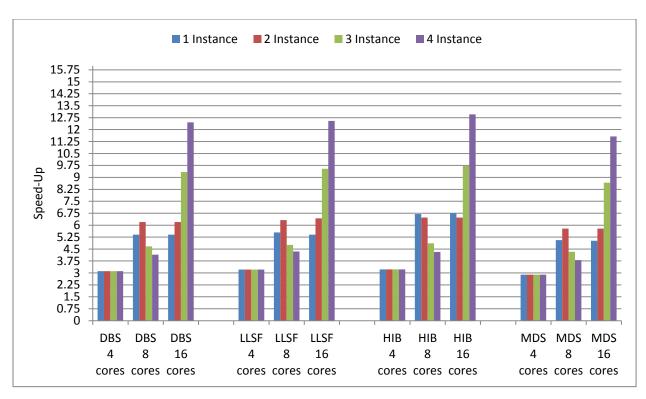

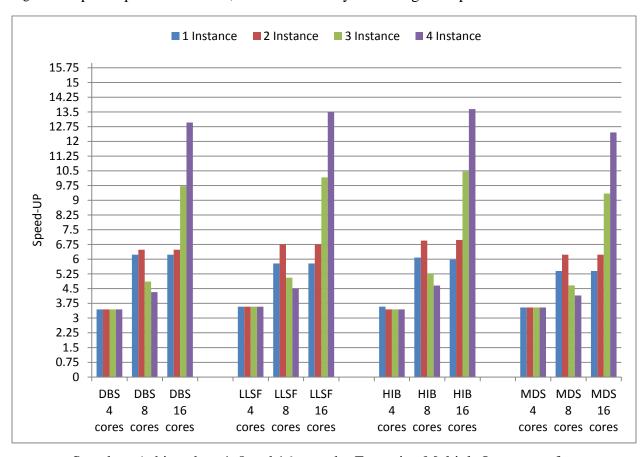

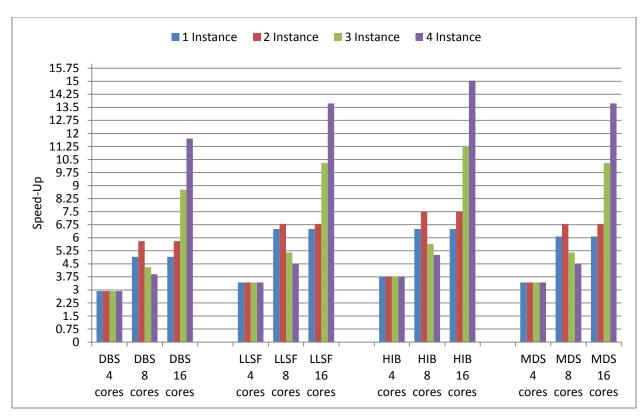

| Figure 43: | Speed up Achieved on 4,8,16 cores by Executing Multiple                   |

|            | Instances of Test Case 1                                                  |

| Figure 44: | Speed up Achieved on 4,8,16 cores by Executing Multiple                   |

|            | Instances of Test Case 2                                                  |

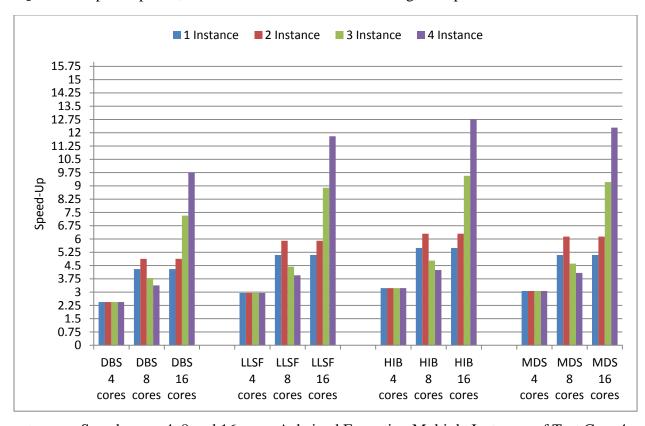

| Figure 45: | Speed up Achieved on 4,8,16 cores by Executing Multiple                   |

|            | Instances of Test Case 3                                                  |

| Figure 46: | Speed up Achieved on 4,8,16 cores by Executing Multiple                   |

|            | Instances of Test Case 4                                                  |

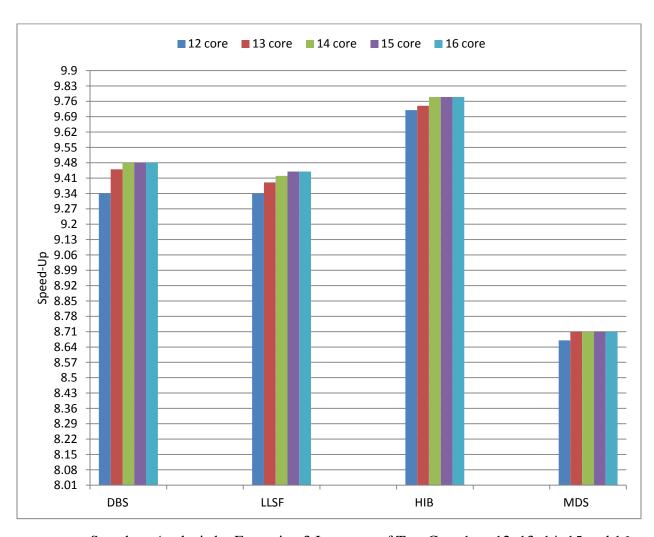

| Figure 47: | Speed-up Analysis by Executing 3 Instances of Test Case 1                 |

|            | on 12, 13, 14, 15 and 16 core for Power Optimization118                   |

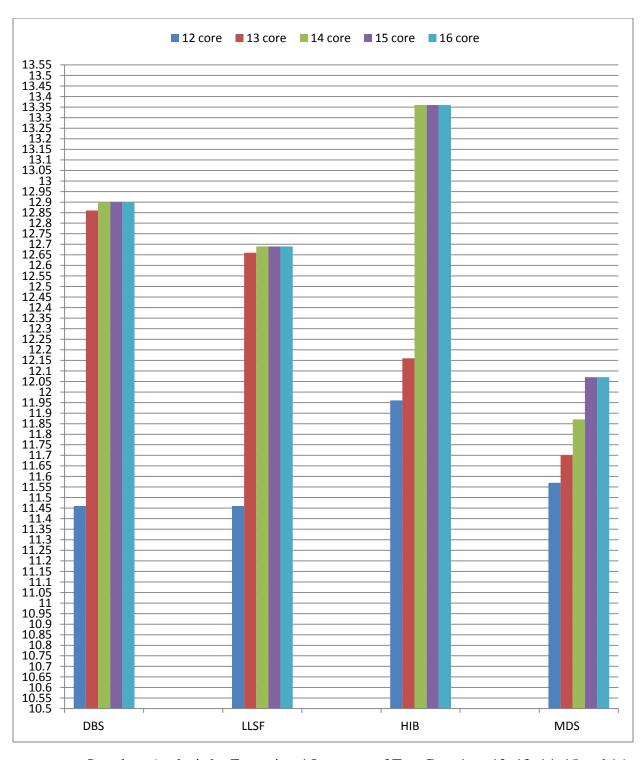

| Figure 48: | Speed-up Analysis by Executing 4 Instances of Test Case 1                 |

|            | on 12, 13, 14, 15 and 16 core for Power Optimization119                   |

# **List of Abbreviations**

| Abbreviation                                 | Details or Expanded Form                                                                      |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| ISA                                          | Instruction Set Architecture                                                                  |  |  |

| BCE                                          | Base Core Equivalent                                                                          |  |  |

| ILP                                          | Instruction Level Parallelism                                                                 |  |  |

| DAG                                          | Directed Acyclic Graph                                                                        |  |  |

| CFG                                          | Control Glow Graph                                                                            |  |  |

| QUAD                                         | Three address code format of instruction                                                      |  |  |

| ARENA                                        | Name of structure of Basic Block of CFG                                                       |  |  |

| SSA                                          | Static Single Assignment                                                                      |  |  |

| SAME                                         | A function used to identify copy related instructions                                         |  |  |

| Phi (φ)                                      | A data structure which stores the information of copy related instructions.                   |  |  |

| DSB                                          | Dependent Sub-block First Scheduler                                                           |  |  |

| MDS                                          | Most Dependent Sub-block First Scheduler                                                      |  |  |

| LLSF                                         | Least Latency Sub-block First Scheduler                                                       |  |  |

| HIB                                          | Height Based Scheduler                                                                        |  |  |

| IBS                                          | Intra Block Scheduler                                                                         |  |  |

| IRS                                          | Integrated Register Allocation and Scheduling                                                 |  |  |

| $SB_i$                                       | i <sup>th</sup> Sub-block                                                                     |  |  |

| $B_p$                                        | p <sup>th</sup> Basic block                                                                   |  |  |

| $\mathrm{SB_{i}B_{p}}$                       | i <sup>th</sup> Sub-block in p <sup>th</sup> Basic block                                      |  |  |

| $Perf_m(r), Perf_s(r), Perf_d(r), Perf_q(r)$ | Performance on multicore, single core, dual core, and quad core processor respectively.       |  |  |

| $Pw_m(r), Pw_s(r), Pw_d(r), Pw_q(r)$         | Power consumed by multicore, single core, dual core, and quad core processor respectively.    |  |  |

| Pfi                                          | Power consumed by cores of powerful multicore processor in idle state                         |  |  |

| Plí                                          | Power consumed by cores of less efficient multicore processor in idle state                   |  |  |

| Pa                                           | Extra power consumed by dual core processor to execute non-parallelized program               |  |  |

| Pa                                           | Extra power consumed by quad core processor to execute non-<br>parallelized program           |  |  |

| $W_c$                                        | Total power consumed by a core in multicore processor to execute non-<br>parallelized program |  |  |

| Abbreviation            | Details or Expanded Form                                       |

|-------------------------|----------------------------------------------------------------|

| TRdy                    | Ready Time                                                     |

| TFns                    | Finish Time                                                    |

| TSct                    | Schedule Time of Core                                          |

| TSch                    | Schedule Time of Sub-block                                     |

| Height <sub>i</sub>     | Height of i <sup>th</sup> sub-block                            |

| $L_i$                   | Latency i <sup>th</sup> sub-block                              |

| $C_{i}$                 | Total Cycle time required by i <sup>th</sup> sub-block         |

| TIc                     | Total Instruction Count                                        |

| Rreq i                  | Register Required by i <sup>th</sup> sub-block                 |

| $\mathrm{HSB_{j}B_{P}}$ | j <sup>th</sup> Hyper sub-block of p <sup>th</sup> basic block |

| Ravl <sub>j</sub>       | Register available in j <sup>th</sup> hyper sub-block          |

# CHAPTER 01

Introduction

Coupled with technological advancement in the field of computer architecture and relentless demand for faster processing has led to development of several innovative technologies and products. Semiconductor industry had kept pace with Moore's law in terms of doubling the number of transistor on a chip and increased clock speed [1]. R. Dennard, et al., in 1974 proposed that with scaling ratio of  $1/\sqrt{2}$ , the transistors count will double on a chip and clock frequency can be increased by 40% keeping the power consumption constant [2][3]. But with current feature size, the Dennard's law does not hold true any longer [4]. The continuous increase in number of transistor and clock speed has thrown design challenges for handling larger amount of heat dissipation. The power dissipation and thermal issues severely restricts the ability to continuously increase operating clock frequency of a processor [5][6]. This has led to development of homogeneous multicore architecture. A multicore chip supports multiple processor core on a single chip. The idea was to replace power hungry powerful processor with less powerful multiple cores [7][8]. Such developments lead to greater focus on exploiting the explicit parallelism by executing multi threaded applications or multiple tasks on multiple processor core to gain performance [9]. Since the approach tries to exploit explicit parallelism, the processor cores can be operated at lower clock frequency to achieve the same or better performance as compared to single core processor operating at higher frequency thus solving the heat dissipation problem.

The cores on a chip can be homogeneous or heterogeneous [10]. In case of homogeneous multicore processor chip, each core is equally capable and therefore allows any thread to execute on any core. Figure 1 provides an overview of the most common design of on chip multiprocessors used in today's system. Figure 1.c, Figure 1.d and Figure 1.e, depict homogeneous multicore processors and Figure 1.f is an example of heterogeneous multicore processor. A homogeneous architecture is undoubtedly easier to program for parallelism, because a program can make use of the all cores than in a heterogeneous architecture where all the cores do not support the same instruction set.

Figure 1. n Base Core Equivalent Processors

The design philosophy of multicore processor says that the cores on chip should be resource equivalent and power equivalent [11]. The Base Core in Figure 1.a, is a unit core made up of some r resources and consume some power to achieve some performance. A n BCE (base core equivalent) processor P is made up of r times the resources used for base core and consume k power budget to get the performance Perf(r). To build a n BCE processor r and k should be shared equally. If r of a single core is increased, sequential performance is increased. If r is distributed among multiple execution units, parallel performance is increased. So in multicore processor r resources are distributed to achieve n BCE processor. A homogeneous multicore processor can have n/r cores to have n BCE processor. For example, a single core processor with capability of 16 BCE (1\*16 BCE) or a homogeneous multicore processor with 4 4BCE cores (4\*4 BCE) are equivalent. Similarly, heterogeneous multicore processor 12\*1 BCE + 1\*4 BCE processor is equivalent to 16 BCE in terms of resources and power consumption.

The performance increases as number of cores increases, that is,  $Perf_q(r) > Perf_d(r) > Perf_s(r)$ . Where  $Perf_s(r)$ ,  $Perf_d(r)$  &  $Perf_q(r)$  are performance of single core, dual core and quad core processors respectively. Ideally,  $Perf_d(r)$  is  $2*Perf_s(r)$  and  $Perf_q(r)$  is  $4*Perf_s(r)$ . But according to Amdahl's law [12], performance (Pref) from N number of cores depends on a fraction  $f(0 \le f \le 1)$  of computation that can be parallelized. The fraction f is also responsible for increase in power consumption. The challenge of multicore programming involves making the

fraction f equal or closer to 1. The challenges and issues associated with the multicore environment are discussed in next section.

#### 1.1 Challenges In Multicore Environment

#### i. Parallelizing the Sequential Program

Though multicore technology offers clear benefits against the single core processor, the general understanding of researchers is that finding an effective way to exploit the parallelism or concurrency inherent in an application is one of the most daunting challenges. The multicore processors are general extension of shared memory multiprocessors whose computation power can be utilized effectively only by the applications with coarse grain threads. These designs provide real benefits for server-class applications that are explicitly multi-threaded. However, for desktop and other systems where single-thread applications dominate, multicore systems are yet to offer much benefit. There is a mismatch with current multicore hardware and applications, as most of the applications are single threaded and are unable to exploit the fine grained parallelism offered by multicore processors. To fully exploit the architectural capability and inherent fine grained parallelism of an application, it is desired to have parallel code. Writing parallel code is a tedious and requires expertise. Most of the features provided by explicit programming languages concentrate on parallelizing loops or iterative statements. It is essential to develop or convert existing sequential codes to parallel implementations. The support from compilers and run-time systems for the development of parallel application for multicore is vital.

#### ii. Memory Management and Data Communication

Memory hierarchy of multicore architecture generally has shared memory, second level shared cache, first level private cache, and private register files [13]. Issues related to memory can be classified as follows,

#### • Register allocation

To avoid the congestion on small shared register file as in other parallel architecture (Pipelined, VLIW), the memory hierarchy of multicore architecture generally has private register files. The threads that are scheduled on to different cores need to be allocated registers from respective register file of the core on which they are scheduled.

#### • Memory bandwidth

Memory bandwidth remains the bottleneck on multicore platform, although computing is cheap since there are many processing cores [14]. The existence of the memory bandwidth bottleneck is because of the use of shared bus by all CPU cores. Efficient memory management is very critical for a scalable application on multicore CPU.

#### • Locality of reference

In a multicore processor with non-uniform cache architectures with distributed cache banks, data access latency is a limiting factor to performance. To mitigate this effect, it is necessary to leverage the data access locality and choose an optimum data placement so that the volume of inter-core messages is minimized. This requires a study of data accesses behaviors among multiple cores.

#### • Memory Contention

Memory systems have been under a lot of pressure to keep up with the increasing demand for parallelism [15]. Memory Contention increases the need of synchronizing data among different cores, which has a big performance penalty because of bus traffic contention, locking cost and cache miss. Lock based synchronization has several limitations, including sensitivity to preemption and possibility of deadlock. A synchronization approach without lock is desirable. In multicore environment lock free synchronization is achieved using transactional memories. Regardless of which synchronization (lock based or non lock based synchronization) is used contention over shared data hamper the scalability.

The current cache hierarchy has been unable to support high level demand for parallelism. Existing architectures employ lock-up free caches to avoid stalling the CPU and allow the cache miss to be serviced in the background. The *Miss Information/Status Holding Register* (MSHR) Files are responsible for keeping track of the outstanding concurrent misses. These types of caches are very costly in terms of chip area and power usage. This limits the size of the MSHR file that can be included, even for today's large transistor budgets. For example, the L1 cache of an Intel Pentium 4 processor supports only eight outstanding misses.

#### iii. Scalability

Traditionally only super computers and high end servers needed major software scalability work, as they used many CPU sockets. The major scalability work was not needed in the low end computer systems as they had less CPU's. Scaling up the number of cores in multicore processors has provided a new dimension to scale up performance and requires extensive scalability work.

The factors which stop scalability are listed below.

- Programs may not inherently exhibit parallelism.

- Application program cannot scale up to meet the time bound constraints due to some physical constraints like memory. As number of cores increase, memory contention may increase leading to sequential access of data by deteriorating parallelism.

The expectation w.r.t increase in performance in multicore era is kept alive by the recent study on reevaluating Amdahl's law [16][17].

#### iv. Power Consumption

It was expected that the power consumption will remain same with the paradigm shift from single core to multicore processor, as the r resources used to design a n-BCE single core processor is distributed to design multicore processor with multiple slow cores (reduced clock speed). Though the slow cores of a multicore processor are energy efficient, the combined power consumption of cores is increased when used for parallel execution than sequential execution on single core processor to complete the task.

The fundamental reasons for increased power consumption are as follows.

- The core is less powerful (runs at reduced clock) than n BCE single core so it takes more time to execute thereby may consume more power.

- The second reason is due to Amdahl's law. According to Amdahl's law, the performance (Pref) from N of cores depend on fraction f (0≤f≤1) of computation that can be parallelized.

The power model proposed by Woo-Lee suggest [12] that if a program is executed on a single core processor the power consumption is  $Pw_s = 1$ . If the same program is executed on a multicore processor with n cores by parallelizing it 100% i.e., f=1 power

consumption should be n\*w<sub>c</sub> where w<sub>c</sub> is power consumed by slow core in multicore processor with n cores. But based on f and reduced strength (reduced clock) the power consumption of dual core processor should be  $(Pw_s \leq Pw_d \leq 2 \ Pw_s)$ . Similarly, when executed on quad core processor it is  $(Pw_s \leq Pw_d \leq 4 \ Pw_s)$ .

The power consumed by single core, dual core and quad core processor to execute the sequential and parallel version of the same program is summarized in Table 1. Let Pfi & Pli be the power consumed in idle state by powerful core & less efficient core respectively. Let Pa & Pa be the extra power consumed by the less efficient n-BCE dual core and n-BCE quad core processor respectively and  $w_c$  be the total power consumed by each core of less efficient n-BCE multicore processor.

TABLE I. POWER CONSUMPTION COMPARISON

|             |                                                                                            | Cores when fully utilized.                                    | When sequential program runs on single core keeping other cores idle. | Ideal power consumption When sequential program ( parallelized) runs on all the cores. | Time | Energy |

|-------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------|------|--------|

| Real        | Single core                                                                                | $Pw_s = 1 W$                                                  | $Pw_s = 1 W$                                                          | $Pw_s = 1 W$                                                                           | 5    | 5      |

| Theoretical | Dual core as powerful as single core                                                       | 2* Pw <sub>s</sub> =2 W                                       | 1 + Pfi <b>W</b>                                                      | 0.5+ 0.5<br>= 1 W                                                                      | 2.5  | 2.5    |

| Expected    | Dual core 50% less<br>powerful than single<br>core (Expected)<br>i.e. w <sub>c</sub> =0.5  | $2*(w_c) + 2 p_d$<br>= $1+2 p_d W$                            | $\mathbf{w}_{\mathrm{s}}$ + Plí $\mathbf{W}$                          | (2*w <sub>c</sub> ) W<br>= 1W                                                          | 2.5  | 2.5    |

| Real        | Dual core 30% less<br>powerful than single<br>core<br>i.e. w <sub>c</sub> =0.7             | $2*(w_c) + 2 p_d$<br>=1.4+ 2 p_d W                            | $w_s$ + Plí $W$                                                       | (2*w <sub>c</sub> ) W<br>= 1.4 W                                                       | 2.5  | 3.5    |

| Theoretical | Quad core as<br>powerful as single<br>core                                                 | 4* Pw <sub>s</sub> = 4 W                                      | 1 + 3 Pfi W                                                           | 0.25 + 0.25 + 0.25 + 0.25 + 0.25 $= 1  W$                                              | 1.25 | 1.25   |

| Expected    | Quad core 25% less<br>powerful than single<br>core (Expected)<br>i.e. w <sub>c</sub> = .25 | 4*( w <sub>c</sub> ) + 4 p <sub>q</sub> =1+4 p <sub>q</sub> W | $w_s + 3$ Plí $W$                                                     | 4*( w <sub>c</sub> )<br>= 1 W                                                          | 1.25 | 1.25   |

| Real        | Quad core 50% less<br>powerful than single<br>core<br>i.e. w <sub>c</sub> =.5              | $4*(w_c) + p_q$<br>= 2 + 4 $p_q$ W                            | $w_s + 3$ Plí $W$                                                     | (4*w <sub>c</sub> ) W<br>= 2 W                                                         | 1.25 | 2.5    |

The third column of the table depict the power consumed by different n BCE (single core, dual and quad core) processor to execute the sequential program. It can be observed that power consumption increases as the number of core is increased either by keeping r resources constant to create n-BCE multicore processor or by creating more than one n-BCE processor when all the cores are fully utilized.

The fourth column gives the amount of power consumed when a program is executed on multicore processor without parallelizing the program. The program is executed on a single core keeping other cores idle. If a non parallelized program (f=0) is executed on a multicore processor with n cores, only one core with r/n resources will execute the program while other (n-1) core will be idle consuming (n-1)\*z unit of power where z is fraction of power that a core consume in idle state  $(0 \le z \le 1)$  [4]. If it is assumed that a core in active state consumes a power of 1 unit, i.e., the amount of power consumed by one core during the sequential computation phase is 1 unit, while the remaining (n-1) cores consume (n-1)\*z units, during the sequential computation phase, the n core processor consumes 1 + (n-1)\*z units of power. In the parallel computation phase, n core processor consumes n units of power, because it takes (1-f) and f/n to execute the sequential and parallel code respectively.

In general, the power consumed by the dual core and quad core processor where each core is n-BCE core is  $Pw_s + Pfi$  unit of power and  $Pw_s + 3 Pfi$  unit of power respectively. The power consumed by the dual core and quad core n-BCE processor is  $w_s + Pli$  unit of power and  $w_s + 3Pli$  unit of power respectively where  $w_{s=} w_c + Pa$ . It is observed that the power consumed by multicore processor is greater than  $Pw_s$ .

The fifth column gives the amount of power consumed by a program to execute on single and multicore (dual and quad core) after parallelizing the program. The power consumed by the dual core and quad core processor where each core is n-BCE core is Pw<sub>s</sub> unit of power which is theoretically possible. The power consumed by the dual core and quad core n-BCE processor is 2\*w<sub>c</sub> unit of power and 4\*w<sub>c</sub> unit of power respectively. If it is possible to execute the program in half the execution time taken by single core processor by reducing the strength of cores by 50%, then the power consumption of a n-BCE single core processor and a n-BCE multicore processor will be equal. But, ideally the strength of the cores is not reduced by 50% thus increases the power consumption to execute the same program. It is observed that the power consumed by multicore processor is greater than Pw<sub>s</sub>. For example, if the power consumed by a

program when executed for 5 unit time on a full blown single core processor  $Pw_s$  is 1. The energy consumed by the processor is 5 units. If the same program is executed on dual core processor whose strength is reduced by 30% compared to single core processor and if we assume the time taken is reduced to half i.e, 2.5 unit time. The power consumed  $w_c$  of each core is 0.7 unit and total power consumed is 1.4 W, but the energy spent is 2\*(2.5\*0.7) = 3.5 units.

The performance per power (Perf/W), which represents the performance achievable at the same cooling capacity is based on the average power (W). This metric is reciprocal of energy, because the definition of *performance* is the reciprocal of execution time.

In other words, a sequential execution and its parallel execution version will consume the same amount of power only when the performance improvement through parallelization scales linearly. Otherwise  $Pw_q > Pw_d > Pw_s$  to finish the same task.

Furthermore maximizing and balancing parallelization among cores is important, not only for higher performance but also for power supply efficiency and extended battery life.

### 1.2 State-of-the-Art of Exploiting Parallelism

All computer systems today, from embedded devices to petascale computing systems, are being developed using multicore processors.

Following are possible approaches available to exploit parallelism:

- Allow programmers to use parallel programming constructs to explicitly specify which parts of the program can run in parallel.

- Allow operating system (OS) to schedule different tasks on different cores.

- Allow hardware to extract parallelism and schedule them dynamically.

- Allow the compiler to extract parallelism and schedule them.

In first approach, developing and verifying an explicitly parallel program is expensive and doesn't scale with the number of cores [9].

In the second approach, the operating system realize each core as a separate processor and OS scheduler schedules coarse grain threads on to different cores. In the thread style approach, two explicit parallel primitives are independent unless an explicit communication primitive (for synchronization) are added to stress what is inside the original code. Further the multicore processor architecture differs from traditional multi processors in terms of having

shared caches, memory controllers, smaller cache sizes available for each computational unit, and low communication latency between cores [18]. Owing to the architectural difference, it is desirable to extract fine grained thread and schedule them on to multiple cores instead of scheduling coarse grained thread as done in multi chip multiprocessing systems (SMP system).

In hardware-centric approach, detecting parallel execution opportunities and creating schedules for parallel regions dynamically by effectively utilizing all available resources is responsibility of the hardware [19]. This approach adds more circuits, which results in complex hardware implementations of algorithms such as branch prediction, instruction level parallelism detection, and register renaming. The hardware based approach work under heavy resources and time constraints.

In software-centric approach, a compiler analyzes the program for the possibilities of parallelism, identifies the code which could be executed in parallel and uses suitable scheduler to schedule the parallel constructs on to multiple cores. Using the various kind of dependency analysis, the compiler can identify the independent instructions that can run in parallel [20]. The compilation being offline one time activity, rigorous analysis to achieve optimal amount of code parallelization can be carried out.

#### 1.3 Objectives and Contribution

The proposed research aims to provide compiler support to exploit parallelism by extracting fine grained threads from a sequential program and creating schedules for multiple cores.

The proposed work involves

- Parallel region formation or Extracting fine grain threads.

- Scheduling parallel regions or fine grain threads on to multiple cores. and

- Global register allocation.

The proposed work introduces two additional passes to the original flow of compiler: Fine grain thread extractor pass and scheduler pass. The fine grain thread extractor pass of the compiler splits the sequential program into parallel regions (fine grain threads) termed as sub-blocks. To facilitate global scheduling new data structure called sub-block dependency graph (SDG) is proposed. Efforts are made to reduce the compilation time for performing fine grain extraction pass. The sub-blocks are created such that they ensure spatial and temporal locality.

The fine grained threads can be scheduled using scheduler. One local scheduling heuristic, termed as Intra block scheduling and four global scheduling heuristics, termed as Inter block scheduling are proposed in the thesis. The scheduler ensures that the sub-blocks scheduled on different cores at same time will not communicate nor access same data, thus provide lock free synchronization. The schedulers are designed to perform power optimization.

The fine grained threads that are scheduled on to different cores need to be allocated registers from respective register file of the core on which they are scheduled. The register allocator perform the global register allocation on each list of sub-blocks dedicated to individual core. Two novel register allocation heuristics are proposed. The first approach proposes a register allocation technique which is performed after scheduling and the second approach integrates register allocation and scheduling pass to mitigate the phase order problem. In first heuristic, the interference graph is constructed incrementally by merging the sub-blocks to create hyper sub-blocks. Hyper sub-blocks are created before register allocation to ensure temporal locality by pushing maximum instructions on to a core for execution. Hyper sub-blocks also ensures that instructions will do zero spills (k-colorable) and will remain in cores private memory till it is committed without doing memory reference during execution.

#### 1.4 Organization of the Thesis

A brief introduction to design philosophy behind multicore architecture, challenges and issues in multicore environment, state of art of exploiting parallelism, and objective of the thesis are discussed in the introductory chapter.

- ➤ In Chapter 2, we investigate several existing parallel architectures to understand how multicore is different from them. Several hardware and compiler support to exploit ILP (Instruction Level Parallelism) on these existing parallel architectures are presented and compared. An effort is made to understand the pros and cons of hardware and compiler approaches. A detailed survey on register allocation approaches is presented in the later part of this chapter.

- ➤ Chapter 3 describes the experimental framework used in this thesis. The framework includes a Compiler, Multicore architecture, the metrics used to evaluate the performance and the benchmark suites used in the proposed work. The phases of compiler are explained. A brief description on how to embed the SSA module in the given compiler is

- explained. A short description of Transactional Memories (TM) which provide run time support in terms of lock free transactions is presented.

- ➤ Chapter 4 aims to provide the details of the support and optimizations achieved in the proposed work. Section 4.1 provide the detailed description of fine grain thread extractor module. Section 4.2 provide details of schedulers and Section 4.3 details the register allocation techniques. The optimizations includes creating power aware schedules and finding compile time efficient approaches.

- ➤ Chapter 5 discusses the parallel region formation techniques. Two different approaches are proposed to obtain disjoint sets (parallel regions). To facilitate global scheduling new data structure called sub-block dependency graph (SDG) is proposed and efficient technique to create it is discussed in detail.

- ➤ Chapter 6 explains the implementation details of local scheduling heuristics (Intra Block Scheduling) which creates schedules for the parallel regions within the basic blocks of CFG. Results in terms of speed-up, power consumption, performance per power and communication cost is presented at the end of this chapter.

- ➤ Chapter 7 introduces four global scheduling heuristics (Inter Block Scheduling) which schedules the parallel regions formed across the basic block of the CFG. The brief discussion on merits and demerits of each heuristics are presented by comparing the results obtained by them. The results obtained by Inter block scheduling is also compared with the results obtained by Intra block scheduling technique.

- In Chapter 8, two register allocation techniques for multicore architecture are proposed. The first approach proposes a register allocation technique after scheduling and the second approach introduces a technique of integrated register allocation and scheduling approach to mitigate the phase order problem. The results obtained by the normal register allocation approach and integrated approach is compared and presented at the end of the chapter.

- ➤ Chapter 9 concludes the thesis by summarizing the achievements of the work, providing limitations and suggests future direction.

- Appendix A, Appendix B, List of references and List of publications by author is appended to chapter 9.

# **CHAPTER**

02 Literature Survey

To achieve high performance computing, a single core processor with parallel processing features were developed during 1975–2000 before multicore architecture was introduced by IBM in 2001. These parallel architectures either had multiple instruction processing units or multiple functional units. As computer architecture started becoming more complex, the compiler technology has also equally became an important factor. The success of each innovation in computer architecture is dependent on the ability of compiler technology to generate efficient code for these architectures. Parallelism has become one of the distinguishing factor in the design of high-performance computers. Parallelism comes in different form, namely instruction level parallelism (ILP), Task / Thread level parallelism (TLP), Memory level parallelism etc. A compiler was used by the parallel architectures to exploit parallelism as required by them to squeeze more performance.

This chapter discusses the relationship between parallel architectures, Instruction Level Parallelism (ILP) extraction techniques and compiler support to exploit ILP for corresponding architecture. Several existing parallel architectures such as pipeline, VLIW, and superscalar architectures are investigated to understand how multicore is different from them. Several techniques in both form, dynamic (hardware) and static (compiler) support to exploit ILP on these existing parallel architectures are presented and compared. In section (2.4) a detailed survey on register allocation approaches is presented and examines the register allocation requirement for multicore architectures.

#### 2.1 Parallel Architecture, ILP & Compiler

The principle behind RISC architecture is to move the architecture boundary closer to the hardware, exposing key performance features to the compiler. By doing so, it can take advantage of the compiler by off-loading the task like choreographing complex instructions from the hardware to compiler, to get high performance processor. Some of the new generation of the microprocessors have implemented branch prediction, ILP detection, register allocation or renaming and hazard detection logic in hardware to achieve ILP and faster execution.

The analysis at compile time can simplify and eliminate many of the complex algorithms in the hardware. Some architecture such as Power4 [21], Cyclops [22], RAW [23][24] and TRIPS [25][26] aims to maximally utilize the compiler by fully exposing the hardware and giving control to the software systems. Furthermore, the rigorous compiler-based analysis can lead to improved optimizations as compared to hardware-based approaches which work under heavy resource and time constraints. The current day compilers can analyze the complete program to infer detailed information about ILP in a given program code.

Instruction level parallelism (ILP) is a technique used to speed up the execution of code by allowing parallel execution of sequence of instructions derived from a sequential program [27]. The exploitation of ILP in a code is majorly hampered by conditional branch instructions and dependent instructions. The dependency analysis can be carried out to identify the set of independent instructions that can be executed in parallel. The instruction dependency is of three types, namely the name dependency, the control dependency and the data dependency. There are two types of name dependencies, Write after Write dependency (WAW) or anti dependency and Write after Read dependency (WAR) also known as output dependency. The name dependency can be eliminated by register renaming. Dynamic register renaming (by hardware) can eliminate WAW and WAR dependencies. But when an intermediate representation of program in static single assignment (SSA) form is used, WAW and WAR dependencies are removed without any need of hardware [28]. SSA form is an intermediate representation of a program in which each variable is defined only once. The control dependencies can be removed by using the hardware to predict conditional branches. Read after Write (RAW) dependency also known as true dependency falls under the data dependency category. It can be removed at run time using data collapsing [29] and re-association [30] technique. These techniques require specialized hardware elements. The compilers can be used for carrying out in-depth code analysis to determine the data dependency. Compiler driven optimizations are likely to significantly improve the execution performance of a processor.

To exploit the instruction level parallelism, first in-depth data dependency analysis is carried out. This analysis is used for segregating dependent and independent set of instructions for scheduling & resource binding. The advancement in the field of VLSI technology has led to design of parallel architecture, and the compiler is used for exploiting ILP on such architectures [31]. The nature of ILP support offered by compiler is heavily dependent on the architecture and

varies for different architecture. The interplay between compiler support and available architectural features is shown in Figure 2. Compiler developed for sequeintal architectures such as superscalar architectures, does not perform any machine level optimizations and does not convey any explicit information regarding parallelsim, special hardware performs machine specific optimizations.

In Dependence and Indipendent architectures such VLIW and Horizon architectures, the responsibility is of machin level optimization is shared between compiler and hardware. Compiler explicitly indicates the dependences that exist between operations.

In fully indipendent architectures such as RAW architecture, compiler will be fully aware of features of the processor and will take full responsibility of machine level optimization. The adventage of these type of architectures is that, execution time and power is saved.

Figure 2. Compiler vs Hardware Support for Exploiting ILP

The hardware approach for achieving ILP is being able to execute multiple instructions simultaneously either by pipelining the instructions or by providing multiple execution units. Pipelined processor, VLIW (Very Long Instruction Word) and super-scalar processors exploit ILP to improve execution time. In pipelined processor, a task is broken into stages, and stages are executed on different (shared) processing units by overlapping the execution of instructions in time [32]. The performance resulting from pipelining is expected to increase with increase in

pipeline stages. However, pipelined operations are required to be continuous without interruption throughout the program execution. Unfortunately, the processor sometimes stalls as a result of data dependency and branch instructions. RISC solution to this problem is code reordering [33]. The task of code reordering is generally left to the compiler, which recognizes data dependencies and attempts to minimize performance stalls by reordering the program instructions.

VLIW processor follows the static scheduling. VLIW issues one long instruction per cycle. Each long instruction consists of many tightly coupled independent operations. These independent operations are simultaneously processed by suitable execution units in a small and statically predictable number of cycles. The task of grouping independent operations into a long instruction is done by a compiler [34]. The major drawback with VLIW is that it uses the fixed number of instructions. The availability of multiple execution units is not utilized completely, because the execution unit which has completed its processing will be idle until all the execution units have completed their processing. Super-scalar processor overcomes the drawback of VLIW by working on variable number of instructions using simultaneous multithreading, where independent threads will run in parallel [35]. The major drawback with the super-scalar processor is that all the execution units share the same memory leading to more register spilling, and race condition due to limited availability of registers.

The multicluster VLIW embedded processor is made up of multiple small processing elements (PEs) [36][37][38]. These PE's are individual groups designed by decentralizing the computing resources to improve the scalability problem. Each tightly interconnected PE's help to reduce the communication cost & power. The instructions partitioned by compiler analysis are executed in parallel on these PEs [39]. The main difference between today's multicore processors and multicluster VLIW processor is that later has shared data cache, while each core in multicore processor will have private caches. The compiler should also be aware of data which are brought into private cache of the core.

VLIW and superscalar machines, both benefit from code reordering. In VLIW, all dependencies are checked during compile time, and the search for independent instructions and scheduling is done exclusively by the compiler. The hardware has no responsibility on the final scheduling. On the other hand, superscalar machines depend on hardware for scheduling the instructions. But it is accepted that compiler techniques for exploiting parallelism must be used in superscalar machines to achieve better performance.

#### 2.2 Background of Instruction Scheduling

In case of Superscalar and VLIW machine, the scheduling of instruction is dependent on identification of set of independent instructions that can be executed in parallel. The scheduler only addresses the issues associated with temporal parallelism leading to exploitation of ILP but it may increase register pressure [40]. These schedulers do not take care of spatial issues as superscalar and VLIW processors exchange the shared/dependent operands through shared register file which is absent in multicore system. For the pipeline based machines, scheduler reorders instructions to minimizes pipeline stalls. The reordering of the instructions should not change the set of operations performed and should make sure that interfering operations are performed in order.

In the past, researchers have proposed several instruction scheduling techniques which includes List scheduling, Trace scheduling, Superblock scheduling and Hyper block scheduling. All these scheduling techniques can be classified based on the nature of the control flow graph used, i.e. whether it uses multiple or single basic blocks, and whether it is cyclic or acyclic control flow graph.

The scheduler that schedules single acyclic basic block is known as local scheduling. List scheduling is an example of local scheduling [41] and is based on highest level priority scheme. Trace scheduling, superblock and hyper-block scheduling are global scheduling techniques that work on regions known as traces which consists of contiguous set of basic blocks [42]. Trace scheduling combines the most common trace of basic blocks and schedule them as a single block [43]. Superblock scheduling is same as trace scheduling without side entrances [44]. Hyper-block scheduling combines basic blocks obtained from multiple paths of control flow graph [45]. In run-time scheduling, an instruction is issued after it is decoded and when its operands are available [46]. The run-time scheduling mechanisms exhibit adaptive behavior which leads to higher degree of load balancing. The run-time scheduling policies incur high run time overhead which may lead to degradation of execution performance. The logic to make decision at run time should be simple and constant time heuristics, otherwise it leads to expensive and complex hardware design which requires relatively large amount of silicon area. The complex hardware in turn results in increased power consumption. The advantage of compile time scheduling over the run-time scheduling is that it can carry out rigorous dependency analysis. The complexity of the

scheduling techniques will affect the compile time of a program but has no adverse impact on its execution time.

Scheduling techniques for various parallel architectures are summarized in Table II illustrating the advantage, drawbacks and algorithm complexity of these techniques.

TABLE II. SCHEDULING TECHNIQUES FOR PARALLEL ARCHITECTURE

| Scheduling<br>Technique                 | Architectur<br>e | Туре   | Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Complexity         |

|-----------------------------------------|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Basic Block<br>Scheduling<br>[47]       | Pipeline         | Static | Topological sort of Dependence graph. Simple and easy to implement.  Restricted to a single block.                                                                                                                                                                                                                                                                                                                                                                                                               | O(N log N)         |

| Region<br>Scheduling<br>[48]            | Pipeline         | Static | Creation of regions from blocks and then topologically sorting the regions.  Inter block scheduling is made possible.  Operations within a loop cannot overlap with those of another loop.                                                                                                                                                                                                                                                                                                                       | O(N <sup>2</sup> ) |

| Gibbons-<br>Muchnick<br>method [49<br>] | Pipeline         | Static | Creation of DAG. Then choosing the instruction to be scheduled according to heuristics such as:- the node with the max no of children or which interlocks with its children or which is on the longest path from the leaves.  Heuristic approach makes scheduling simple. Dependency DAG's can be used for other code optimizations. Deadlocks are prevented.  Much of the hazard detection is assumed to be done by the hardware to make things simple. Also, scheduling across basic blocks is not considered. | O(N <sup>2</sup> ) |

| Bernstein's method [50]                 | Pipeline         | Static | First a level is assigned to each instruction. Next a list scheduling is performed in decreasing order of priority.  Nodes on the critical path are assigned higher priorities and therefore scheduled first.  Structural hazards cannot be avoided as the DAG is not weighted i.e. it does not take into account the latency of each operation.                                                                                                                                                                 | O(Nlog N)          |

| Shieh-<br>Papachristou<br>method<br>[51][52] | Pipeline | Static  | Construction of priority list using several heuristics and then assigning time slots based on the priorities.  Using multiple heuristics reduces the probability of choosing a wrong node for scheduling.  The greedy heuristics used can schedule two floating point operations in consecutive cycles even when the processor is not pipelined.                                                                     | O( N + E) |

|----------------------------------------------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Superblock<br>Scheduling<br>[53]             | Pipeline | Static  | Involves finding the most frequently executed path using trace selection. Then superblocks are formed from these traces and DAG is formed, after which list scheduling is performed.  Reduces the complexity associated with side entrances by removing them. Also, it focuses on the frequently executed paths.  Cannot deal with the situation when different execution paths have equal frequencies of execution. | O(N*E)    |

| The<br>Scoreboard<br>[54][55]                | Pipeline | Dynamic | Used multiple execution units for out of order execution. A centralized control unit called the scoreboard is responsible for instruction issue and execution, including the detection of hazards.  Enables out of order execution. Allowed instructions behind stalls to proceed.  Structural hazards stall the pipeline. Limited to instructions in basic block.                                                   |           |

| Tomasulo<br>Algorithm<br>[56]                | Pipeline | Dynamic | Two floating point units are used – add and multiply/divide. Buffers called reservation stations are used for fetching and storing instruction operands. The result of an operation is stored at reservation stations to remove WAW and WAR hazards.  Register renaming removes structural hazards.  Limited to instructions in a basic block. A common data bus limits the amount of data transfer.                 |           |

| List<br>Scheduling<br>[57]               | VLIW and<br>Superscalar<br>(but mainly<br>for<br>superscalar) | Static | It finds ILP within a single basic block and fills data stalls (if any) by instructions in other basic blocks.                                                                           | O(N)     |

|------------------------------------------|---------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Trace<br>Scheduling<br>[58]              | VLIW                                                          | Static | It exploits ILP across basic block boundaries and tries to locate the most frequently executed path called <i>trace</i> by preserving program semantics (book-keeping).                  | $O(N^2)$ |

| Software<br>Pipelining<br>[59]           | VLIW                                                          | Static | It tries to find the maximum ILP through the loop unrolling and scheduling the iterations of the loop every initiation interval.                                                         | $O(N^2)$ |

| Enhanced<br>Modulo<br>Scheduling<br>[60] | VLIW and<br>Superscalar                                       | Static | It schedules the loops by maintaining an optimal value of initiation interval.                                                                                                           | $O(N^2)$ |

| Speculative<br>Execution<br>[61][62]     | VLIW and<br>Superscalar                                       | Static | It tries to speculatively execute instructions that are moved upward of conditional branches.                                                                                            | $O(N^2)$ |

| Superblock<br>Scheduling<br>[63]         | VLIW and<br>Superscalar                                       | Static | It is derived from trace scheduling. It schedules the instructions from most frequently executed and optimized <i>superblock</i> (a trace with no side entrance is called a superblock). | $O(N^2)$ |

Next section explains the motivation to carry out the research in the area of multicore architecture.

#### 2.3 Scheduler Requirement for Multicore Architecture

i. All the existing techniques find it difficult to make good decision on scheduling because, scheduling algorithms are strongly dependent on the machine model for which they are developed. The instruction scheduling techniques are NP-complete and follow heuristics.

Some of the heuristic/ practices are loop transformations, static branch prediction,

- speculative code motion, predicated execution, software pipelining, and clustering. Different heuristics work well with different types of graph.

- ii. In the existing local scheduling techniques, ILP is achieved by scheduling one instruction at a time on multiple execution units. To perform this task, a critical path of instructions is created by analysing the dependencies. The instruction with lengthy critical path is scheduled first to enable other instructions to get scheduled. This technique cannot be applied on multi-core environments because two dependent instructions may get scheduled on different cores resulting in increased communication latency. The ILP on multicore architecture can be fully exploited only if all dependent instructions are scheduled on to same core.

- to group them based on the dependency analysis. Since there are three dependencies to look for, the output of these techniques were discouraging for most of the applications. The programs in static single assignment (SSA) have proved useful by eliminating false dependencies in traditional code. Removing false dependencies allows more flexibility in scheduling since data independent operations can move close to each other during instruction scheduling. Along with simplifying the dependency analysis among the instructions, SSA form programs gives solutions to the class of NP-complete problems like register allocation and enables various optimizations [64][65]. The proposed work is performed on SSA form program, which forms the backbone of further analysis.

- In most of the traditional instruction scheduling algorithms the goal is to improve performance in terms of execution time by increasing the amount of instruction-level parallelism in program code. Since communication between distant computing resources may invite delays, instruction scheduler is expected to take care of spatial problem along with temporal problem in multicore environment. The instruction scheduler needs to partition instructions across the computing resources. Based on the parallel schedule generated by compiler, the power consumption may vary [66]. Power reduction without impeding the speedup is an important scheduling constraint for parallel architecture. The proposed work involves power-aware scheduling strategies which minimizes the switching activities between instructions and use reduced number of cores to achieve performance per power.

# 2.4 Survey on Register Allocation

Register allocation is a crucial phase of compilation. It maps unbounded number of variables of a program to a fixed number of physical registers of a processor. Values stay in registers as long as variables are live, In general, register allocation problem is NP-complete from the fact that number of registers available is small and some of them are special purpose registers. Due to limited number of available registers, the register allocation to all variables will not be possible, and hence are required to be stored in memory. These variables are called spilled variables. The cost of spilling is minimized by spilling the least frequently used variables. The commonly used register allocation approaches are shown in Figure 3.

Figure 3. Register Allocation Approaches

Most of the register allocation algorithms assume that the CPU has regular register files and these algorithms fail to adopt themselves for irregular architectures. Several solutions have been proposed for irregular architectures, but without considering the specific implementation details,