## Design Exploration of Low Power Arithmetic and SRAM circuits using Subthreshold Design technique

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of

#### **DOCTOR OF PHILOSOPHY**

By

Priya Gupta ID No. 2011PHXF416P

Under the supervision of **Prof. Anu Gupta**

Co-supervision of **Dr. Abhijit Asati**

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN) INDIA MARCH 2017

Date:

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN) INDIA

### **CERTIFICATE**

This is to certify that the thesis entitled "Design Exploration of Low Power Arithmetic and SRAM circuits using Subthreshold Design technique" submitted by Ms. Priya Gupta, ID No 2011PHXF416P for award of Ph.D. of the Institute embodies original work done by her under our supervision.

(Signature of the Supervisor)

Prof. Anu Gupta

Dr. Abhijit Asati

Professor

Assistant Professor

Birla Institute of Technology & Science Pilani

Pilani - 333031 (Rajasthan) INDIA

(Signature of the Co-Supervisor)

Dr. Abhijit Asati

Assistant Professor

Birla Institute of Technology & Science Pilani

Pilani - 333031 (Rajasthan) INDIA

#### **ACKNOWLEDGEMENTS**

I intend to extend my gratitude to my advisor, Prof. Anu Gupta, Professor, and co-advisor, Dr. Abhijit Asati, Assistant Professor, BITS Pilani for their suggestion, guidance and supervision in the present work.

Many thanks to my two thesis committee members, Prof. S Gurunarayanan and Dr. Nitin Chaturvedi for reviewing my proposal and advising time to time during my Ph.D.

I would also like to thank the Departmental Research Committee members, Prof. Navneet Gupta, Prof. H. O. Bansal and Dr. K. K. Gupta for their constructive feedback.

I greatly acknowledge the support of Pawan Sharma for all kind of technical discussions which helped me a lot in my research.

I must acknowledge all my fellow research scholars, Ashish Kumar Sharma, V. Balaji, Yogesh B., Prachi Sharma, Jitendra Kumar, Satish Mohanty, Abhishek Joshi, Jyotirmoy Bhardwaj, Fani Mani, Ravinder, Prashant Upadhyay and Dhananjay Mishra for providing me all kind of support to my research work. Working, playing, living, and arguing with my fellow research scholars (Nikita Sharda, Anurada Devi, Arun Nihal Singh, Himanshu Chawla, Pankaj Munjal, Mr. & Mrs. Dandautiya, Gaurav, Meenakshi, Rini, Rajesh, Sonal etc.) has been enriching and enjoyable.

My heartfelt thanks are due to all those teachers and students who took time out from their busy schedule to help me in this thesis. I thank all those who were involved in typing and printing this project report. I also want to thank staff members of EEE Department: Surender, Manoj Kumar, Amitabh, Mahesh Sani, Birdi Chand and Sanjay for their kind help in laboratory and other official work.

Last but certainly not the least, I would also like to thank my all family members for their invaluable support and everlasting trust. Most of all, I would like to thank God for everything especially his love and grace.

Priya Gupta 21A/1F/8 Gandhi Marg, BITS-PILANI, Rajasthan, INDIA March 2017

#### **ABSTRACT**

Complete analyses of the arithmetic circuits and SRAM cells used for above-threshold operation have never been examined in the context of sub-threshold operation. The conventional arithmetic circuits and SRAM cells may not work in sub-threshold region at nanometer technologies due to ultra-low supply voltage.

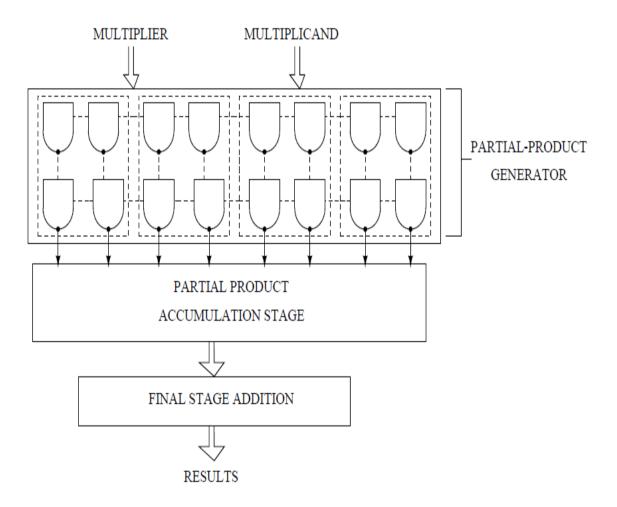

This thesis work presents new functional designs and design space exploration for arithmetic circuits and SRAM cells in sub-threshold region. Exploration includes three parallel prefix adder architectures, two column compression multipliers and Static Random Access Memory (SRAM) cells, with transistor count ranging from 6 to 12, in terms of power consumption, propagation delay, and power-delay product. Their performance is also obtained at 45 nm and 180 nm technology nodes to find the impact of scaling on their performance. The work has been carried out in three parts.

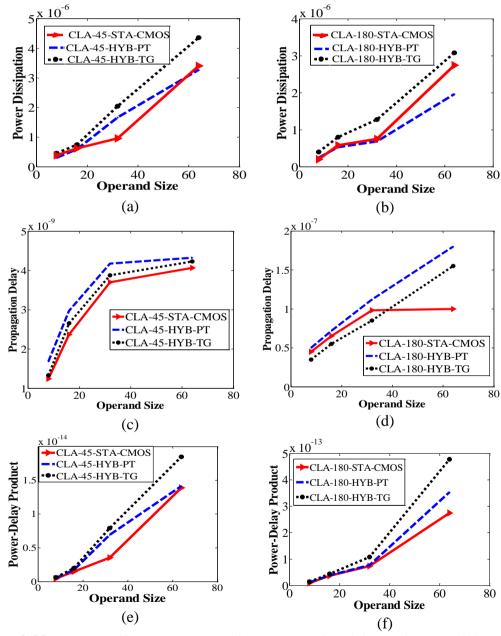

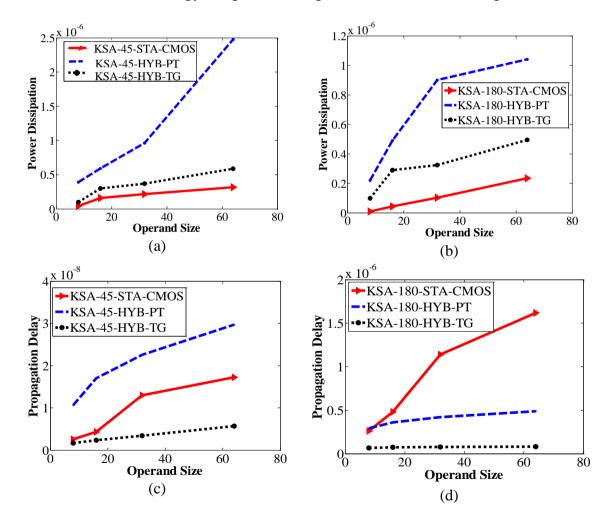

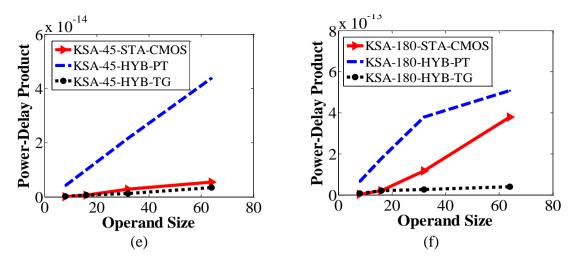

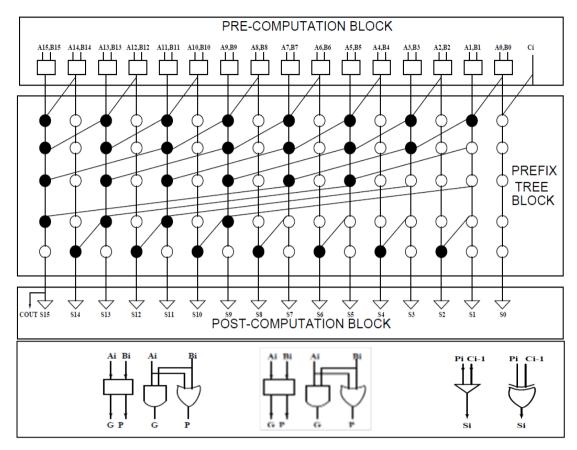

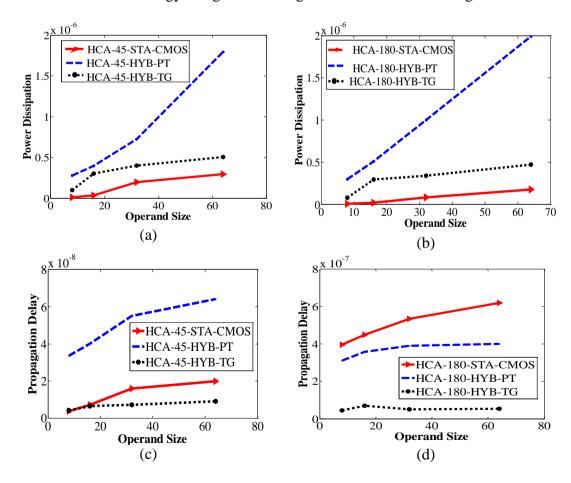

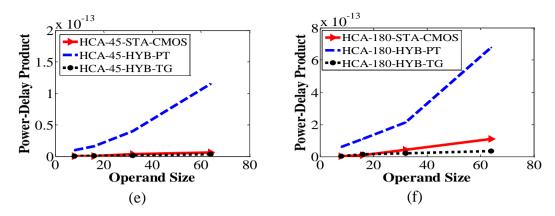

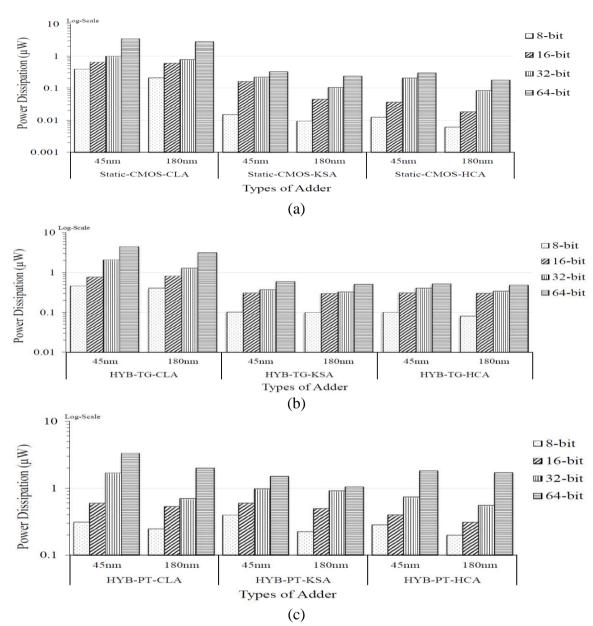

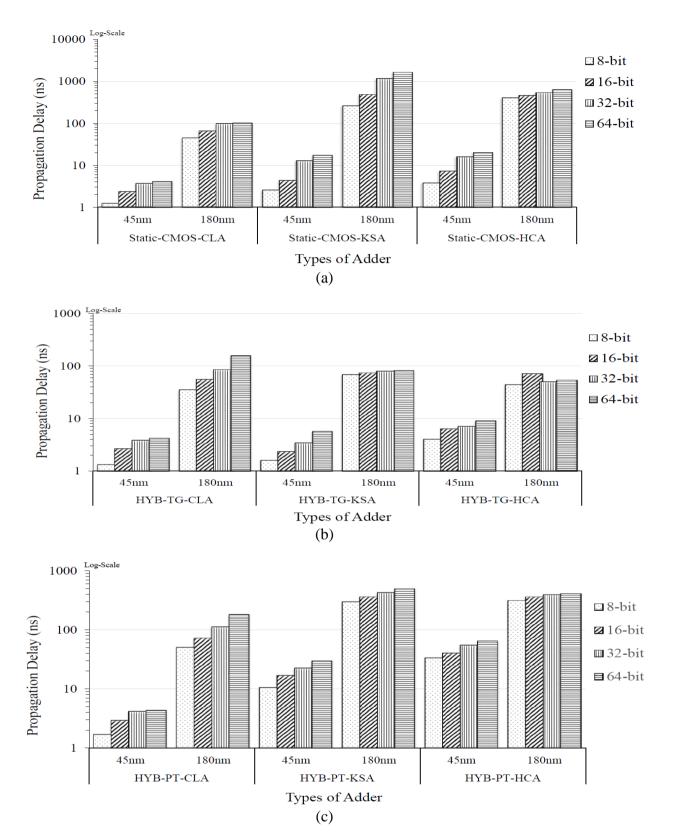

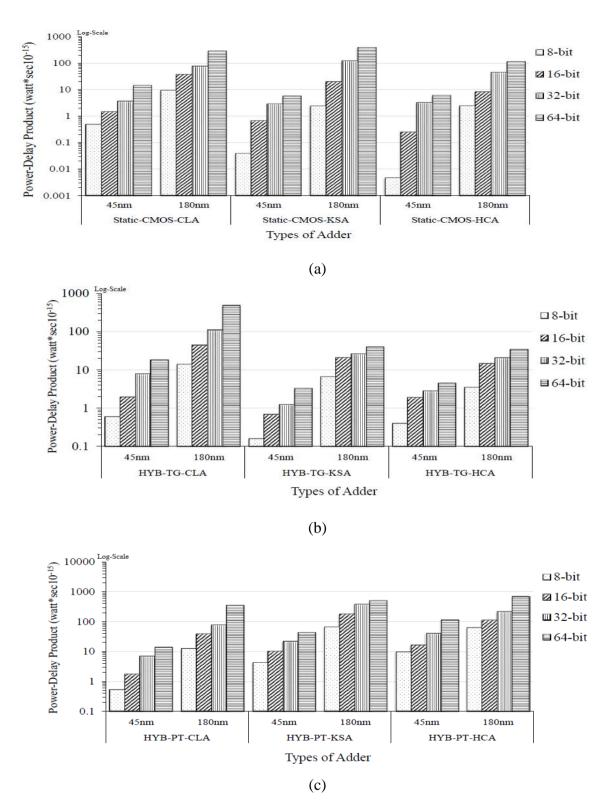

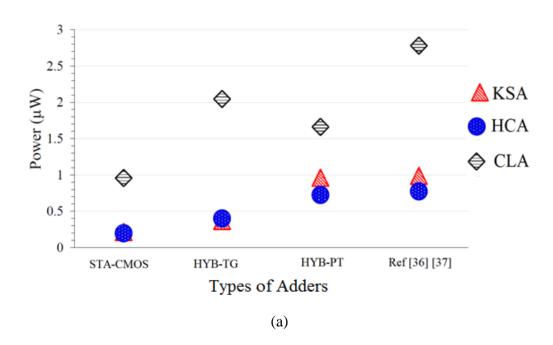

In the first part, three power efficient parallel prefix adders namely Carry look-ahead adder (CLA), Kogge-Stone adder (KSA) and Han-Carlson adder (HCA) architectures are selected as per literature survey. These architectures are designed, simulated and analyzed, in subthreshold region, with three different logic design styles namely Static-CMOS, Hybrid Pass Transistor (Hybrid PT), and Hybrid Transmission Gate (Hybrid TG) for operand sizes of 8, 16, 32 and 64 bits. At 45 nm technology, it is observed that in comparison among themselves of all three selected adder architectures, HCA is the most power efficient, and CLA is the high-speed adder architecture in sub-threshold region. In contrast to worst (maximum) value obtained, HCA shows 96.8% lesser power consumption, CLA shows 79.8% lesser propagation delay and KSA shows 63.7% lesser power-delay product. Reverse body bias technique in Static-CMOS logic only leads to functional circuits with 61.87% reduction in propagation delay but with the increments in average power consumption and power-delay product by 77.03% and 38.3%respectively. Same trend of power consumption, delay and power-delay product for all the adder architectures is observed at 180 nm technology.

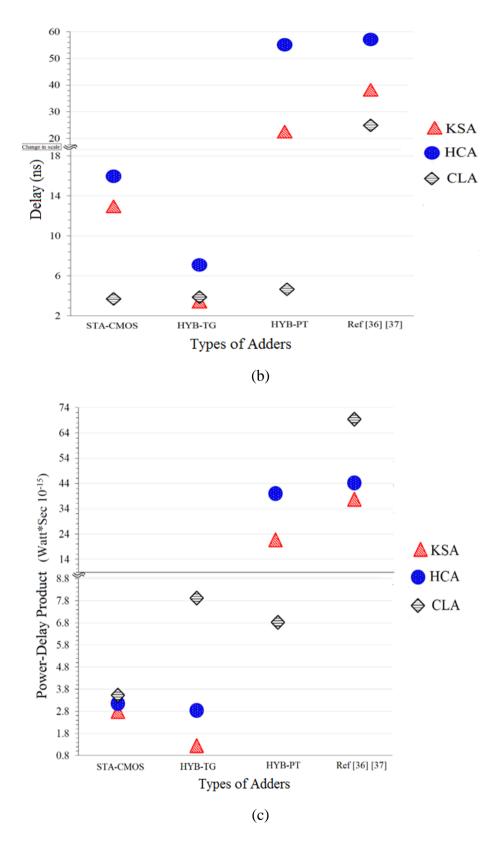

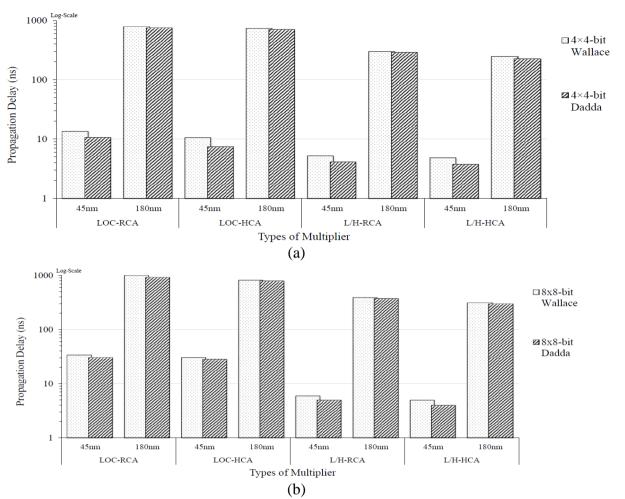

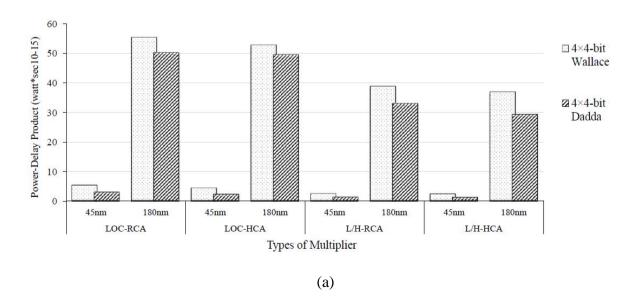

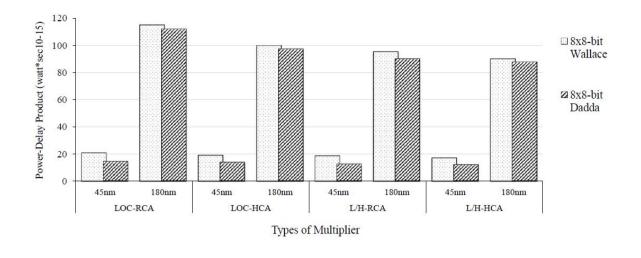

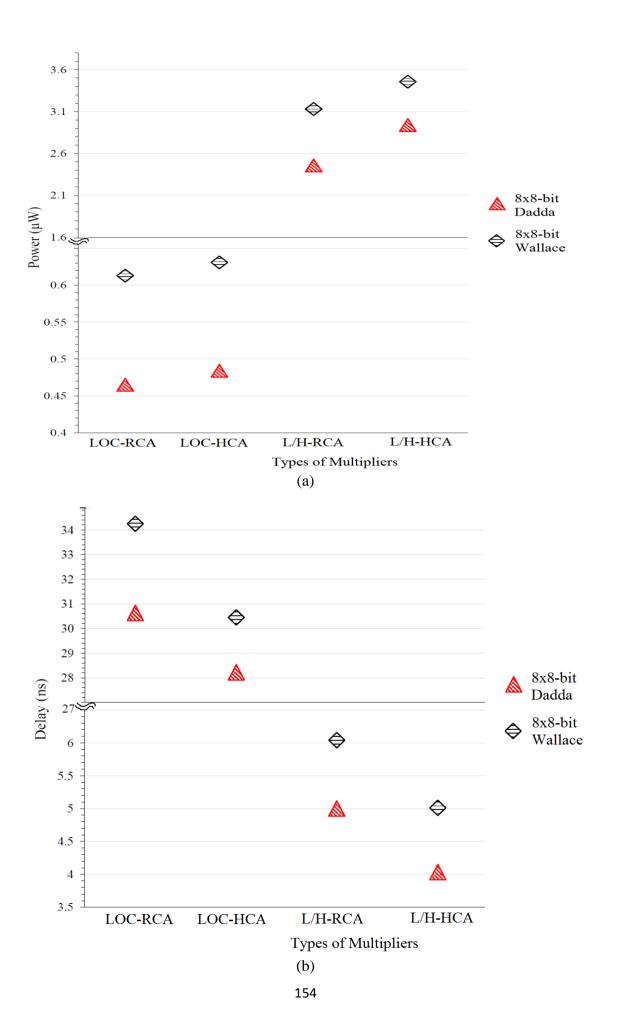

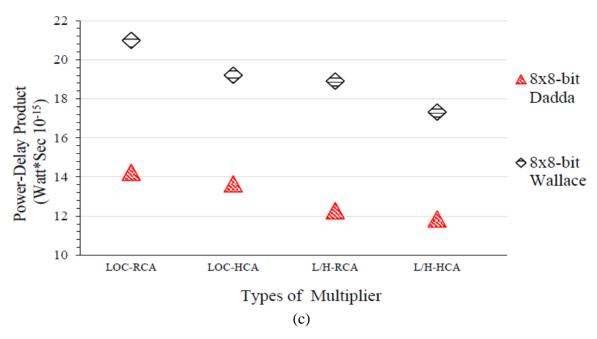

In the second part, two power efficient column compression multipliers namely Wallace tree and Dadda are selected as per literature survey. Total sixteen new designs of these architectures have been developed using two different partial product accumulation schemes namely using lower order compressors (LOC) and Mixed lower and higher order compressors (Mixed L/H). These designs are developed with two logic design styles (Static-CMOS &

HYB-TG) for two sizes (4x4 & 8x8) at two technology nodes (45 nm & 180 nm) in subthreshold region.

At 45 nm, among all eight multipliers implemented, Dadda-45-L/H-HCA has the least power-delay product. It has 49% (for 4x4-bit), and 31.5% (for 8x8-bit) lesser power-delay product in comparison to highest power-delay product obtained. Static-CMOS logic and HYB-TG design style are most power-delay product efficient design styles for LOC and Mixed L/H based multipliers respectively. Same trend of power-delay product is observed at 180 nm technology.

At 45 nm, the power consumption is higher than 180 nm technology for all adders and multiplier designs. The power consumption is increasing due to increments in the leakage current at 45 nm technology as compared to 180 nm technology since supply voltage is kept same at 0.4V.

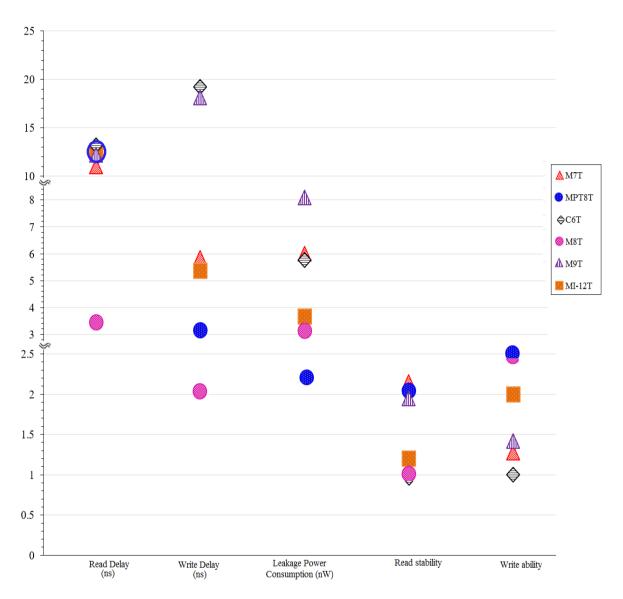

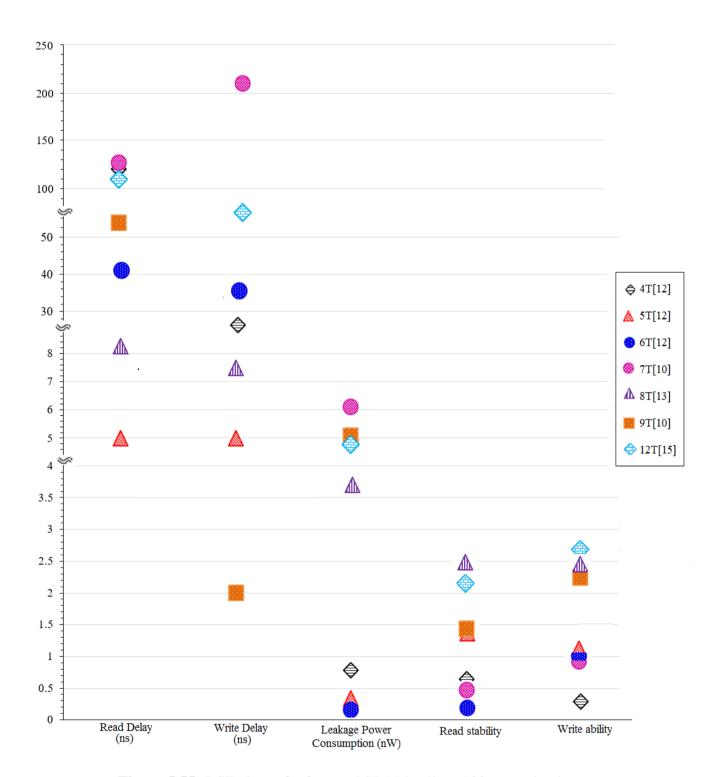

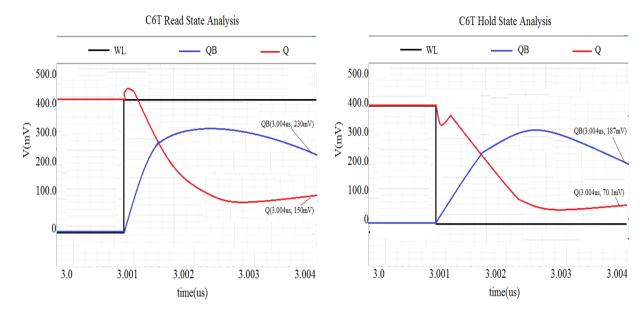

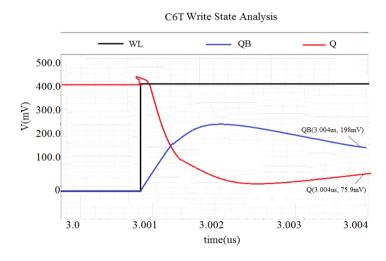

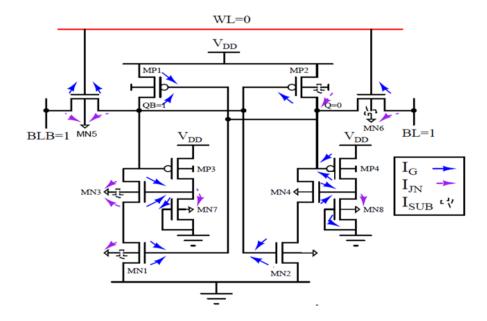

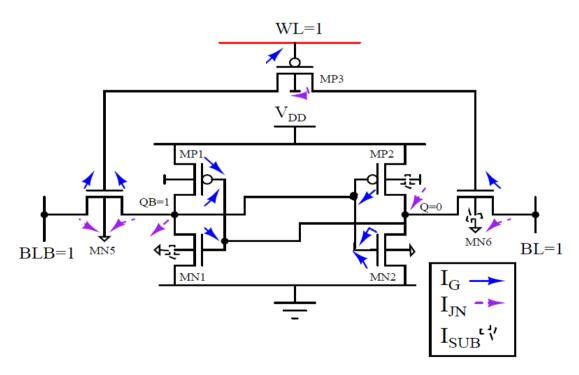

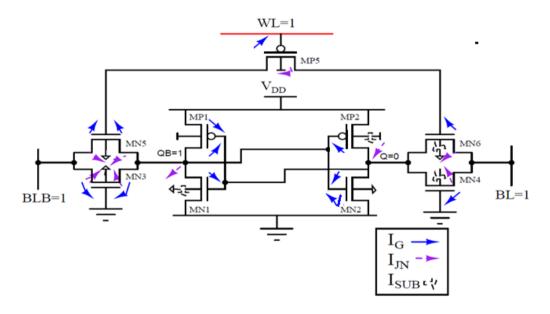

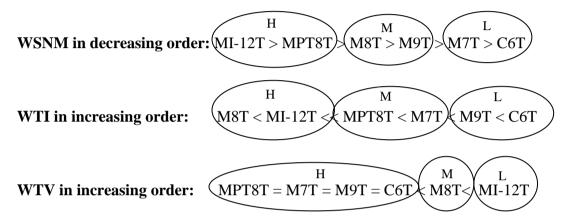

In the third part, for sub-threshold operation at 45 nm technology, five new designs of SRAM cells have been proposed with 7, 8, 9 and 12 transistor configurations at 0.4V power supply. Cell stability analysis is done using standard measures like hold/ read/ writes static noise margins as well as N-curve cell stability metrics. For performance analysis, read/write delay and leakage power consumption in hold mode are considered. The results show improvement in all the design parameters over other published designs and conventional 6 transistor (6T) SRAM cell. The comparison of proposed designs among themselves exhibit that three new designs namely M8T, MPT8T and MI-12T have low leakage power consumption along with other improved design parameters such as high read stability, high write ability, fast read & write operation. Thus, these designs can be an attractive choice for low power application. In comparison to results of published designs at 180nm, all proposed designs show improvement in read stability, write ability, read delay and write delay but with increment in leakage power consumption in hold mode.

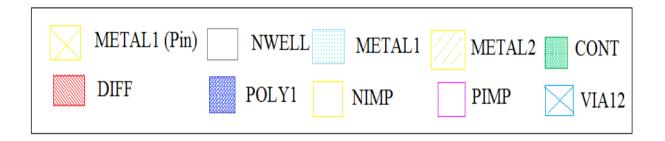

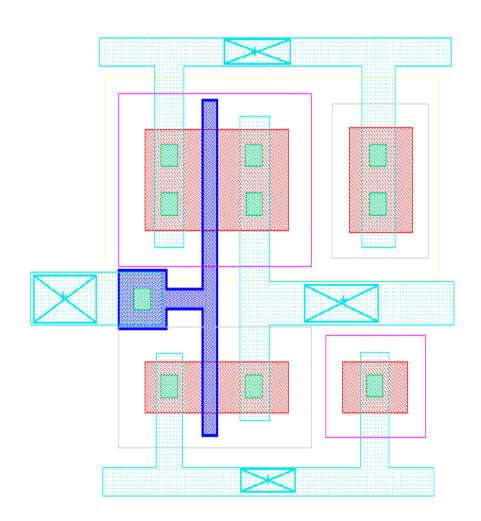

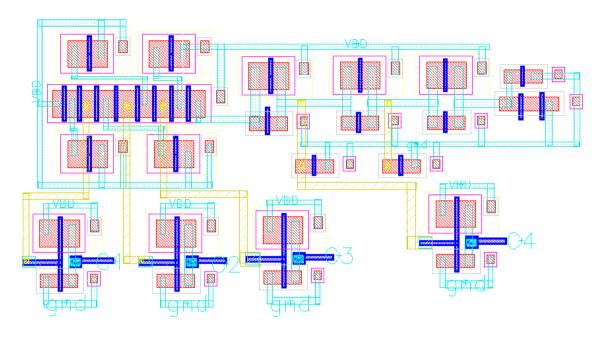

## **LAYOUT TEMPLATE**

## **Layer Information:**

### **TABLE OF CONTENTS**

| Ce  | ertificate                                                  | i      |

|-----|-------------------------------------------------------------|--------|

| Ac  | cknowledgements                                             | ii     |

| At  | ostract                                                     | iii    |

| La  | yout templates                                              | v      |

| Ta  | ables of Contents                                           | vi     |

| Lis | st of Tables                                                | X      |

| Lis | st of Figures                                               | xii    |

| Lis | st of Abbreviations                                         | xvii   |

| 1.  | Introduction                                                | 1-17   |

|     | 1.1. Background                                             | 1      |

|     | 1.2. Sub-Threshold Operation                                | 2      |

|     | 1.2.1. MOSFET in Sub-Threshold Region                       | 2      |

|     | 1.2.2. The MOSFET Drain Current in the Sub-threshold Region | 2      |

|     | 1.3. Sources of Power Consumption in CMOS Logic Gate        | 7      |

|     | 1.4. Motivations and Challenges in Sub-threshold Design     | 9      |

|     | 1.5. Research Gaps                                          | 11     |

|     | 1.6. Objectives of the thesis                               | 12     |

|     | 1.7. Organization of the thesis                             | 13     |

|     | References                                                  | 14-17  |

| 2.  | Literature Review                                           | 18-43  |

|     | 2.1. Introduction                                           | 18     |

|     | 2.2. Arithmetic Circuits                                    | 19     |

|     | 2.2.1. Parallel Adder Architectures                         | 22     |

|     | 2.2.2. Column Compression Multipliers                       | 27     |

|     | 2.3. SRAM Cells                                             | 28     |

|     | References                                                  | 33-43  |

| 3.  | Adders                                                      | 44-104 |

|     | 3.1. Introduction                                           | 44     |

|     | 3.2. Adder Architectures                                    | 46     |

|     | 3.2.1. CLA                                                  | 47     |

|     | 3.2.2. KSA                                                  | 49     |

|     | 3.2.3. HCA                                                  | 50     |

|     | 3.3. Logic Families for Sub-threshold Circuit Design        | 51     |

| 3.3.1. Static-CMOS Logic                                                                                    | 52      |

|-------------------------------------------------------------------------------------------------------------|---------|

| 3.3.2. Pass Transistor (PT) Logic Family                                                                    | 53      |

| 3.3.3. Complementary Pass-Transistor Logic (CPL)                                                            | 54      |

| 3.3.4. Swing Restored Pass-Transistor Logic (SRPL)                                                          | 55      |

| 3.3.5. Double Pass-Transistor Logic (DPL)                                                                   | 57      |

| 3.3.6. Transmission Gate Logic (TG)                                                                         | 58      |

| 3.3.7. Comparative Analysis of Basic Logic Gates using Different Logic Families for Sub-Threshold Operation | 59      |

| 3.4. Effect of Reverse Body Bias (RBB) Scheme                                                               | 60      |

| 3.4.1 Simulation Results of Logic Gates with RBB using Different Logic Families                             | 64      |

| 3.5. Design and Analysis of Parallel Adders                                                                 | 66      |

| 3.5.1. Design Implementation using CLA                                                                      | 68      |

| 3.5.1.1. CLA with Static-CMOS logic (Static-CMOS CLA)                                                       | 70      |

| 3.5.1.2. CLA with Hybrid TG logic (HYB-TG CLA)                                                              | 73      |

| 3.5.1.3. CLA with Hybrid pass transistor logic (HYB-PT CLA)                                                 | 75      |

| 3.5.2. Simulation Methodology and Results of CLA                                                            | 77      |

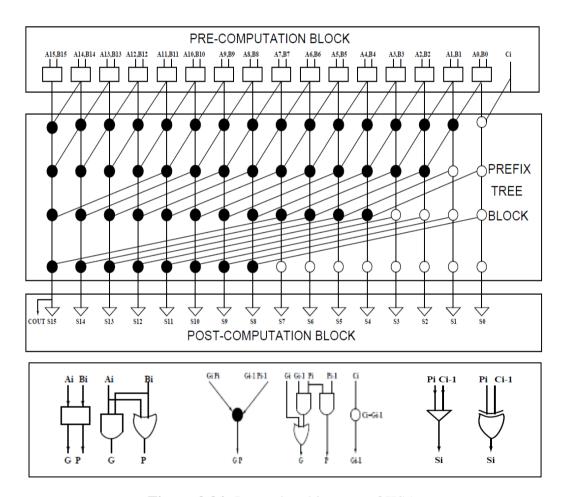

| 3.5.3. Design Implementation using KSA                                                                      | 81      |

| 3.5.4. Simulation Methodology and Results of KSA                                                            | 82      |

| 3.5.5. Design Implementation using HCA Architectures                                                        | 85      |

| 3.5.6. Simulation Methodology and Results of HCA                                                            | 86      |

| 3.6. Impact of RBB on Static-CMOS Adders                                                                    | 89      |

| 3.7. Final Results and Discussions                                                                          | 90      |

| 3.8. Conclusions                                                                                            | 96      |

| References                                                                                                  | 101-104 |

| Multipliers                                                                                                 | 105-158 |

| 4.1. Introduction                                                                                           | 105     |

| 4.2. Partial Product Generation                                                                             | 107     |

| 4.3. Partial Product Accumulation                                                                           | 109     |

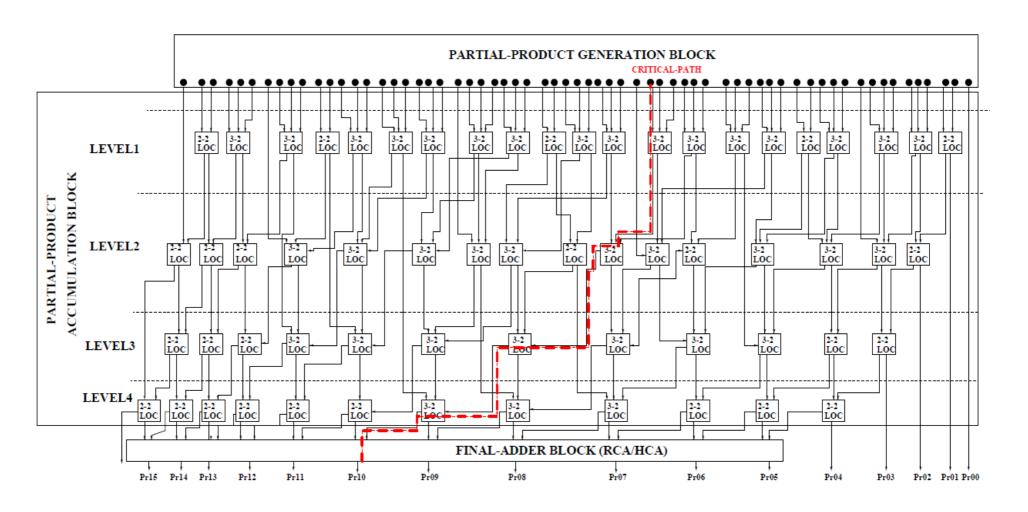

| 4.3.1. Partial Product Accumulation using LOC in Wallace tree                                               | 109     |

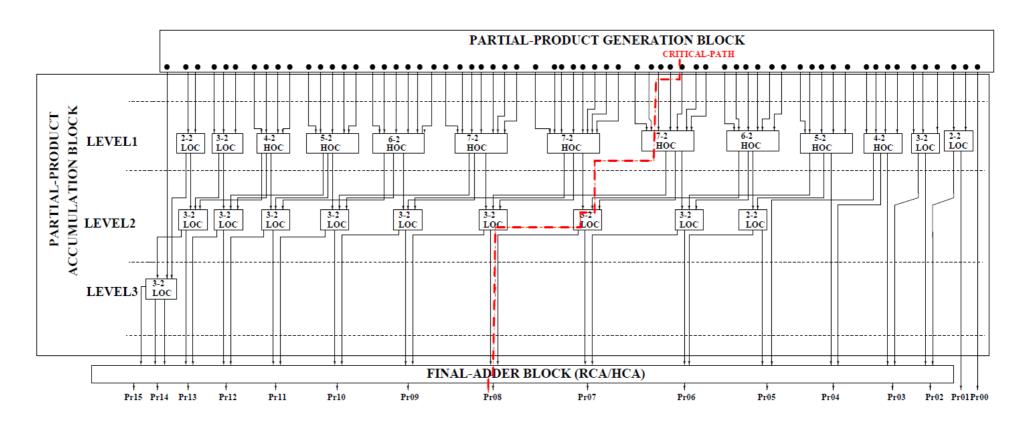

| 4.3.2. Partial Product Accumulation using Mixed L/H in Wallace tree                                         | 111     |

| 4.3.3. Partial Product Accumulation using LOC in Dadda Tree                                                 | 112     |

| 4.3.4. Partial Product Accumulation using Mixed L/H in Dadda Tree                                           | 114     |

| 4.4. Final Stage Addition in Wallace tree and Dadda Multipliers                                             | 115     |

| 4.4.1. RCA                                                                                                  | 116     |

| 4.4.2. HCA                                                                                                  | 116     |

| 1.5 Design and Analysis of Partial Product Accumulation Modules                                             | 117     |

4.

|    |      | 4.5.1.  | LOC Desi               | igns                                                                                 | 117     |

|----|------|---------|------------------------|--------------------------------------------------------------------------------------|---------|

|    |      | 4.5.2.  | LOC Desi               | gn using Static-CMOS                                                                 | 117     |

|    |      | 4.5.3.  | LOC Desi               | gn using HYB-TG Logic                                                                | 120     |

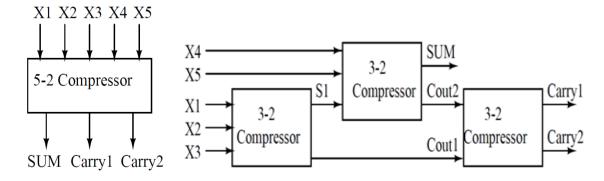

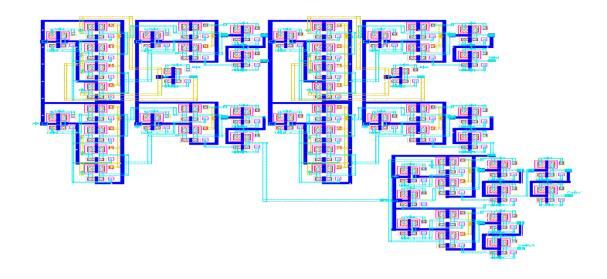

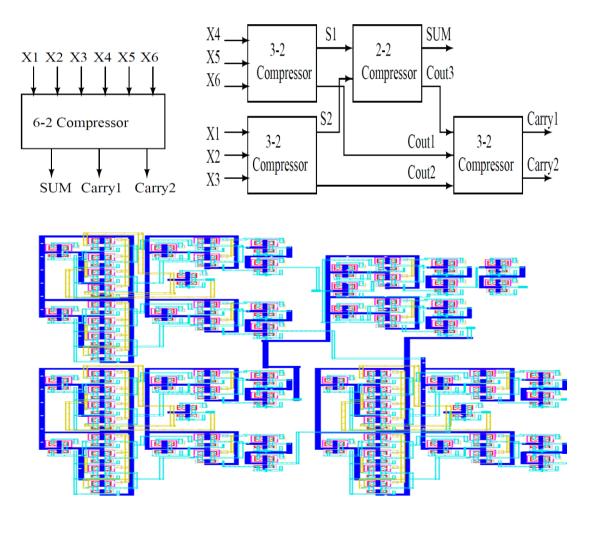

|    |      | 4.5.4.  | Higher Or              | rder Compressors (HOC)                                                               | 123     |

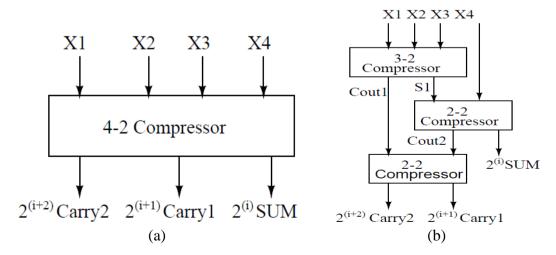

|    |      |         | 4.5.4.1.               | Conventional and Modified Architecture of 4-2 Compressor                             | 125     |

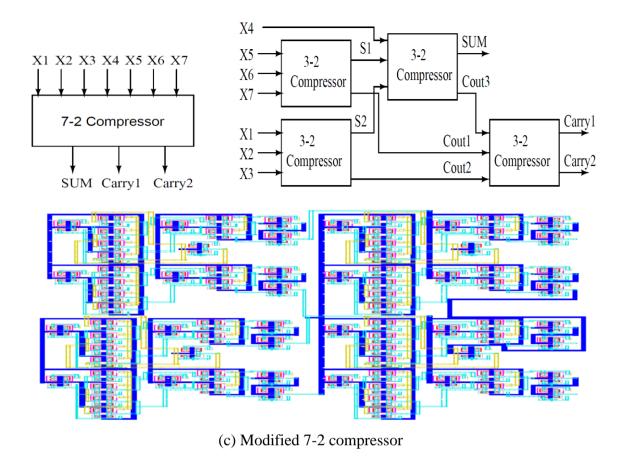

|    |      |         | 4.5.4.2.               | Design Implementation of Modified HOC's (5-2, 6-2 and 7-2)                           | 128     |

|    |      | 4.5.5.  | Performan<br>Sub-Thres | nce Analysis of Compressor Designs using Different Design Styles for shold Operation | 130     |

|    | 4.6. | Desig   | n and Anal             | ysis of Wallace tree and Dadda Multipliers                                           | 134     |

|    |      | 4.6.1.  | Design Im              | nplementation using Wallace tree Multipliers                                         | 134     |

|    |      | 4.6.2.  | Simulation             | n Methodology and Results of Wallace tree Multipliers                                | 137     |

|    |      | 4.6.3.  | Design Im              | nplementation using Dadda Multipliers                                                | 139     |

|    |      | 4.6.4.  | Simulation             | n Methodology and Results of Dadda Multipliers                                       | 142     |

|    | 4.7. | Final   | Results and            | d Discussions                                                                        | 144     |

|    | 4.8. | Concl   | usions                 |                                                                                      | 149     |

|    | Ref  | erence  | S                      |                                                                                      | 155-158 |

| 5. | Sta  | tic Rai | ndom Acce              | ess Memory (SRAM)                                                                    | 159-254 |

|    | 5.1. | Introd  | uction                 |                                                                                      | 159     |

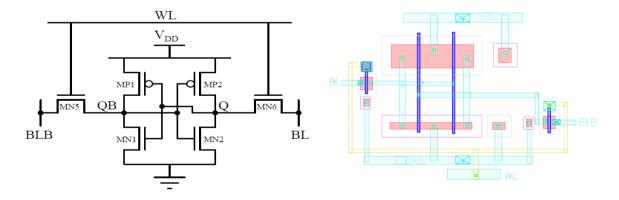

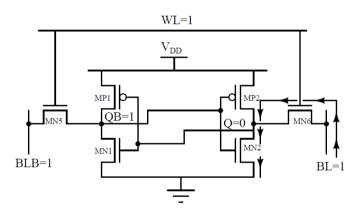

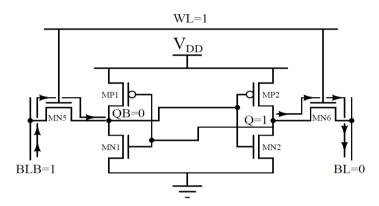

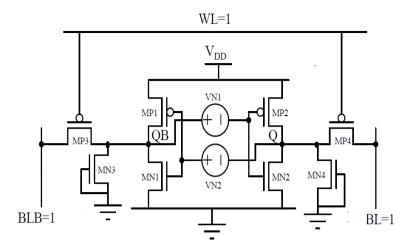

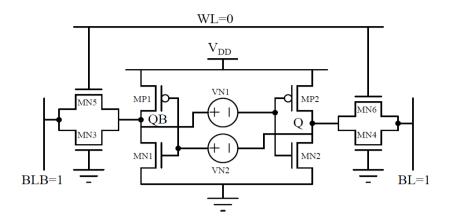

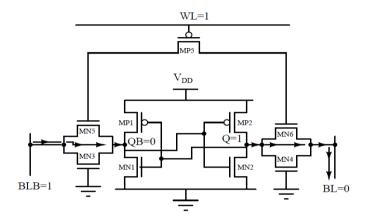

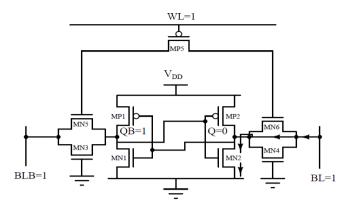

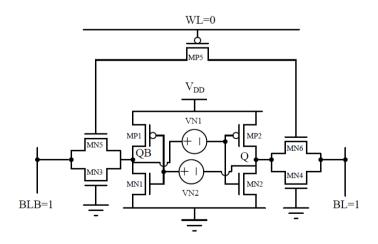

|    | 5.2  | Desig   | n and Oper             | ration of C6T                                                                        | 163     |

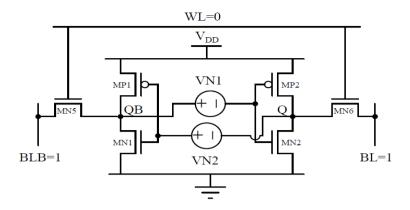

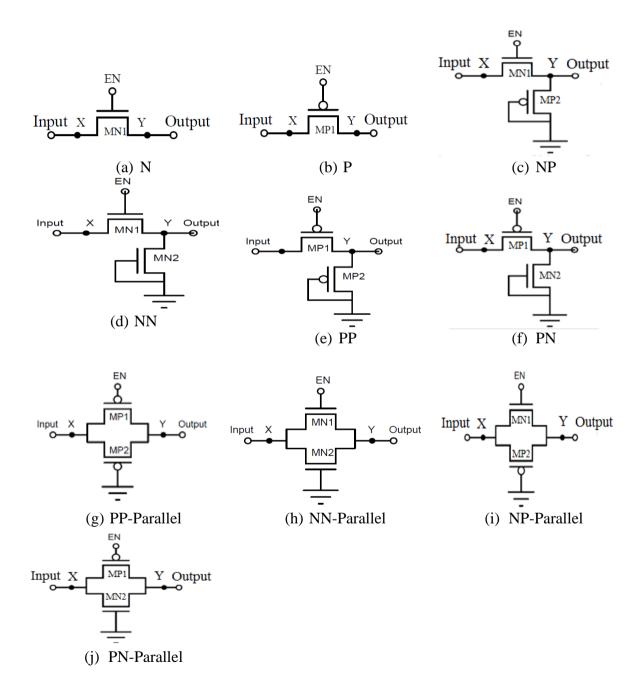

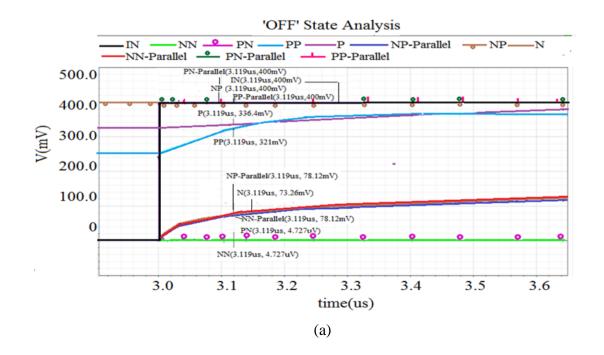

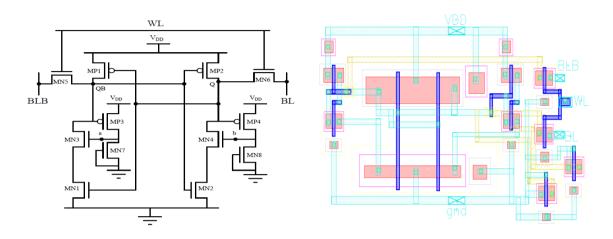

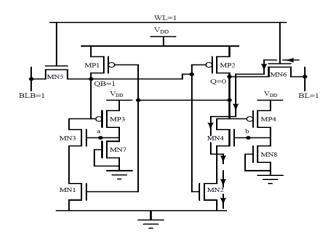

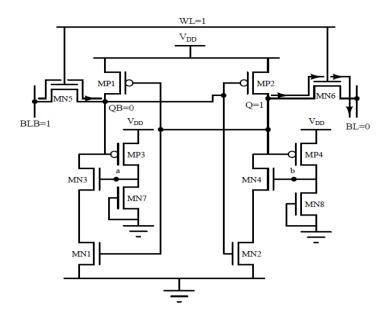

|    | 5.3  | Desig   | n and Oper             | ration of Proposed SRAM Cells at 45nm                                                | 167     |

|    |      | 5.3.1   | Design of              | Proposed MPT8T using PN Access Transistor                                            | 171     |

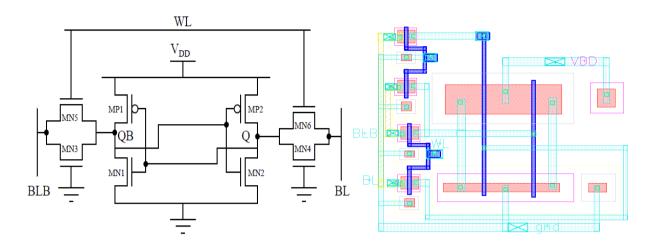

|    |      | 5.3.2   | Design of              | Proposed M8T using NN-Parallel Access Transistor                                     | 174     |

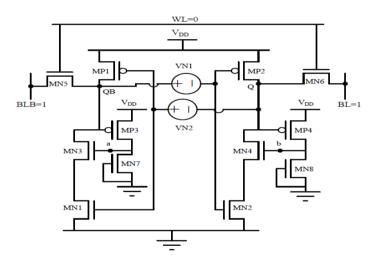

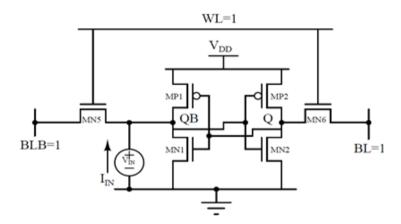

|    |      | 5.3.3   | Design of              | Proposed MI-12T                                                                      | 177     |

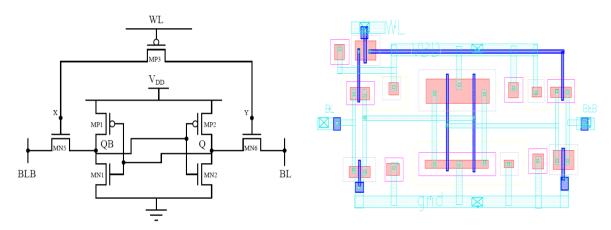

|    |      | 5.3.4   | Design of              | Proposed M7T                                                                         | 181     |

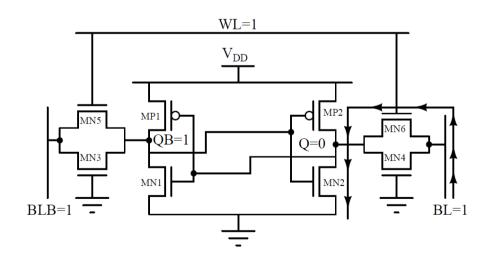

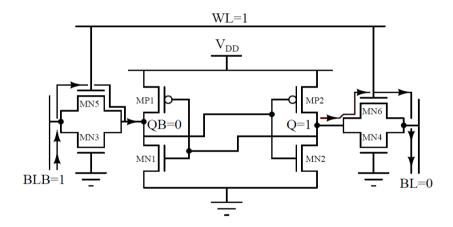

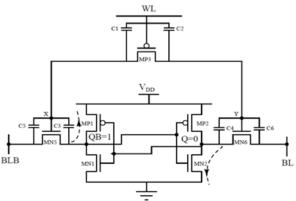

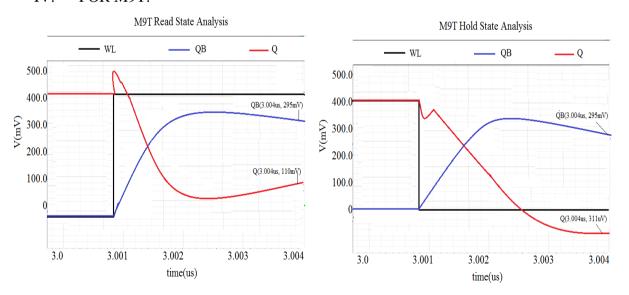

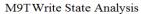

|    |      | 5.3.5   | Design of              | Proposed M9T                                                                         | 194     |

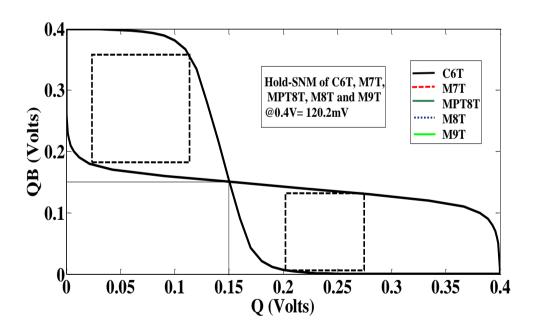

|    | 5.4. | Simul   | ation Resul            | lts and Discussion at 45 nm                                                          | 197     |

|    |      | 5.4.1.  | SRAM sta               | andby stability analysis (Hold stability)                                            | 198     |

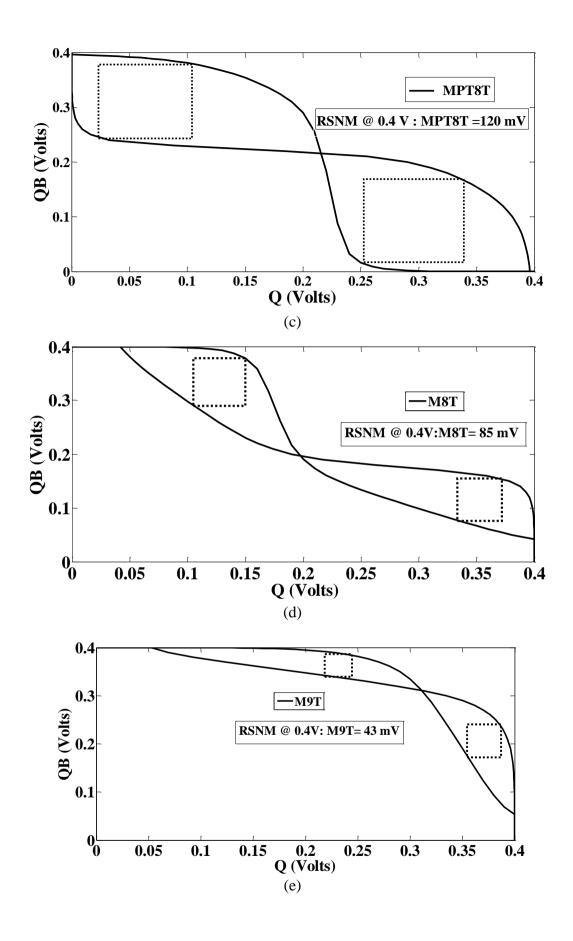

|    |      | 5.4.2.  | SRAM Re                | ead Stability Analysis                                                               | 201     |

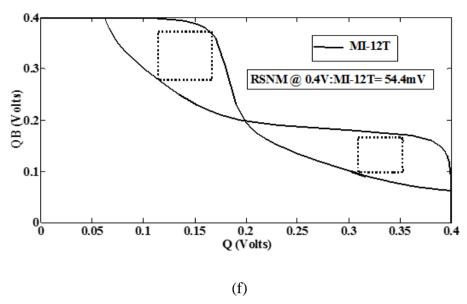

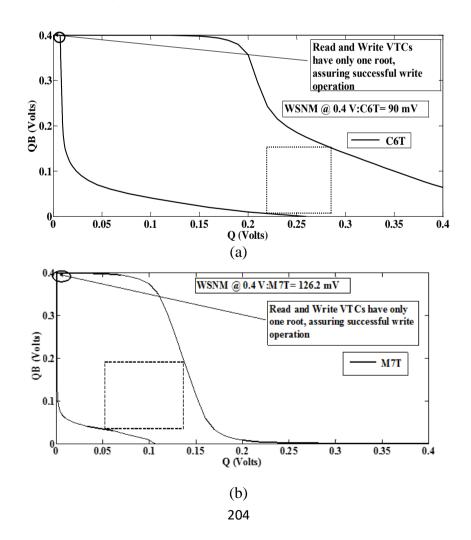

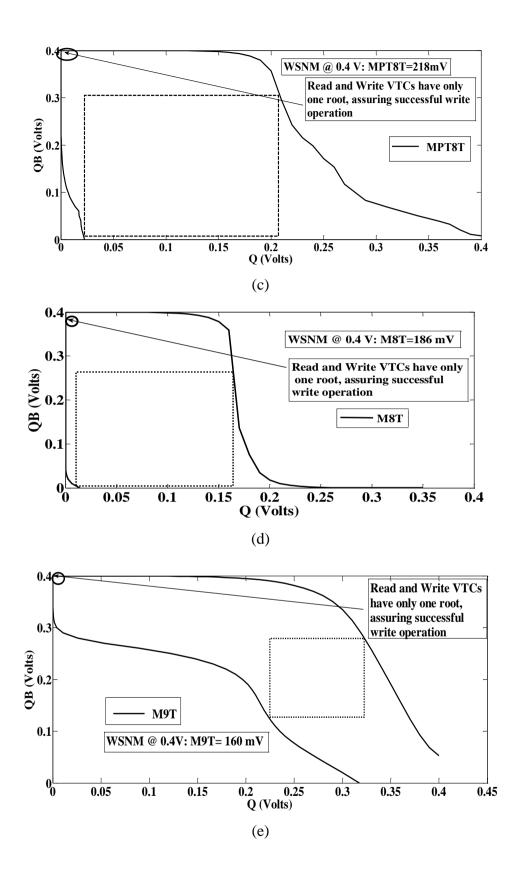

|    |      | 5.4.3.  | SRAM W                 | rite Ability Analysis                                                                | 204     |

|    |      | 5.4.4.  | Alternativ             | e Noise Margins                                                                      | 207     |

|    |      | 5.4.5.  | Read Acce              | ess Time (T <sub>RA</sub> ) with Variability                                         | 211     |

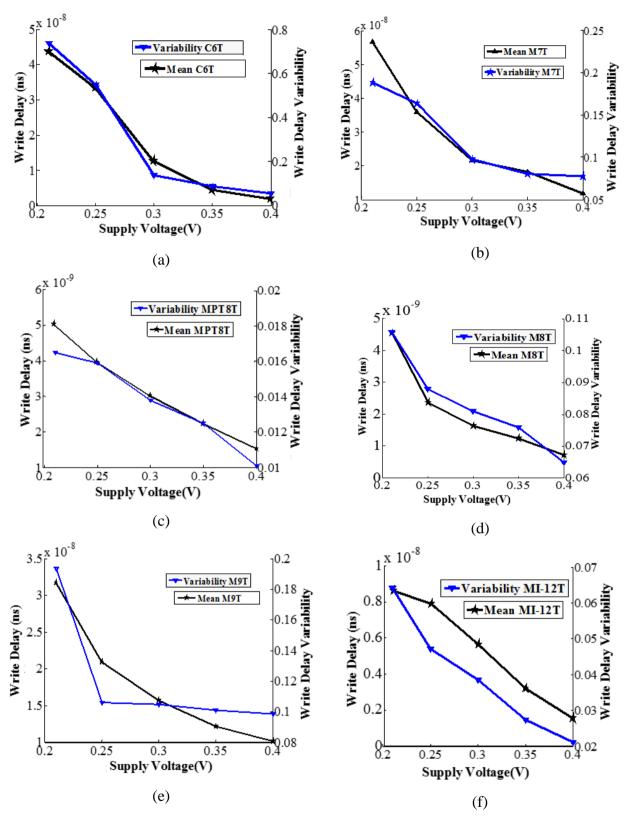

|    |      | 5.4.6.  | Write Acc              | ess Time (T <sub>WA</sub> ) with Variability                                         | 213     |

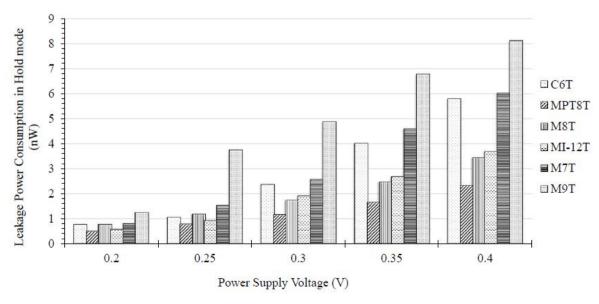

|    |      | 5.4.7.  | Leakage P              | Power Consumption in Hold mode                                                       | 215     |

|    | 5.5. | Analy   | tical Expre            | essions for HOLD, RSNM & WSNM of SRAM Cells                                          | 216     |

|    |      | 5.5.1.  | Analytical<br>12T SRAM | Expressions for Hold SNM of C6T, M7T, MPT8T, M8T, M9T and MI-M cells                 | 218     |

|    | 5.5.2. Analytical Expressions for RSNM of C6T, M7T, MPT8T, M8T, M9T and MI-<br>12T SRAM cells | 221     |

|----|-----------------------------------------------------------------------------------------------|---------|

|    | 5.5.3 Analytical Expressions for WSNM of C6T, M7T, MPT8T, M8T, M9T and MI-<br>12T SRAM cells  | 228     |

|    | 5.6. Final Results and Discussions                                                            | 235     |

|    | 5.7. Conclusions                                                                              | 245     |

|    | References                                                                                    | 250-254 |

| 6. | Conclusions & Future Scope of Work                                                            | 255-263 |

|    | 6.1. Conclusions on Adders                                                                    | 255     |

|    | 6.2. Conclusions on Multipliers                                                               | 257     |

|    | 6.3. Conclusions on SRAM Cells                                                                | 260     |

|    | 6.4. Future scope of the work                                                                 | 262     |

|    | Appendix A                                                                                    | 264     |

|    | Appendix B                                                                                    | 265     |

|    | Appendix C                                                                                    | 269     |

|    | Appendix D                                                                                    | 276     |

|    | Appendix E                                                                                    | 278     |

|    | Appendix F                                                                                    | 279     |

|    | List of Publications                                                                          | 283-284 |

|    | Publication in Peer Reviewed Journals                                                         | 283     |

|    | Publication in Peer Reviewed Conferences                                                      | 284     |

|    | Brief Biography of the Candidate                                                              | 285     |

|    | Brief Biography of the Supervisor                                                             | 286     |

|    | Brief Biography of the Co-Supervisor                                                          | 287     |

## **LIST OF TABLES**

| Table 2.1  | Comparison of various referenced CLA architectures                                                                         | 24  |

|------------|----------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.2  | Comparison of various referenced HCA architectures                                                                         | 25  |

| Table 2.3  | Comparison of various referenced KSA architectures                                                                         | 26  |

| Table 2.4  | Comparison of various referenced compressor designs                                                                        | 28  |

| Table 2.5  | Comparison of various referenced low power SRAM cells                                                                      | 32  |

| Table 3.1  | Simulation results for AND Gate                                                                                            | 59  |

| Table 3.2  | Simulation results for OR Gate                                                                                             | 59  |

| Table 3.3  | Simulation results for XOR Gate                                                                                            | 60  |

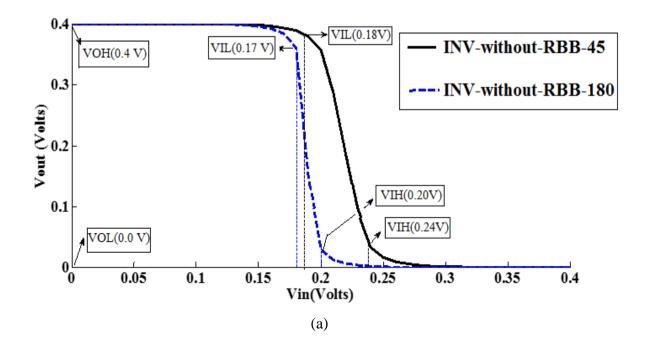

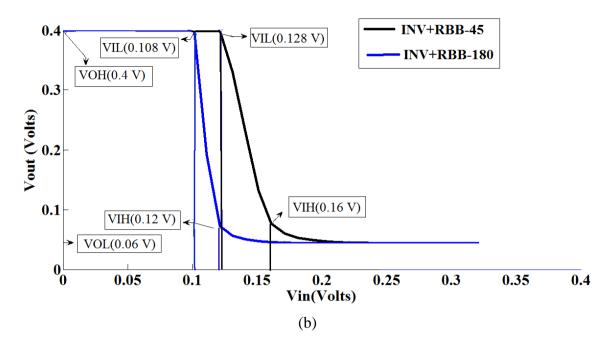

| Table 3.4  | Noise margin of CMOS Inverter with/without RBB                                                                             | 63  |

| Table 3.5  | Simulation results for Inverter with/without RBB at 0.4V                                                                   | 64  |

| Table 3.6  | Simulation results for AND Gate with RBB                                                                                   | 65  |

| Table 3.7  | Simulation results for OR Gate with RBB                                                                                    | 65  |

| Table 3.8  | Simulation results for XOR Gate with RBB                                                                                   | 65  |

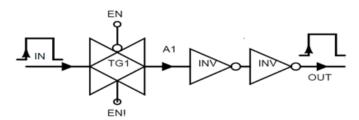

| Table 3.9  | Operations of TG-2INV block                                                                                                | 73  |

| Table 3.10 | Operations of PT-2INV block                                                                                                | 76  |

| Table 3.11 | Nomenclature used for the proposed designs of CLA                                                                          | 78  |

| Table 3.12 | Simulation results of CLA's at 45 nm technology                                                                            | 79  |

| Table 3.13 | Simulation results of CLA's at 180 nm technology                                                                           | 79  |

| Table 3.14 | Nomenclature used for the proposed designs of KSA                                                                          | 82  |

| Table 3.15 | Simulation results of KSA's at 45 nm technology                                                                            | 83  |

| Table 3.16 | Simulation results of KSA's at 180 nm technology                                                                           | 81  |

| Table 3.17 | Nomenclature used for the proposed designs of HCA                                                                          | 87  |

| Table 3.18 | Simulation results of HCA's at 45 nm technology                                                                            | 87  |

| Table 3.19 | Simulation results of HCA's at 180 nm technology                                                                           | 87  |

| Table 3.20 | Simulation results of adder's at 45 nm technology                                                                          | 89  |

| Table 3.21 | Simulation results of adder's at 180 nm technology                                                                         | 90  |

| Table 3.22 | Comparative table between proposed and referenced adder designs at 45 nm                                                   | 91  |

| Table 3.23 | Comparative table between proposed and referenced adder designs at 180 nm                                                  | 91  |

| Table 4.1  | Truth table of different Compressors (2-2, 3-2, 4-2, 5-2, 6-2, and 7-2)                                                    | 124 |

| Table 4.2  | Simulation results of LOC and modified HOC Designs                                                                         | 131 |

| Table 4.3. | Comparative results of proposed modified compressor with designs of published references at 45 nm technology               | 132 |

| Table 4.4  | Comparative results of proposed LOC and modified HOC compressors with designs of published references at 180 nm technology | 133 |

| Table 4.5    | Nomenclature used for the proposed designs of Wallace tree multiplier                                                              | 137 |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 4.6    | Simulation results of Wallace tree multipliers using 45 nm technology at $V_{\rm DD}\!\!=\!\!0.4V$                                 | 138 |

| Table 4.7    | Simulation results of Wallace tree multipliers uisng 180 nm technology at $V_{\rm DD}\!\!=\!\!0.4V$                                | 138 |

| Table 4.8    | Nomenclature used for the proposed designs of Dadda multiplier                                                                     | 142 |

| Table 4.9    | Simulation results of Dadda multipliers using 45 nm technology at $V_{DD}$ =0.4 $V$                                                | 143 |

| Table 4.10   | Simulation results of Dadda multipliers using 180 nm technology at $V_{DD}$ =0.4 $V$                                               | 143 |

| Table 4.11   | Comparative table between proposed and referenced multiplier designs at 45 nm                                                      | 145 |

| Table 4.12   | Comparative table between proposed and referenced multiplier designs at 180 nm                                                     | 145 |

| Table 5.1(a) | Comparison of various SRAM cells at 180 nm technology at 0.4 V                                                                     | 160 |

| Table 5.1(b) | Comparison of low power SRAM cells at 180 nm technology at 0.4 V                                                                   | 161 |

| Table 5.2    | Results of conventional and modified access transistor (P, NP, PP, PN, and NN) at $0.4 \text{V}$ supply for $45 \text{ nm}$        | 169 |

| Table 5.3    | Generation of Voltages at node X and node Y in write, read, and hold operation                                                     | 188 |

| Table 5.4    | Comparative analysis of RSNM, at 0.4V                                                                                              | 203 |

| Table 5.5    | Comparative analysis of WSNM, at 0.4V                                                                                              | 206 |

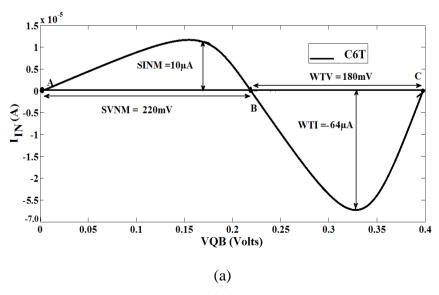

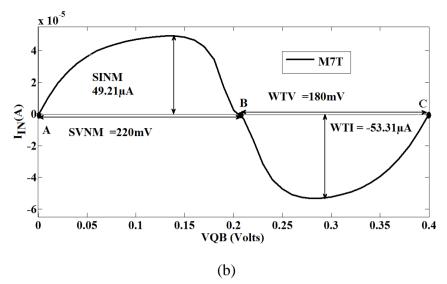

| Table 5.6    | Comparative analysis of SVNM, SINM, WTI and WTV at 0.4V                                                                            | 210 |

| Table 5.7    | Comparison of WTV, WTI with WSNM                                                                                                   | 210 |

| Table 5.8    | Comparison of SVNM, SINM, with RSNM                                                                                                | 211 |

| Table 5.9    | Comparative analysis of read delay and its variability for all proposed SRAM cells with C6T                                        | 213 |

| Table 5.10   | Comparative analysis of write delay and its variability for all proposed SRAM cells with C6T                                       | 215 |

| Table 5.11   | Comparative analyses of leakage power consumptions in hold mode at 0.4 V supply                                                    | 216 |

| Table 5.12   | Comparison of hold SNM between simulated and estimated values through analytical and regression equation at $0.4\mathrm{V}$        | 221 |

| Table 5.13   | Comparison of RSNM between simulated and estimated values through analytical and regression equation at $0.4\mbox{\ensuremath{V}}$ | 227 |

| Table 5.14   | Comparison of WSNM between simulated and estimated values through analytical and regression equation at 0.4V                       | 234 |

| Table 5.15   | Comparison of proposed with referenced SRAM cells (for 7T, 8T, 9T and 12T configurations) at 45 nm technology, $V_{DD}\!\!=\!0.4V$ | 236 |

| Table 5.16   | Write ability metric of proposed SRAM cells at 45 nm                                                                               | 238 |

| Table 5.17   | Read stability metric of proposed SRAM cells at 45 nm                                                                              | 239 |

| Table 5.18   | Percentage comparison of all proposed SRAM cells with C6T at 45 nm                                                                 | 240 |

| Table 5.19   | Write ability metric of SRAM cells at 180 nm                                                                                       | 242 |

| Table 5.20   | Read stability metric of SRAM cells at 180 nm                                                                                      | 243 |

## **LIST OF FIGURES**

| Figure 1.1  | A cross-sectional view of an n-channel MOSFET                                                | 2  |

|-------------|----------------------------------------------------------------------------------------------|----|

| Figure 1.2  | A cross-sectional view of an n-channel MOSFET operated in sub-threshold region               | 3  |

| Figure 1.3  | $I_{D,SUB}-V_{DS}$ characteristics in sub-threshold operation region                         | 5  |

| Figure 1.4  | $I_{D, SUB}$ - $V_{GS}$ Characteristics                                                      | 5  |

| Figure 1.5  | Sub-threshold slope plot at 180 nm technology                                                | 6  |

| Figure 1.6  | CMOS inverter mode for dynamic power consumption                                             | 7  |

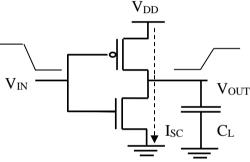

| Figure 1.7  | CMOS inverter mode for short-circuit power consumption                                       | 8  |

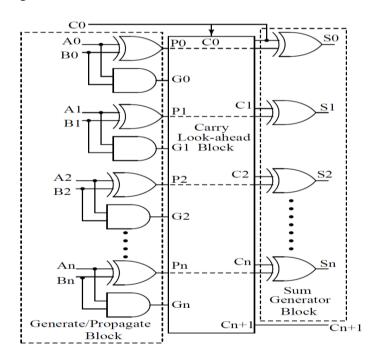

| Figure 3.1  | Block diagram of n-bit CLA                                                                   | 47 |

| Figure 3.2  | Block diagram of n-bit KSA                                                                   | 49 |

| Figure 3.3  | Block diagram of n-bit HCA                                                                   | 50 |

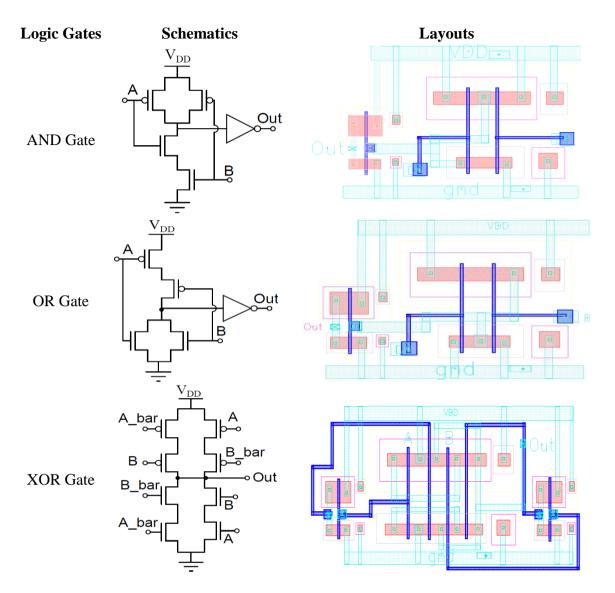

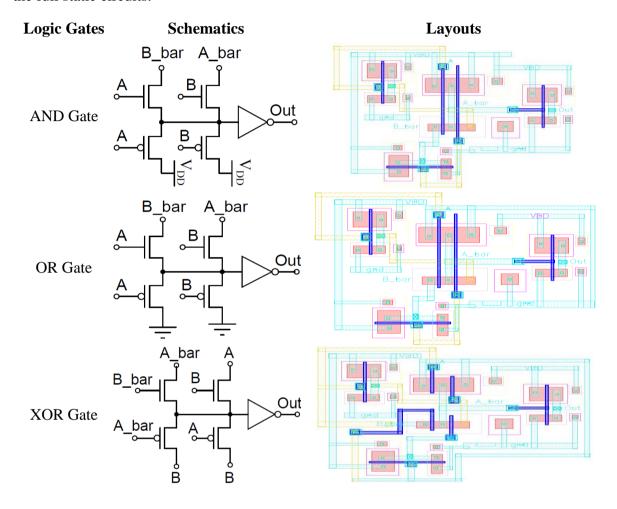

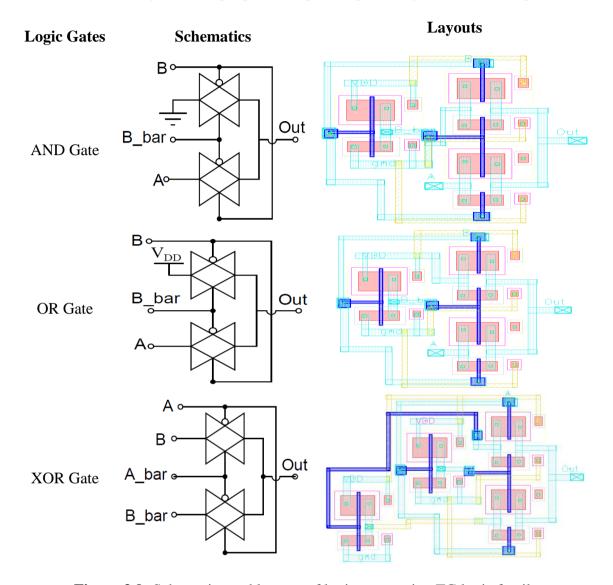

| Figure 3.4  | Schematics and layouts of logic gates using Static-CMOS logic family                         | 53 |

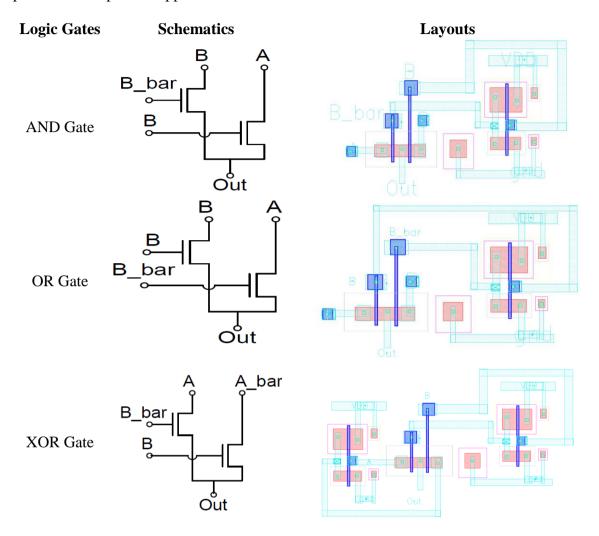

| Figure 3.5  | Schematics and layouts of logic gates using PT logic family                                  | 54 |

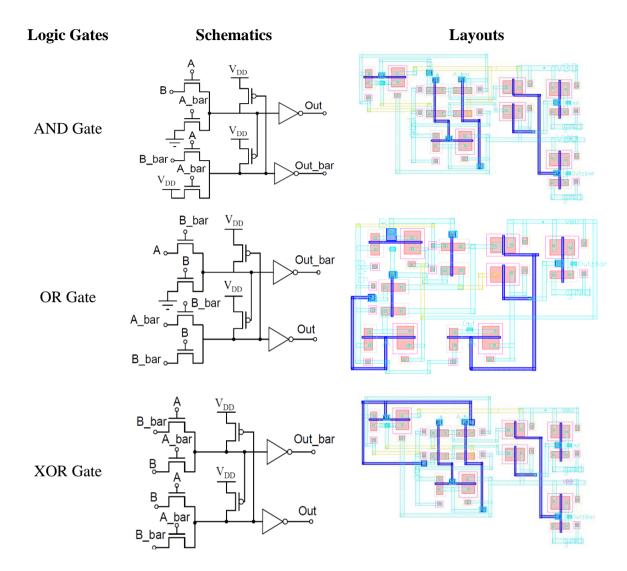

| Figure 3.6  | Schematics and layouts of logic gates using CPL logic family                                 | 55 |

| Figure 3.7  | Schematics and layouts of logic gates using SRPL logic family                                | 56 |

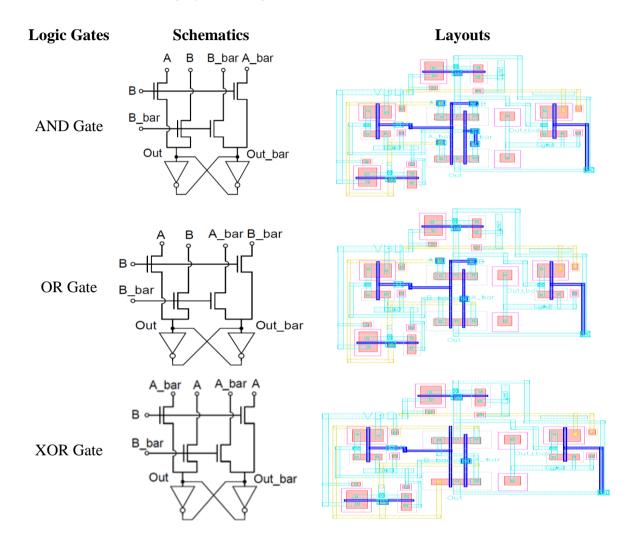

| Figure 3.8  | Schematics and layouts of logic gates using DPL logic family                                 | 57 |

| Figure 3.9  | Schematics and layouts of logic gates using TG logic family                                  | 58 |

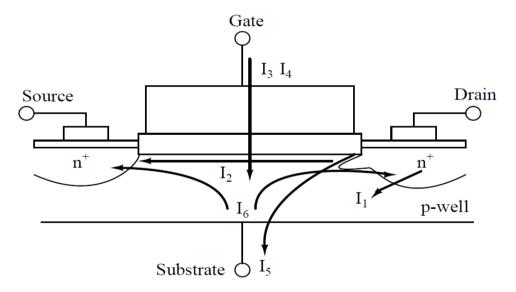

| Figure 3.10 | Cross sectional view of N-MOS with all leakage currents                                      | 61 |

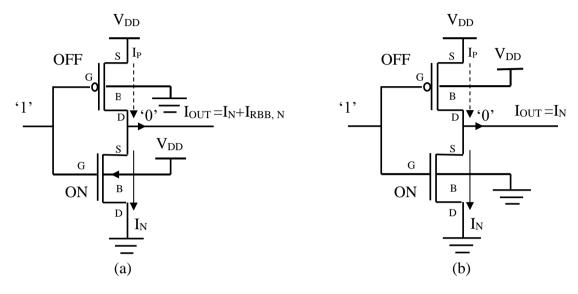

| Figure 3.11 | Schematic diagram of CMOS inverter (a) with RBB (b) without RBB                              | 62 |

| Figure 3.12 | VTC's of CMOS inverter (a) with RBB (b) without RBB                                          | 63 |

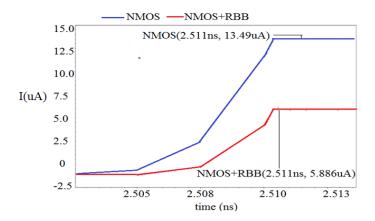

| Figure 3.13 | Current characteristics of NMOS in CMOS inverter with RBB/without RBB at 45 nm technology $$ | 64 |

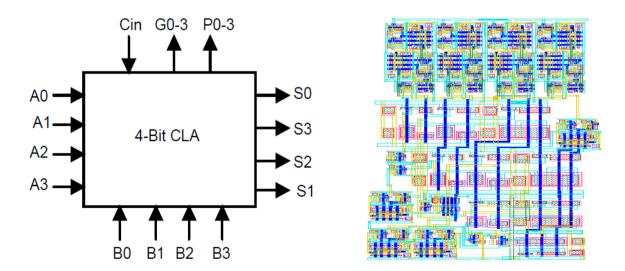

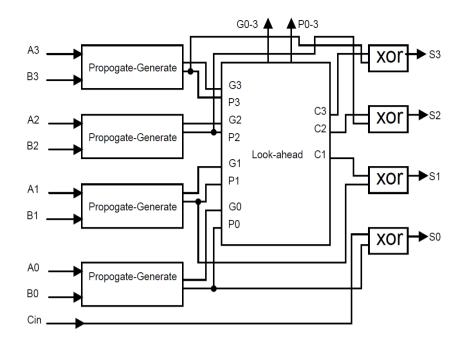

| Figure 3.14 | Basic block diagram of 4-bit CLA                                                             | 66 |

| Figure 3.15 | Internal blocks of 4-bit CLA                                                                 | 67 |

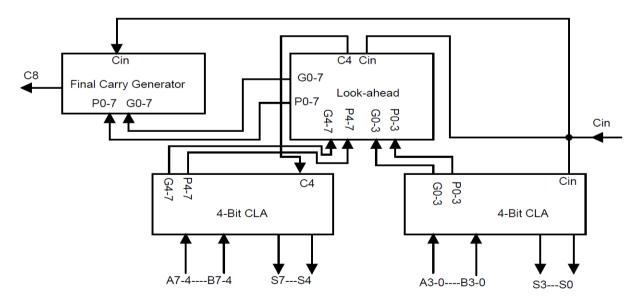

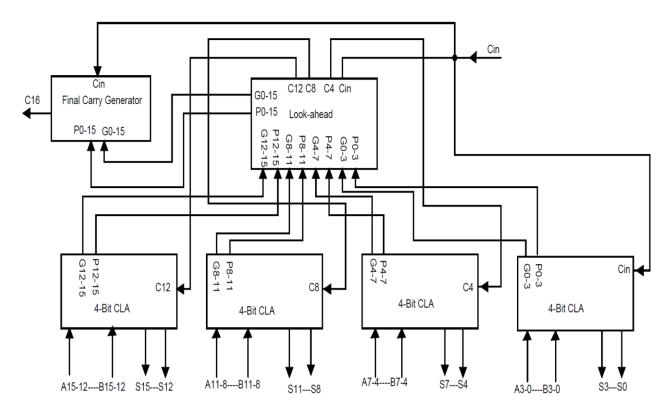

| Figure 3.16 | Block diagram of 8-bit CLA built using 4-bit CLA unit                                        | 67 |

| Figure 3.17 | Block diagram of 16-bit CLA built using 4-bit CLA unit                                       | 68 |

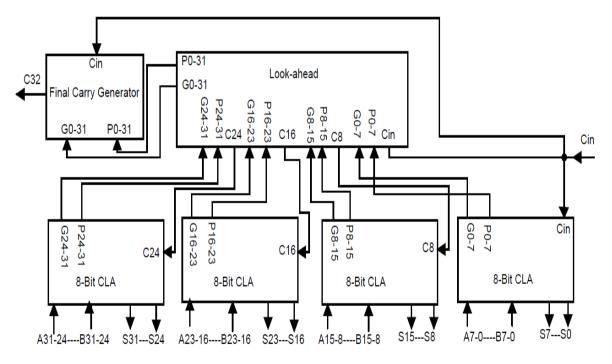

| Figure 3.18 | Block diagram of a 32-bit CLA built using 8-bit CLA unit                                     | 68 |

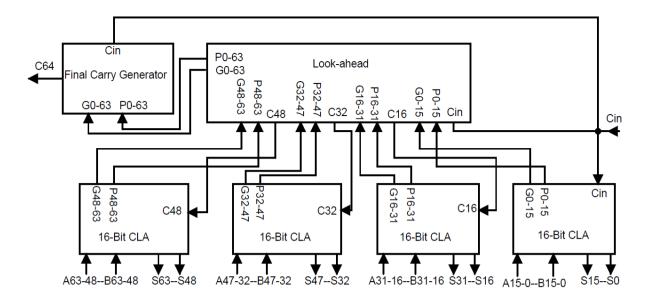

| Figure 3.19 | Block diagram of a 64-bit CLA built using 16-bit CLA unit                                    | 69 |

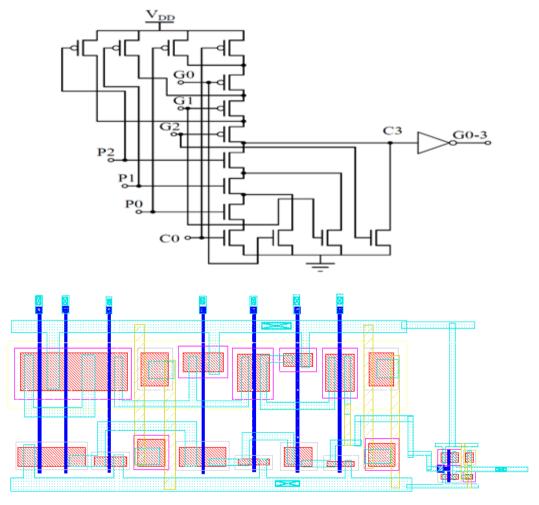

| Figure 3.20 | Circuit diagram of 4-bit group generate                                                      | 70 |

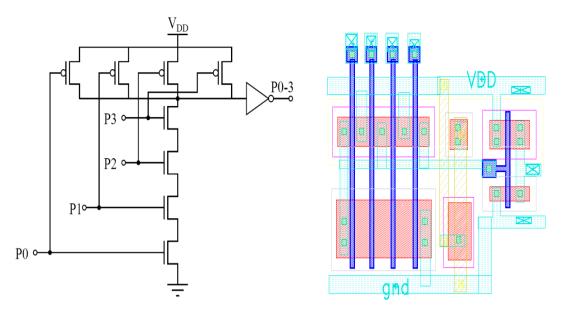

| Figure 3.21 | Circuit diagram of 4-bit group propagate                                                     | 71 |

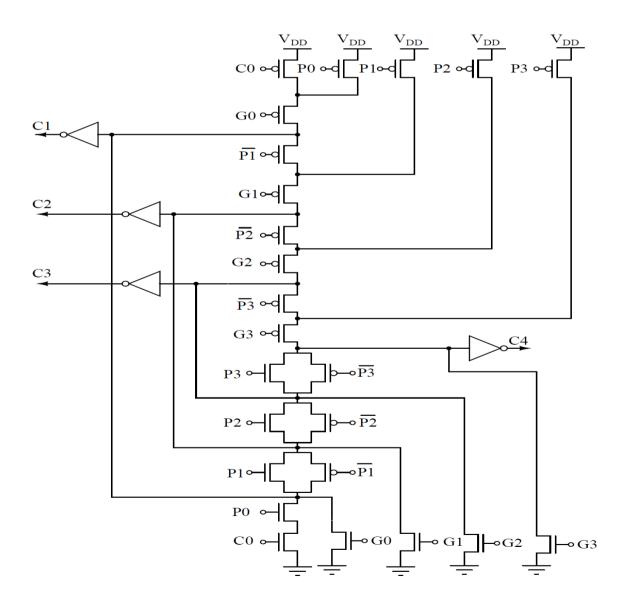

| Figure 3.22 | Circuit diagram of 4-bit carry generator                                                     | 72 |

| Figure 3.23 | Circuit diagram of bit-wise generate/propagate                                               | 72 |

| Figure 3.24 | Circuit diagram of bit-wise sum-generator                                                    | 72 |

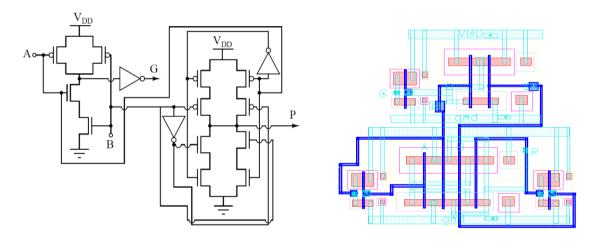

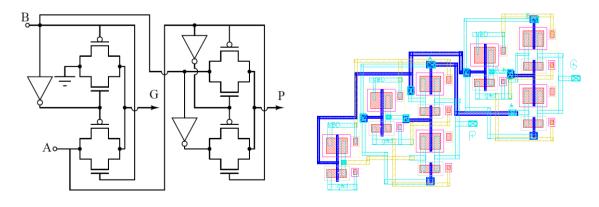

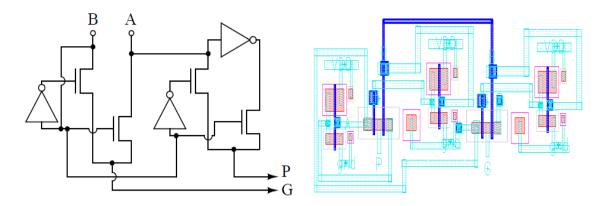

| Figure 3.25 | TG-2INV block                                                                                | 73 |

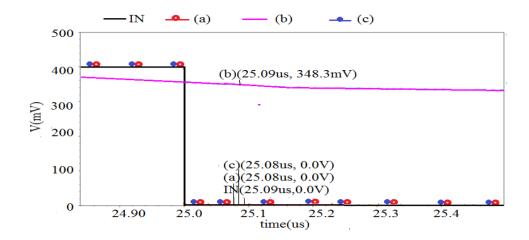

| Figure 3.26 | Graph for TG-2INV block at OFF condition                                                     | 74 |

| Figure 3.27 | Circuit diagram of bit-wise generate/propagate                                                                                                                          | 74  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 3.28 | Circuit diagram of bit-wise sum-generator                                                                                                                               | 75  |

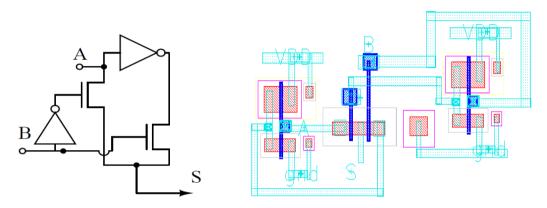

| Figure 3.29 | PT-2INV block                                                                                                                                                           | 75  |

| Figure 3.30 | Graph for PT-2INV block at OFF condition                                                                                                                                | 76  |

| Figure 3.31 | Circuit diagram of bit-wise generate/propagate                                                                                                                          | 77  |

| Figure 3.32 | Circuit diagram of bit-wise sum-generator                                                                                                                               | 77  |

| Figure 3.33 | The overall power consumption, propagation delay and power-delay product graphs of CLA at 45 nm $\!/$ 180 nm technology                                                 | 80  |

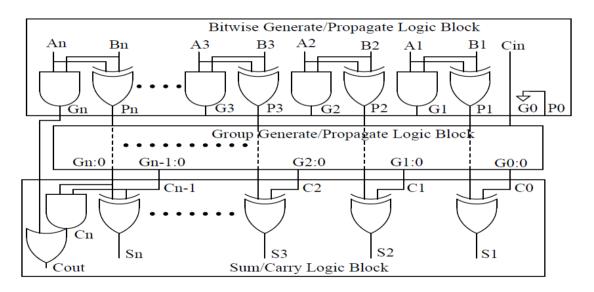

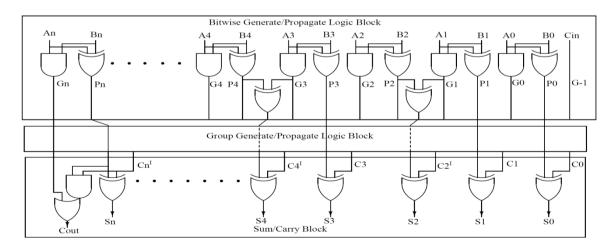

| Figure 3.34 | Internal architecture of KSA                                                                                                                                            | 81  |

| Figure 3.35 | The overall power consumption, propagation delay and power-delay product graphs of KSA at 45 nm $\!\!/$ 180 nm technology                                               | 85  |

| Figure 3.36 | Internal architecture of HCA                                                                                                                                            | 86  |

| Figure 3.37 | The overall power consumption, propagation delay and power-delay product graphs of HCA at 45 nm $\!/$ 180 nm technology                                                 | 89  |

| Figure 3.38 | The power consumption graph between CLA, KSA and HCA at 45 nm / 180 nm technology (a) using Static-CMOS logic (b) using HYB-TG logic (c) using HYB-PT logic             | 92  |

| Figure 3.39 | The propagation delay graph between CLA, KSA and HCA at 45 nm / 180 nm technology (a) using Static-CMOS logic (b) using HYB-TG logic (c) using HYB-PT logic             | 93  |

| Figure 3.40 | The power-delay product graph between CLA, KSA and HCA at 45 nm / 180 nm technology (a) using Static-CMOS logic (b) using HYB-TG logic (c) using HYB-PT logic           | 94  |

| Figure 3.41 | DSE chart of all published referenced and proposed 32-bit CLA, KSA and HCA architecture using different logic design styles (a) power (b) delay (c) power-delay product | 100 |

| Figure 4.1  | Block diagram of n x n bit multiplier                                                                                                                                   | 105 |

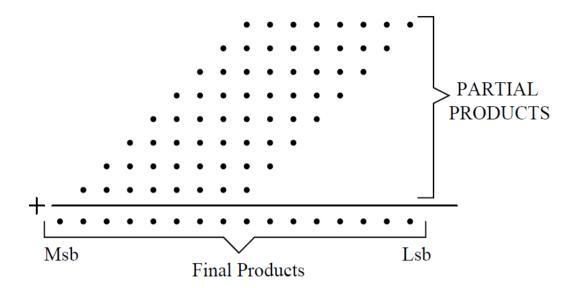

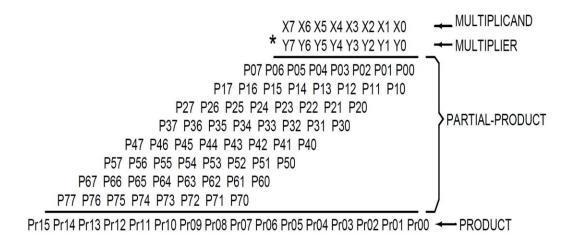

| Figure 4.2  | Partial Products generation of 8x8-bit simple multiplication                                                                                                            | 108 |

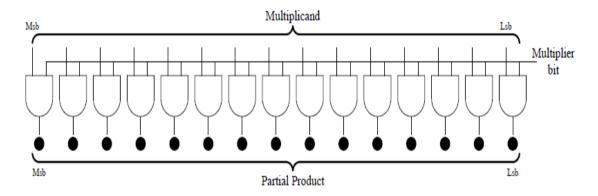

| Figure 4.3  | Partial Products selection logic for simple multiplication                                                                                                              | 108 |

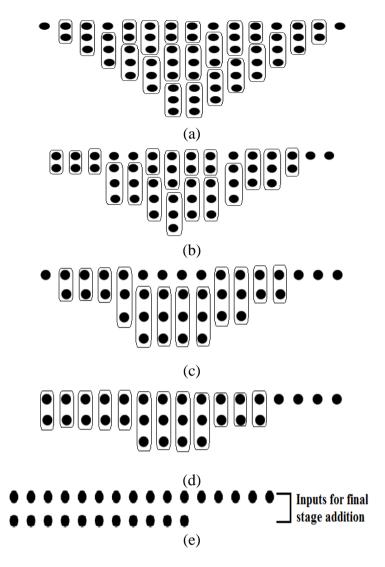

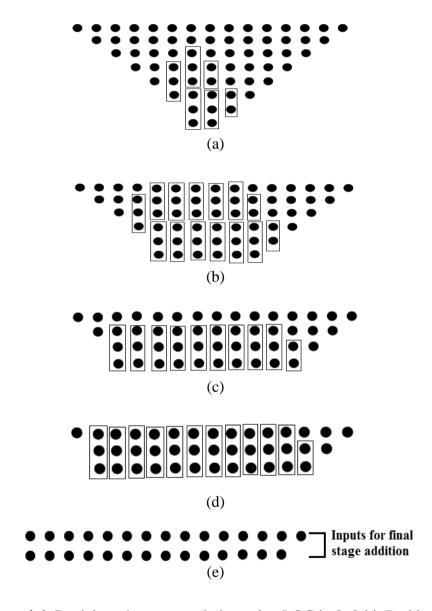

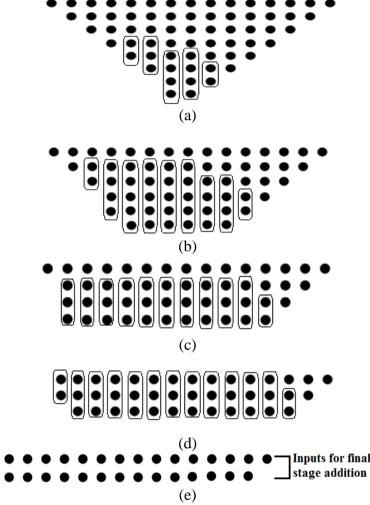

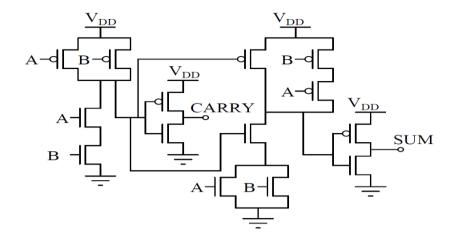

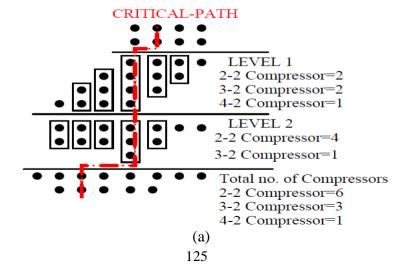

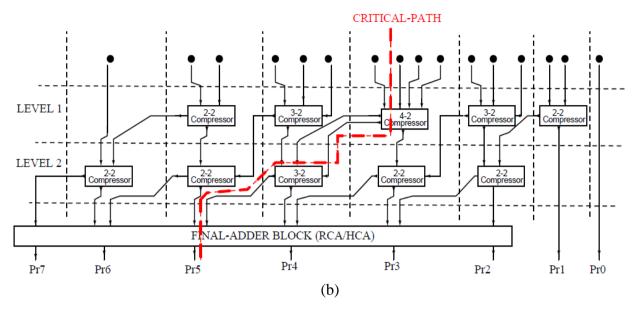

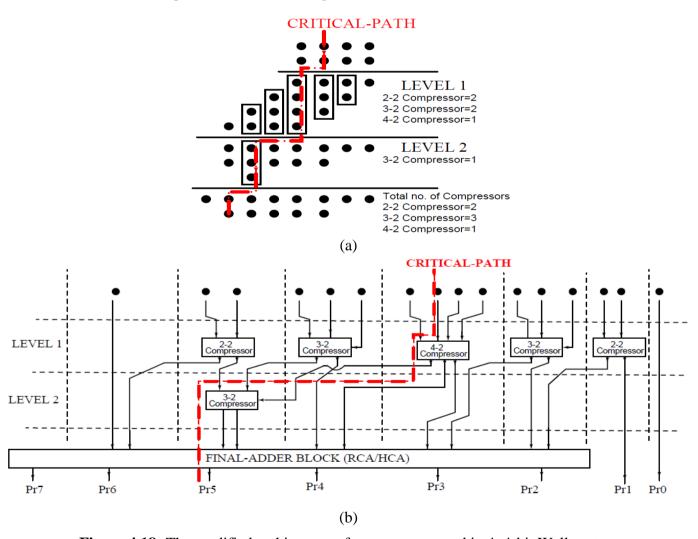

| Figure 4.4  | Partial product accumulation using LOC's in 8x8-bit Wallace tree                                                                                                        | 110 |

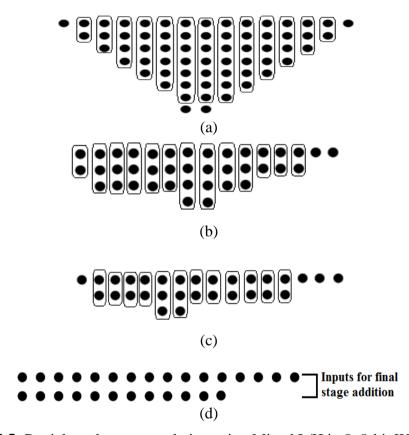

| Figure 4.5  | Partial product accumulation using Mixed L/H in 8x8-bit Wallace tree                                                                                                    | 111 |

| Figure 4.6  | Partial product accumulation using LOC's in 8x8-bit Dadda tree                                                                                                          | 113 |

| Figure 4.7  | Partial product accumulation using Mixed L/H in 8x8-bit Dadda tree                                                                                                      | 114 |

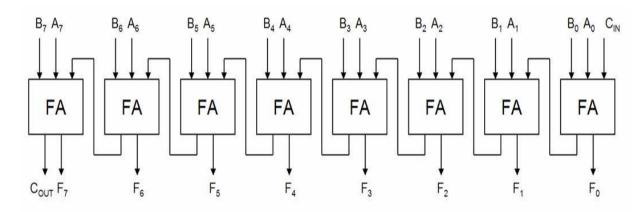

| Figure 4.8  | Block level diagram of 8-bit RCA                                                                                                                                        | 116 |

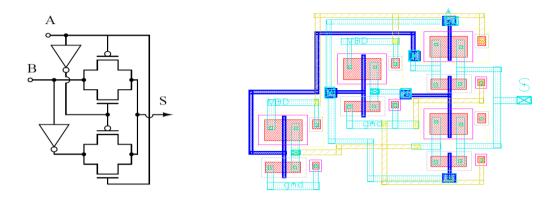

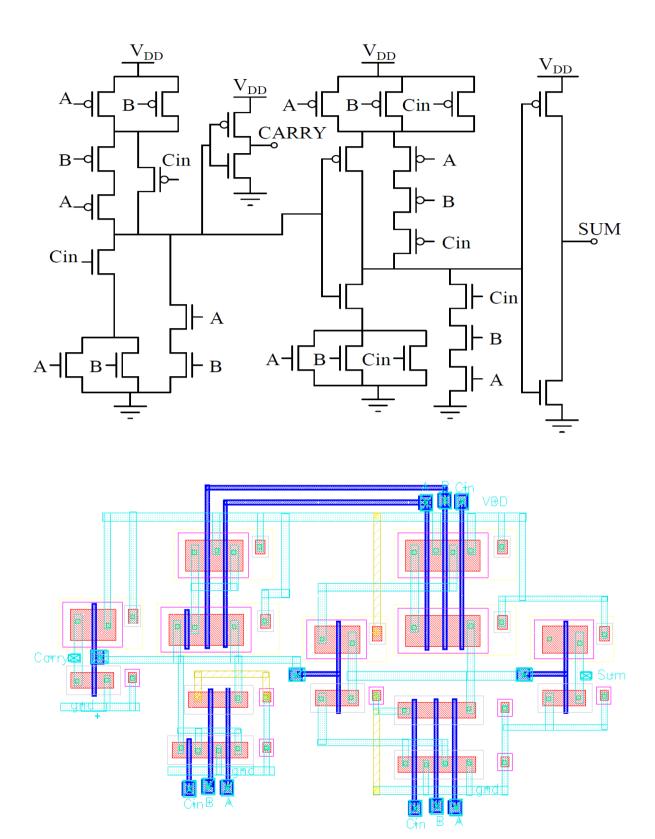

| Figure 4.9  | Schematic and layout of 2-2 LOC using Static-CMOS logic                                                                                                                 | 118 |

| Figure 4.10 | Schematics and layouts of 3-2 LOC using Static-CMOS logic                                                                                                               | 119 |

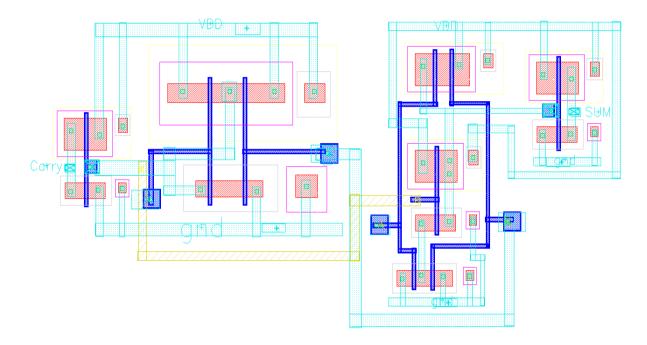

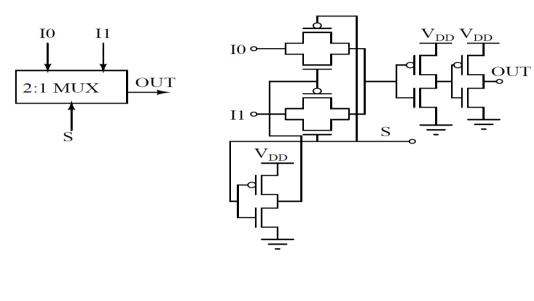

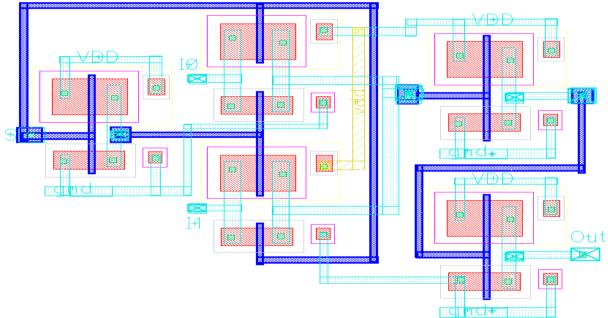

| Figure 4.11 | Schematic and layout of modified 2:1MUX using HYB-TG logic                                                                                                              | 120 |

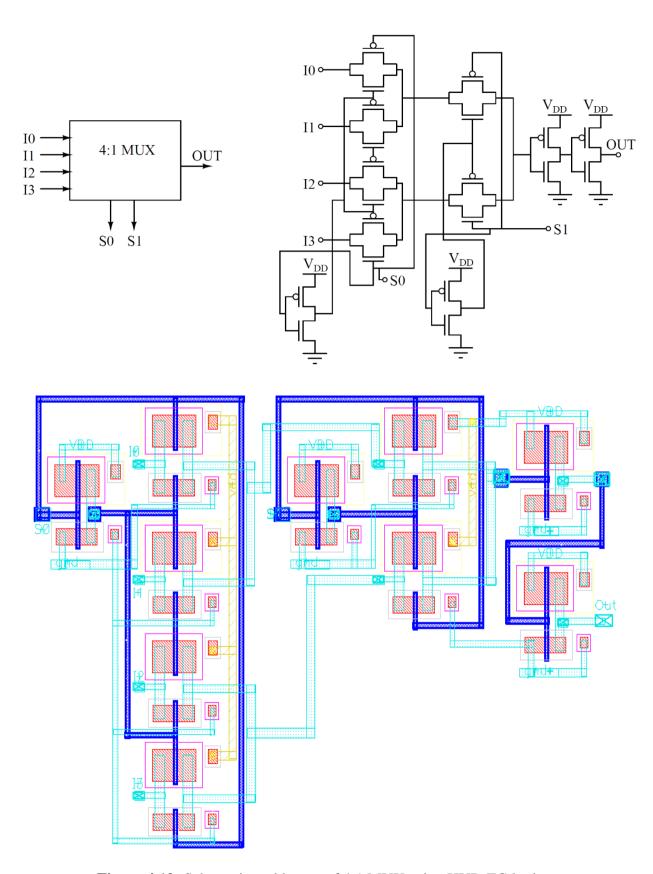

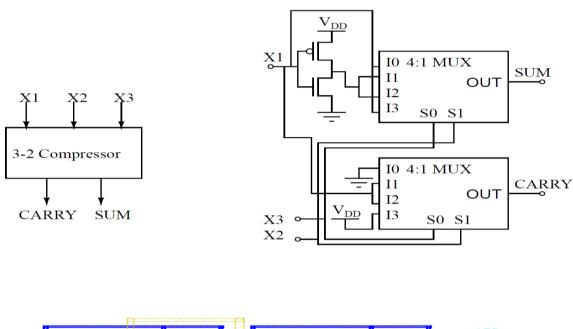

| Figure 4.12 | Schematic and layout of modified 4:1 MUX using HYB-TG logic                                                                                                             | 121 |

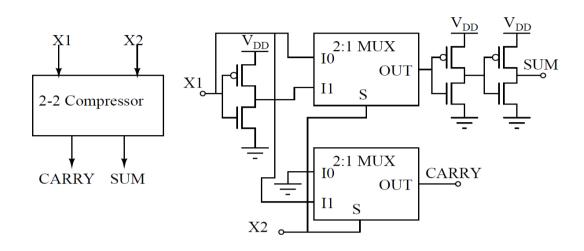

| Figure 4.13 | Schematic and layout of 2-2 LOC using HYB-TG logic                                                                                                                      | 122 |

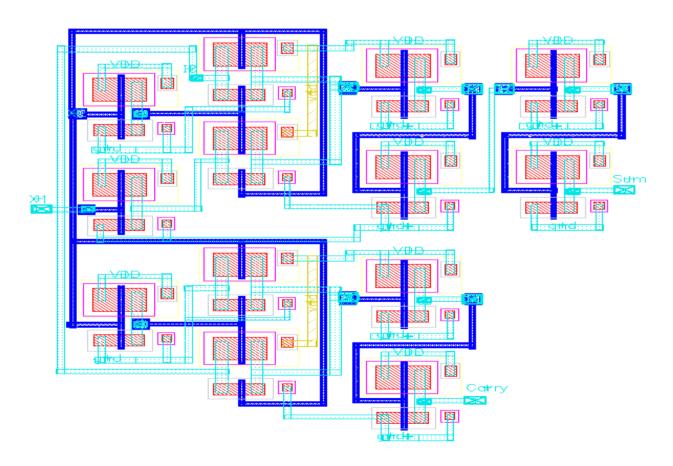

| Figure 4.14 | Schematic and layout of 3-2 LOC using HYB-TG logic                                                                                                                      | 123 |

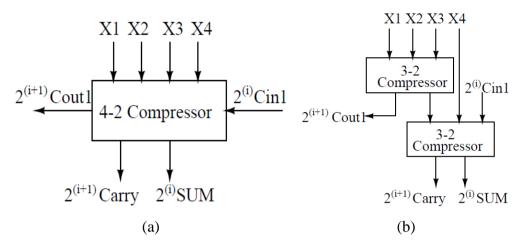

| Figure 4.15 | The conventional architecture of 4-2 compressors                                                                                             | 125 |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.16 | The conventional architecture of compressors used in 4x4-bit Wallace tree multiplier                                                         | 126 |

| Figure 4.17 | The modified architecture of 4-2 compressors                                                                                                 | 126 |

| Figure 4.18 | The modified architecture of compressors used in 4x4-bit Wallace tree multiplier                                                             | 127 |

| Figure 4.19 | The Schematics and layouts of modified HOC''s                                                                                                | 130 |

| Figure 4.20 | Multiplication of 8x8-bit multiplier                                                                                                         | 134 |

| Figure 4.21 | Block diagram of Wallace tree using LOC                                                                                                      | 135 |

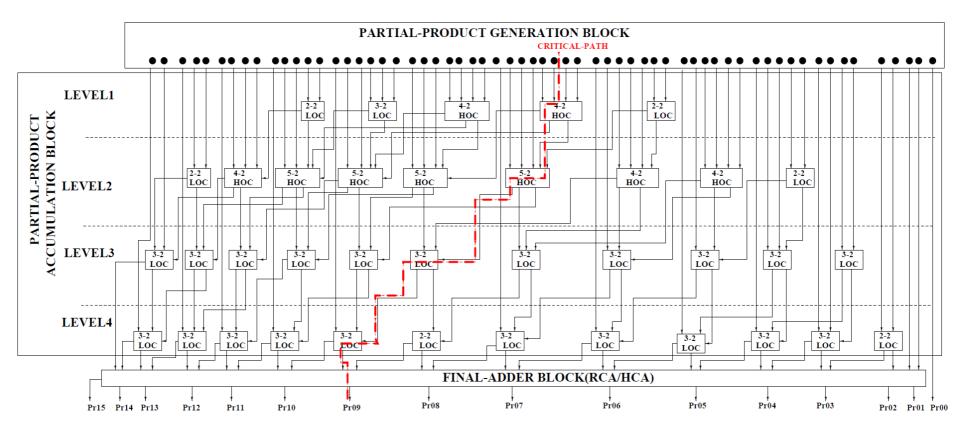

| Figure 4.22 | Block diagram of Wallace tree using Mixed L/H                                                                                                | 136 |

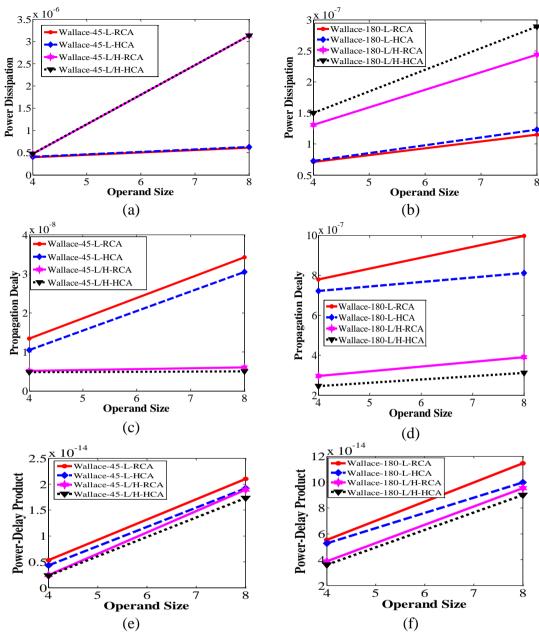

| Figure 4.23 | The overall power consumption, propagation delay and power-delay product graphs of Wallace tree multipliers at 45 nm $\!/$ 180 nm technology | 139 |

| Figure 4.24 | Block diagram of Dadda tree using LOC                                                                                                        | 140 |

| Figure 4.25 | Block diagram of Dadda tree using Mixed L/H                                                                                                  | 141 |

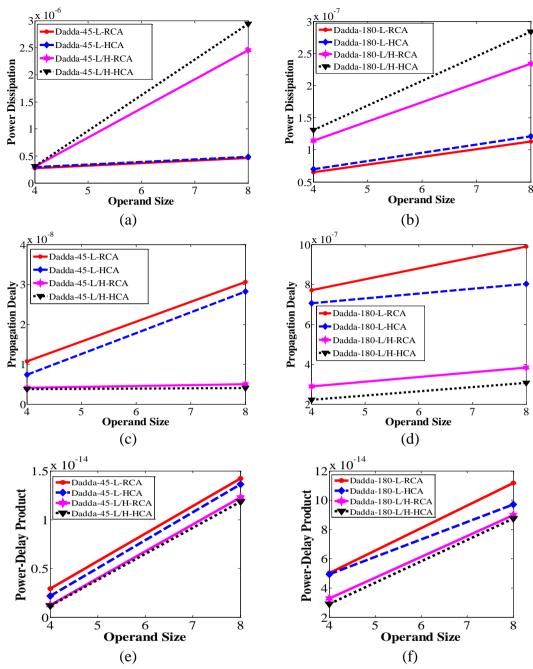

| Figure 4.26 | The overall power consumption, propagation delay and power-delay product graphs of Dadda multipliers at 45 nm $\!/$ 180 nm technology        | 144 |

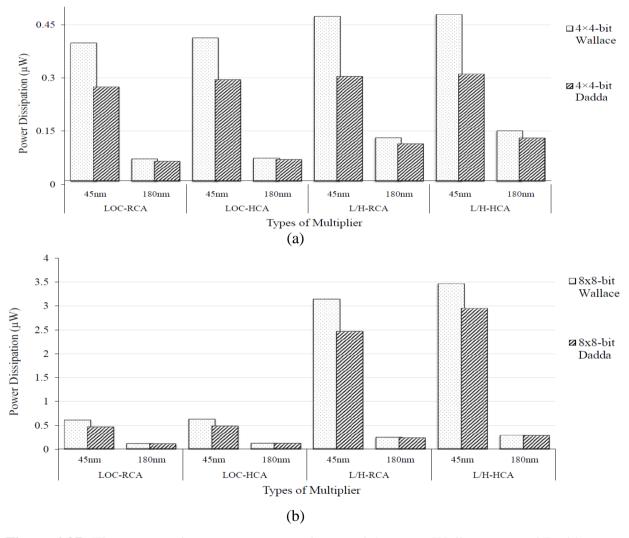

| Figure 4.27 | The comparative power consumption graph between Wallace tree and Dadda multipliers for (a) 4x4-bit (b) 8x8-bit                               | 146 |

| Figure 4.28 | The comparative propagation delay graph between Wallace tree and Dadda multipliers for (a) $4x4$ -bit (b) $8x8$ -bit                         | 147 |

| Figure 4.29 | The comparative power-delay product graph between Wallace tree and Dadda multipliers for (a) 4x4-bit (b) 8x8-bit                             | 148 |

| Figure 4.30 | DSE chart of all published referenced and proposed 8x8-bit Wallace tree and Dadda architectures (a) power (b) delay (c) power-delay product  | 155 |

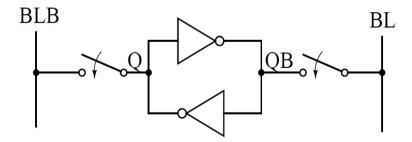

| Figure 5.1  | Basic SRAM cell                                                                                                                              | 163 |

| Figure 5.2  | Schematic and Layout of C6T                                                                                                                  | 164 |

| Figure 5.3  | Test circuit for read operation of C6T                                                                                                       | 165 |

| Figure 5.4  | Test circuit for write operation of C6T                                                                                                      | 166 |

| Figure 5.5  | Test circuit for measurement of hold SNM of C6T                                                                                              | 167 |

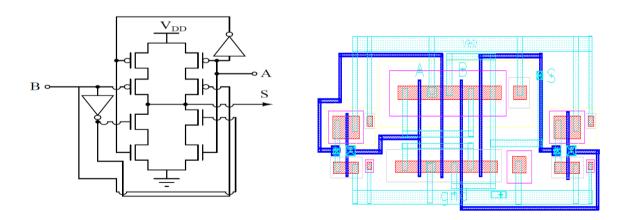

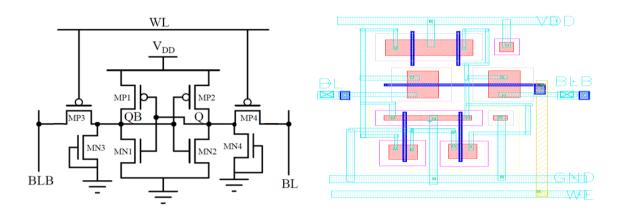

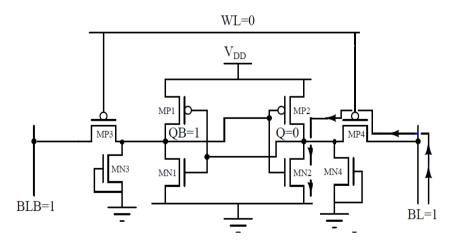

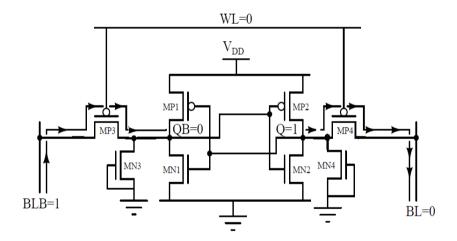

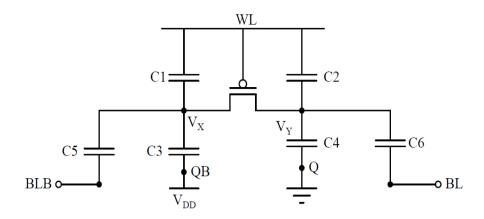

| Figure 5.6  | Schematics of access transistor pairs                                                                                                        | 168 |

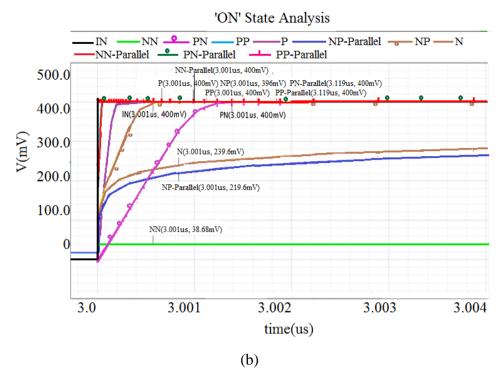

| Figure 5.7  | ON/OFF state analysis of access transistors                                                                                                  | 171 |

| Figure 5.8  | Schematic and layout of MPT8T                                                                                                                | 172 |

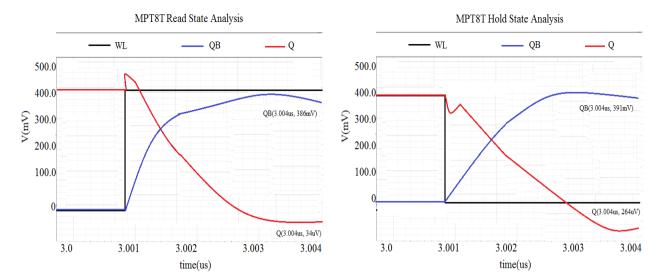

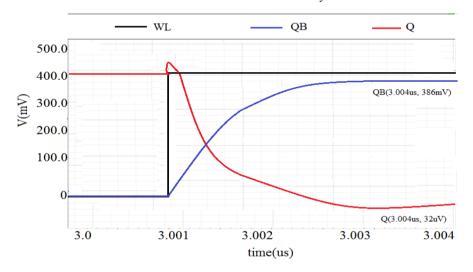

| Figure 5.9  | Test circuit for read operation of MPT8T                                                                                                     | 172 |

| Figure 5.10 | Test circuit for write operation of MPT8T                                                                                                    | 173 |

| Figure 5.11 | Test circuit for measurement of hold SNM of MPT8T                                                                                            | 174 |

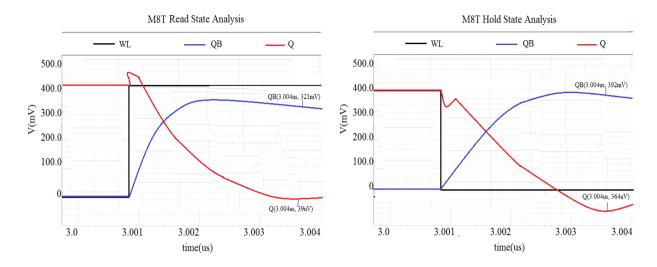

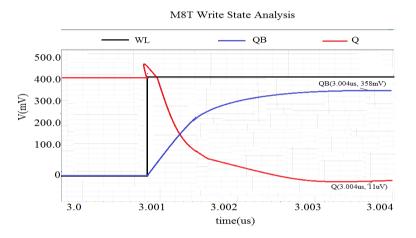

| Figure 5.12 | Schematic and layout of M8T                                                                                                                  | 175 |

| Figure 5.13 | Test circuit for read operation of M8T                                                                                                       | 175 |

| Figure 5.14 | Test circuit for write operation of M8T                                                                                                      | 176 |

| Figure 5.15 | Test circuit for measurement of hold SNM of M8T                                                                                              | 177 |

| Figure 5.16 | Schematic and layout of MI-12T                                                                                                               | 178 |

| Figure 5.17 | Test circuit for read operation of MI-12T                                                        | 178 |

|-------------|--------------------------------------------------------------------------------------------------|-----|

| Figure 5.18 | Test circuit for write operation of MI-12T                                                       | 180 |

| Figure 5.19 | Test circuit for measurement of hold SNM of MI-12T                                               | 180 |

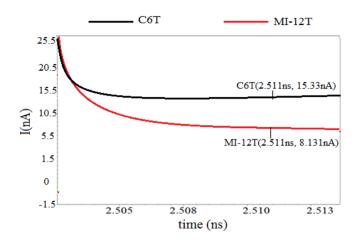

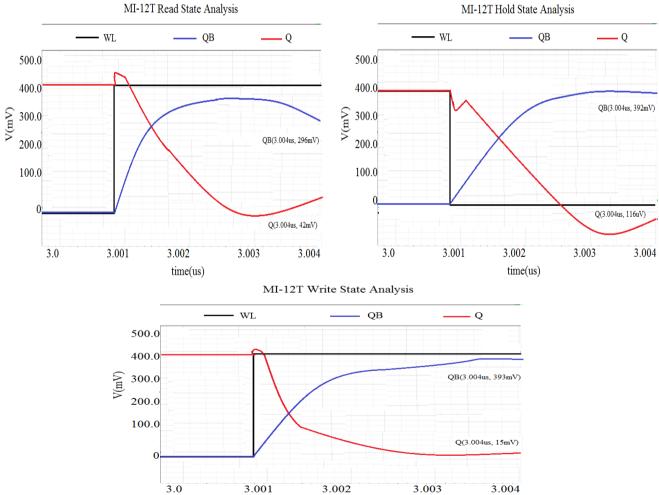

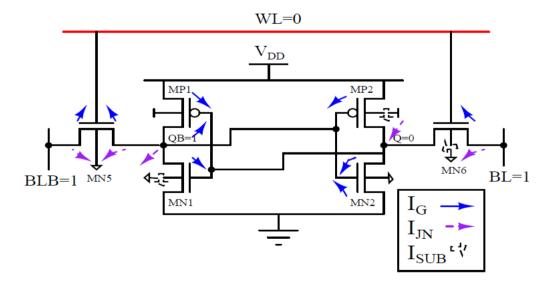

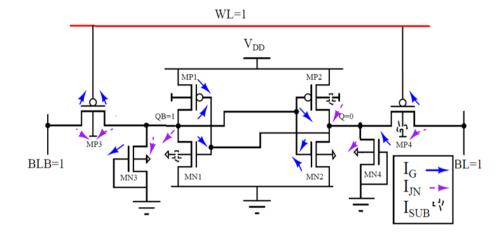

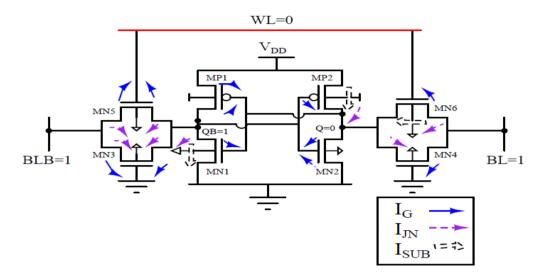

| Figure 5.20 | Currents plot for MI-12T and C6T during hold operation                                           | 181 |

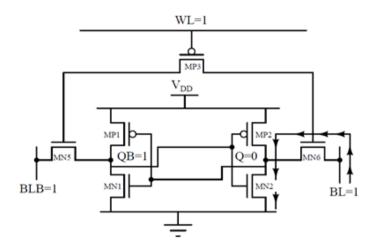

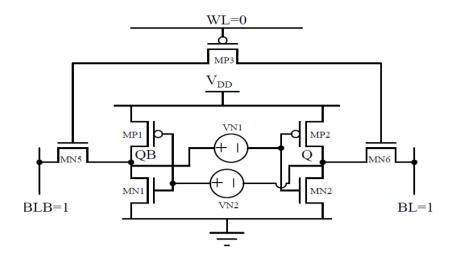

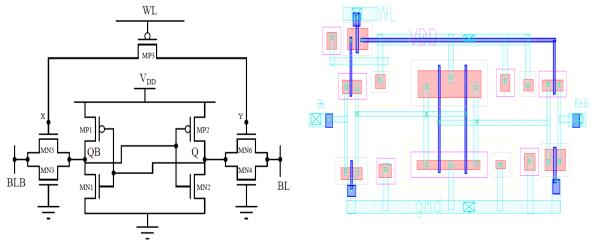

| Figure 5.21 | Schematic and layout of M7T                                                                      | 182 |

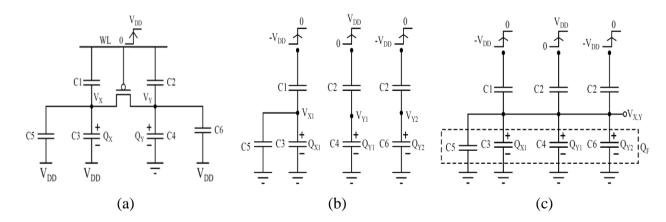

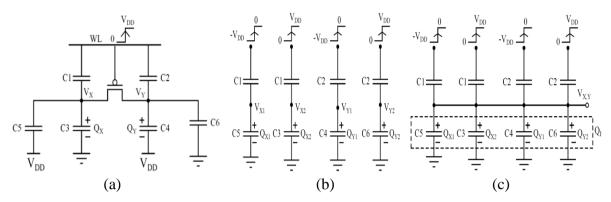

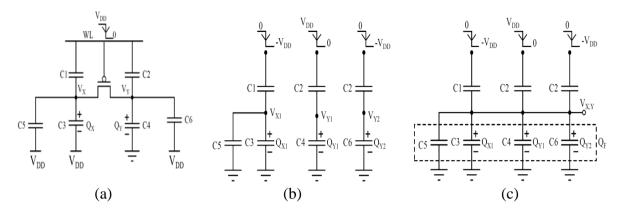

| Figure 5.22 | Coupling of parasitic capacitances in M7T during clock feed-through event                        | 182 |

| Figure 5.23 | Model for estimation of voltage at node X and Y during clock feed-through event                  | 183 |

| Figure 5.24 | Read circuit set up for estimation of charge at different nodes during clock feed-through event  | 183 |

| Figure 5.25 | Write circuit set up for estimation of charge at different nodes during clock feed-through event | 185 |

| Figure 5.26 | Hold circuit set up for estimation of charge at different nodes during clock feed-through event  | 187 |

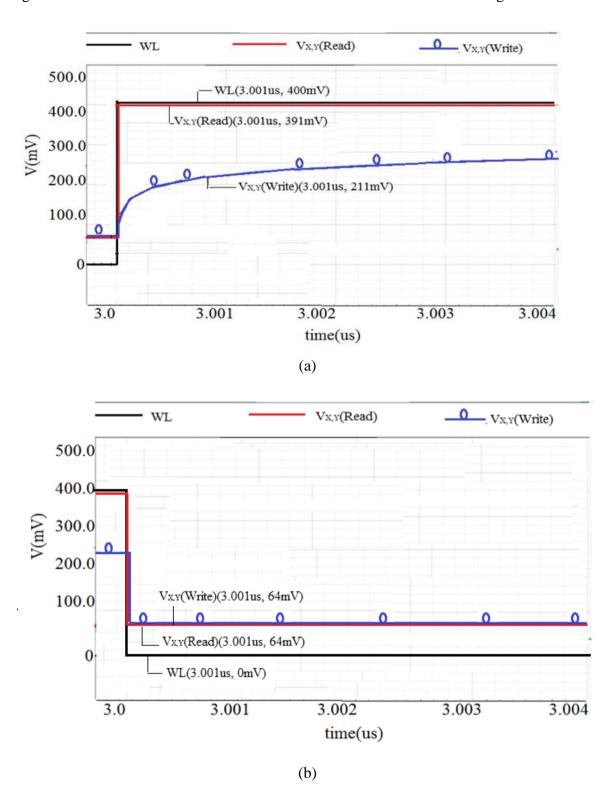

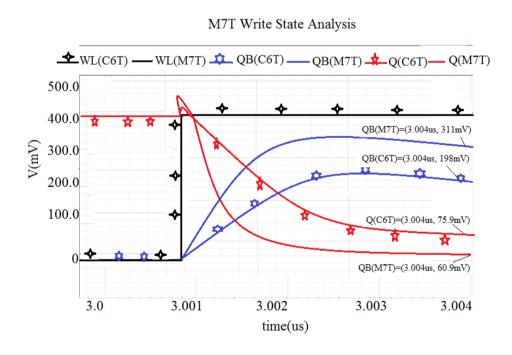

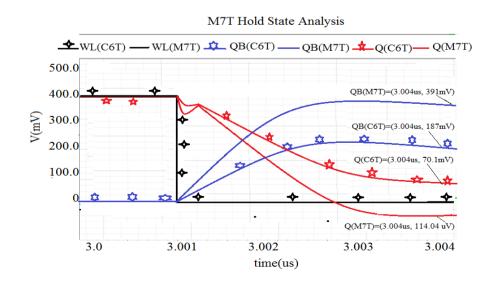

| Figure 5.27 | Waveforms at nodes X and Y during (a) read/ write (b) hold operation                             | 189 |

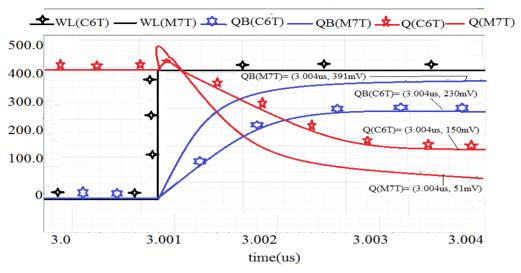

| Figure 5.28 | Test circuit for read operation of M7T                                                           | 190 |

| Figure 5.29 | Waveforms at nodes Q and QB during read mode                                                     | 191 |

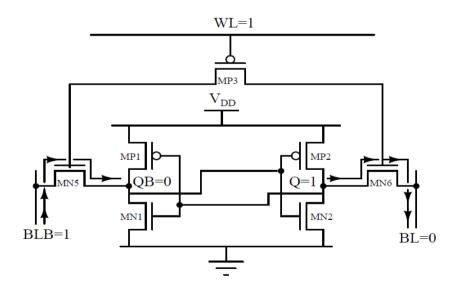

| Figure 5.30 | Test circuit for write operation of M7T                                                          | 191 |

| Figure 5.31 | Waveforms at nodes Q and QB during write mode                                                    | 192 |

| Figure 5.32 | Test circuit for measurement of hold SNM of M7T                                                  | 193 |

| Figure 5.33 | Waveforms at nodes Q and QB during hold mode                                                     | 193 |

| Figure 5.34 | Schematic and layout of M9T                                                                      | 194 |

| Figure 5.35 | Test circuit for read operation of M9T                                                           | 195 |

| Figure 5.36 | Test circuit for write operation of M9T                                                          | 196 |

| Figure 5.37 | Test circuit for measurement of hold SNM of M9T                                                  | 196 |

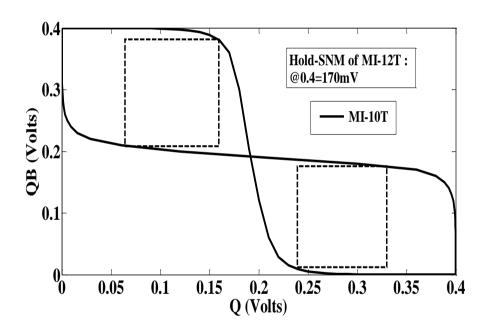

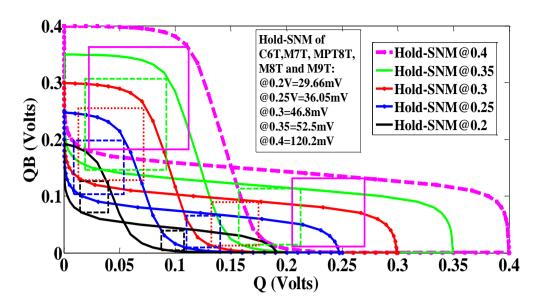

| Figure 5.38 | Overlapped VTC's of C6T, M7T, MPT8T, M8T and M9T during hold operation                           | 198 |

| Figure 5.39 | VTC of MI-12T during hold operation                                                              | 199 |

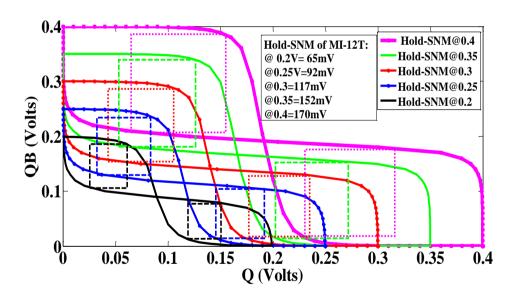

| Figure 5.40 | Combined VTC's of C6T, M7T, MPT8T, M8T and M9T during hold operation at varying $V_{\text{DD}}$  | 200 |

| Figure 5.41 | VTC's of MI-12T during hold operation at varying $V_{\text{DD}}$                                 | 200 |

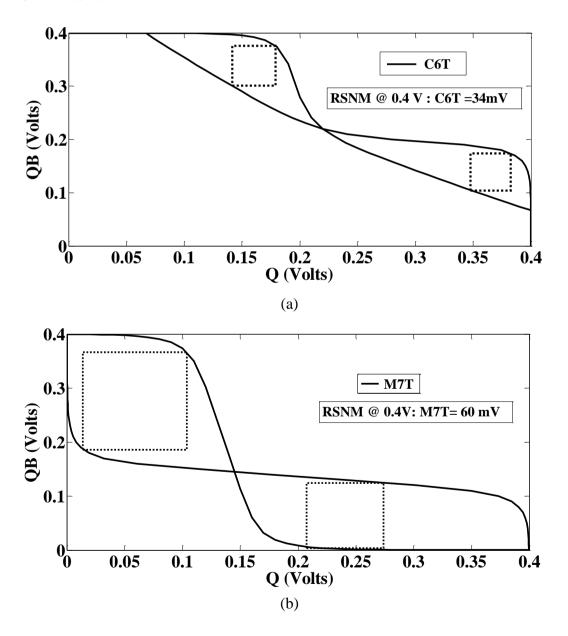

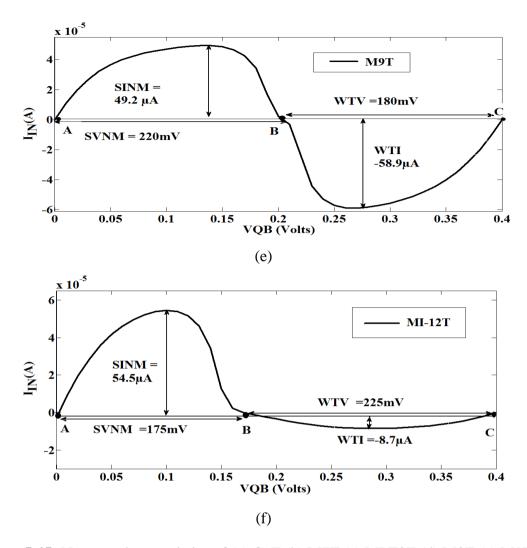

| Figure 5.42 | RSNM "butterfly curve" of (a) C6T (b) M7T (c) MPT8T (d) M8T (e) M9T (f) MI-12T $$                | 203 |

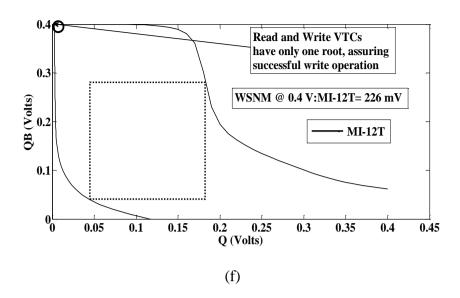

| Figure 5.43 | WSNM "butterfly curve" of (a) C6T (b) M7T (c) MPT8T (d) M8T (e) M9T (f) MI12T $$                 | 206 |

| Figure 5.44 | Test circuit for extracting N-curve of C6T during read mode                                      | 207 |

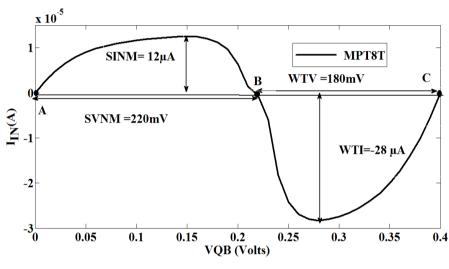

| Figure 5.45 | N-curve characteristics of (a) C6T (b) M7T (c) MPT8T (d) M8T (e) M9T (f) MI-12T                  | 209 |

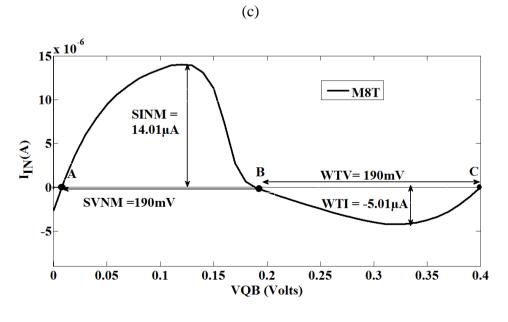

| Figure 5.46 | Read delay and its variability of (a) C6T (b) M7T (c) MPT8T (d) M8T (e) M9T (f) MI-12T           | 212 |

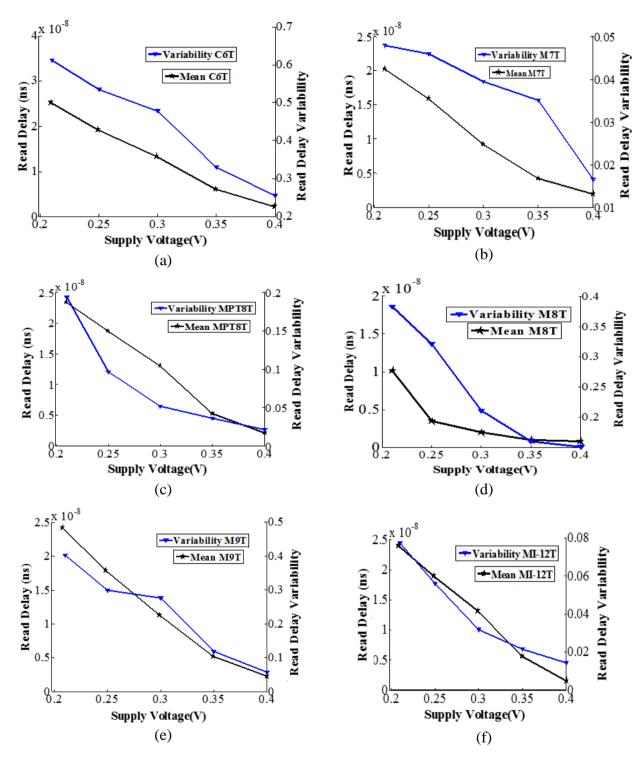

| Figure 5.47 | Write delay and its variability of (a) C6T (b) M7T (c) MPT8T (d) M8T (e) M9T (f) MI-12T          | 214 |

| Figure 5.48 | Leakage power consumptions in hold mode versus supply voltage                                      | 215 |

|-------------|----------------------------------------------------------------------------------------------------|-----|

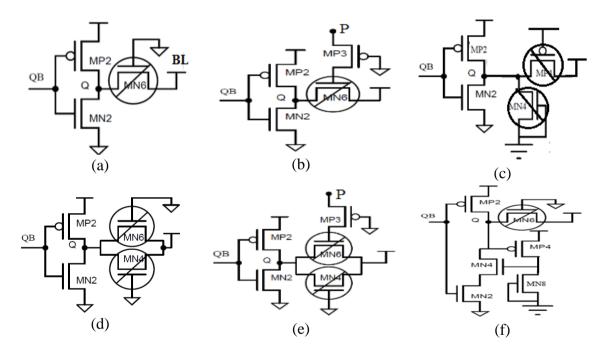

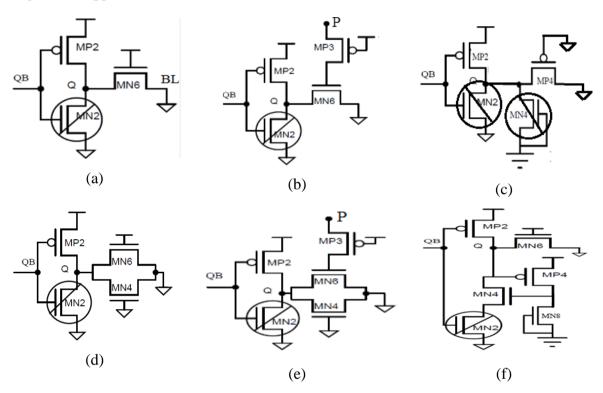

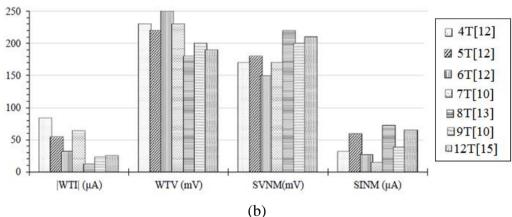

| Figure 5.49 | Half part of SRAM cells during hold operation (a) C6T (b) M7T (c) MPT8T (d) M8T (e) M9T (f)MI-12T  | 218 |

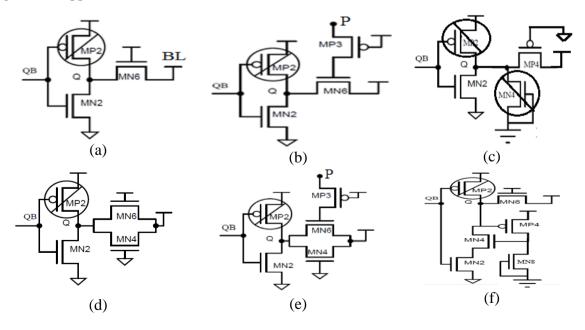

| Figure 5.50 | Half part of SRAM cells during read operation (a) C6T (b) M7T (c) MPT8T (d) M8T (e) M9T (f) MI-12T | 221 |

| Figure 5.51 | Half part of SRAM cells during write operation (a) C6T (b)M7T (c) MPT8T (d) M8T (e) M9T (f) MI-12T | 228 |

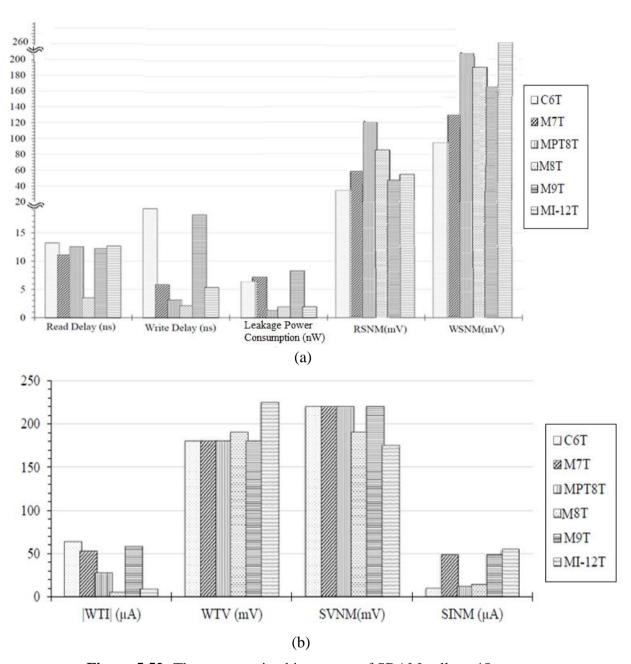

| Figure 5.52 | The comparative histograms of SRAM cells at 45 nm                                                  | 237 |

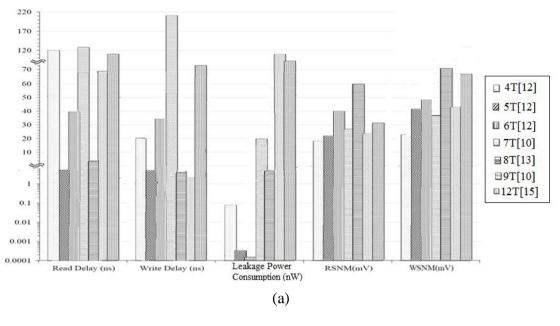

| Figure 5.53 | The comparative histograms of SRAM cells at 180 nm                                                 | 241 |

| Figure 5.54 | DSE chart of all five proposed SRAM cells as compared to C6T at 45 nm technology                   | 248 |

| Figure 5.55 | DSE chart of referenced SRAM cells at 180 nm technology                                            | 249 |

#### **LIST OF ABBREVIATIONS**

Si: Silicon

DIBL: Drain induced barrier lowering

SCE: Short channel effect

MAC: Multiply and Accumulator

LSB: Least Significant Bit

MSB: Most Significant Bit

PDP: Power-delay Product

WSN: Wireless sensor network

CSA: Carry save adder

CLA: Carry look-ahead adder

KSA: Kogge-Stone adder

HCA: Han-Carlson Adder

PP: Partial product

FA: Full Adder

HA: Half Adder

VLSI: Very large scale integration

MOS: Metal oxide semiconductor

SNM: Static noise margin

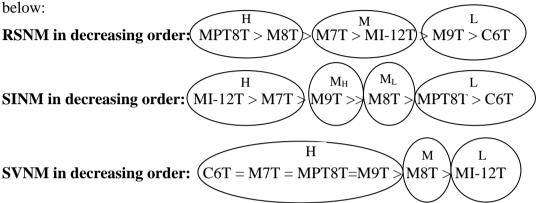

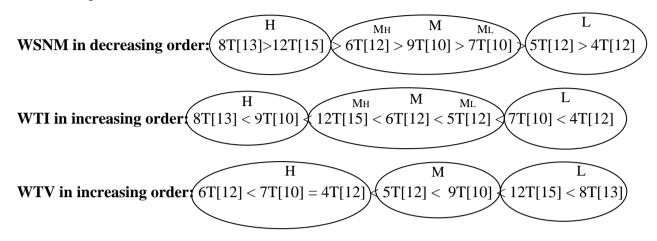

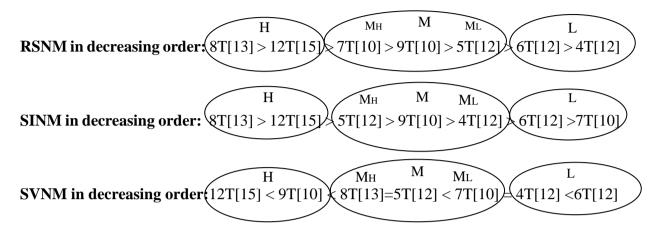

RSNM: Read static noise margin

WSNM: Write static noise margin

SRAM: Static random access memory

LOC: Lower order compressor

WTI: Write trip current

SINM: Static current noise margin

SVNM: Static voltage noise margin

## CHAPTER 1 INTRODUCTION

#### 1.1. BACKGROUND

Efficient power management has become a critical constraint with the rapid growth of portable, wireless and battery-operated applications. Higher power consumption increases the on-chip temperature which results in reduced operating life of the chip and battery life [1][2][3][4]. It is observed that in present scenario more than 50% power consumption occurs due to leakage current of the entire VLSI chip [5]. To overcome this leakage current problem, number of low power based design techniques like multi-threshold voltage technique, power gating schemes, back (substrate) bias scheme, sub-threshold design technique etc. have been investigated and explored by many researchers. Out of the different potential alternatives, sub-threshold technique has been found to be one of the most useful technique to obtain the ultralow power consumption, which utilizes leakage current as main conduction current. In sub-threshold circuits, the power supply voltage  $(V_{DD})$  is reduced below the threshold voltage  $(V_{th})$  of metal oxide semiconductor (MOS) transistor i.e.  $(V_{DD} < V_{th})$ . Sub-threshold circuit manages to satisfy the ultralow power requirement due to the quadratic reduction in power with respect to the supply voltage [6].

The increasing demand of smaller, lighter and more durable low power electronic products highlights the importance of sub-threshold design technique. Sub-threshold circuits are promising for applications where performance can be scarified for low power. Some of applications are wireless sensor networks, electronic watch, radio frequency identification (RFID), cryptographic applications like electronic passport (where security and power consumption rather than performance are given high priority), battery operated applications (implantable biomedical devices), and other portable communication devices. These applications need ultra-low power consumption with medium performance of operation (e.g. tens to hundreds of MHz) [7][8][9].

Automatic supply and body biasing controller [10] has been developed to minimize total active power in digital circuits by dynamically adjusting both threshold voltage and supply voltage based on circuit operating conditions such as temperature, workload, or circuit architecture.

In system on chip (SOC) architectures, embedded cache memories and arithmetic circuits may occupy more than 90% of the total die area [11]. In the arithmetic circuits, adders and multipliers used in the MAC unit are the major power consuming units. Here, the subthreshold design approaches appear to be suitable for low power/low energy application. Possibilities of making changes in the digital arithmetic circuits and on chip memory cell designs exists which can lead to many new efficient designs. This reflects the great need of the study and exploration of the alternative methods of efficient sub-threshold logic design.

#### 1.2. SUB-THRESHOLD OPERATION

#### 1.2.1. MOSFET in Sub-Threshold Region

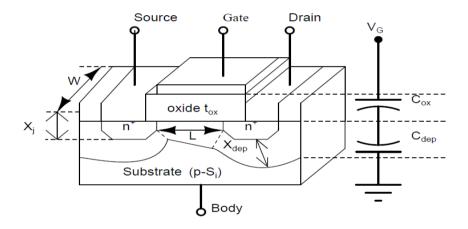

The cross-sectional view of an n-channel MOSFET is shown in Figure 1.1 [12].

Figure 1.1: A cross-sectional view of an n-channel MOSFET

In the gradual channel approximation for n-channel MOS structures, the drain current is considered to zero if the gate to source voltage  $(V_{GS})$  is less than the  $V_{th}$ , i.e. when  $V_{GS} \le V_{th}$ .

However, in practical aspects, the drain current is present due to minority charge carriers available at the surface under the gate when the gate voltage is less than threshold, i.e. in 'subthreshold' region. This population of mobile electrons under the gate provides a mechanism for charge flow between the drain and source even when  $V_{GS} \leq V_{th}$ . Thus, there is in fact a small, non-zero drain current through a MOSFET biased below threshold [13].

#### 1.2.2. The MOSFET Drain Current in the Sub-threshold Region

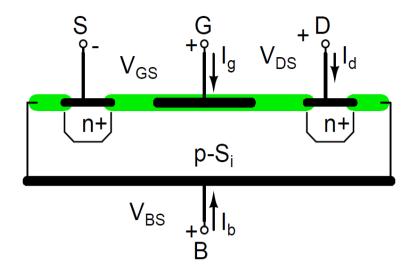

Figure 1.2 shows a cross-sectional view of an n-channel MOSFET biased with a positive drain voltage i.e.  $V_{DS} \ge 0$ , a negative substrate voltage, i.e.  $V_{BS} \le 0$  and the gate to source  $V_{GS}$  is biased positively but below threshold voltage  $V_{th}$ .

**Figure 1.2:** A cross-sectional view of an n-channel MOSFET operated in sub-threshold region

When the gate-to-source voltage,  $V_{GS}$ , is less than the threshold voltage,  $V_{th}$ , the semiconductor surface below the gate is a lightly doped n-channel [14] and [15]. The diffusion (due to the difference in the electron concentrations at the drain and source ends) of the thermally generated minority carriers of the substrate semiconductor material results in some conduction between the source and drain terminals through this weakly inverted channel [16]. This condition is known as weak inversion or the sub-threshold region. The off current, of a MOSFET operating in sub-threshold region, is defined here as the current flowing through the MOSFET transistor when its gate-to-source voltage,  $V_{GS}$ , is equal to 0 V.

The sub-threshold drain current of n-channel MOSFET under ( $V_{GS} \le V_{th}$ ) is given by Eq. (1.1). It shows that sub-threshold drain current ( $I_{D, SUB}$ ) is exponentially dependent on ( $V_{GS}$ - $V_{th}$ ) and it decreases with increase in  $V_{th}$  [17].

$$I_{D,SUB} = \begin{cases} I_{S} e^{\frac{V_{GS} - V_{th}}{nV_{T}}} \left( 1 - e^{-\frac{V_{DS}}{V_{T}}} \right), 0 \le V_{DS} \le 3V_{T} \\ I_{S} e^{\frac{V_{GS} - V_{th}}{nV_{T}}}, V_{DS} > V_{T} \end{cases}$$

(1.1)

Where  $I_S$  is the drain current when  $V_{GS} = V_{th}$  and is given by Eq. (1.2).

$$I_{s} = \mu_{0} C_{ox} \frac{W}{I_{t}} V_{th}^{2} (n-1)$$

(1.2)

The parameters in Eq. (1.1) and Eq. (1.2) are:

$\mu_{0}$ : Carrier mobility,

W: Channel width,

L: Channel length,

$C_{ox} = \varepsilon_{ox}/t_{ox}$ : gate oxide capacitance (Where  $\varepsilon_{ox}$  and  $t_{ox}$  is the gate oxide dielectric constant and gate oxide thickness),

$V_T$ : Thermal voltage (kT/q),

k: Boltzmann constant in joules per Kelvin,

T: Temperature in Kelvin,

q: Electronic charge in coulombs,

n: Sub-threshold slope factor of a long-channel uniformly doped device,

n can be calculated using following equation:

$$n = 1 + \frac{C_b}{C_g}$$

, where  $C_b = \frac{\varepsilon_{si}}{\omega_d}$  and  $C_g = \frac{\varepsilon_{ox}}{t_{ox}}$  (1.3)

Where,  $C_g$  is the gate capacitance,  $C_b$  is the bulk capacitance,  $\varepsilon_{si}$  and  $\omega_d$  denote the dielectric constants for silicon and depletion width under the channel respectively.

In sub-threshold operation, threshold voltage 'V<sub>th</sub>' is defined as the gate-to source voltage after which the drain current ceases to depend exponentially on the gate-to-source voltage [18].

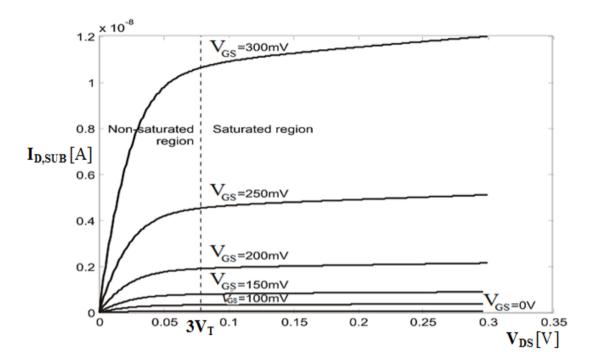

#### (i) I<sub>D, SUB</sub> – V<sub>DS</sub> Characteristics

According to Eq. (1.1), sub-threshold drain current ( $I_{D, SUB}$ ) does not depend on  $V_{DS}$  when  $V_{DS} > 3V_T$  because ( $e^{-3} << 1$ ), while at  $0 \le V_{DS} \le 3V_T$  condition, its dependence on  $V_{DS}$  is (1- $e^{-V_{DS}/V_T}$ ).

The behavior of current ( $I_{D, SUB}$ ) versus  $V_{DS}$  in the sub-threshold region is illustrated in Figure 1.3 [19].

**Figure 1.3:** I<sub>D, SUB</sub> – V<sub>DS</sub> characteristics in sub-threshold operation region

From the plot of  $I_{D, SUB} - V_{DS}$ , it is observed that MOSFET operates in non- current saturated region at below  $3V_T$  and at above  $3V_T$  ( $V_T$  is thermal voltage = 26mV), it operates in current saturation region.

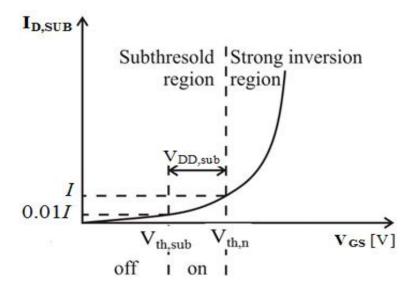

#### (ii) I<sub>D, SUB</sub> – V<sub>GS</sub> Characteristics

The exponential behavior of the sub-threshold drain current ( $I_{D, SUB}$ ) versus  $V_{GS}$  is illustrated in Figure 1.4 [20][21].

Figure 1.4: I<sub>D, SUB</sub>- V<sub>GS</sub> Characteristics

From the plot of  $I_{D,\,SUB}-V_{GS}$ , it is observed that MOSFET operates in sub-threshold region at below threshold voltage  $(V_{th,n})$  and at above threshold point, it operates in strong inversion region. There are two states (off and on) in sub-threshold region. In on state, the sub-threshold current increases by tenfold and the voltage difference between the two voltage points  $(V_{th,sub}$  and  $V_{th,n})$  is called on state voltage range  $(V_{DD,sub})$ , whereas below  $V_{th,sub}$  (off state), the magnitude of current is negligible.

For 45 nm / 180 nm process technologies at  $V_{DD} = 0.4 \text{ V}$ , observed values are:

$$V_{th,n} = 0.496V, V_{th,sub} = 0.028 V$$

(For 180 nm)

$$V_{th,n} = 0.416V$$

,  $V_{th,sub} = 0.02 V$  (For 45 nm)

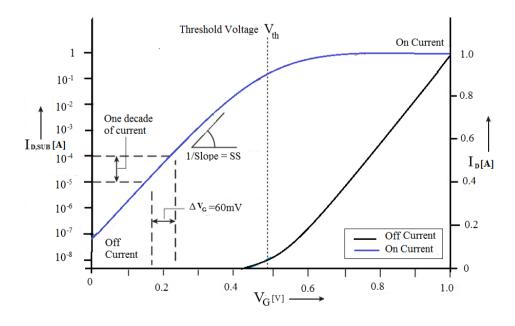

#### (iii) Sub-threshold Slope [22][23]

Sub-threshold Slope (SS) is defined as the amount of the gate voltage swing required to reduce the sub-threshold drain current by a decade. It is expressed in units (mV/decade) and is given by following equation:

$$SS = \frac{dV_{GS}}{d(lnI_{DS})} ln10 = \left(1 + \frac{C_{dep}}{C_{ox}}\right) \left(\frac{kT}{q}\right) ln10$$

(1.4)

Figure 1.5 shows the sub-threshold slope plot.

**Figure 1.5:** Sub-threshold slope plot at 180 nm technology

The two curves show identical data that have been plotted using a linear scale (on y axis, right side) and a logarithmic scale (on y axis, left side) on same plot.

When the gate voltage  $(V_G)$  is increased, the number of electrons in the channel increases. This, in turn, increases the current flowing between the source and the drain. The current at the minimum gate voltage  $(0\ V)$  is called off current, and the current at the maximum gate voltage  $(1V\ in\ this\ case)$  is the on current. Above the threshold voltage  $V_{th}$  (dashed line), the drain current  $(I_D)$  increases linearly. Below the threshold voltage, the drain current  $(I_{D,\ SUB})$  increases exponentially with the gate voltage.

In the present thesis work, sub-threshold slope value is observed as approximately 60 mV/dec for both, 45 nm / 180 nm process technologies.

#### 1.3. SOURCES OF POWER CONSUMPTION IN CMOS LOGIC GATE

Power consumption is an important property of a design that affects feasibility, cost and reliability. It influences a greater number of critical design decisions, such as power supply capacity, the battery lifetime, supply line sizing, packaging and cooling requirements [24].

In sub-threshold region of operation, sub-threshold current is the main operating current which is otherwise considered as leakage current in strong inversion region.

The total power consumption in a CMOS circuit is constituted by dynamic, short circuit and static power consumption.

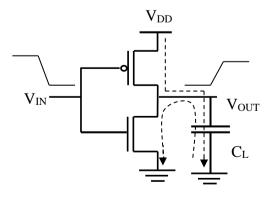

#### (i) Dynamic power consumption

This power consumption is due to logic transitions causing logic gates to charge/discharge output capacitances. It depends on the supply voltage, device threshold, the input rise/fall time and the operating frequency of the transistor.

Figure 1.6 shows the current flow in CMOS inverter resulting into dynamic power consumption.

**Figure 1.6:** CMOS inverter mode for dynamic power consumption

The equation for dynamic power consumption is expressed as

$$P_{\text{Dynamic}} = \alpha_{0-1}.C_{\text{L}}.V_{\text{DD}}^2.f_{\text{clk}}$$

(1.5)

Where  $V_{DD}$  is the power supply voltage;  $C_L$  is the load capacitance;  $f_{clk}$  is the operating input signal frequency and  $\alpha_{0-1}$  is the probability that a power consuming transition occurs (the activity factor).

#### (ii) Short-circuit power consumption

This power consumption is due to the direct current path from supply to ground when both NMOS and PMOS transistors are conducting current simultaneously for a brief duration due to non-zero rise/fall times.

Figure 1.7 shows the current (Isc) flow in CMOS inverter causing short-circuit power consumption.

**Figure 1.7:** CMOS inverter mode for short-circuit power consumption

The equation for short circuit power consumption is expressed as

$$P_{\text{shortcircuit}} = I_{\text{sc}}.V_{\text{DD}}$$

(1.6)

Where, I<sub>SC</sub> is short circuit current.

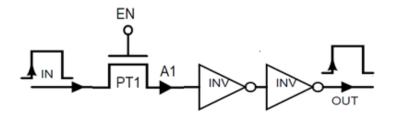

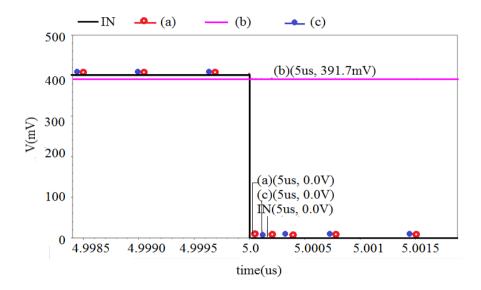

The short-circuit power consumption is the dominant component of power consumption which increases exponentially with the power-supply voltage. Reduction in the short-circuit power consumption in the sub-threshold region is achieved by reducing power supply voltage and by applying input pulses with rise/ fall time. In the present thesis, input signals have rise/ fall times of 1 pico-second, pulse width (ON time) of 1 micro-second and pulse period of 5 micro-second. [25].

#### (iii) Static power consumption

This power consumption occurs due to leakage current when the system is in standby mode. In sub-threshold region, the sources of leakage is the gate-oxide tunneling current that results due to the tunneling of carriers across the very thin gate oxide [26], the edge-direct tunneling that appears between the source and drain extension, the gate overlap [27][28], the reverse currents of the source-substrate and the drain-substrate pn junctions. This power consumption does not depend on the input transition or load capacitance. It remains constant for a logic cell

Static power is expressed as

$$P_{\text{Static}} = I_{\text{leakage}} \cdot V_{\text{DD}} \tag{1.7}$$

Where I<sub>leakage</sub> is the leakage current as discussed above.

The total power consumption in digital CMOS circuit is the combination of the Eq. (1.5), (1.6) and (1.7), given by

$$\begin{aligned} P_{\text{total}} &= P_{\text{dynamic}} + P_{\text{shortcircuit}} + P_{\text{static}} \\ &= \alpha_{0-1}.C_{L}.V_{\text{DD}}^{2}.f_{\text{clk}} + I_{\text{sc}}.V_{\text{DD}} + I_{\text{leakage}}.V_{\text{DD}} \end{aligned} \tag{1.8}$$

During sub-threshold operation, these three components of the power consumption increase with  $V_{DD}$  but with different rates with dynamic and short-circuit power consumption increasing quadratically and exponentially with  $V_{DD}$  respectively [29]. Hence, all these components of power consumption can be reduced by reduction in power supply voltage. With technology scaling down, power consumption increases due to significant increments in the leakage current (as for CMOS inverter the leakage currents are found to be 1.05 nA and 0.18 nA at 45 nm / 180 nm technology respectively through simulation).

#### 1.4. MOTIVATIONS AND CHALLENGES IN SUB-THRESHOLD DESIGN

In recent years, as technology of metal oxide semiconductor (MOS) transistors keeps scaling down to deep submicron region, sub-threshold region design focuses on to develop circuits operating at very low power supply voltage.

This is to support battery operated applications with very less power consumption, especially in ultra-low power application fields such as portable biosensors, wireless sensor nodes, RFID tags, hearing aids, pace-maker, wearable computing or implants, and personal digital assistants. These are dominated primarily by the need to minimize energy consumption and increase battery life time whereas speed is a secondary consideration.

To design these types of ultra-low power system, sub-threshold based SRAM and arithmetic circuits (adders and multipliers) are the basic units and the most power consuming modules [30]. Thus, it requires low power consuming memories and arithmetic circuits that are efficient with optimal performance at the same time.

Researchers have done exploration and design of Carry look-ahead adder, Kogge-Stone adder and Han-Carlson adder architectures, Wallace tree and Dadda multiplier architectures and SRAM cell designs operated in super-threshold region (gate voltage above threshold voltage region operation) using conventional Static-CMOS logic [31], transmission gate logic and pass transistor logic families. But these published architectures operation is degraded in subthreshold region [32].

Therefore, it is important to design fully functional power efficient arithmetic and memory circuits which show least power-delay-product when operated in sub-threshold region.

Various challenges for circuit design in sub-threshold region have been discussed in the [33][34][35][36]. These mainly relate to reduced supply voltage, and device scaling as given below:

- i. Exploring Logic Families for Robust Design: The current ratio  $I_{ON}/I_{OFF}$  decreases with low  $V_{DD}$  which leads to functional degradation and hence, reduces robustness of the circuits. Therefore, to design robust sub-threshold logic circuits, existing logic families need to be explored and modified.

- ii. Impact of Device Scaling on circuit performance: The influence of scaling on circuits operating in the weak inversion region has been limited to device-level studies and few circuit-level simulations of simple circuits. Hence, a thorough investigation is necessary to find the impact of scaling on function of logic gates.

- iii. Delay: Another challenging parameter of the circuit operation in the sub-threshold region is the longer propagation delay, hence lower frequency of operation due to weak current flow in the channel. This requires circuit optimization techniques for achieving optimum performance.

- iv. Development of Sub-threshold Compatible and Robust Memory Design: SRAM is an important component of many ICs, and contributes a large fraction of the active and leakage power consumption. Process variation and reduced I<sub>ON</sub>/I<sub>OFF</sub> are the major parameters which degrade the read/write operation and affect read/write access time in sub-threshold region.

- v. Noise Margin: It is directly affected by the choice of supply voltage and has high sensitivity to process variations. Therefore, in the presence of process variations, there is need to study noise margin of logic gate and SRAM cell in sub-threshold region.

#### 1.5. RESEARCH GAPS

A detailed literature review of published research work of logic design style, arithmetic circuits, and SRAM cell has been carried out and reported in Chapter 2. Based on it, following research gaps are identified:

i. Exploration of basic logic gates using different logic families in sub threshold logic is missing in literature

The current research scenario focuses on the power efficient architectures of arithmetic circuits and SRAM cell design that requires minimum supply voltage and increase the operating frequency of a circuit for sub-threshold operation. For the implementation of these architectures, there is great need to do extensive exploration of basic logic gates using different logic families which is currently missing.

ii. Comprehensive exploration of Adder/ Multiplier/ SRAM circuits has not been carried out in the sub-threshold region.

A limited study of the arithmetic circuits using different architectures has been published in the area of sub-threshold region. Therefore, design and exploration of these circuits with possible modifications in design of internal blocks at circuit and architectural level are required to ensure functional and power-efficient designs in sub-threshold region.

Similarly, operation and analysis of sub-threshold SRAM cells during read, write and hold mode have been least explored. SRAM cells designed for super-threshold operation give degraded function and performance at scaled down technologies Therefore designs of power efficient SRAM cells operating in sub-threshold region with higher noise margin during read/write/hold mode at ultra-low power supply in deep sub-micron technology are required.

iii. Impact of technology scaling on circuits designed in sub-threshold region.

The impact of technology scaling in arithmetic/ memory circuits has not been analyzed out in the sub-threshold region.

#### 1.6. OBJECTIVES OF THE THESIS

Complete analyses of the arithmetic circuits and SRAM cells used for super-threshold operation have never been examined in the context of sub-threshold operation. The conventional arithmetic circuits and SRAM cells may not be either functional or not give efficient result in sub-threshold region due to ultra-low supply voltage and process variation effect. Therefore, there is a great need to modify the conventional arithmetic circuits and SRAM cells with improved functional parameters of the design. The main objective of this work is based on structural optimizations to reduce very long critical path delay and to improve the overall power-delay-product of the arithmetic circuits in sub-threshold operation. The subthreshold based SRAM cells are more sensitive to power, voltage and temperature variations and their effects have discussed in published work to some extent [37][38]. But comprehensive analysis of SRAM cell design in terms of various parameters like process sensitivity, area overhead, read stability, write ability, hold stability, read/write access time and leakage power consumption is not carried out in sub-threshold region [39]. The proposed work aims to design low power SRAM cells with improvement in above mentioned design parameters in subthreshold region. The arithmetic circuits and SRAM cells are designed and implemented at two different technology nodes (45 nm / 180 nm) which shows the effect of scaling in subthreshold region.

In this thesis, the research is carried out with following objectives:

- i. Explorations and design of functional basic logic gates using different logic families in sub-threshold region.

- ii. Design and analysis of **power efficient functional adder architectures** in subthreshold region using two different technology nodes.

- iii. Design and analysis of **power efficient functional multiplier architectures** in subthreshold region using two different technology nodes. Overall comparative analyses to be performed to get a full view of the improvements with respect to power, delay and power-delay product for arithmetic circuits.

- iv. Design and analysis of **low power functional SRAM cells** in sub-threshold region. A comprehensive analysis of SRAM cells with read stability, write ability, hold stability, read/write access time and leakage power consumption is to be carried out.

#### 1.7. ORGANIZATION OF THE THESIS

This thesis is divided into six chapters. The organization of this thesis is as follows:

**Chapter 1** presents an introduction of sub-threshold design technique. It is followed by sub-threshold operation of MOSFET and sources of power consumption. This chapter also explains motivation and challenges of sub-threshold logic design. The research gaps and objectives chosen for this research work are discussed in this chapter.

Chapter 2 describes the detailed literature review on arithmetic circuits and SRAM cells. The characteristics and performance parameters of various power efficient arithmetic circuits such as power, delay and power-delay product at different technology nodes have been discussed. Various low power SRAM cell designs and their parameters in terms of read stability, write ability, hold stability, read/write access time and leakage power consumption have been discussed in detail.

**Chapter 3** explores and proposes new designs of the frequently used adders like Carry lookahead adder, Kogge-Stone adder and Han-Carlson adder architectures with different logic design style and operand size in sub-threshold region.

The comparative analysis of logic gates is given which are used to implement adder architectures using different logic families along with their post layout simulation results. For additional power-delay-product optimization, the effects of reverse body bias scheme on logic gates have been discussed. The design and analysis of chosen adders is done at 45 nm as well as 180 nm technology to find the impact of scaling.

Chapter 4 explores and proposes new designs of column compression multipliers namely Wallace tree and Dadda multiplier architectures, for different bit-widths and different logic design styles in sub-threshold region. The partial product generation scheme, the partial product accumulation scheme used in Wallace tree and Dadda multipliers have been discussed in detail. The design and analysis of chosen multipliers is done at 45 nm as well as 180 nm technology to find the impact of scaling.