# Investigations on Electronic Behavior and Stability Issues of Zinc Oxide (ZnO) based Thin-Film Transistors (TFTs)

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of

#### **DOCTOR OF PHILOSOPHY**

By

Kavindra Kandpal

ID No. 2014PHXF0601P

Under the supervision of

Dr. Navneet Gupta

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE

PILANI (RAJASTHAN) INDIA

April 2018

# BIRLA INSTITUTE OF TECHNOLOGY & SCIENCE PILANI- 333031 (RAJASTHAN) INDIA

# **CERTIFICATE**

This is to certify that the thesis entitled "Investigations on Electronic Behavior and Stability Issues of Zinc Oxide (ZnO) based Thin-Film Transistors (TFTs)" submitted by Kavindra Kandpal, ID. No. 2014PHXF0601P for award of Ph.D. of the Institute embodies original work done by him under my supervision.

| Signature of the Supervisor |                                                                                                                                                       |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                        | Prof. NAVNEET GUPTA                                                                                                                                   |

| Designation                 | Associate Professor and Head<br>Department of Electrical & Electronics Engineering,<br>Birla Institute of Technology and Science, Pilani<br>Rajasthan |

| Date                        |                                                                                                                                                       |

## **ACKNOWLEDGEMENTS**

I sincerely thank my research advisor and mentor Prof. Navneet Gupta, Associate Professor and Head, Department of Electrical and Electronics Engineering, BITS Pilani, Pilani Campus, for the opportunity to work with him. He has always stood by me with his valuable guidance and support. Since, I joined BITS Pilani as a lecturer in EEE Department, he guided me in both professional and personal areas. He also introduced me to the domain of thin film transistors which was relatively new to me, and motivated me to pursue my dreams. Prof. Gupta nurtured me, inspired me and helped me to excel. I am grateful to him as my mentor and thesis supervisor.

I take this opportunity to celebrate another influential mentor in my career at BITS, Prof. Chandra Shekhar, Sr. Emeritus Professor, EEE Department BITS Pilani. Since he joined our department, I have been fortunate to work with him. He is the one who directed me towards the "learning by doing". It's a valuable advice that I would carry forward. In the same vein, I am indebted to Dr. Jitendra Singh, Scientist, Sensors and Nanotechnology Group, CSIR-CEERI Pilani for assisting me in material characterization, ZnO thin film deposition and MIS-C fabrication. I would cherish his valuable feedback and guidance throughout.

My doctoral advisory committee members, Dr. Niladri Sarkar and Dr. Abhijit Asati have stood by me always with their valuable feedbacks that made me a better scholar and an individual. I am indebted to Dr. Ak Saravanan and his research group in National Taiwan University of Science & Technology (NTUST) for providing experimental facility for deposition of ZnO thin film using ZnO ceramic target (RF sputter deposition). Similarly, I thank Material Research Center, Malaviya National Institute of Technology (MNIT) Jaipur, for providing access to characterization facilities.

I sincerely thank Prof. A. K. Sarkar, Director, BITS Pilani, Pilani Campus and Prof. Santanu Chaudhury, Director CSIR-CEERI Pilani for approving a project of academic interest on "Investigation of leakage current density and threshold voltage shift in ZnO Thin Film Transistor with high–κ dielectrics". This gave us access to use lab facility of CEERI Pilani to fabricate a MIS-C structure. Similarly, I am indebted to Prof. Anshuman Dalvi for providing access to XRD characterization facility. I am equally thankful to Prof. Anu Gupta, Prof. S. Gurunarayanan, Prof. H. D. Mathur, and Prof. V. K. Chaubey, for their encouragement and inputs during my research days.

I would like to thank Mr. Ravindra Kumar, Mr. Jitendar Kumar, Research fellows, CEERI Pilani for assisting me in MIS-C device fabrication. I also would like to acknowledge Mr. Prateek Kothari, Technical Officer, CEERI Pilani, Mr. Ramesh Chandra Prajapati, Mr. Hitesh Kumar Sharma, Mr. Shriniwas Yadav, Technical Assistant, MRC MNIT Jaipur for assisting me in the thin film characterization.

I am fortunate to have a mentor and friend like Dr. Kumar Sankar Bhattacharya who during the course of last 4 year have always inspired and motivated me and stood by me through thick and thin. I am grateful to my friends and my other colleagues Dr. Praveen Kumar A.V., Mr. Karri Babu Ravi Teja, Mr. Devesh Samaiya, Dr. Vinita Tiwari for being with me during my research days. At the same time, I am grateful to all the staff members of EEE department for their support in all kind of official work.

Last but not the least, I am extremely indebted to my family for making me what I am today. My parents' unflinching support for my education throughout, has made my Doctorate possible today. My wife, Divya has been my strongest pillar of support taking care of everything, easing out of my life and helping me excel in all my endeavors. The sheer amount of hard work she does to make my family run while working herself, is an inspiration for me. No words can express my love and gratitude for her. Finally, I am indebted to the Almighty for choosing me to be what I am today.

#### **Kavindra Kandpal**

Dedicated

to

My Son Devansh

## **ABSTRACT**

As research in the area of new materials for display technology has been intensifying, a different class of semiconducting materials, i.e. oxide semiconductors, is emerging as an alternative. Among the known oxide semiconductors, Zinc Oxide (ZnO) has attracted interest for thin-film-transistor (TFT) applications because of its high transparency, nontoxicity and high electron mobility. ZnO intrinsically is an n-type semiconductor mainly due to oxygen vacancies and metal interstitial. ZnO thin films have been investigated for TFT applications such as, pixel driving and switching circuit in active-matrix display panels (AMOLEDs, AMLCDs). The operation characteristic of TFTs, however, critically depends on the physical and structural properties of the deposited ZnO film, the gate dielectric, quality of ZnO and gate dielectric interface.

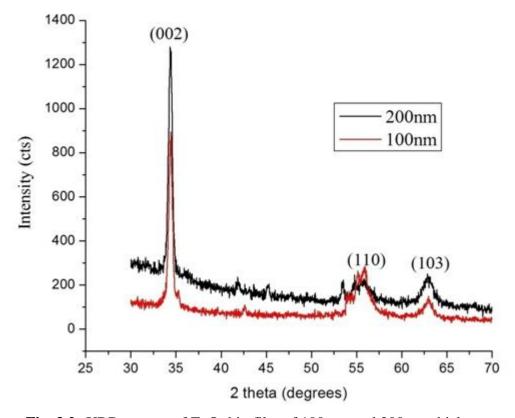

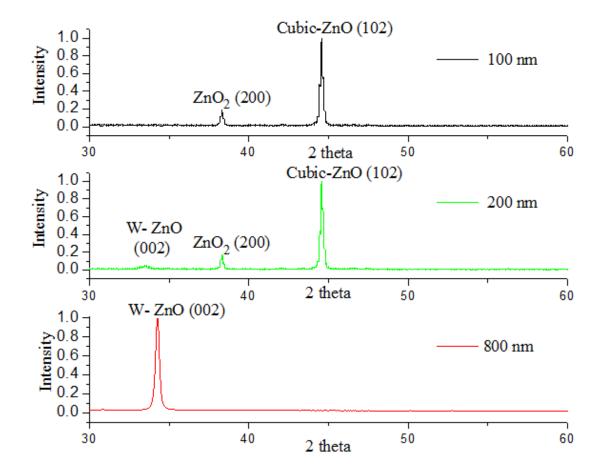

To analyze physical and structural properties of the film, this thesis reports the room temperature deposition of ZnO film of different thicknesses using RF magnetron sputtering technique. For TFT applications, room temperature deposition is highly desirable as it can support wide range of substrate material. Structural and surface morphological characterization were done using X-ray Diffraction (XRD), Field Emission Scanning Electron Microscope (FESEM) and Atomic Force Microscopy (AFM) techniques, while resistivity measurement was done using Four-Probe method. ZnO films were deposited using ZnO ceramic target and Zn metallic target. In both cases, the nature of deposited film was polycrystalline and it is found that crystallinity and grain size improve with the increase in film thickness. RF magnetron sputtering with Zn metallic target provides cost effectiveness for large coating area as it results in faster deposition rate (1-1.1 Å/s) than RF magnetron sputter deposition using ZnO target (0.6-0.7Å/s). However, the ideal stoichiometry and strong c-axis oriented phase of hexagonal wurtzite structure of ZnO was observed when deposition is carried out using ZnO target. For ZnO deposition with Zn metallic target, XRD analysis of 100 nm and 200 nm thick

films show dominant cubic phase of ZnO along with small presence of ZnO<sub>2</sub>, while, XRD analysis of 800 nm thick film confirms strong c-axis growth of wurtzite ZnO. ZnO film deposited using Zn metallic target shows higher sheet resistance  $(10^{10} - 10^{11} \Omega/\Box)$  than the ZnO film deposited using ZnO target  $(10^7 - 10^8 \Omega/\Box)$ , which indicates that Zn metallic target deposited films were more oxygen rich.

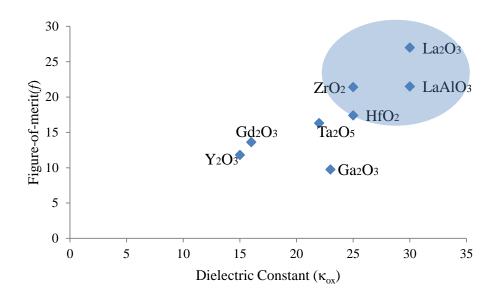

To address the high threshold voltage and high leakage in ZnO based TFTs, a detailed investigation on high–κ dielectrics for low operating voltage and low leakage Zinc Oxide thin film transistor (ZnO TFT) was carried out using three material selection methodologies namely Ashby, Technique for Order Preference by Similarity to Ideal Solution (TOPSIS) and VlseKriterijumska Optimizacija I Kompromisno Resenjein in Serbian (VIKOR). Various material properties such as dielectric constant, conduction band offset to ZnO, band-gap and temperature coefficient mismatch of high–κ dielectric to ZnO are investigated to find out the most promising gate dielectric material. The analysis concludes that Lanthanum oxide (La<sub>2</sub>O<sub>3</sub>) is the most promising gate dielectric material closely followed by Hafnium oxide (HfO<sub>2</sub>) and Zirconium oxide (ZrO<sub>2</sub>) for ZnO based thin film transistor. The results obtained show a good agreement among Ashby's, TOPSIS and VIKOR approaches.

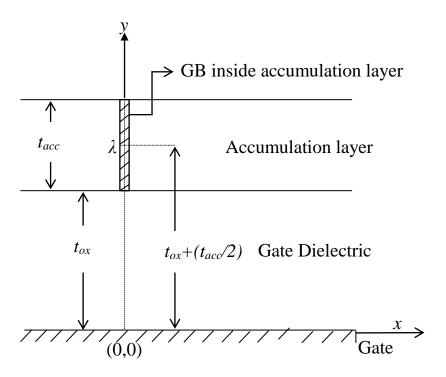

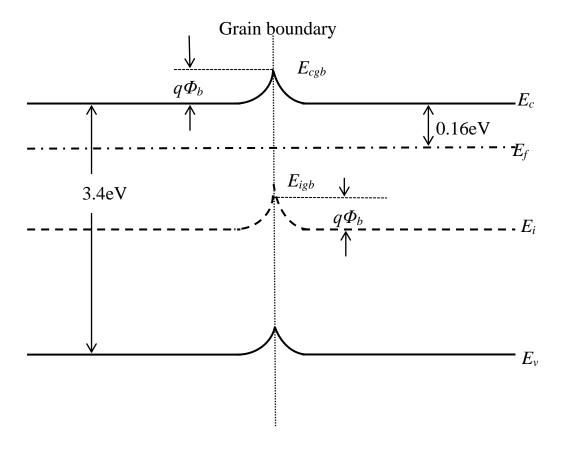

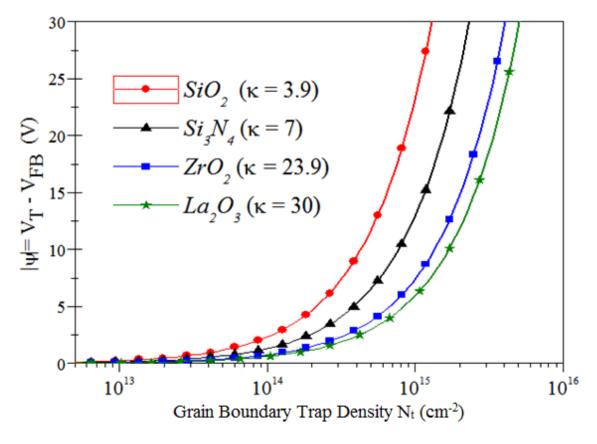

ZnO based TFT operates in accumulation mode. In ZnO based TFT, the threshold voltage has remained ambiguous due to existence of grain boundary traps in polycrystalline semiconducting channel. This thesis also provides analytical relationship of threshold voltage with grain boundary trap density by assuming grain boundary as continuous one dimensional line charge. The analysis concludes that for higher density of grain boundary traps, threshold voltage increases, and its effect can be minimized by employing high–κ dielectric as a gate dielectric. Further, it discusses the effect of grain boundary dominated scattering on effective mobility and concludes that the thermionic emission dominated regime in ZnO based TFT is limited to low value of overdrive voltage.

To describe the electrical characteristic of ZnO based TFT, SPICE LEVEL-3 model, which is originally defined for metal oxide field effect transistor (MOSFET), is successfully adapted as a behavioral model for ZnO based TFT. Various performance

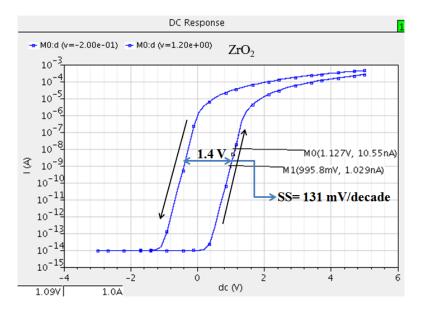

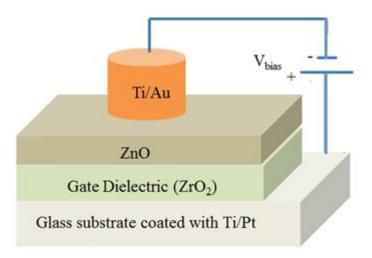

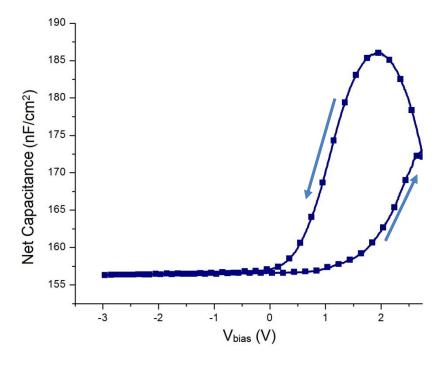

parameters like subthreshold slope, on-to-off ratio, threshold voltage and effective mobility are described in detail. Finally, to investigate the threshold voltage instability in ZnO based TFT, fabrication of MIS-C (metal-insulator-semiconductor capacitor) structure using  $ZrO_2$  gate dielectric is reported. ZnO based TFT exhibits counter clockwise hysteresis due to existence of oxygen vacancies in the gate dielectric which may be originated during ZnO sputtering.

# **TABLE OF CONTENT**

| <b>C</b> ]   | ERTIFICATE                                         | i   |

|--------------|----------------------------------------------------|-----|

| A            | CKNOWLEDGEMENTS                                    | ii  |

| $\mathbf{A}$ | BSTRACT                                            | V   |

|              | ABLE OF CONTENT                                    |     |

|              | IST OF TABLES                                      |     |

|              |                                                    |     |

|              | IST OF FIGURES                                     |     |

| $\mathbf{L}$ | IST OF SYMBOLS                                     | xvi |

| $\mathbf{L}$ | IST OF ABBREVIATIONS                               | xix |

| CHA          | APTERS                                             |     |

|              |                                                    |     |

| 1.           | INTRODUCTION                                       | 1   |

| 1.1          | Evolution of Thin Film Transistor (TFT) Technology | 1   |

| 1.2          | ZnO TFT                                            | 5   |

| 1.3          | TFT Performance Parameters                         | 6   |

| 1.4          | Research Motivation and Objectives                 | 10  |

| 1.5          | Thesis Organization                                | 12  |

| 2.           | ZnO BASED TFT: LITERATURE REVIEW                   | 14  |

| 2.1          | Recent Development in ZnO based TFT Technology     | 14  |

| 2.2          | Fabrication of Bottom Gate ZnO TFT                 | 17  |

| 2.           | 2.1 ZnO Semiconductor                              | 19  |

| 2.           | 2.2 Gate Dielectric                                | 22  |

| 2.3          | Transport Model of ZnO TFT                         | 23  |

| 2.           | 3.1 Hossain Model                                  | 23  |

| 2.           | 3.2 Multiple- Trapping and Release (MTR) Model     | 25  |

| 2.           | 3.3 Other Device Models                            |     |

| 2.4          | Electrical Instability in ZnO based TFT            | 27  |

| 2.5 | Co  | onclusion                                                   | 32    |

|-----|-----|-------------------------------------------------------------|-------|

| 3.  | DE  | POSITION AND CHARACTERIZATION OF ZnO F                      | ILM33 |

| 3.1 | Int | roduction                                                   | 33    |

| 3.2 | RF  | Magnetron Sputtering                                        | 35    |

| 3.3 | RF  | F Sputtered Deposition of ZnO Film Using ZnO Target         | 36    |

| 3.  | 3.1 | Experimental                                                |       |

| 3.  | 3.2 | Structural and Surface Morphological Characterization       | 37    |

| 3.  | 3.3 | Resistivity Measurement                                     | 44    |

| 3.4 | RF  | F Sputtered Deposition of ZnO Film Using Zn Metallic Target | 46    |

| 3.4 | 4.1 | Experimental                                                | 46    |

| 3.4 | 4.2 | Structural and Surface Morphological Characterization       | 48    |

| 3.4 | 4.3 | Resistivity Measurement                                     | 53    |

| 3.5 | Co  | onclusion                                                   | 55    |

| 4.  | MA  | ATERIAL SELECTION FOR GATE DIELECTRIC                       | 57    |

| 4.1 | Int | roduction                                                   | 57    |

| 4.2 | Ma  | aterial Selection Methodologies                             | 59    |

| 4.  | 2.1 | Ashby's Approach                                            | 61    |

| 4.  | 2.2 | TOPSIS Approach                                             | 62    |

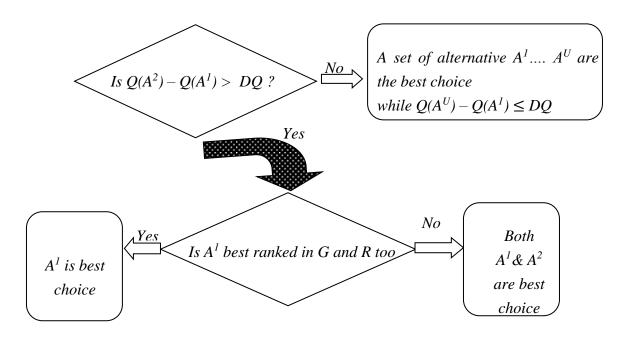

| 4.  | 2.3 | VIKOR Approach                                              | 63    |

| 4.3 | Ma  | aterial Indices of the Gate- Dielectrics                    | 65    |

| 4.4 | Re  | sults and Discussion                                        | 69    |

| 4.  | 4.1 | Ashby's Analysis                                            | 69    |

| 4.  | 4.2 | TOPSIS Analysis                                             | 72    |

| 4.  | 4.3 | VIKOR Analysis                                              | 74    |

| 4.5 |     | onclusion                                                   |       |

| 5.  | DE  | VICE MODEL FOR ZnO TFT                                      | 77    |

| 5.1 | Int | roduction                                                   | 77    |

| 5.2 |     | nalytical Model for Threshold Voltage                       |       |

| 5.3 |     | obility Model                                               |       |

| 5.4 |     | PICE LEVEL-3 Model for ZnO TFT                              |       |

| 5.4 | 4.1 | Background                                                  |       |

| 5.4 | 4.2 | Methodology                                                 |       |

| 5.5 | SPICE LEVEL-3 Model Validation   | 97  |

|-----|----------------------------------|-----|

| 5.6 | Threshold Voltage Instability    | 100 |

| 5.7 | Conclusion                       | 103 |

| CC  | ONCLUSION AND FUTURE WORK        | 104 |

| AF  | PPENDIX                          | 109 |

| RF  | EFERENCES                        | 114 |

| LI  | ST OF PUBLICATIONS               | 126 |

| BF  | RIEF BIOGRAPHY OF THE CANDIDATE  | 128 |

| BF  | RIEF BIOGRAPHY OF THE SUPERVISOR | 129 |

# **LIST OF TABLES**

| Table 1.1 | Comparative analysis of various TFTs                        | 9    |

|-----------|-------------------------------------------------------------|------|

| Table 2.1 | Material parameters of ZnO                                  | 20   |

| Table 2.2 | Performance characteristics of ZnO based TFTs with various  |      |

| fab       | prication techniques                                        | 22   |

| Table 3.1 | Summary of AFM results for different thicknesses ZnO films  | . 49 |

| Table 4.1 | Materials and their conduction band offset ( $\Delta E_c$ ) | 67   |

| Table 4.2 | Material indices matrix                                     | 68   |

| Table 4.3 | Material indices  ΔTEC  PPM/°K for various dielectrics      | 69   |

| Table 4.4 | Weighted normalized matrix                                  | 73   |

| Table 4.5 | TOPSIS results with ranks                                   | 73   |

| Table 4.6 | VIKOR $R_i$ , $G_i$ and $Q_i$ values with respective ranks  | 75   |

| Table 4.7 | Experimental data for the validation of proposed analysis   | . 75 |

| Table 5.1 | Key SPICE LEVEL-3 model parameters                          | 95   |

| Table 5.2 | List of device parameters used in analysis                  | 97   |

# **LIST OF FIGURES**

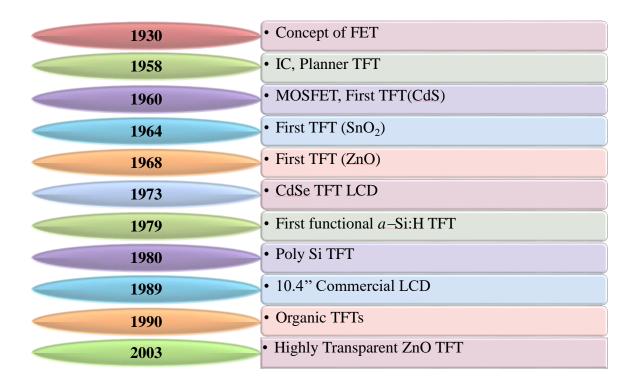

| <b>Fig. 1.1</b> | Timeline of TFT technology development (prior to next generation ZnO                   |     |

|-----------------|----------------------------------------------------------------------------------------|-----|

|                 | TFT)                                                                                   | . 3 |

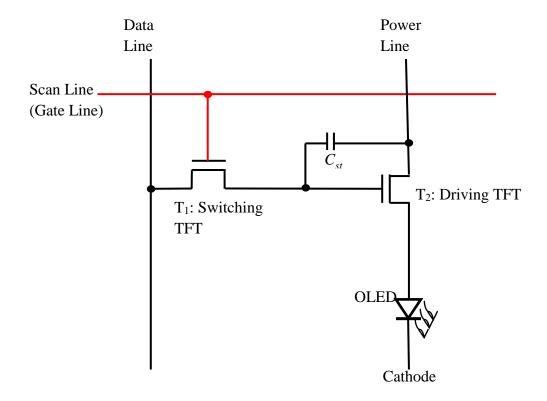

| Fig. 1.2        | Typical two TFT, OLED pixel driver circuit                                             | . 4 |

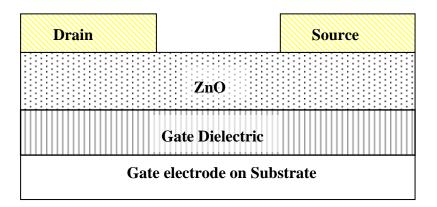

| Fig. 1.3        | Schematic view of bottom-gate ZnO TFT                                                  | . 5 |

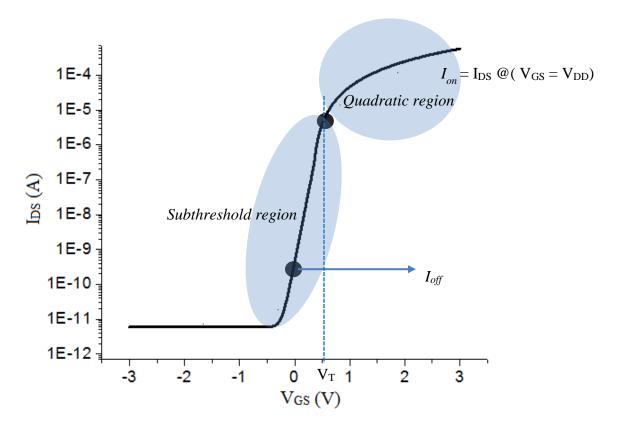

| Fig. 1.4        | Typical transfer characteristic of low voltage ZnO based TFT                           | . 7 |

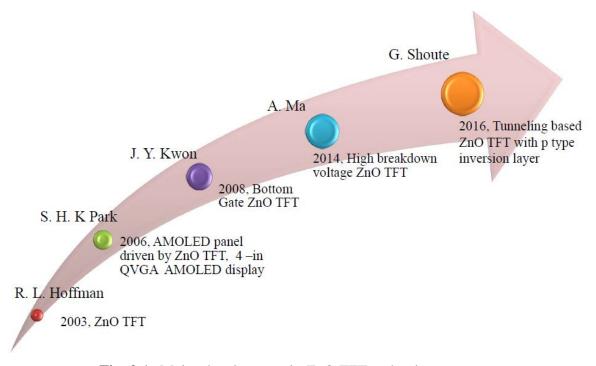

| Fig. 2.1        | Major development in ZnO TFT technology                                                | 15  |

| Fig. 2.2        | Two-mask process flow of bottom gate ZnO TFTs with self-aligned                        |     |

|                 | structure                                                                              | 18  |

| <b>Fig. 2.3</b> | ZnO crystal structure                                                                  | 19  |

| Fig. 2.4        | Energy band diagram of ZnO channel in the presence of grain boundary                   | 24  |

| Fig. 2.5        | Multiple- tapping and release mechanism                                                | 26  |

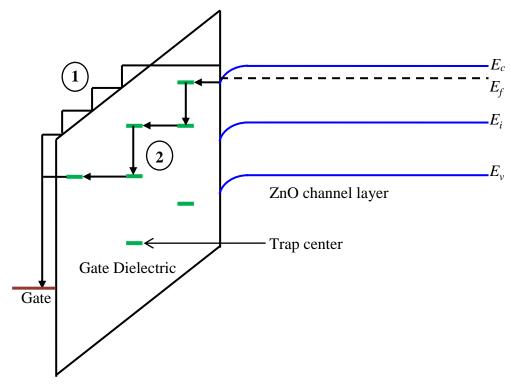

| Fig. 2.6        | Band diagram of metal gate dielectric/ZnO interface when positive voltage              |     |

|                 | is applied at the gate. Process 1: Fowler –Nordheim Tunneling, Process 2:              |     |

|                 | Trap assisted tunneling.                                                               | 29  |

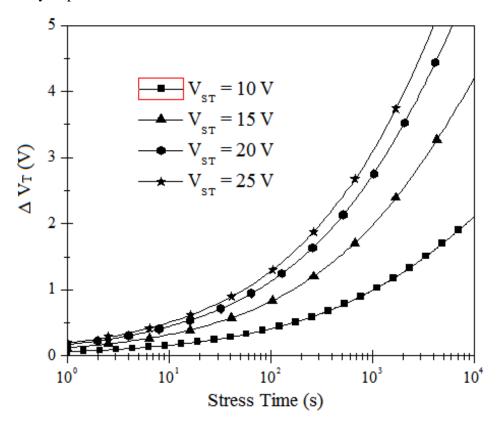

| Fig. 2.7        | Time dependence of threshold voltage shift under different gate bias stress            | 30  |

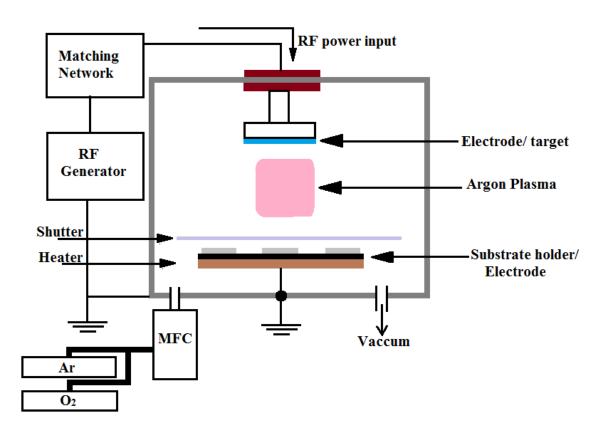

| Fig. 3.1        | Schematic diagram of RF sputtering technique for thin film deposition                  | 35  |

| Fig. 3.2        | XRD spectra of ZnO thin film of 100 nm and 200 nm thickness                            | 38  |

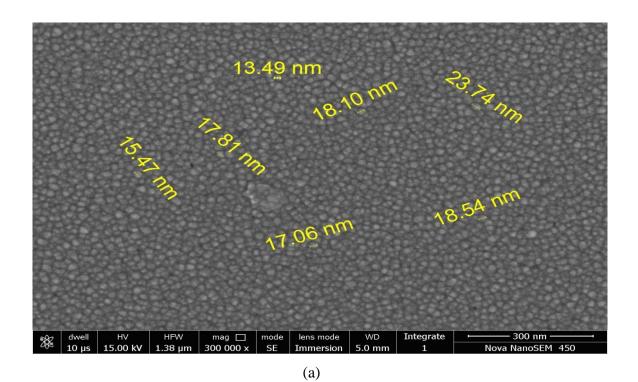

| Fig. 3.3        | SEM micrograph image of (a) 100 nm thick ZnO film (b) 200 nm thick                     |     |

|                 | ZnO film                                                                               | 40  |

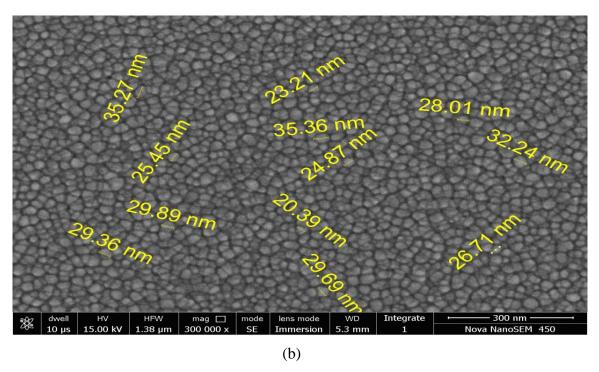

| Fig. 3.4        | Surface elemental survey scan XPS spectrum of ZnO film                                 | 41  |

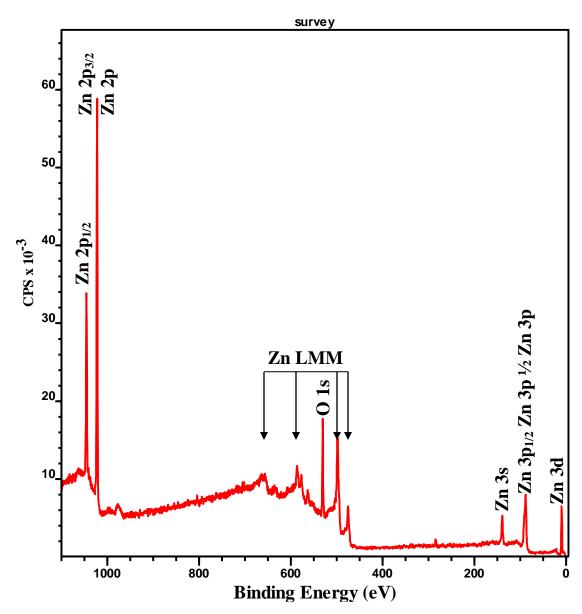

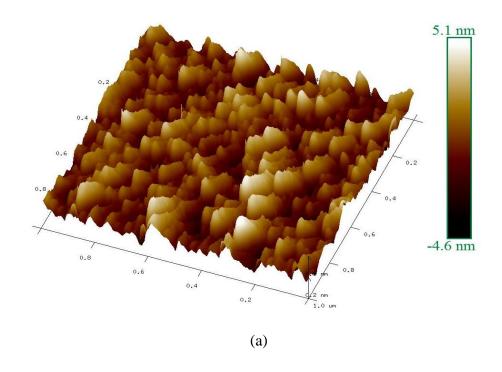

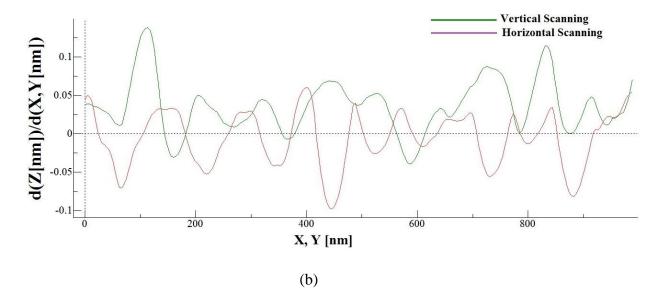

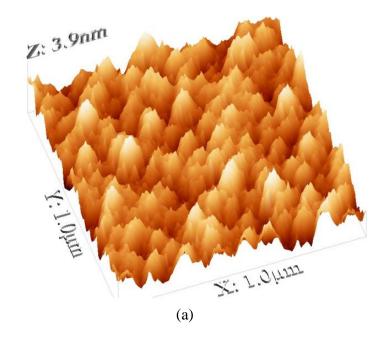

| Fig. 3.5        | (a) Three – dimensional AFM image of 100 nm thick ZnO film, (b)                        |     |

|                 | $(dz/d(x,y))$ of 100 nm thick ZnO film for a scan area of 1 $\mu$ m $\times$ 1 $\mu$ m | 42  |

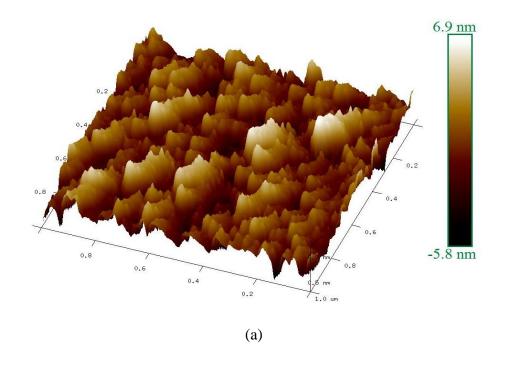

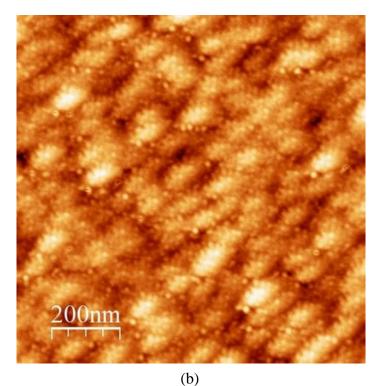

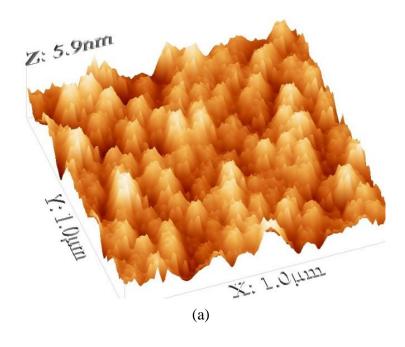

| Fig. 3.6        | (a) Three – dimensional AFM image of 200 nm thick ZnO film (b)                         |     |

|           | $(dz/d(x,y))$ of 200 nm thick ZnO film for a scan area of 1 $\mu$ m $\times$ 1 $\mu$ m             | . 43  |

|-----------|----------------------------------------------------------------------------------------------------|-------|

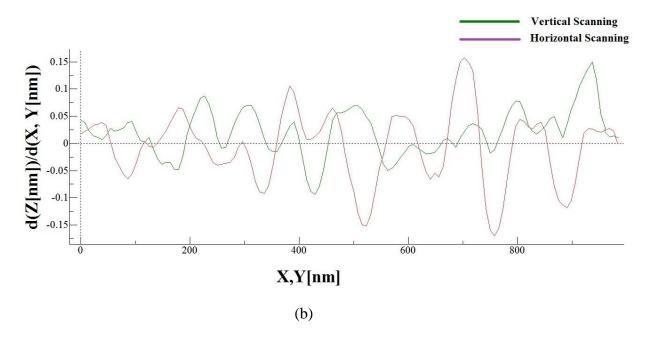

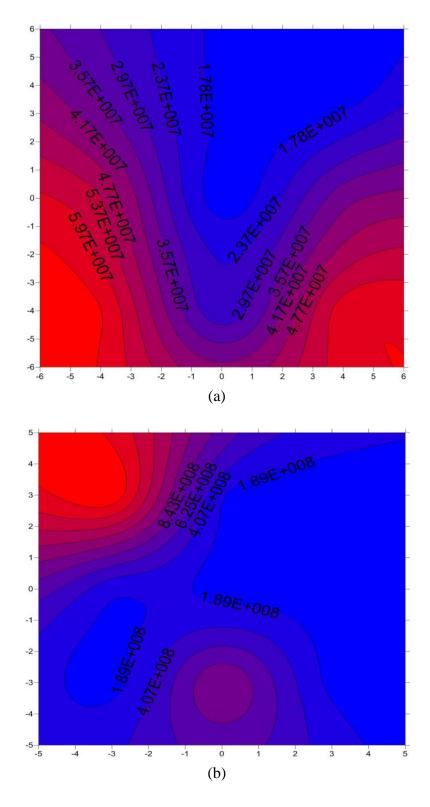

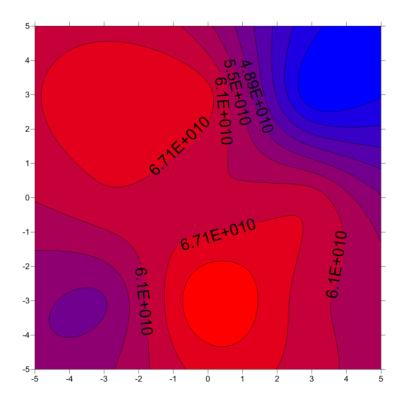

| Fig. 3.7  | Sheet resistance contour map of (a) 200 nm thick ZnO film, (b) 100 nm                              |       |

|           | thick ZnO film, where blue to red region shows an increase in sheet                                |       |

|           | resistance                                                                                         | . 45  |

| Fig. 3.8  | Reactive magnetron sputtering unit in CSIR- CEERI Pilani                                           | . 47  |

| Fig. 3.9  | XRD spectra of ZnO thin film of 100, 200, 800 nm thickness                                         | . 48  |

| Fig. 3.1  | (a) 3-D and (b) 2-D AFM image of 100 nm thick ZnO film                                             | . 50  |

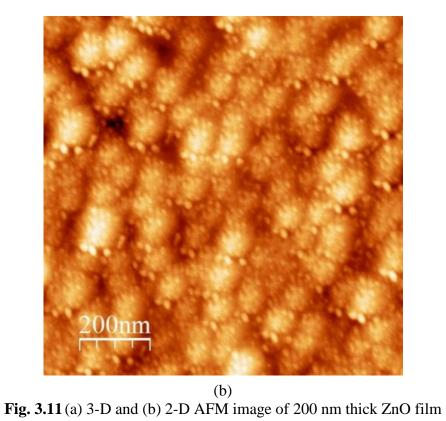

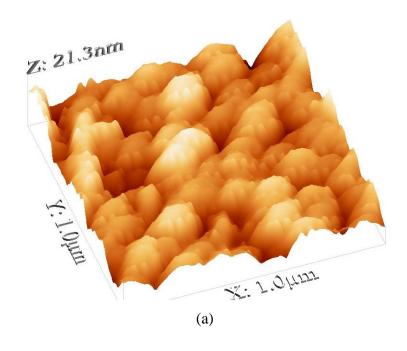

| Fig. 3.1  | 1 (a) 3-D and (b) 2-D AFM image of 200 nm thick ZnO film                                           | . 51  |

| Fig. 3.1  | 2 (a) 3-D and (b) 2-D AFM image of 800 nm thick ZnO film                                           | . 52  |

| Fig. 3.1  | 3 Sheet resistance contour map of 100 nm thick ZnO circular sample                                 | . 53  |

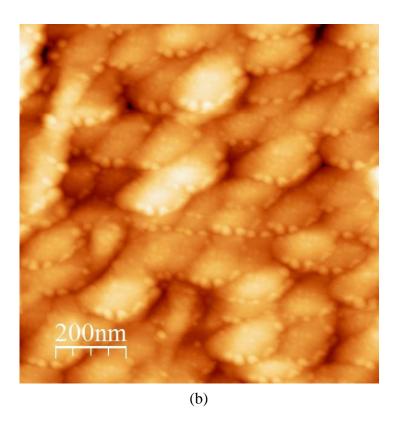

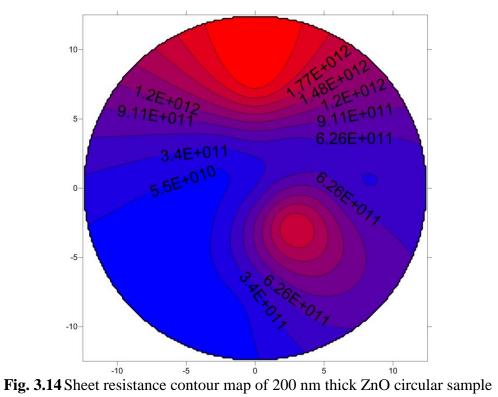

| Fig. 3.1  | 4 Sheet resistance contour map of 200 nm thick ZnO circular sample                                 | . 54  |

| Fig. 3.1  | 5 Sheet resistance contour map of 800 nm thick ZnO circular sample                                 | . 54  |

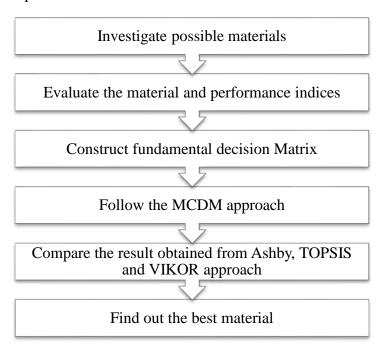

| Fig. 4.1  | Flow chart of material selection approach                                                          | . 60  |

|           | Flow chart illustrating the decision making in VIKOR approach                                      |       |

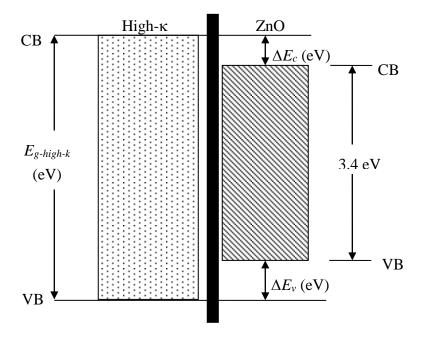

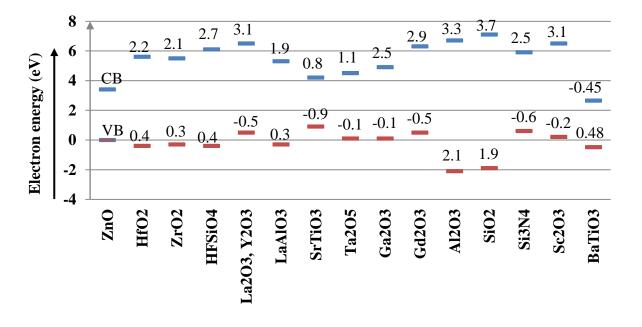

|           | Conduction band offset ( $\Delta E_c$ ) and valance band offset ( $\Delta E_v$ ) of high- $\kappa$ |       |

| J         | material on ZnO                                                                                    | . 66  |

| Fig. 4.4  | The conduction band and valance band offset of various high–κ dielectrics                          |       |

| 8         | on ZnO                                                                                             | . 68  |

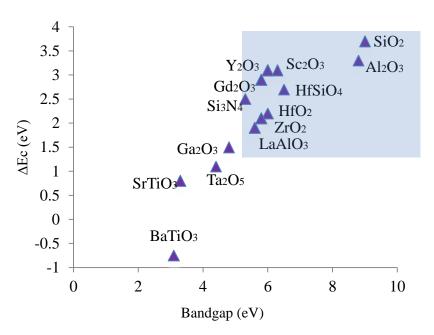

| Fig. 4.5  | Plot of conduction band offset versus band-gap of various dielectrics                              |       |

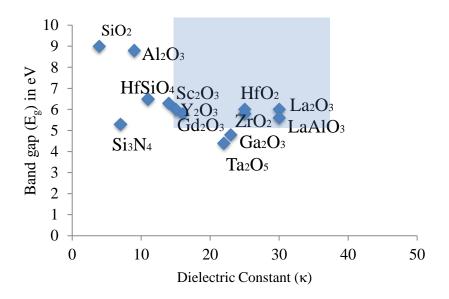

| _         | Plot of band-gap versus dielectric constant for various dielectrics                                |       |

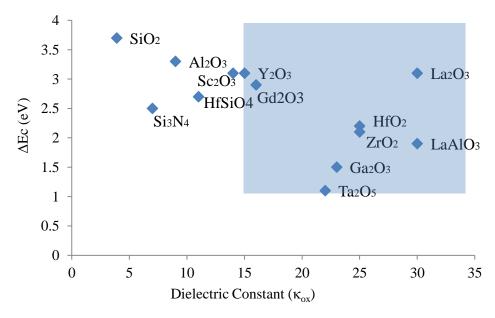

| _         | Plot of conduction band offset versus dielectric Constant                                          |       |

| J         | Plot of figure of merit (f) versus dielectric constant                                             |       |

| Fig. 5.1  | Schematic of a bottom gate TFT system involving one dimensional line                               |       |

| 116.011   | charge associated with a grain boundary present in ZnO semiconductor                               |       |

|           | channel                                                                                            | 79    |

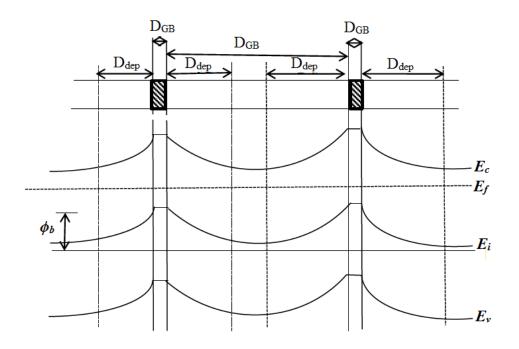

| Fig. 5.2  | Energy band diagram of ZnO TFT channel with potential barrier $(q\phi_b)$                          | . , , |

| - 15, 0,2 | located at the grain boundary at equilibrium                                                       | 81    |

| Fig. 5.3  | Effect of grain boundary trap density $(N_t)$ on threshold voltage $(V_T)$ for                     |       |

|           | different gate dielectrics.                                                                                | . 82 |

|-----------|------------------------------------------------------------------------------------------------------------|------|

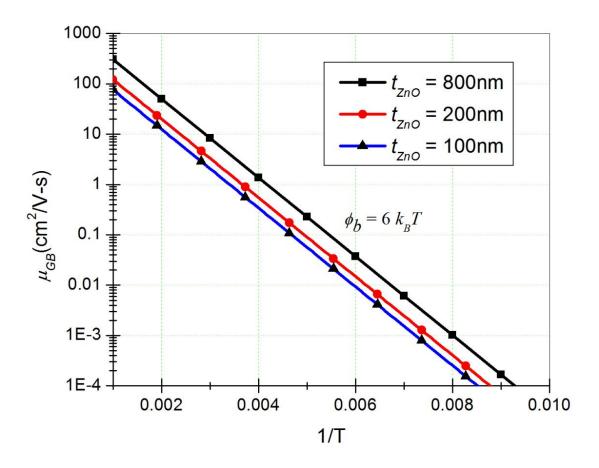

| Fig. 5.4  | Variation of mobility at grain boundary $(\mu_{GB})$ vs. inverse of absolute                               |      |

|           | temperature (1/T) for different ZnO film thicknesses                                                       | . 86 |

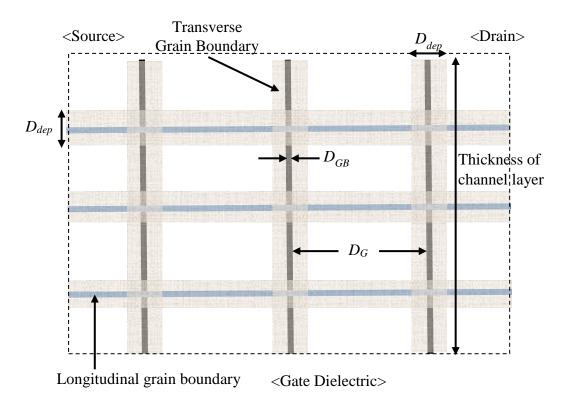

| Fig. 5.5  | Polycrystalline TFT Channel for bottom gate ZnO TFT                                                        | . 88 |

| Fig. 5.6  | Transverse grain boundaries in polycrystalline ZnO channel                                                 | . 88 |

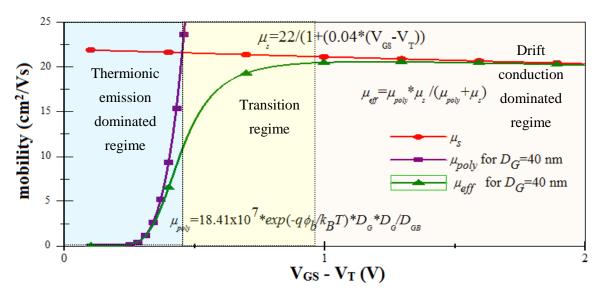

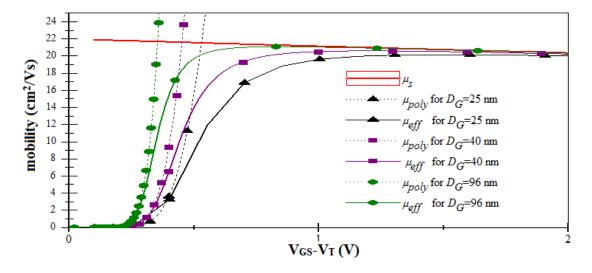

| Fig. 5.7  | Plot of effective mobility ( $\mu_{\it eff}$ ) versus overdrive voltage ( $V_{\rm GS}$ - $V_{\rm T}$ ),    |      |

|           | illustrating different conduction regime in ZnO based TFT                                                  | . 91 |

| Fig. 5.8  | Plot of effective mobility ( $\mu_{\it eff}$ ) versus overdrive voltage ( $V_{\rm GS}$ - $V_{\rm T}$ ) for |      |

|           | different grain sizes                                                                                      | . 91 |

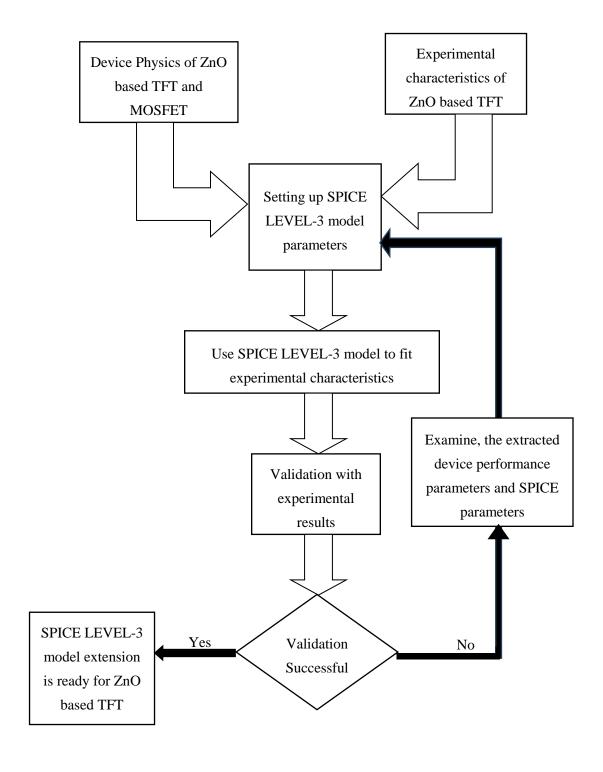

| Fig. 5.9  | Flowchart illustrating SPICE LEVEL-3 model adaption flow for ZnO                                           |      |

|           | based TFT.                                                                                                 | . 94 |

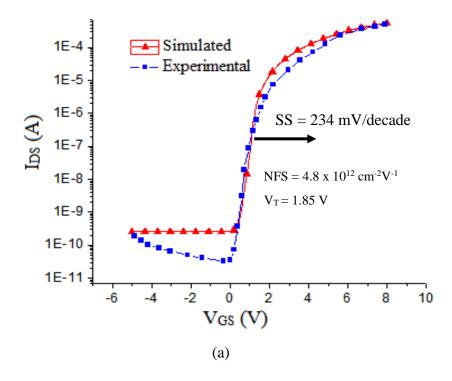

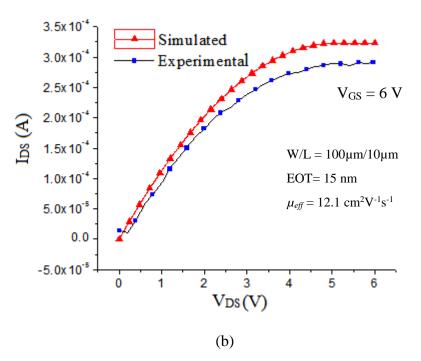

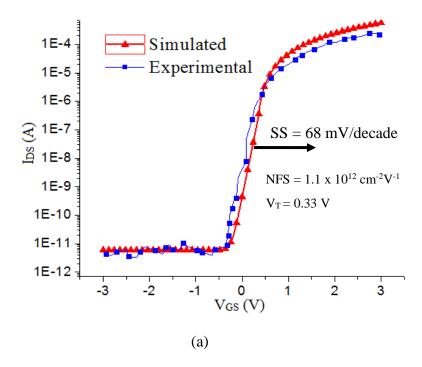

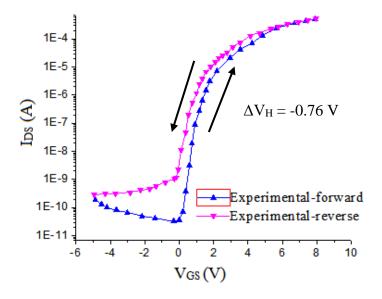

| Fig. 5.10 | Experimental [109] versus simulated characteristics of ZnO based                                           |      |

|           | TFT with La <sub>2</sub> O <sub>3</sub> gate dielectric (a) Transfer characteristics, (b) Output           |      |

|           | characteristics                                                                                            | . 98 |

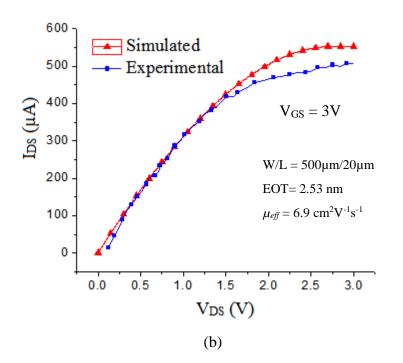

| Fig. 5.1  | 1 Experimental [122] versus simulated characteristics of ZnO based                                         |      |

|           | temperature (1/T) for different ZnO film thicknesses                                                       |      |

|           | characteristics                                                                                            | . 99 |

| Fig. 5.12 | 2 Transfer characteristic of ZnO/ ZrO <sub>2</sub> based TFT under forward and                             |      |

|           | reverse V <sub>GS</sub> sweep.                                                                             | 101  |

| Fig. 5.1. | 3 Transfer characteristic of ZnO/ La <sub>2</sub> O <sub>3</sub> based TFT under forward and               |      |

|           | reverse V <sub>GS</sub> sweep [109]                                                                        | 101  |

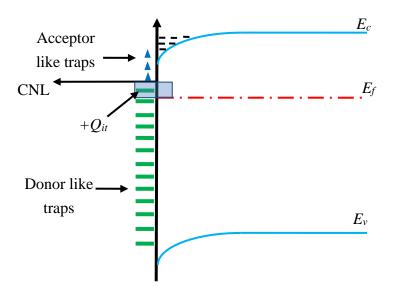

| Fig. 5.1  | Band diagram at ZnO/ dielectric interface showing charge neutrality                                        |      |

|           | level (Shaded region denotes unoccupied donor like traps at the interface)                                 | 102  |

|           |                                                                                                            |      |

| Fig. A.1  | Schematic representation of bottom-gate MIS structure.                                                     | 109  |

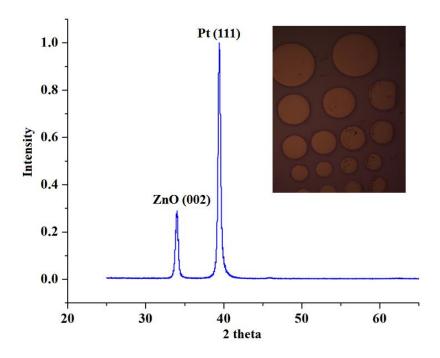

| Fig. A.2  | Optical micrograph image of MIS-C structure and XRD spectra of ZnO                                         |      |

|           | Film deposited over ZrO <sub>2</sub> gate dielectric                                                       | 110  |

| Fig. A.3  | High frequency (at 1 MHz) capacitance-voltage (C-V) analysis of ZrO <sub>2</sub> /                         |      |

|           | ZnO MIS Structure                                                                                          | 111  |

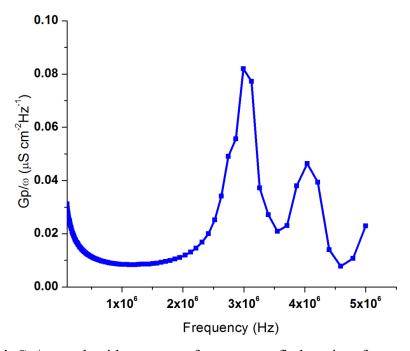

| Fig. A.4  | I Gp/ω graph with respect to frequency to find out interface state density                                 |      |

|         | $(D_{it})$                                                                               | 112 |

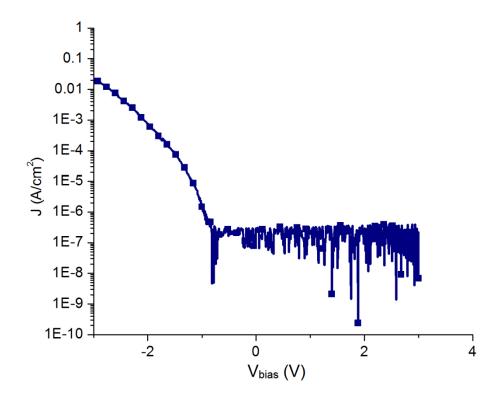

|---------|------------------------------------------------------------------------------------------|-----|

| Fig. A. | 5 Gate leakage current density versus applied gate to bulk bias (V <sub>bias</sub> ) for |     |

|         | ZrO <sub>2</sub> / ZnO MIS- structure.                                                   | 113 |

# **LIST OF SYMBOLS**

T Absolute temperature

$D_G$  Average grain size  $R_a$  Average roughness

$E_g$  Band-gap

*k*<sub>B</sub> Boltzmann constant

L Channel length

T<sub>0</sub> Characteristic temperature

$v_c$  Collection velocity

$\Delta E_c$  Conduction band offset

*N*\* Critical concentration

J Current density

g(E) Density of states

$N_c$  Density of states of electron in conduction band

$\kappa_{ox}$  Dielectric constant of oxide

$|\psi|$  Difference of threshold voltage and flat band voltage of ZnO TFT

N Dopant concentration

I<sub>DS</sub> Drain current

V<sub>DS</sub> Drain to source voltage

$\mu_{poly}$  Effective grain dominated mobility in polycrystalline channel

*m*\* Effective mass

$\mu_{\it eff}$  Effective mobility

E Electric field

*χ* Electron affinity

*n* Electron concentration

$m_0$  Electron rest mass

q Electronic charge

$\varepsilon_{\infty}$  Electronic part of dielectric constant

$D_{GB}(E)$  Energy dependent acceptor type DOS

$E_f$  Equilibrium Fermi level

S\* Euclidean distance from ideal solution

S<sup>-</sup> Euclidean distance from worst case solution

$\mu_{FE}$  Field effect mobility

f Figure of merit

β Full width half maxima

F Functional parameter (Ashby)

$J_{GL}$  Gate leakage current density

V<sub>GS</sub> Gate to source voltage

$\mu_{GB}$  Grain boundary scattering dominated mobility

$N_t$  Grain boundary trap density

A\* Ideal solution (TOPSIS)

$D_{it}$  Interface state density

$N_{it}$  Interface trap charge density

$Q_i$   $i^{th}$  alternative of VIKOR

$G_i$  Maximum group utility

$\phi_{ms}$  Metal-semiconductor work function difference

$R_i$  Minimum regret of the opponent

$\mu_{GB\parallel}$  Mobility due to longitudinal grain boundaries

$\mu_{GB\perp}$  Mobility due to transverse grain boundaries

A Negative ideal solution (TOPSIS)

$N_G$  Number of grains in polycrystalline channel

$I_{on}/I_{off}$  On-to-off ratio

$C_{ox}$  Oxide capacitance per unit area

t<sub>acc</sub> Physical extent of accumulation layer in ZnO channel

$\phi_b$  Potential barrier

$C_i$  Relative closeness of  $i^{th}$  alternative from ideal solution

$\varepsilon_r$  Relative permittivity

$\rho$  Resistivity

A\* Richardson constant

$R_q$  Root mean square roughness

$\mu_{sat}$  Saturation mobility

S Schottky barrier pinning factor

$R_s$  Sheet resistance

D<sub>GB</sub> Size of grain boundary

$\mu_s$  Surface mobility

V<sub>T</sub> Threshold voltage

$\Delta V_T$  Threshold voltage shift

$g_m$  Transconductance

Vox Voltage dropped across oxide

σ Weight of maximum group utility

$D_d$  Width of depletion region

W Width of the TFT

### LIST OF ABBREVIATIONS

AFM Atomic Force Microscopy

ALD Atomic Layer Deposition

AMLCD Active-Matrix Liquid Crystal Displays

AMOLED Active-Matrix Organic Light Emitting Diodes

ATSC Advance Television System Committee

BJT Bipolar Junction Transistor

BLO Backside Lift Off

BUV Back Side Ultraviolet

CAD Computer-Aided Design

CBO Conduction Band Offset

CMOS Complementary Metal Oxide Semiconductor

CNL Charge Neutrality Level

C–V Capacitance – Voltage

DOS Density of States

EOT Equivalent Oxide Thickness

FESEM Field Emission Scanning Electron Microscopy

FET Field-Effect Transistor

FN Fowler Nordheim

FPD Flat Panel Display

GB Grain Boundary

HDTV High-Definition Television

*a*–Si:H Hydrogenated Amorphous Silicon

IC Integrated Circuit

ITO Indium Tin Oxide

I–V Current – Voltage

LOCOS Local Oxidation of Silicon

LTPS Low Temperature Polysilicon

MADM Multi- Attribute Decision Making

MBE Molecular Beam Epitaxy

MCDM Multi-Criteria Decision Making

MFP Mean Free Path

MIS-C Metal-Insulator-Semiconductor-Capacitor

MOCVD Metal-Organic Chemical Vapor Deposition

MODM Multi-Objective Decision Making

MOSFET Metal-Oxide-Semiconductor Field-Effect-Transistor

$\Delta$  |TEC| Mismatch in thermal expansion Coefficient

MTR Multiple-Trapping and Release

NBTI Negative-Bias Temperature Instability

OTFT Organic Thin Film Transistor

PBTI Positive-Bias Temperature Instability

PLD Pulsed Laser Deposition

Poly-Si Polycrystalline Silicon

QVGA Quarter Video Graphics Array

RCA Radio Corporation of America

RF Radio Frequency

SPICE Simulation Program with Integrated Circuit Emphasis

SS Subthreshold Slope

TCO Transparent Conductive Oxide

TFT Thin Film Transistor

TOPSIS Technique for Order Preference by Similarity to Ideal Solution

TTFT Transparent-Thin Film Transistor

VIKOR VlseKriterijumska Optimizacija I Kompromisno Resenje in Serbian

XPS X-Ray Photoelectron Spectroscopy

XRD X-Ray Diffraction

# **CHAPTER - 1**

### INTRODUCTION

#### 1.1 Evolution of Thin Film Transistor (TFT) Technology

The evolution history of metal-oxide-semiconductor field-effect transistor (MOSFET) and TFTs are almost similar. In 1930, the concept of field effect transistor (FET) was introduced by J. E. Lilienfield [1]. On his patent "method and apparatus for controlling electric currents", he proposed a three terminal structure using copper-sulfide semiconducting layer deposited over glass substrate and aluminium foil as a gate, but oxide was absent in this structure. Later in 1935, Oskar Heil in his British patent [2] gave a description of modulation in resistance of semiconducting layer placed between two electrodes via capacitive coupling from a third electrode. However, the concept of FET took time to commercialize because it needed sophisticated fabrication techniques for reliable and reproducible device behaviour. TFTs are also essentially a kind of field effect transistor, where the modulation in current at deposited semiconducting thin film is achieved by varying vertical electric field using gate electrode.

In early days, compound semiconductors like CdSe or CdS received lot of interest for TFT applications because of their high mobility (40 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) [3], [4]. But, because of limitation of fabrication technology, mass production of these TFTs were not realized. Meanwhile, due to the evolution of silicon technology (BJT and MOSFET), the focus shifted to developing silicon based integrated circuits (ICs) which offers enhanced performance, high reliability, reproducibility and high packing density. However, IC technology needs single crystal silicon as a substrate which is very costly and undergoes

high temperature processing. Researchers find this as a motivation and tried to look other cheaper options available for channel and substrate material, and technology to fabricate cheaper TFT in low thermal budget. So, different materials (*a*–Si:H, poly–Si, oxide semiconductors and organic material) were proposed and used to fabricate TFTs.

In 1968, Boesen and Jacobs proposed lithium (Li) doped ZnO semiconducting material as a channel layer to realize insulated gate FET structure [5]. The fabricated structure resulted in depletion type FET with  $V_T = -8$  V. In 1979, one major breakthrough came as hydrogenated amorphous silicon (a–Si:H) TFT was fabricated in glass substrate using PECVD (Plasma Enhanced Chemical Vapour Deposition) with silicon nitride (Si<sub>3</sub>N<sub>4</sub>) as a gate dielectric [6]. However, the mobility of this TFT was too low to drive the pixel of OLED display. Besides this, a–Si:H exhibits photoconductive properties and, hence, leakage due to visible light exposure becomes a major concern. Even then, in early days, a–Si:H TFTs were used in LCD display for mass production due to its cost effectiveness and compatibility with existing IC technology. Later, the researchers addressed the issue of extreme low mobility ( $\sim$ 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) of a–Si:H TFTs and developed a method of depositing poly–Si in glass substrate which was able to obtain a mobility value as high as 360 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [7]. However, this process requires very high temperature ( $\sim$  600 °C) anneal for re-crystallization. Not only that, due to polycrystalline nature of deposited film, it also suffers from grain boundary scattering.

In late 1990s, a new class of TFTs named as OTFT (organic thin film transistor) was introduced. Organic thin film deposition is advantageous as it need low thermal budget and does not require costly vacuum equipment. Organic films can be easily spin coated or printed on the substrate at the room temperature. The main challenge with the OTFT is poor mobility. Though some of the OTFTs have been demonstrated for high field mobility [8], high mobility OTFT often requires a large operating voltage, that results in power consuming display panels. Later major breakthrough came as, R. L. Hoffman *et al.* demonstrated the new generation transparent TFT (TTFT) using ZnO as a channel [9]. This TFT showed an optical transmission of 75% in the visible portion of the electromagnetic spectrum. The C–V (capacitance–voltage) measurement indicated n–type, enhancement-mode TFT with excellent on-to-off ratio ( $I_{on}$ /  $I_{off}$ ) of 10<sup>7</sup>, high

threshold voltage (10 – 20 V) and decent field effect mobility ( $\mu_{eff} = 0.3$  to 2.5 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>). In last decade, various breakthroughs came in ZnO based TFT technology which include low threshold voltage, improved field effect mobility and room temperature deposition. Fig. 1.1 shows the timeline of TFT technology development, using different channel materials prior to the year 2003.

**Fig. 1.1** Timeline of TFT technology development (prior to next generation ZnO TFT)

In last decade, TFT technology has been experiencing rapid transition from *a*–Si:H and polysilicon based TFT to ZnO based TFT, and because of this transition, transparent TFT has become a reality. Over the years, advancement in TFT technology has become a driving force of human civilization. The consumers which were earlier passive are now connected to each other through various electronic gadgets like laptops, tablets, phablets and smart phones due to advancement in large area electronics. TFTs are commonly used as a pixel addressing element and as a driving transistor in active matrix liquid crystal display (AMLCD) and active matrix organic light emitting diode (AMOLED) display panels [10]–[13]. Fig. 1.2 shows the use of TFT as a switching transistor (T<sub>1</sub>) and driving transistor (T<sub>2</sub>) in a typical pixel circuit.

Fig. 1.2 Typical two TFT, OLED pixel driver circuit

Although, the display technologies like LCD were available for over last six decades, they were unable to compete with well-established CRT technology. In the last decade, the scenario has changed drastically due to rapid development of AMOLED and AMLCD based devices together with Micro Electro Mechanical System (MEMS) technology (especially smart phones and tablets). According to the IHS *Display Long-Term Demand Forecast Tracker*, the worldwide revenue of the TFT LCD improved from about \$1 billion in 1989 to near \$131.4 billion in 2014. In the same span, the technology has seen transition from *a*–Si:H TFT to ZnO based TFT. The main producers expanded from Japan to the surrounding Asia Pacific countries, such as South Korea, Taiwan, and China. Some of the key players in the zinc oxide based TFT market are Sharp Corporation (Japan), Sony Corporation (Japan), Apple Inc. (U.S.), LG Electronics (South Korea), Asus (Taiwan), AU Optronics (Japan), Samsung Group (South Korea), and Fujitsu (Japan).

#### **1.2 ZnO TFT**

In ZnO TFTs, ZnO is used as a semiconducting channel layer as it possesses high mobility and high optical transparency in visible spectrum. ZnO based TFTs provide several advantages over a-Si:H based TFT. First, ZnO can be grown as a crystalline material at relatively lower deposition temperature. Second, it can be deposited on various substrates made up of silicon, plastic, amorphous glasses [14] which make it possible to realize a total transparent ZnO based TFT. Moreover, because of its wide band gap, the characteristics of ZnO do not degrade in the exposure of visible light. Finally, ZnO thin film can achieve considerably higher mobility than a-Si:H ( $\sim$ 12 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, compared to 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> for a–Si:H produced in similar conditions) [15]. ZnO TFT typically consists of ZnO channel, gate dielectric and three electrodes namely source, drain and gate. Depending upon the position of source and drain with respect to the channel, one can define TFT structures as coplanar or staggered. In coplanar structure, source and drain are on the same side with respect to channel, while in staggered structure source and drain are on the opposite side with respect to channel. Inside these, bottom-gate and top-gate structures exist depending on whether the gate electrode is on bottom or top of the structure [16]. Fig. 1.3 shows a schematic view of one of the most popular topology of ZnO TFT i.e. staggered bottom-gate ZnO TFT.

**Fig. 1.3** Schematic view of bottom-gate ZnO TFT

The operation of a TFT is similar to that of MOSFET i.e. for gate to source voltage (V<sub>GS</sub>) greater than threshold voltage (V<sub>T</sub>), electron flows from source to drain through the ZnO semiconductor. However, important difference exists in TFT and MOSFET, as TFT uses cheaper substrate material like glass or plastic as a substrate whereas, MOS uses the single crystal silicon as a substrate, which accounts for higher electrical performance of MOSFET over TFT. In MOSFET, the substrate material itself serves as a channel layer whereas, in TFTs deposited semiconducting film on the substrate is used as a channel layer. Moreover, MOSFET fabrication process temperature usually exceeds 1000 °C whereas the thermal budget associated in fabrication of TFT is quite less, as it is limited by softening point of substrate. In MOSFET, at source and drain the p-n junctions are present however; in oxide TFT they are not present. Another important difference between MOSFET and TFT exist in terms of conduction mechanism. In MOSFET, current conduction is achieved after formation of an inversion layer close to the interface between semiconductor and gate dielectric while in TFT, it is achieved by formation of an accumulation layer.

In order to study the performance of ZnO based TFT, it is essential to know about the figures of merit of the device. These figures of merit are extracted from static characteristics of the TFT and are discussed in the following section.

#### 1.3 TFT Performance Parameters

Performance of TFT is defined mainly by following figures of merit:

- **a.** On-to-off ratio  $(I_{on}/I_{off})$

- **b.** Threshold voltage  $(V_T)$

- **c.** Subthreshold slope (SS)

- **d.** Mobility  $(\mu)$ .

These performance parameters are extracted from the output and transfer characteristic of TFT. Fig. 1.4 shows typical transfer characteristic ( $I_{DS}$ - $V_{GS}$ ) of low operating voltage ZnO TFT, where drain to source current ( $I_{DS}$ ) is plotted in logarithmic axis.

Fig. 1.4 Typical transfer characteristic of low voltage ZnO based TFT

$I_{off}$  of a TFT is defined as the source to drain subthreshold leakage current and is measured when gate to source voltage (V<sub>GS</sub>) is equal to 0 V and drain to source voltage (V<sub>DS</sub>) is equal to supply voltage [17].  $I_{off}$  determines the standby or off-state power consumption of TFT panels and its minimum value is generally given by the gate leakage current or noise level of the measurement equipment. In TFT, the on-current ( $I_{on}$ ) is defined as current in saturation region when both V<sub>DS</sub> and V<sub>GS</sub> are equal to supply voltage. A high value of  $I_{on}$  ensures fast switching speed of a TFT. Hence,  $I_{on}/I_{off}$  is an important performance metric of ZnO TFT, and needs to be kept as high as possible for the low power, high speed TFT applications.

Threshold voltage  $(V_T)$  in ZnO TFT corresponds to the value of gate to source voltage which can form an accumulation layer close to semiconductor dielectric interface, between the source and drain terminal. For n-type TFT, if  $V_T > 0$  V then, the device is known as enhancement type device; else, depletion mode device. Usually enhancement

type device is preferred as no  $V_{GS}$  is required to turn off the transistor thereby minimizing power dissipation. However, in oxide TFTs exact estimation of threshold voltage is difficult due to structural disorder of semiconducting channel.

Another important performance parameter of a TFT is subthreshold slope (SS) (sometimes called as inverse subthreshold slope or subthreshold swing) which is a measure of necessary gate to source (V<sub>GS</sub>) required to increase drain current (I<sub>DS</sub>) by one decade. A smaller value of SS results in low power consumption and higher speed. SS is defined as inverse of maximum slope of transfer characteristic [16].

$$SS = \left(\frac{d \log(I_{DS})}{dV_{GS}} | \max\right)^{-1} \qquad \dots (1.1)$$

Mobility is related with the efficiency of carrier transport in a semiconductor. It affects directly the drain current and operating frequency of the TFT. In polycrystalline ZnO film, mobility is affected by several scattering mechanism like scattering at the grain boundaries, lattice vibration and ionized impurities. Moreover, since the motion of carriers is constrained to narrow region close to semiconductor dielectric interface, additional source of scattering like columbic scattering due to dielectric charge is also present. Gate field perpendicular to the channel also has a significant effect on mobility. In TFTs, mobility can be extracted from the transfer or output characteristics in several ways [18].

One way is to define mobility as effective mobility ( $\mu_{eff}$ ). If  $C_{ox}$  is gate dielectric capacitance per unit area and W/L is aspect ratio of the transistor then  $\mu_{eff}$  can be defined in terms of conductance ( $g_{ds} = \partial I_{DS} / \partial V_{DS}$ ) in deep triode region (low value of  $V_{DS}$ ) as:

$$\mu_{eff} = \frac{g_{ds}}{C_{ox}(V_{GS} - V_T)(W/L)}$$

...(1.2)

The calculation of  $\mu_{eff}$  includes the effect of  $V_{GS}$  on mobility. However, to compute  $\mu_{eff}$  it is required to have exact value of threshold voltage  $V_T$ . Moreover, calculation of  $\mu_{eff}$  is also sensitive to contact resistance due to low value of  $V_{DS}$ . An alternative way of defining mobility is by defining field effect mobility ( $\mu_{FE}$ ) in terms of transconductance ( $g_m = \partial I_{DS} / \partial V_{GS}$ ) for low value of  $V_{DS}$ , and is expressed as:

$$\mu_{FE} = \frac{g_m}{C_{ox}V_{DS}(W/L)}$$

...(1.3)

$\mu_{FE}$  is the most widely used parameter as it does not require the value of  $V_T$  and the derivative of transfer characteristic can be easily obtained. Similarly, mobility in saturation region ( $\mu_{sat}$ ) can be extracted from the graph of square root of drain current ( $\sqrt{I_{DS}}$ ) vs. gate to source voltage, as:

$$\mu_{sat} = \frac{\left(\frac{d(\sqrt{I_{DS}})}{dV_G}\right)^2}{\frac{1}{2}C_{ox}\frac{W}{L}} \qquad \dots(1.4)$$

Table 1.1, illustrates the comparative analysis of various TFT. It is clear from the table that poly – Si TFT offers highest mobility. But, its performance is affected by high leakage current and very slow response (high value of SS). On the other hand, ZnO TFT offers decent field effect mobility, excellent on-to-off ratio ( $I_{on}/I_{off}$ ) and fast response. But, it suffers from the requirement of high threshold voltage (V<sub>T</sub>). However, this can be lowered by the incorporation of high– $\kappa$  dielectric as a gate dielectric and this will be discussed in detail, in chapter-4.

**Table 1.1** Comparative analysis of various TFTs

| Performance                                           | a-Si:H TFT | Poly-Si TFT | Organic TFT | ZnO TFT  |

|-------------------------------------------------------|------------|-------------|-------------|----------|

| parameters                                            | [19]       | [20]        | [21]        | [22]     |

| $\mu_{FE}  (\text{cm}^2 \text{V}^{-1} \text{s}^{-1})$ | 0.8        | 37          | 0.02        | 20       |

| $I_{on}/I_{off}$                                      | $10^{7}$   | $10^{5}$    | $10^{6}$    | $10^{9}$ |

| $V_T(V)$                                              | 4.5        | 3.4         | 0.7         | 6        |

| SS (V/ dec)                                           | 0.5        | 1.10        | 0.17        | 0.14     |

#### 1.4 Research Motivation and Objectives

The rate of progress of TFT technology has been quite commendable. Industry R&D activities have been aiming at improving the throughput, cost and yield of ZnO TFTs. As mentioned earlier, TFTs performance highly depends upon the ZnO film quality and its interface with the gate dielectric. ZnO based TFT provide several advantages over its a–Si based counterpart. However, inspite of its huge potential, in the flat panel display (FPD) market, it carries a significant number of challanges.

- I. The room temperature deposition of high quality and highly uniform ZnO film is extremely important as it supports wide range of substrates including glass, plastic and silicon. At the same time, it is also important to analyze the structural and electrical properties of ZnO film, as it determines the TFT behavior.

- II. ZnO TFTs primarily suffer from high threshold voltage, compared to nc–Si, poly–Si and *a*–Si-H TFT. e.g. ZnO TFT with Si<sub>3</sub>N<sub>4</sub> or SiO<sub>2</sub> gate dielectric exhibits a very high value of threshold voltage (10 20 V) [23]. However, high–κ dielectric can be used as a gate dielectric to reduce threshold voltage. But, the selection of high–κ dielectric is not straightforward, e.g. dielectrics having very high dielectric constant may not have good conduction band offset to ZnO, and a high value of band offset is needed for low leakage ZnO TFT. Other criteria, which are very critical while selecting potential gate dielectric are band-gap of dielectric material (should be as high as possible), its thermodynamic stability and quality of interface. Usually dielectrics which have high value of band-gap possess low value of dielectric constant and vice versa. So clearly there is a trade- off among various material indices for selection of gate dielectric.

- III. Academic research in many institutions has helped in developing the device models for the oxide TFT performance and the associated technical issues. But, each of these models has their own conditions of validity and also has limited range of applicability. In principle, ZnO TFT operates in accumulation mode as opposed to inversion mode. In accumulation mode TFTs, the threshold voltage has remained ambiguous due to existence of grain boundary traps in polycrystalline semiconducting channel. In these grain boundary traps, the carriers get trapped and due to this a very

- limited number of carriers remains available in extended states at room temperature. Hence, a model for threshold voltage needs to be developed, which can introduce the effect of grain boundary trap state density in threshold voltage.

- IV. All kinds of TFTs (a–Si:H, poly–Si, organic, oxide) suffer from threshold voltage instablity and need significant attention for improved and reliable performance. These devices can be commercially used in AMOLED and AMLCD applications successfully, only if, the reliablity and reproducibility can be assured. The interface of ZnO with gate dielectric is very critical and needs to be optimized so that the interface state density ( $D_{ii}$ ) can be minimized. The ZnO dielectric interface is also very crucial to determine subthreshold behavior of device.

- V. Moreover, as most of the design engineers need computer aided design (CAD) tools compaitable SPICE models for the design of large area FPDs, it is needed to develop either a new TFT SPICE model or need to adapt existing SPICE model effectively. Though, HSPICE LEVEL-40 is customized for TFTs but its use is covered by a license [24]. This limits its adoption in early development phase of TFT technology. Adapting existing SPICE model for ZnO TFT application is a good idea but, it needs a detailed investigation so that in simulation, behaviour of ZnO based TFT can be produced with the least possible error compared to experimental characteristic.

Thus, to address the above mentioned challenges in ZnO based TFT, the following objectives of this thesis are formulated:

- **I.** To deposit and analyze the structural and electrical properties of ZnO films.

- **II.** To identify most suitable gate dielectric material for low threshold voltage and low leakage ZnO based TFT using material selection methodologies.

- **III.** To develop analytical model for mobility and threshold voltage including the effect of structural disorder in channel layer.

- **IV.** To adapt existing SPICE model for behavioral modeling of ZnO based TFT and its validation with experimental work.

- V. To investigate threshold voltage instability present in ZnO based TFT using current voltage (I–V) or capacitance voltage (C–V) characteristics.

#### 1.5 Thesis Organization

**Chapter 1** provides an overview of TFT in general and ZnO TFT in particular. It compares TFT with conventional MOSFET and discusses the TFT performance parameters and its structure. Comparative analysis of various TFTs (*a*–Si:H, poly–Si, organic and ZnO based TFT) is done. Finally, it provides research motivation and objective of the thesis.

Chapter 2 deals with a comprehensive literature review on ZnO based TFT. It describes ZnO properties as a semiconductor and provides fabrication flow of transparent ZnO TFT. It also discusses the technological challenges on ZnO based TFT like high threshold voltage, and provides the review of transport mechanisms in ZnO based TFT. It wraps up the discussion with electrical instability in ZnO based TFTs.

Chapter 3 discusses deposition and characterization of ZnO films deposited at room temperature using RF magnetron sputtering. Two different sputtering targets, ZnO ceramic target and Zn metallic target were used for the deposition. Both types of film were well studied using structural and electrical characterization. Additionally, this chapter also provides film thickness dependent study on structural and electrical properties.

**Chapter 4** presents the investigations on high–κ dielectrics for low operating voltage and low leakage ZnO TFT using three material selection methodologies namely *Ashby's approach*, *Technique for Order Preference by Similarity to Ideal Solution* (TOPSIS) and *VlseKriterijumska Optimizacija I Kompromisno Resenjein in Serbian* (VIKOR). Various material properties such as dielectric constant, conduction band offset to ZnO, band-gap and temperature coefficient mismatch of high–κ to ZnO are investigated to find out the most promising gate dielectric material.

**Chapter 5** formulates an analytical model of threshold voltage as a function of grain boundary trap density, by assuming grain boundary as continuous one dimensional line charge. In the process, it discusses the thermionic emission dominated mobility model in detail. It is followed by adaption of SPICE LEVEL-3 model for ZnO based TFT and its validation. Finally, it investigates the origin of threshold voltage instability in ZnO based TFT using C–V or I–V characteristics and discusses its impact on TFT performance.

**Chapter 6** summarizes the outcomes of this research and provides suggestions for future work and research direction related to the area of ZnO based TFTs.

**Appendix** sections A.1 - A.4 discuss the fabrication and characterization of ZnO / ZrO<sub>2</sub> metal-insulator-semiconductor-capacitor (MIS-C) structure. The characterization includes high frequency C-V analysis, I-V analysis and interface state density ( $D_{it}$ ) measurement.

# **CHAPTER - 2**

## ZnO BASED TFT: LITERATURE REVIEW

#### 2.1 Recent Development in ZnO based TFT Technology

This section reports recent development in ZnO based TFT technology. Fig. 2.1 shows major development of new generation ZnO TFT technology. In 2006, Liu et al. fabricated a high performance ZnO TFT on a glass substrate using RF magnetron sputtering [25]. In the same year, Park et al. successfully demonstrated 2.15 inch AM-OLED panel driven by ZnO -TFT in which ZnO thin film was deposited by ALD (Atomic layer deposition) technique [26]. Chiang et al. [27] fabricated transparent TFTs with a new set of oxide semiconductor, zinc tin oxide which is composed of heavy metal cations. The channel layer was deposited via RF magnetron sputtering and the result shows that the post – deposition annealing affects mobility and threshold voltage of device. A mobility of 50 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> and a drain current on-to-off ratio  $(I_{on}/I_{off})$  greater than  $10^7$  was obtained [27]. Kwon et al. [28], fabricated a Ga<sub>2</sub>O<sub>3</sub>–In<sub>2</sub>O<sub>3</sub>–ZnO (GIZO) TFT with bottom gate topology to drive 4-in QVGA AMOLED display. In 2014, Ma et al. [29] proposed high breakdown voltage ZnO TFT using ZrO<sub>2</sub> as the high-κ gate dielectric with ALD deposition technique and a thermal budget less than 130 °C. A 5 nm thin layer of ZrO<sub>2</sub> was used as gate dielectric; this transistor showed enhancement type operation with gate bias voltage less than 2 V due to high–κ dielectric.

Fig. 2.1 Major development in ZnO TFT technology

In past few years, various efforts have been done for improving the device performance of ZnO TFT. In 2014, to overcome the growing demand of enhanced mobility of TFT for OLED application, Song *et al.* [30] proposed a methodology to fabricate high mobility ZnO- graphene hybrid TFT. It combines the advantage of graphene with extremely high mobility and ZnO film with high on-to-off ratio. Graphene was synthesized using thermal CVD and a 25-mm-thick Cu foil was used as a catalytic substrate for graphene growth. A dilute ZnO solution was spin-coated onto the graphene/SiO<sub>2</sub>/Si substrate. Hybrid TFT exhibited ambipolar behavior, high on-to-off ratio of 10<sup>5</sup>, and very high mobility of 329.7 ± 16.9 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. The ambipolar behavior of the hybrid (ZnO/Graphene) TFT could be due to the superimposed density of states (DOS) involving the donor states in the wide band-gap of ZnO thin films and the linear dispersion of monolayer graphene. In 2015, Lee *et al.* [31] investigated thin film of zinc oxynitride (ZnON) a glassy composite of ZnO, ZnO<sub>x</sub>N<sub>y</sub> and Zn<sub>3</sub>N<sub>2</sub> for high mobility TFTs. Fabrication of ZnON thin film involves an anion control strategy based on the substitution of oxygen with nitrogen in ZnO by adopting the argon plasma process. The

channel mobility of ZnON TFT was extracted to be 138 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>. The STEM image of ZnON material shows uniform contrast throughout the entire thin film, and this uniformity is the root cause of enhanced mobility in ZnON thin film [31]

Another major issue with TFTs are their sensitivity towards threshold voltage shift. A prolonged use or operation under excess bias can cause increased temperature of display device, which in turn, can cause significant shift in threshold voltage of pixel- TFTs. To increase the immunity of TFTs over gate bias stress, Nayak *et al.* [32] in 2015, investigated a highly stable ZnO TFT using ZnO/HfO<sub>2</sub> multilayer channel structure. Inserting ultra-thin HfO<sub>2</sub> layers between ZnO films greatly improve gate- bias stress stability compared to TFT with a single layer of ZnO. The thin HfO<sub>2</sub> layer acts as a passivation layer which prevents the adsorption of water and oxygen molecules in ZnO film hence improves the gate-bias stress stability of ZnO TFT [32].

Oxide semiconductors TFT have been mainly limited to n–type electronic applications because of the lack of availability of p–type oxide semiconductor. Researchers from University of Alberta, in 2016, investigated the ZnO semiconductor that is able to sustain a strong p–type inversion layer using ultra-thin high–κ dielectric constant barrier when sourced with a p–type material [33]. A ZnO film of 25 nm was deposited on a p–type (100) silicon wafer and a 4 nm thick HfO<sub>2</sub> high–κ oxide layer was deployed as gate insulator. The presence of ultra-thin high–κ insulator reveals the presence of enhanced tunnel current of electrons from the metal (Al/ Au), through the barrier, into ZnO. The resulting performance of this device (HfO<sub>2</sub>/n-ZnO/p-Si) exhibited the highest reported current (63 mA/mm), and transconductance densities (56 mS/mm).

### 2.2 Fabrication of Bottom Gate ZnO TFT

For the fabrication of TFT, typically, glass is used as a substrate material. From 1990 to 2010, glass substrate size has been constantly enlarged i.e. up to 2.88 × 3.15 m, thus supported the large area electronics. This also corresponds to almost 6 pieces of 65 - inch TFT array patterned over the glass substrate. For fabricating top gated TFT, one can follow similar mask steps as used in MOSFET. However, for TFT isolation one doesn't need the device isolation techniques like LOCOS and trench isolation as the substrate itself is insulator. Further, in TFT fabrication the semiconducting layer and dielectric is deposited on substrate.

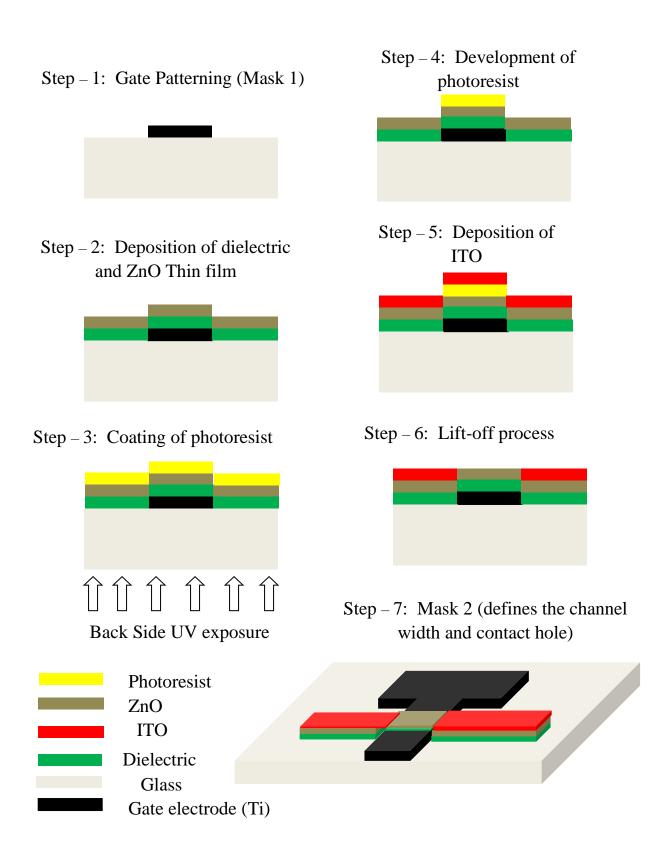

To fabricate, bottom gate staggered ZnO TFT, back side ultraviolet (BUV) exposure is preferred. Geng *et al.* proposed a self aligned process (where gate is defined first and with respect to gate source and drain are defined) involving BUV and five photo mask [34]. Self aligned process provides immunity to mask alignment errors. Fan *et al.* fabricated the bottom gate staggered ZnO TFT using two- mask process and backside-lift-off (BLO) scheme [35] shown in Fig. 2.2. Step – 1 shows, a Ti layer is deposited onto a glass substrate by using thermal evaporation and then it is patterned by the first photomask and defines the gate electrode. Step – 2 involves the deposition of gate dielectric layer and it is followed by the deposition of ZnO thin layer using RF sputtering. Step – 3 involves lithography, where the patterned gate serves as a mask for back – side UV exposure. In Step – 4, the development of photoresist is done and after the development photoresist remains over the unexposed portion. Step – 5 involves deposition of indium tin oxide (ITO) for source and drain. Step – 6 involves lift-off process and uses photoresist as sacrificial layer. Following the BLO the second photo-mask were used to define the channel width and contact region.

Fig. 2.2 Two-mask process flow of bottom gate ZnO TFTs with self-aligned structure

The performance of ZnO based TFT greatly depends upon structural and electrical properties of ZnO films. Similarly, choice of gate dielectric is highly important as it determine operating voltage and gate leakage of TFT. The next subsections discuss about, ZnO as a semiconductor and various gate dielectrics for ZnO TFT.

### 2.2.1 ZnO Semiconductor

ZnO is a wide band-gap (3.4 eV), II-VI compound semiconductor, having a wurtzite structure (most stable) with lattice spacing a = 0.325 nm and c = 0.521 nm [14], [15]. The crystal structure of ZnO material is shown in Fig. 2.3. The zinc (Zn) atoms are tetrahedrally co-ordinated to four oxygen atoms, with the oxygen atom occupying the octahedral sites. Intrinsically, ZnO is an n-type semiconductor primarily due to presence of intrinsic native defects (oxygen vacancies and Zn interstitials). Hydrogen is considered as main cause of n-type doping in undoped ZnO. The Zn interstitials acts like a shallow donor which constitutes the donor level just below the bottom of conduction band, while the oxygen vacancies act like a deep donor.

Fig. 2.3 ZnO crystal structure

Table 2.1 lists various material parameters of ZnO semiconductor [36]. ZnO is promised to be an attractive material for numerous applications in electronics, photonics, sensing and acoustic [37]. The primary applications of ZnO lie in the area of Transparent TFT owing to its high conductivity and high optical transparency and in the area of photonics as an optical emitter due to its high exciton binding energy (~ 60 meV). Another promising area of ZnO is acoustic wave devices mainly due to its large electrochemical coupling along *c* axis. One emerging application area of ZnO is its possible use as a transparent conductive oxide (TCO). As the world is facing the shortage of the growing demand of indium for ITO, ZnO is promised to be the alternate TCO because of its good conductivity, excellent surface smoothness, low deposition temperature, high optical transparency and good etching chemistry [37]. A great deal of research is being carried out in ZnO nanostructures like ZnO nanowires, nanobelts and their integration with mainstream semiconductor like Si, GaAs and GaN. High crystalline quality and good charge carrier property are the main reason driving its use as nanoscale devices [Photodetectors, Lasers, Surface acoustic wave device (SAW)].

Table 2.1 Material parameters of ZnO

| Density                                          | 5.606 gcm <sup>-3</sup>                        |

|--------------------------------------------------|------------------------------------------------|

| Stable phase @ 300K                              | Wurtzite                                       |

| Melting point                                    | 1975 <sup>0</sup> C                            |

| Band-gap $(E_g)$ @ 300K                          | 3.4 eV                                         |

| Relative permittivity of ZnO ( $\varepsilon_r$ ) | 8.12                                           |

| Refractive Index                                 | 2.008                                          |

| Hall mobility $(\mu_H)$                          | $150 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ |

| Electron affinity $(\chi)$                       | 4.6 eV                                         |

| Charge neutrality level (CNL) from vacuum level  | 3.27 eV                                        |

| Exciton binding energy                           | 60 meV                                         |

| Effective mass of electron in conduction band    | $0.318 \ m_o$                                  |

| Effective mass of holes in valence band          | 0.5 m <sub>o</sub>                             |

where  $m_o$  is electron rest mass.

ZnO semiconductor is commonly doped with group III elements like aluminum (Al), gallium (Ga) and indium (In) to make it n-type. However, obtaining a stable p-type behavior in ZnO semiconductor is still a challenge. To achieve the projection of thin film technology by Nikki asia [38] such as, CMOS ICs using oxide TFT, one need stable ptype ZnO semiconductor so that CMOS realization (where both n-type and p-type FET are present) will be possible. p-type ZnO can also facilitate the material for light emitting devices emitting in UV region because of its high exciton energy. Though researchers have achieved limited success in obtaining stable and reproducible p-type ZnO, the widespread fabrication of ZnO homojunction p-n junction LED is still a challenge. To obtain reliable p-type ZnO, one needs to minimize the high donor defect density. Researchers have used N<sub>2</sub> for the same purpose, in which N<sub>2</sub> passivate the interface trap formed by oxygen vacancies. A very low p-type dopant concentration was obtained (~ 10 <sup>16</sup> cm<sup>-3</sup>) [39]. If wide band gap semiconductor like ZnO are doped with high dose of acceptor impurities, it can results in localization of carriers, thereby unable to modulate the conductivity of ZnO film. A polycrystalline ZnO doped with 10% Mg and 2% P were used to fabricate the enhancement type ZnO TFT [40]. Mg doping increases the band gap of semiconductor therefore increase the activation energy for the donor like defects, hence compensating n–type doping.

It was reported that ZnO thin films can be grown by various growth technique like RF sputtering [41], metal organic CVD [42], molecular beam epitaxy (MBE) [43], and pulsed laser deposition [44]. The various methods for fabricating ZnO TFTs and reported electrical characteristics are summarized in Table 2.2. From the list of parameters mentioned in the table, mobility and on-to-off ratio is hugely impacted by film quality and hence fabrication technology and its controlling parameters. However, the threshold voltage is mainly influenced by the dielectric constant and thickness of gate dielectric. RF sputtering is the mostly used fabrication technology for ZnO TFT due to its room temperature processing as it enables compatibility with wide variety of substrate. The only disadvantage in this process is use of high vacuum equipment.

**Table 2.2** Performance characteristics of ZnO based TFTs with various fabrication techniques

| Deposition | References  | Max.       | Mobility             | on-to-off ratio          | Threshold |

|------------|-------------|------------|----------------------|--------------------------|-----------|

| method     |             | Processing | $(cm^2V^{-1}s^{-1})$ | $(I_{on} / I_{o\!f\!f})$ | Voltage   |

|            | temperature |            |                      | (V)                      |           |

|            |             | (°C)       |                      |                          |           |

| RF         | [45], [46]  | R.T.       | 16.3 - 20            | $6.4 \times 10^4 -$      | 2.8 - 21  |

| sputtering |             |            |                      | $2 \times 10^5$          |           |

| PLD        | [40], [47]  | 500 - 600  | 2.3-5.32             | $10^4 - 1.5 \times 10^8$ | 1.2 - 3   |

| Sol- gel   | [23]        | 700        | 0.2                  | $10^{7}$                 | 10 - 20   |

| ALD        | [48]        | 150        | 6.7                  | $9.5 \times 10^7$        | 4.7       |

| Spray      | [49]        | 400        | 54                   | $10^{7}$                 |           |

| pyrolysis  |             |            |                      |                          |           |

### 2.2.2 Gate Dielectric

The performance and stability of ZnO TFT hugely depends upon the deposited gate dielectric. ZnO based TFT suffers from high threshold voltage requirement. However, high— $\kappa$  gate dielectric can solve this problem easily. To achieve effective coupling between gate electrode and semiconductor surface, one needs either high— $\kappa$  dielectric or needs thin gate dielectric layer. However, a thin dielectric layer can lead to considerable amount of gate leakage, hence the use of high— $\kappa$  dielectric is the only choice after a certain limit of dielectric layer thickness. Moreover, most of the display applications need high current driving capacity of driver TFT to drive the OLED pixel. Hence, one needs higher oxide capacitance ( $C_{ox}$ ), as current is directly proportional to  $C_{ox}$  and this can be achieved effectively by high— $\kappa$  dielectric. Most of the high— $\kappa$  dielectrics faces mainly two issues: first, high— $\kappa$  dielectric usually have lower band gap which leads to low breakdown voltage and second, they exhibit polycrystalline structure and a rough surface which results in less reliability and degraded interface quality. In literature ZnO interface is studied with various high— $\kappa$  dielectrics such as: HfO<sub>2</sub>, ZrO<sub>2</sub>, La<sub>2</sub>O<sub>3</sub>, Y<sub>2</sub>O<sub>3</sub> and BaTiO<sub>3</sub>

[50]–[53]. All these dielectrics have their own merits and demerits over others when used in ZnO TFTs, e.g. BaTiO<sub>3</sub> has a very high value of permittivity ( $\kappa$  = 2000) but has a very poor value of conduction band offset (– 0.45 eV). On the other hand, Al<sub>2</sub>O<sub>3</sub> has very low value of permittivity ( $\kappa$  = 9) but has a very good value of conduction band offset to ZnO (3.3 eV). Other criteria, which are very critical while selecting gate dielectric, are bandgap of dielectric material and its thermodynamic stability.

# 2.3 Transport Model of ZnO TFT

The adequate knowledge of transport mechanism through ZnO semiconductor is essentially required to analyze the electrical behavior of ZnO TFT. In ZnO polycrystalline channel, one needs to understand the current conduction mechanism through grain and grain boundaries. The two most popular models that explain the transport mechanism are: *Hossain's model* and *Multiple Trap and Release model* (MTR model). These models are presented in next subsections.

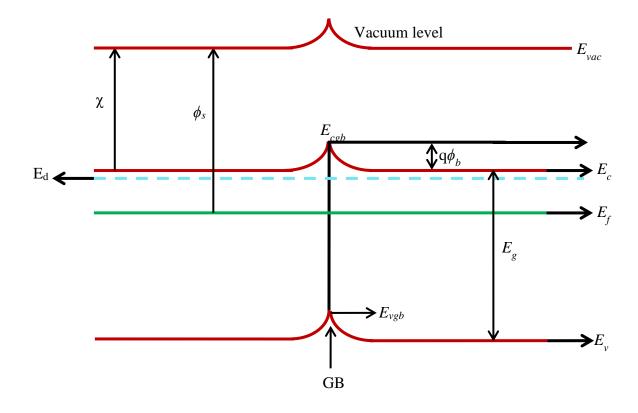

### 2.3.1 Hossain Model

Hossain *et al.* [36], proposed model for current conduction in ZnO TFTs by assuming the defects in crystallite and the ZnO gate dielectric are localized in grain boundaries (GBs), with a peak density at the mid gap. The value of characteristic decay energy of Gaussian distribution constant  $E_1$  and  $E_2$  of the defects in the GB are assumed material constant [36]. The polycrystalline thin film of ZnO is defined by equally spaced GBs parallel to ZnO film thickness and perpendicular to direction of carriers. The GB is modeled as a thin layer having acceptor and donor type states with Gaussian distribution as:

$$N_{ga}(E) = N_{ta} \exp\{-[(E_{1a} - E)/E_{2a}]^2\}$$

...(2.1)

$$N_{gd}(E) = N_{td} \exp\{-[(E - E_{1d})/E_{2d}]^2\}$$

...(2.2)

where a, d, g stands for acceptor like states, donor like states and Gaussian distribution. E and  $N_g(E)$  are the trap energy inside the band gap and corresponding

density of defect states respectively.  $N_t$  is the total density of trap states. According to this model, the Poisson's equations, to define the potential profile across the ZnO Channel and in GBs can be written as:

$$\frac{\partial^2 V}{\partial x^2} = -\frac{q(n - p - N_d^+)}{\varepsilon_{Z_{PQ}}}$$

for crystallite region...(2.3)

$$\frac{\partial^2 V}{\partial x^2} = -\frac{q(n - p - N_d^+)}{\varepsilon_{ZnO}} + \frac{q(n_a - n_d)}{\varepsilon_{ZnO}} \qquad \text{for GB region...(2.4)}$$

where n, p, are electron and hole density respectively,  $N_d$ <sup>+</sup> is ionized shallow donor density and the  $(n_a - n_d)$  are the net negative charge in GB. These charges are responsible for depletion of neighboring electrons from the GB. The resulting barrier of height  $\phi_b$  (Fig. 2.4) is the main obstacle for the carriers to transport through ZnO channel.

Fig. 2.4 Energy band diagram of ZnO channel in the presence of grain boundary

Mainly, two different transport mechanisms are utilized for the defect free grain region and GB. Drift and diffusion mechanism are responsible for the current conduction through grain while thermionic emission is utilized for current conduction over grain boundaries. If applied field across the channel is  $\stackrel{\rightarrow}{E}$  then electron current density  $\stackrel{\rightarrow}{J}$  equation for the defect free region can be written as:

$$\vec{J} = qn\mu\vec{E} + qD\nabla n \qquad ...(2.5)$$

where q, n,  $\mu$ , D, and  $\nabla n$  are the electron charge, electron concentration, mobility, diffusion coefficient and electron concentration gradient respectively. Electron current density in the GB of barrier of height  $\phi_b$  due to thermionic process can be written as [36]:

$$\vec{J}_{gb} = A^* T^2 \frac{n}{Nc} \exp\left(-\frac{q\phi_b}{k_B T}\right) \qquad \dots (2.6)$$

where  $N_c$  is the density of states for electron in conduction band,  $A^*$  is the electron Richardson constant, T is the absolute temperature,  $k_B$  is Boltzmann's constant and n is electron density which is given as:  $n = N_c \exp[-(E_c - E_f)/k_BT]$  where  $E_f$  is equilibrium Fermi level and  $E_c$  is the energy of conduction band. This model is used to calculate the potential profile for single grain boundary and multiple grain boundaries for ZnO TFT. However, this model has several limitations such as, it considers current through grain boundary only due to thermionic process, and ignore the impact of drain to source voltage on barrier height, which can surpass the barrier for certain  $V_{DS}$  and the mechanism of carrier transport will be governed by drift and diffusion.

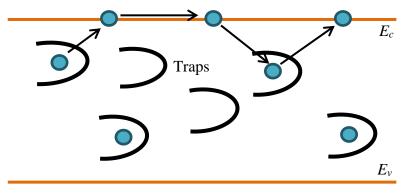

# 2.3.2 Multiple- Trapping and Release (MTR) Model

Torricelli *et al.* [54], proposed the multiple-trapping-and-release (MTR)-transport model to describe the transport mechanism in ZnO TFTs. At low disorder levels, the localized states are mainly at the band edges and as the disorder increases the localized states move further into bands. This physical scenario is described conventionally by density of states (DOS). The MTR model formulates density of states for acceptor like states with respect to conduction band edge ( $E_c$ ) using double exponential DOS given by

g(E) as: