## Towards Realizing Low Quantum Cost Reversible Logic Circuits

#### THESIS

Submitted in partial fulfillment

of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

by

Sai Phaneendra P

ID No. 2009PH230009H

Under the Supervision of

Dr. M. B. Srinivas

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

### CERTIFICATE

This is to certify that the thesis entitled <u>"Towards Realizing Low Quantum Cost</u> <u>Reversible Logic Circuits"</u> and submitted by <u>Sai Phaneendra P</u> ID No <u>2009PH230009H</u> for award of Ph.D. of the Institute embodies original work done by him under my supervision.

Signature of the Supervisor Dr. M. B. SRINIVAS Professor BITS-Pilani, Hyderabad Campus

Date:

## Acknowledgments

First and foremost, I would like to express my sincere gratitude to my supervisor Prof. M. B. Srinivas for his constant support and valuable guidance through out my work. I would also like to thank my Doctoral Advisory Committee members, Prof. BVVSN Prabhakar Rao, Dr. Sumit Kumar Chatterjee and Prof. Y Yoganandam for their time and their constructive comments and suggestions.

I take this opportunity to express my gratitude for Council of Scientific and Industrial Research (CSIR) - India and BITS-Pilani, Hyderabad Campus, India for providing financial assistance and infrastructure support during my thesis work.

I appreciate the help I received from Chetan Kumar V, Goutham M and Avinash S Vaidya during different stages of my work.

Furthermost, I would like to thank all members of Department of Electrical Engineering at BITS-Pilani, Hyderabad Campus, that have supported me by their suggestions and discussions. I would also like to thank members of Academic Research Division, Academic Registration & Counseling Division and Student Welfare Division at BITS-Pilani, Hyderabad Campus for their support during my thesis work.

Finally, I am grateful to my family members, especially my parents, Sridhar and Padmaja, and my wife, Keerthi, for their patience, encouragement and inspiration, without which this thesis would not have been possible.

### Abstract

Research on reversible logic gained momentum in the past decade owing to its applications in quantum computing and low power circuit implementation. Reversible circuits realized by the existing synthesis techniques are often sub-optimal and optimization techniques are applied on them to reduce the 'cost', a metric used to compare reversible circuits. While several optimization techniques are present in the literature, finding optimal or near-optimal reversible circuit is still an open-problem.

In this thesis, a set of optimization techniques is proposed that can be applied on a pair of gates to reduce the cost of a reversible circuit. Initially, a decomposition technique is presented that decomposes a pair of gates into a set of smaller gates without changing the functionality. This technique is then used in conjunction with an Exclusive-OR Sum-of-Product (ESOP) based reversible circuit synthesis algorithm to check its efficiency. It is known that the decomposition technique does not always result in cost reduction for a given gate pair. This leads us to examine the condition that results in reduction and it has been found that the effectiveness of this technique is proportionate to the number of common control lines between the gate pair. In order to increase the number of common control lines, a transformation approach is presented.

Lastly, a representation is proposed to classify a pair of gates according to their control line characteristics. This classification helps in identifying the gate pairs that can be optimized as opposed to those that can not be. Based on this classification, a methodology is presented to reduce the cost of a given gate pair. In order to apply the proposed techniques on reversible circuits, these techniques are integrated into 'greedy' optimization algorithms. A set of benchmark circuits is applied on these algorithms and are compared with existing benchmark circuits. Results indicate that the proposed techniques lead to significant improvement in the cost of reversible circuits.

# Contents

| A             | cknov | vledgements                              | iii |

|---------------|-------|------------------------------------------|-----|

| A             | bstra | et                                       | iv  |

| C             | onter | ts                                       | vi  |

| Li            | st of | Figures                                  | ix  |

| $\mathbf{Li}$ | st of | Tables                                   | cii |

| Li            | st of | Abbreviations x                          | iii |

| 1             | Intr  | oduction                                 | 1   |

|               | 1.1   | Contributions of the Thesis              | 4   |

|               | 1.2   | Organization of the Thesis               | 5   |

| <b>2</b>      | Pre   | iminaries                                | 7   |

|               | 2.1   | Introduction                             | 7   |

|               | 2.2   | Reversible Functions                     | 7   |

|               | 2.3   | Reversible Gates, Libraries and Circuits | 11  |

|               |       | 2.3.1 Reversible Gate Libraries          | 12  |

|               |       | 2.3.2 Reversible Circuit                 | 13  |

|   | 2.4  | Quantum Gates and Circuits                       |                                                                   |    |  |

|---|------|--------------------------------------------------|-------------------------------------------------------------------|----|--|

|   | 2.5  | Cost Metrics for Reversible and Quantum Circuits |                                                                   |    |  |

|   |      | 2.5.1                                            | Number of Gates                                                   | 20 |  |

|   |      | 2.5.2                                            | Quantum Cost                                                      | 21 |  |

|   |      | 2.5.3                                            | Number of Lines                                                   | 21 |  |

|   | 2.6  | Summ                                             | ary                                                               | 22 |  |

| 3 | Cuł  |                                                  | omposition Technique for Optimizing Reversible Logic Cir          | _  |  |

| U | cuit |                                                  | omposition reeninque for optimizing reversible Logie en           | 23 |  |

|   | 3.1  |                                                  | uction                                                            | 23 |  |

|   |      |                                                  |                                                                   |    |  |

|   | 3.2  | Backg                                            | round                                                             | 24 |  |

|   |      | 3.2.1                                            | Decomposition of an MCT/MPMCT gate                                | 24 |  |

|   |      | 3.2.2                                            | Exclusive-Or Sum-of-Products (ESOP) based Reversible Circuit      |    |  |

|   |      |                                                  | Synthesis                                                         | 25 |  |

|   |      |                                                  | 3.2.2.1 Exclusive-Or Sum-of-Products (ESOP)                       | 25 |  |

|   |      |                                                  | 3.2.2.2 ESOP based Reversible Synthesis techniques                | 26 |  |

|   | 3.3  | Cube                                             | Decomposition Technique                                           | 28 |  |

|   |      | 3.3.1                                            | General Idea                                                      | 28 |  |

|   |      | 3.3.2                                            | Generation of Primary and Secondary gates for a Cube Pair $\ .$ . | 30 |  |

|   |      |                                                  | 3.3.2.1 Case 1: $T_a \cap T_b \neq \phi$                          | 32 |  |

|   |      |                                                  | 3.3.2.2 Case 2: $T_a \cap T_b = \phi$                             | 33 |  |

|   |      |                                                  | 3.3.2.3 Case $3:pg_a = G(C_b)$ or $sg_a = G(C_b)$                 | 35 |  |

|   |      | 3.3.3                                            | Algorithm for Cube Decomposition                                  | 36 |  |

|   | 3.4  | Simula                                           | ation Results and Comparisons                                     | 40 |  |

|   | 3.5  | Summary                                          |                                                                   |    |  |

| 4                      | Complementary Control Line Transformation for Optimizing Reversible |                                     |                                                                                                   |      |  |  |  |  |

|------------------------|---------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------|------|--|--|--|--|

|                        | $\operatorname{Log}$                                                | ic Circu                            | its                                                                                               | 46   |  |  |  |  |

|                        | 4.1                                                                 | Introduc                            | ction                                                                                             | 46   |  |  |  |  |

|                        | 4.2                                                                 | ion                                 | 47                                                                                                |      |  |  |  |  |

|                        | 4.3                                                                 | mentary Control Line Transformation | 51                                                                                                |      |  |  |  |  |

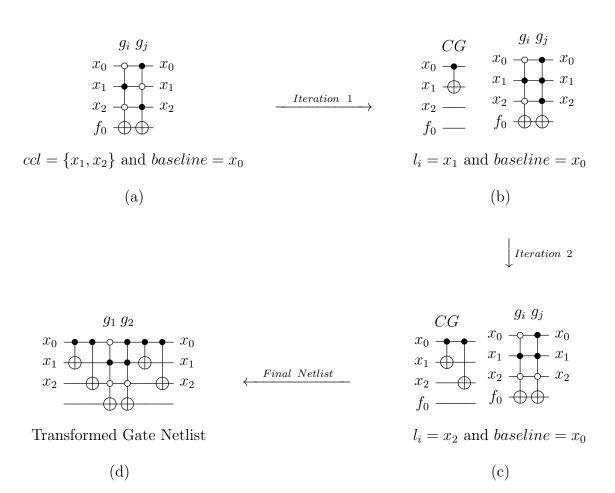

|                        | ansformation Algorithm                                              |                                     |                                                                                                   |      |  |  |  |  |

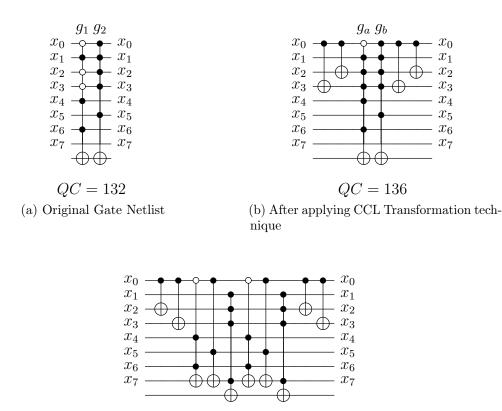

|                        | 4.5                                                                 | Applicat                            | tion of CCL Transformation Algorithm                                                              | 57   |  |  |  |  |

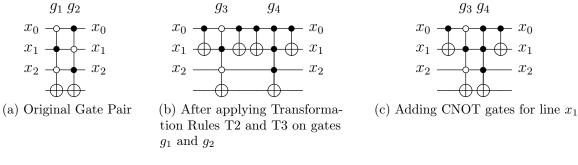

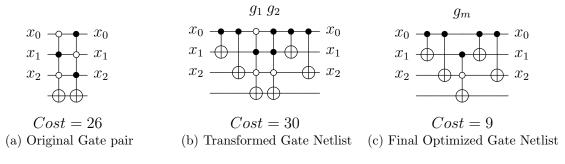

|                        |                                                                     | 4.5.1 (                             | CCL Transformation Algorithm and Decomposition Rule $\ . \ .$                                     | 57   |  |  |  |  |

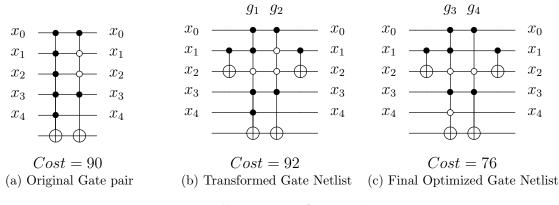

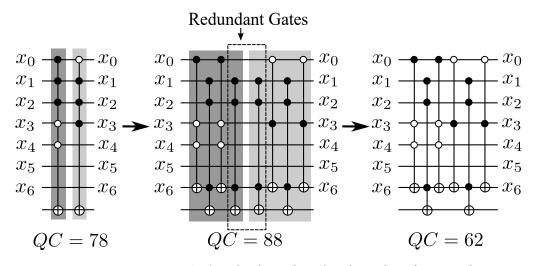

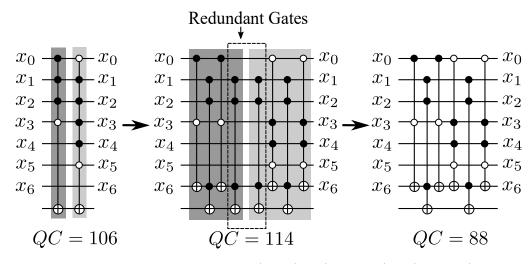

|                        |                                                                     | 4.5.2 (                             | CCL Transformation Algorithm and Rule Based Optimization                                          | . 57 |  |  |  |  |

|                        |                                                                     | 4.5.3 (                             | Greedy Optimization                                                                               | 60   |  |  |  |  |

| 4.6 Simulation Results |                                                                     |                                     |                                                                                                   |      |  |  |  |  |

|                        | 4.7 Summary                                                         |                                     |                                                                                                   |      |  |  |  |  |

| 5                      | Cla                                                                 | ssificatio                          | on of a Pair of Reversible Gates                                                                  | 71   |  |  |  |  |

|                        | 5.1                                                                 | Introduc                            | ction                                                                                             |      |  |  |  |  |

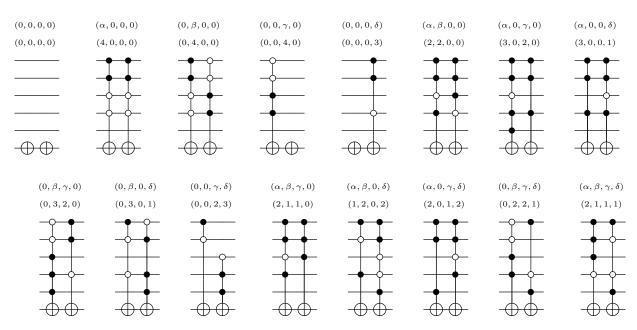

|                        | 5.2                                                                 | Quadruj                             | ple Representation to Classify a Gate Pair                                                        |      |  |  |  |  |

|                        | 5.3                                                                 | Optimiz                             | vation Techniques for different $QR$ classifications                                              | 75   |  |  |  |  |

|                        |                                                                     | 5.3.1 (                             | Optimization Technique for $QR(g_i, g_j) = (\alpha, \beta, \gamma, \delta)$ when $\alpha > \beta$ | 0 75 |  |  |  |  |

|                        |                                                                     | 5.3.2 (                             | Optimization Technique for $QR(g_i, g_j) = (0, \beta, \gamma, \delta)$                            |      |  |  |  |  |

|                        |                                                                     | 5.3.3 (                             | Optimization Techniques for Specific QR Classifications                                           | 80   |  |  |  |  |

|                        |                                                                     | E                                   | 5.3.3.1 For $QR(g_i, g_j) = (\alpha, \beta, 0, 0)$ and $(0, \beta, 0, 0)$                         | 80   |  |  |  |  |

|                        |                                                                     | 1                                   | 5.3.3.2 For $QR(g_i, g_j) = (\alpha, \beta, 1, 0)$ and $(\alpha, \beta, 0, 1)$                    |      |  |  |  |  |

|                        |                                                                     | л<br>С                              | 5.3.3.3 For $QR(g_i, g_j) = (\alpha, \beta, 1, 1)$                                                | 83   |  |  |  |  |

|                        | 5.4                                                                 | Post-Syr                            | nthesis Optimization Algorithm using QR Classification $\ . \ .$                                  | 88   |  |  |  |  |

|                        | 5.5 Simulation Results and Comparison                               |                                     |                                                                                                   |      |  |  |  |  |

|   | 5.6 | Summary    |           |      | <br> | <br> | <br> | 95 |

|---|-----|------------|-----------|------|------|------|------|----|

| 6 | Con | clusions a | nd Future | Work |      |      |      | 97 |

# List of Figures

| 1.1  | Design Flow for Reversible Logic Synthesis [17]                           | 3  |

|------|---------------------------------------------------------------------------|----|

| 2.1  | Negation Function $(\neg)$                                                | 8  |

| 2.2  | OR function $(\vee)$                                                      | 8  |

| 2.3  | Half Adder Function                                                       | 8  |

| 2.4  | Reversible OR function after Embedding Process                            | 10 |

| 2.5  | Reversible Half Adder after embedding process                             | 11 |

| 2.6  | Reversible Half Adder Function with a different embedding process         | 11 |

| 2.7  | Reversible Gates                                                          | 13 |

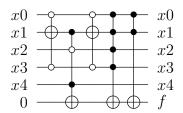

| 2.8  | Example of Reversible Circuit with cascade of gates                       | 14 |

| 2.9  | Reversible Half Adder Circuit                                             | 14 |

| 2.10 | Single-qubit Quantum Gates                                                | 17 |

| 2.11 | Two-qubit quantum gates                                                   | 18 |

| 2.12 | Mapping of Toffoli gate for different combinations of control lines using |    |

|      | NCV library                                                               | 19 |

| 2.13 | Mapping of Reversible Half Adder Circuit to Quantum Circuit $\ . \ . \ .$ | 19 |

| 3.1  | Decomposition of MCT gate into network of four smaller gates              | 24 |

| 3.2  | (a) Cube list and (b) representation of cubes for functions $f_1 = x_0 \overline{x_1} \oplus$                       |    |

|------|---------------------------------------------------------------------------------------------------------------------|----|

|      | $x_0x_1x_2$ and $f_2 = \overline{x_0} \oplus x_0x_1x_2 \dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 26 |

| 3.3  | ESOP based Synthesis Technique presented in $[31]$                                                                  | 27 |

| 3.4  | (a) Initial Circuit $(QC=78)$ (b) Individual Gate decomposition $(QC=98)$                                           |    |

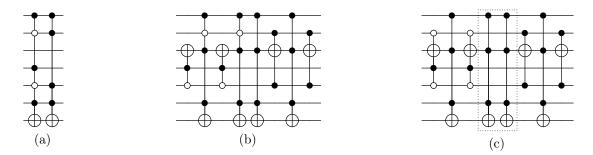

|      | (c) Pairwise decomposition $(QC=62)$                                                                                | 28 |

| 3.5  | Gate decomposition for a pair of cubes with the same empty line as                                                  |    |

|      | target line                                                                                                         | 33 |

| 3.6  | Gate decomposition for a cube pair with different empty lines as target                                             |    |

|      | lines                                                                                                               | 35 |

| 3.7  | Gate decomposition for a cube pair with $pg_a = G(C_b)$                                                             | 37 |

| 3.8  | Cube list                                                                                                           | 39 |

| 3.9  | Decomposed gate netlist for the cube pair $C_1$ and $C_4$                                                           | 39 |

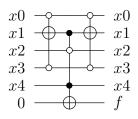

| 3.10 | Status of cube list and output gate netlist after iteration $1$                                                     | 39 |

| 3.11 | Decomposed gate netlist for the cube pair $C_2$ and $C_3$                                                           | 40 |

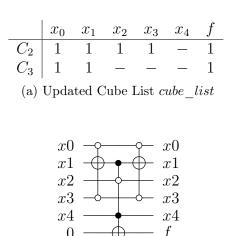

| 3.12 | Status of cube list and output gate netlist after iteration $2$                                                     | 40 |

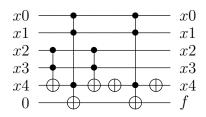

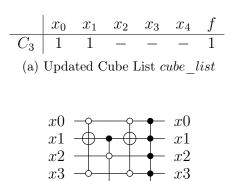

| 3.13 | Output gate netlist after Final Iteration                                                                           | 41 |

| 4.1  | Illustration of Decomposition Rule                                                                                  | 48 |

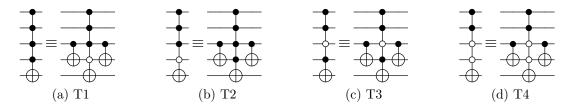

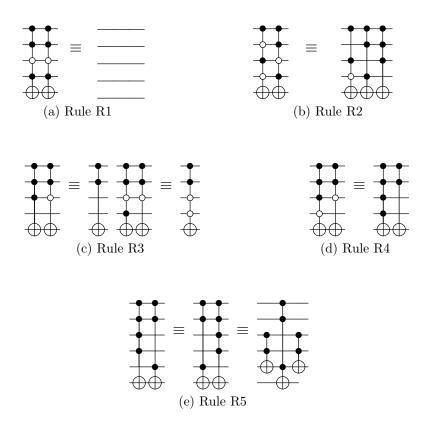

| 4.2  | Illustration of Transformation Rules                                                                                | 52 |

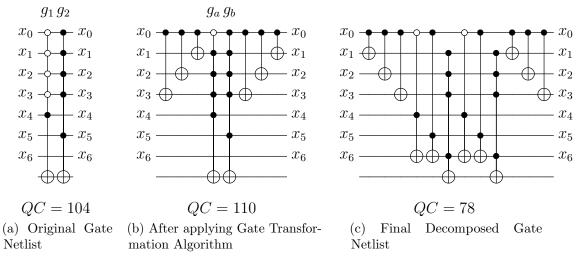

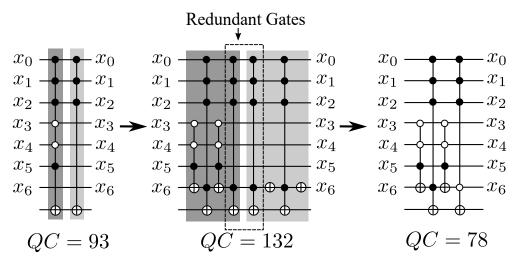

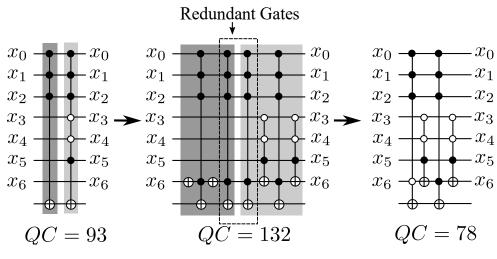

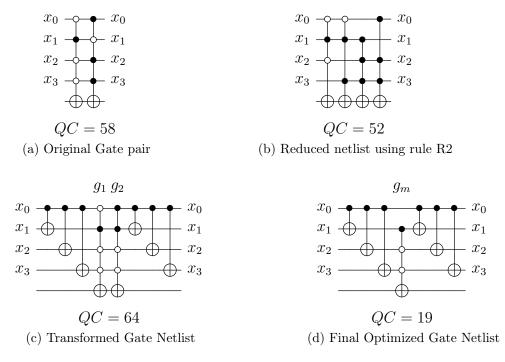

| 4.3  | Illustration of Example 4.2                                                                                         | 54 |

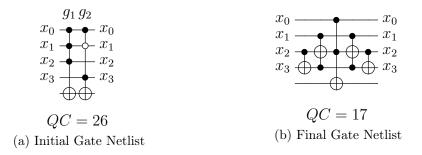

| 4.4  | Illustration of Gate Transformation Algorithm (a) Initial Gate Pair (b)                                             |    |

|      | After Iteration 1 (c) After Iteration 2 (d) Final Transformed Gate Netlist                                          | 56 |

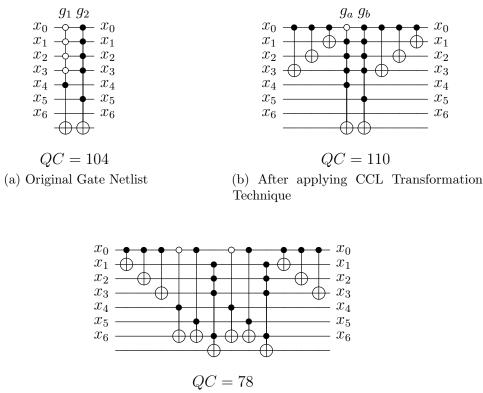

| 4.5  | Illustration of Example 4.4                                                                                         | 58 |

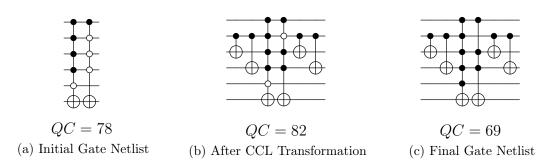

| 4.6  | Illustration of Example 4.5                                                                                         | 59 |

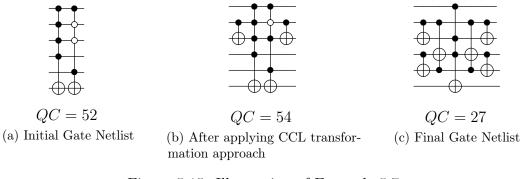

| 4.7  | Illustration of Example 4.6                                                                                         | 60 |

| 5.1  | Example for quadruple representation (QR) $\ldots \ldots \ldots \ldots \ldots$                      | 72 |

|------|-----------------------------------------------------------------------------------------------------|----|

| 5.2  | Examples for different QR classifications                                                           | 73 |

| 5.3  | Examples for Existing Optimization Rules                                                            | 74 |

| 5.4  | Example for $QR(g_i, g_j) = (\alpha, \beta, \gamma, \delta) = (2, 2, 1, 1) \dots \dots \dots \dots$ | 75 |

| 5.5  | Example for $QR(g_i, g_j) = (\alpha, \beta, \gamma, 0) = (2, 2, 1, 0) \dots \dots \dots \dots$      | 76 |

| 5.6  | Example for $QR(g_i, g_j) = (\alpha, \beta, 0, \delta) = (2, 2, 0, 2) \dots \dots \dots \dots$      | 76 |

| 5.7  | Example for $QR(g_i, g_j) = (\alpha, 0, \gamma, \delta) = (3, 0, 2, 1)$                             | 76 |

| 5.8  | Example for $QR(g_i, g_j) = (\alpha, 0, \gamma, 0) = (3, 0, 3, 0)$                                  | 77 |

| 5.9  | Example for $QR(g_i, g_j) = (\alpha, 0, 0, \delta) = (3, 0, 0, 3)$                                  | 77 |

| 5.10 | Illustration of Example 5.2                                                                         | 79 |

| 5.11 | Illustration of Example 5.3                                                                         | 81 |

| 5.12 | Illustration of Example 5.4                                                                         | 82 |

| 5.13 | Illustration of Example 5.5                                                                         | 83 |

| 5.14 | Illustration of Example 5.6                                                                         | 85 |

| 5.15 | Illustration of Example 5.7                                                                         | 86 |

# List of Tables

| 2.1 | Reversible Gate Libraries                                               | 13 |

|-----|-------------------------------------------------------------------------|----|

| 2.2 | Quantum Cost of an MCT gate                                             | 21 |

| 3.1 | Comparison with Existing ESOP Based Synthesis Methods $\ . \ . \ .$ .   | 42 |

| 4.1 | Comparison with Input Gate Netlist                                      | 63 |

| 4.2 | Comparison with Existing ESOP based Synthesis Methods $\ . \ . \ .$ .   | 66 |

| 5.1 | Quantum Cost reduction for different classifications after applying     |    |

|     | decomposition Rule                                                      | 78 |

| 5.2 | QR Transformation                                                       | 80 |

| 5.3 | Summary of Optimization Techniques for different $QR$ classifications . | 87 |

| 5.4 | Comparison with Existing Post-Synthesis Optimization Algorithms .       | 90 |

| 5.5 | Comparision with Exisiting ESOP Based Methods                           | 93 |

# List of Abbreviations

| BDD   | Binary Decision Diagram              |

|-------|--------------------------------------|

| CCL   | Complementary Control Line           |

| CNOT  | Controlled NOT                       |

| ECL   | Equal Control Line                   |

| ESOP  | Exclusive-or Sum-of-Product          |

| MCT   | Multi-Control Toffoli                |

| MPMCT | Multi-Polarity Multi-Control Toffoli |

| QC    | Quantum Cost                         |

| QR    | Quadruple Representation             |

| SOP   | Sum-of-Product                       |

| UCL   | Unequal Control Line                 |

## Chapter 1

## Introduction

Power dissipation is a significant problem in designing small and high performance complex integrated circuits. Recent advancements in integration of circuits and fabrication techniques have helped reduce the power consumption but some part of power, which is independent of underlying technology, is dissipated due to information loss. In 1961 Landauer [1] proved that, a loss of single bit of information in irreversible (or conventional) logic computation leads to dissipation of heat energy of kTln2 Joules, where Kand T are Boltzmann's constant and absolute temperature at which computation is performed, respectively. This principle has been experimentally validated recently [2] by measuring the amount of heat dissipated when a bit of information is erased. Further, in 1973, Bennett [3] showed that the dissipated energy is directly correlated to the number of information bits lost and if the computation can be made information-lossless then the energy dissipation can be reduced or theoretically eliminated. One way this can be achieved is by making computation reversible, i.e. a bijective mapping between inputs and outputs, resulting in no information loss.

Reversible computation thus, for one, is motivated by its implication to reduce the

power consumption. Further, it also has relevance to quantum computing [4] because unitary transformation in quantum computing was shown to be reversible [5]. Quantum algorithms are known to solve some hard problems in polynomial time like Shor's algorithm [6] for factoring and Grover's algorithm [7] for searching for which classical computing is known to take exponential time. In applications of these algorithms, currently a large part of the computation is performed using classical computing which can be described in terms of classical functions [5]. If these were to be implemented on a quantum computer, the classical logic functions need to be translated into reversible logic functions (since quantum transformations are reversible in nature) and implemented using reversible gates and circuits. Apart from the applications in low power design and quantum computing, reversible computing also has applications in optical [8–10], DNA computing [11,12], cryptography [13], program inversion [14] and coding devices [15,16].

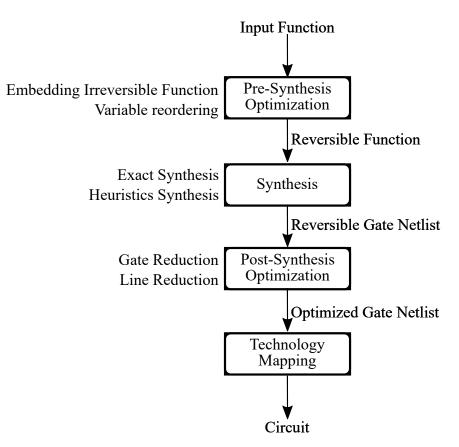

The bijective mapping of a reversible function does not allow for fan-out and feedback in the implementation of reversible logic circuits. These constraints limit the usage of existing conventional logic synthesis techniques to synthesize reversible logic functions. In order to implement these functions, new algorithms, techniques and design flows have been developed in the past decade [17, 18]. A general design flow for reversible logic function implementation is shown in figure 1.1.

Synthesis techniques can be broadly categorized in to exact and heuristic. Exact synthesis techniques [19–21] are based on exhaustive search or Boolean satisfiability which search for optimal solutions to generate minimum cost circuits but are applicable only on functions with small number of variables (not more than 6) [18]. For functions with a large number of variables, heuristic approaches like transformation based [22–25], cycle based [26–28], binary decision diagram (BDD) based [29,30], Exclusive-OR Sum-

Figure 1.1: Design Flow for Reversible Logic Synthesis [17]

of-Product (ESOP) based approaches [31–36] are used. In the transformation based approach [23] input specification is given in the form of a truth-table. The lines of the truth-table are traversed and gates are added until it is transformed to a identity function truth-table. In the cycle based approach [26], input specification is given in the form of a permutation. This permutation is decomposed into a set of cycles and each cycle is synthesized separately and cascaded to generate final gate netlist. In the BDD based approach [29], a BDD is constructed from input specification and each node is replaced with corresponding gate netlist and added to the circuit. In ESOP based approach [31] the product terms of ESOP are directly mapped using equivalent reversible gates.

Heuristic synthesis approaches usually generate circuits which are sub-optimal and post-synthesis optimization techniques [25, 37–40] are typically applied to reduce the cost of the circuit. Optimization technique presented in [40] reduces the cost of a reversible circuit with the help of additional lines. However, increase in the number of lines directly affects the complexity of its implementation [41]. Technique described in [25] uses template-based local optimization to reduce the cost of the circuit. However, this method involves a search for templates which becomes complex as the circuit size increases. Rule-based optimization algorithms have been presented in [37–39] where a group of gates is replaced with a lesser cost gate netlist using a set of rules. However, when a pair of gates is considered, existing optimization techniques address only a few combinations of gate pairs. In this thesis, we explores different optimization techniques to reduce the cost of a reversible circuit using gate pairs and quantify their performance with respect to the existing ones.

### 1.1 Contributions of the Thesis

Contributions of this thesis may be described as follows:

- Initially a technique is developed to decompose a pair of gates to a network of smaller gates without any change in the functionality. This technique generates and eliminates any redundant gates that appear at the time of decomposition resulting in a gate netlist with reduced cost compared with initial pair. A cube decomposition algorithm is presented which integrates the proposed technique with ESOP based approach to synthesize reversible circuits with reduced cost.

- The decomposition technique however does not always result in cost reduction for a given gate pair. This lead us to examine the nature of a given gate pair that results in reduction and is found that the effectiveness of the technique is

proportional to the number of common control lines between the gate pair. That is, larger the number of lines more effective the technique is. Thus, in order to increase the lines, a transformation approach named "Complementary Control Line Transformation" is proposed which transforms some of the unequal control lines to equal control lines with the help of extra gates. Further, we also found that this transformation enables application of some of the existing rules which cannot be applied on gates with more than one unequal control line.

• Finally, a framework based on quadruple representation, which classifies a pair of gates based on its control line characteristics, is proposed. This classification helps in identifying gate pairs that can be optimized as opposed to those that can not be. Further, this classification also helps in selecting appropriate techniques that can be applied on a gate pair to reduce the cost of its implementation. A 'greedy' optimization algorithm is presented that uses the classification and the proposed techniques to reduce the overall cost of the circuit.

### 1.2 Organization of the Thesis

Rest of the thesis is organized as follows:

Chapter 2 provides the necessary background required for the work described in this thesis. It describes reversible logic, reversible gates and their circuit implementation. A brief overview of quantum logic and quantum gates is presented. Finally, implementation of reversible gates and circuits using quantum gates and the cost metrics to evaluate them are discussed.

Chapter 3 presents a technique to decompose a pair of gates. Motivation for this approach and its application in ESOP based synthesis are discussed. This technique is

then used in conjunction with an ESOP based reversible circuit synthesis algorithm to verify its efficiency.

**Chapter 4** demonstrates the relation between the number of equal control lines in a given gate pair and the cost reduction achieved after applying the decomposition approach. Later, a transformation approach is described that increases the number of equal control lines in a given gate pair. Application of this transformation approach to different existing optimization techniques is then presented.

**Chapter 5** proposes a framework based on a representation to classify a pair of gates. Existing and proposed optimization techniques are then categorized according to this representation. Finally, an optimization algorithm is described which is applied to these techniques to reduce the cost of a given reversible circuit.

Chapter 6 concludes the thesis and presents directions for future research.

## Chapter 2

## Preliminaries

### 2.1 Introduction

This chapter provides a brief summary of reversible logic, reversible gates and circuits and necessary background required for the work reported in this thesis. The first part of this chapter discusses reversible functions and conversion of irreversible functions to reversible functions. The second part gives details of different reversible gates and their functionalities, gate libraries and circuits. The third part discusses quantum gates that can be used to implement reversible gates and circuits. Finally, different cost metrics to evaluate these gates and circuits are presented.

### 2.2 Reversible Functions

In classical computing, a Boolean function is defined as

**Definition 2.1** (Boolean Function). A Boolean function is a mapping  $f : \mathbb{B}^n \to \mathbb{B}$ where  $\mathbb{B} = \{0, 1\}$  denotes the *Boolean values* and  $n \in \mathbb{N}$ .

The behavior of a function is represented as a tabular form known as *truth table*.

The left side of this table lists the permutations of *inputs* and the right side provides the results of the function as *outputs* for each input combination. Following examples show different Boolean functions and their truth tables:

**Example 2.1.** Figure 2.1 shows the truth table of a negation function  $(\neg)$  which has one input (a) and one output (z).

| a | z |

|---|---|

| 0 | 1 |

| 1 | 0 |

Figure 2.1: Negation Function  $(\neg)$

**Example 2.2.** Figure 2.2 shows the truth table of an OR function  $(\vee)$  which has two inputs (a, b) and one output (z).

| a | b | z |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

Figure 2.2: OR function  $(\vee)$

A multi-output Boolean function with m outputs is a system of m Boolean functions  $f_i(x_1, x_2, ..., x_n)$  where  $1 \le i \le m$ . For example, figure 2.3 shows a multi-output function, *Half adder*, with two inputs (a, b) and two outputs (sum, carry).

| C | ı b  | sum | carry |

|---|------|-----|-------|

| ( | ) () | 0   | 0     |

| ( | ) 1  | 1   | 0     |

| 1 | L 0  | 1   | 0     |

| ] | l 1  | 0   | 1     |

Figure 2.3: Half Adder Function

In contrast to classical computing, reversible computing is limited to functions which can be operated in inverted fashion, i.e. inputs can be constructed from outputs. A reversible function is defined as: **Definition 2.2** (Reversible Function). An *m*-input *m*-output function  $f : \mathbb{B}^m \to \mathbb{B}^m$ where  $m \in \mathbb{N}$  is said to be *reversible* if it has one-to-one and onto mapping i.e., bijective mapping between inputs and outputs.

Since the mapping is bijective, reversible functions can be operated in forward and backward directions resulting in no information loss. If a function f is reversible then its number of inputs is same as the number of outputs. For example, negation function  $(\neg)$ shown in figure 2.1 is a reversible function whereas OR function  $(\lor)$  shown in figure 2.2 is not. Even though the half adder function shown in figure 2.3 has same number of inputs and outputs, the mapping between inputs and outputs is not bijective and thus not reversible. These irreversible functions can be transformed in to reversible function by adding additional inputs/outputs and assigning don't-care values such that the mapping between inputs and outputs is bijective. This process of transforming an irreversible function to reversible function is called *embedding of irreversible function* [42].

**Definition 2.3** (Ancillary Inputs). The additional inputs that are added to make a function reversible are termed as *ancillary inputs* or *ancillae inputs*. In general, these inputs are assigned with constant values and thus they are also known as *constant inputs*.

**Definition 2.4** (Garbage Outputs). The additional outputs that are added to make a function reversible are termed as *garbage outputs*.

According to Theorem 1 given in [43], the minimum number of garbage outputs required to make a function reversible is  $\lceil log_2(\mu) \rceil$ , where  $\mu$  is the maximum of number of times an output pattern is repeated in its truth table.

**Example 2.3.** Consider the OR function shown in figure 2.2. From the truth table, it can be seen that the output has three occurrences of '1'. Thus, the number of garbage

outputs that is required to make this function reversible is  $\lceil log_2(3) \rceil = 2$ . Since, the number of outputs and inputs should be equal, one ancillary input is required to make the function reversible. After adding these additional inputs and outputs and assigning values to the don't cares, the final truth table is shown in figure 2.4. The outputs  $go_1$ and  $go_2$  are the garbage outputs and the input  $ai_1$  is the ancillary input. Don't care values are assigned in such a way as to achieve bijective mapping between the inputs and outputs.

| $ai_1$ | a | b | z | $go_1$ | $go_2$ |

|--------|---|---|---|--------|--------|

| 0      | 0 | 0 | 0 | 0      | 0      |

| 0      | 0 | 1 | 1 | 0      | 1      |

| 0      | 1 | 0 | 1 | 1      | 0      |

| 0      | 1 | 1 | 1 | 1      | 1      |

| 1      | 0 | 0 | 1 | 0      | 0      |

| 1      | 0 | 1 | 0 | 0      | 1      |

| 1      | 1 | 0 | 0 | 1      | 0      |

| 1      | 1 | 1 | 0 | 1      | 1      |

Figure 2.4: Reversible OR function after Embedding Process

**Example 2.4.** Consider the half adder function shown in figure 2.3. The maximum number of occurrences of an output pattern is '2' for '10'. Thus at least one  $(\lceil log_2(2) \rceil = 1)$  garbage output and one ancillary input are required to make this function reversible. The reversible half adder after embedding the extra inputs and outputs is shown in figure 2.5 where  $go_1$  and  $ai_1$  are garbage output and ancillary input respectively.

The embedding of irreversible functions is not unique and there are several possibilities depending on the don't care assignments. For example figure 2.6 shows an alternative embedding of half adder function to make it reversible which is different from the embedding shown in figure 2.5. This process of embedding irreversible functions to reversible has been studied in the past and different approaches have been proposed in literature [42, 44–46].

| $ai_1$ | a | b | sum | carry | $go_1$ |

|--------|---|---|-----|-------|--------|

| 0      | 0 | 0 | 0   | 0     | 0      |

| 0      | 0 | 1 | 1   | 0     | 1      |

| 0      | 1 | 0 | 1   | 0     | 0      |

| 0      | 1 | 1 | 0   | 1     | 1      |

| 1      | 0 | 0 | 0   | 1     | 0      |

| 1      | 0 | 1 | 1   | 1     | 1      |

| 1      | 1 | 0 | 1   | 1     | 0      |

| 1      | 1 | 1 | 0   | 0     | 1      |

Figure 2.5: Reversible Half Adder after embedding process

| $ai_1$ | a | b | sum | carry | $go_1$ |

|--------|---|---|-----|-------|--------|

| 0      | 0 | 0 | 0   | 0     | 0      |

| 0      | 0 | 1 | 1   | 0     | 1      |

| 0      | 1 | 0 | 1   | 0     | 0      |

| 0      | 1 | 1 | 0   | 1     | 1      |

| 1      | 0 | 0 | 1   | 1     | 0      |

| 1      | 0 | 1 | 1   | 1     | 1      |

| 1      | 1 | 0 | 0   | 1     | 0      |

| 1      | 1 | 1 | 0   | 0     | 1      |

Figure 2.6: Reversible Half Adder Function with a different embedding process

#### 2.3 Reversible Gates, Libraries and Circuits

A reversible gate is defined as,

**Definition 2.5** (**Reversible Gate**). A gate is said to be *reversible* if it realizes reversible function i.e. bijection.

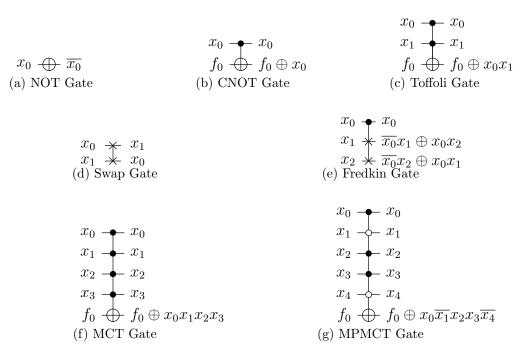

The variables of a reversible function are represented with circuit lines in the reversible gates. The commonly used reversible gates are NOT, CNOT, Toffoli [47] and Fredkin gates [48]. The characteristics and representations of these gates are discussed below:

**NOT Gate** A *NOT gate* has one input and one output and inverts the input.

**CNOT Gate** A *Controlled-NOT (CNOT) gate* or *Feynman gate* has a control line and a target line where the target line value gets inverted if the control line is equal to '1'.

- **Toffoli Gate** A Toffoli gate has two control lines and one target line where the target line value gets inverted when both the control lines are set to '1'.

- Swap Gate A Swap gate has two inputs, two outputs and swaps the values on the two lines.

- **Fredkin Gate** A Fredkin gate is a Controlled-Swap gate with one control and two target lines. When the control line is set to '1', the target lines are swapped.

- **MCT Gate** A *n*-bit multi-controlled Toffoli (MCT) gate is a generalized Toffoli gate with n - 1 control lines and one target line.

- **MPMCT Gate** A multi-polarity multi-control Toffoli (MPMCT) gate is similar to MCT gate but control lines can be either positive or negative. The *negative* control line in a gate is active when it is set to '0'.

The representation of these gates is shown in figure 2.7. The positive control line is indicated with  $\bullet$ , negative control line with  $\circ$  and target line with  $\oplus$ . The MCT and MPMCT gates are represented as MCT(C;t) and MPMCT(C;t) respectively, where C is the set of control lines and t is the target line.

#### 2.3.1 Reversible Gate Libraries

A gate library is a group of basic gates by which any function can be implemented. Similarly, a reversible gate library consists of gates that can realize any reversible function. There exist different reversible gate libraries as shown in Table 2.1:

Figure 2.7: Reversible Gates

| Table $2.1$ : | Reversible | Gate | Libraries |

|---------------|------------|------|-----------|

|---------------|------------|------|-----------|

| Library | Included Gate(s)                           |

|---------|--------------------------------------------|

| NCT     | NOT, CNOT and Toffoli Gates                |

| NCTS    | NOT, CNOT, Toffoli and Swap Gates          |

| MCT     | Multi-Control Toffoli Gates                |

| MPMCT   | Multi-Polarity Multi-Control Toffoli gates |

#### 2.3.2 Reversible Circuit

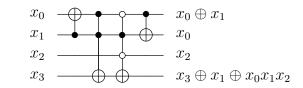

The bijective mapping in reversible functions imposes the constraints like no fan-out and no feedback in the implementation. Thus, reversible functions are realized by cascading reversible gates to form a *reversible circuit*. For example, a reversible circuit with cascade of four reversible gates is shown in figure 2.8. The representation of this circuit with MPMCT gates is given as follows:

$$MPMCT(\{x_1\};x_0) \circ MPMCT(\{x_0,x_1\};x_3) \circ MPMCT(\{\overline{x_0},x_1,\overline{x_2}\};x_3) \circ MPMCT(\{x_0\};x_1) \circ MPMCT(\{x_0\};x_1) \circ MPMCT(\{x_0,x_1\};x_2) \circ$$

where  $\circ$  denotes cascade of gates/circuits.

Figure 2.8: Example of Reversible Circuit with cascade of gates

Similar to reversible gates, reversible circuits also have same number of inputs and outputs and perform bijection. Also, reversible circuits can be operated in backward direction to realize inverse functions.

**Example 2.5.** Consider the reversible half adder function given in Example 2.4. The reversible circuit to implement this function is shown in figure 2.9. The *carry* is generated using a Toffoli gate with the help of an ancilla line  $(ai_1)$  and the *sum* is generated using a CNOT gate. This circuit can be operated in backward direction to get input *a* from *Sum* and *b*.

$$a \xrightarrow{\bullet} Sum \\ b \xrightarrow{\bullet} b \\ ai_1 \xrightarrow{\bullet} Carry$$

Figure 2.9: Reversible Half Adder Circuit

Now, definitions used in this thesis for different lines of a reversible circuit are given below:

- **Control Connection** The *control connection* defines the state of connection i.e., positive or negative, of a given control line in a gate.

- **Equal Control Line (ECL)** A line having same control connection and same value for a set of gates is termed as *equal control line (ECL)*.

**Complementary Control Line (CCL)** A line having positive control connection on one gate and negative control connection on another gate is termed as *complementary control line (CCL)* for the gate pair.

**Unequal Control Line (UCL)** A line having different control connections for a pair of gates is termed as *unequal control line (UCL)*.

**Unused Line** A line which is neither a control line nor a target line of a gate is termed as *unused line* for that gate.

In order to the implement the classical Boolean functions in quantum algorithms, the functions are first realized using reversible circuits and the gates in the circuit are mapped to equivalent quantum circuits. In the next section different quantum gates and circuits are explained along with the mapping of reversible circuits to quantum circuit.

### 2.4 Quantum Gates and Circuits

In quantum computing, information is encoded into quantum states and is represented using quantum bit represented as qubit. In contrast to Boolean logic where classical bits take values of Boolean's 0 or 1, qubits not only take values of Boolean's 0 or 1 but also take superposition of these values. A qubit  $|\psi\rangle$  can be described as [5]:

$$|\psi\rangle = \alpha_0 |0\rangle + \alpha_1 |1\rangle \tag{2.1}$$

where  $|0\rangle$  and  $|1\rangle$  are column vectors corresponding to  $\begin{pmatrix} 0\\1 \end{pmatrix}$  and  $\begin{pmatrix} 1\\0 \end{pmatrix}$  respectively. The coefficients  $\alpha_0$  and  $\alpha_1$  are complex values, with  $|\alpha_0|^2 + |\alpha_1|^2 = 1$ , which

represents the amplitudes of  $|0\rangle$  and  $|1\rangle$  respectively. When a qubit is measured, depending on the current state, 0 and 1 are returned with a probability of  $|\alpha_0|^2$  and  $|\alpha_1|^2$  respectively.

**Definition 2.6** (Unitary Matrix). If the conjugate transpose  $(U^{\dagger})$  of a matrix (U) is also its inverse then the matrix is termed as Unitary Matrix, i.e.  $U^{\dagger}U = UU^{\dagger} = I$  where I is identity matrix.

For example, consider a matrix  $U = \begin{bmatrix} i & 0 \\ 0 & 1 \end{bmatrix}$ . The conjugate transpose of this matrix is  $U^{\dagger} = \begin{bmatrix} -i & 0 \\ 0 & 1 \end{bmatrix}$  and  $U^{\dagger}U = UU^{\dagger} = \begin{bmatrix} 1 & 0 \\ 0 & 1 \end{bmatrix}$ . Thus, the matrix U is a unitary matrix.

A quantum gate is represented as  $2^n \times 2^n$  unitary matrix operated on n qubits. For example, a single-qubit quantum gate where n = 1, the quantum gates represent a  $2 \times 2$ unitary matrix. The commonly used single-qubit gates are discussed below:

**Pauli-X Gate** The Pauli-X gate transforms a qubit  $|\psi\rangle = \alpha_0 |0\rangle + \alpha_1 |1\rangle$  to  $|\psi\rangle = \alpha_1 |0\rangle + \alpha_0 |1\rangle$  i.e. interchanging the amplitudes of  $|0\rangle$  and  $|1\rangle$  and the transformation matrix is given in Eq. (2.2). Thus, this gate is also referred to as *NOT gate*.

$$X = \begin{bmatrix} 0 & 1 \\ 1 & 0 \end{bmatrix}$$

(2.2)

V Gate The square-root of NOT (Pauli-X) gate is referred to as V gate i.e.  $V^2 = X$ . The transformation matrix of this gate is given in Eq. (2.3). The cascade of two V gates results in a NOT gate.

$$V = \frac{1+i}{2} \begin{bmatrix} 1 & -i \\ -i & 1 \end{bmatrix}$$

(2.3)

$V^{\dagger}$  Gate The  $V^{+}$  gate is a complex conjugate of V gate i.e.  $V^{+}V = I$  where I is a identity gate and the transformation matrix is given in Eq. (2.4). Similar to V gate, two consecutive  $V^{+}$  gates also result in a NOT gate.

$$V^{+} = \frac{1-i}{2} \begin{bmatrix} 1 & i \\ i & 1 \end{bmatrix}$$

(2.4)

The representation of NOT (Pauli-X), V and  $V^+$  gates are shown in figure 2.10.

(a) NOT Gate (b) V Gate (c)

$$V^+$$

Gate

Figure 2.10: Single-qubit Quantum Gates

Similar to a single-qubit quantum gate, a two-qubit quantum gate represents a  $4 \times 4$  unitary matrix. A general two-qubit gate is a *controlled-U* gate which consists of control and target qubits. The unitary matrix U is applied on the target qubit only if the control qubit is  $|1\rangle$  else it is unchanged. The transformation matrix is given in Eq. (2.5), where  $U_{00}, U_{01}, U_{10}, U_{11}$  are elements corresponding to matrix U. The commonly used two-qubit quantum gates are explained as follows:

$$Controlled - U = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & U_{00} & U_{01} \\ 0 & 0 & U_{10} & U_{11} \end{bmatrix}$$

(2.5)

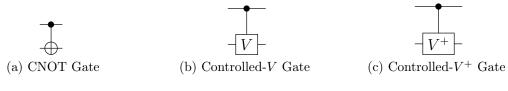

The Controlled-NOT (CNOT), Controlled-V and controlled- $V^+$  gates are controlled-U gates where U = X, U = V and  $U = V^+$  respectively. The transformation matrices

of these gates are given in Eqs. (2.6), (2.7) and (2.8) and their representation is shown in figure 2.11.

$$CNOT = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix}$$

(2.6)

$$Controlled - V = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & \frac{1+i}{2} & \frac{1-i}{2} \\ 0 & 0 & \frac{1-i}{2} & \frac{1+i}{2} \end{bmatrix}$$

(2.7)

$$Controlled - V^{+} = \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & \frac{1-i}{2} & \frac{1+i}{2} \\ 0 & 0 & \frac{1-i}{2} & \frac{1+i}{2} \\ 0 & 0 & \frac{1+i}{2} & \frac{1-i}{2} \end{bmatrix}$$

(2.8)

Figure 2.11: Two-qubit quantum gates

Quantum circuits are implemented by cascading quantum gates on a set of qubits. The widely used quantum library in the literature to map reversible circuits to quantum circuits is NCV library [49]. This library consists of NOT, CNOT, Controlled-V and Controlled- $V^+$  gates. The quantum NOT and CNOT gates are same as reversible NOT and CNOT gates when applied on Boolean logic. The mapping of Toffoli gate to quantum circuit, for different combinations of control lines, using NCV gate library is shown in figure 2.12.

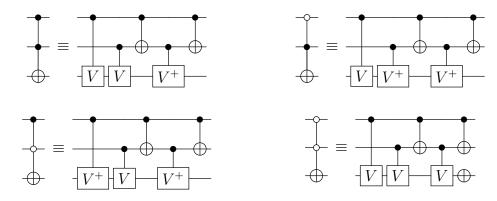

Figure 2.12: Mapping of Toffoli gate for different combinations of control lines using NCV library

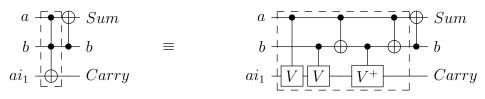

**Example 2.6.** Consider the reversible circuit shown in figure 2.9. The gates in the circuit are mapped to their quantum equivalent circuits resulting in circuit shown in figure 2.13.

Figure 2.13: Mapping of Reversible Half Adder Circuit to Quantum Circuit

Since the quantum gates can be applied on at most two-qubits, the maximum possible mapping for MCT/MPMCT gates is with the number of control lines as 2 i.e. Toffoli gate. Thus these gates are decomposed into NOT, CNOT or Toffoli gates before mapping to NCV gate library.

# 2.5 Cost Metrics for Reversible and Quantum Circuits

In this section, different cost metrics to evaluate reversible circuits that are available in the literature are discussed.

#### 2.5.1 Number of Gates

The 'number of gates' refers to the total number of reversible gates required to realize a given function. This metric depends on the gate library that is selected to implement the function. For example, the number of gates in the circuit shown in figure 2.8 is 4 when MPMCT gate library is selected but 8 when MCT gate library is selected. In this thesis, the widely used reversible gate library i.e. NCT gate library is chosen to compute the gate count in the circuit. The MCT/MPMCT gates in the circuit with more than two control lines are decomposed into NCT gates using the approach presented in Lemmas 7.2 and 7.3 of [49]. The cost of an MCT gate in terms of Toffoli gates is given in Eq. (2.9) and the total number of lines in circuit respectively. The total number of NCT gates that is present in a circuit gives the NCT cost of that circuit.

$$Cost_{NCT}(MCT) = \begin{cases} 8(c-3) & if \ c > \lceil \frac{n+1}{2} \rceil \\ 4(c-2) & if \ c \le \lceil \frac{n+1}{2} \rceil \end{cases}$$

(2.9)

where c and n denote the number of control lines of a gate.

#### 2.5.2 Quantum Cost

The Quantum Cost (QC) of a reversible gate is the number of primitive quantum gates required to implement the gate functionality. The primitive gates in NCV quantum library are NOT, CNOT, controlled V and controlled V+ gates [49]. The QC of a reversible gate is calculated according to RevLib [50] and is given in Table 2.2. Here c denotes the number of control lines and n denotes the total number of lines in the circuit. When all the control lines of an MCT gate are negative, the QC is increased by a value of 2. The QCs of each reversible gate in a circuit are summed up to calculate the QC of that circuit. As an example, the QC of the circuit shown in figure 2.8 is 1+5+13+1=20.

|     | QC                  |              |              |  |  |

|-----|---------------------|--------------|--------------|--|--|

| c   | $(n - (c + 1)) \ge$ |              |              |  |  |

|     | 0                   | 1            | c-2          |  |  |

| 0   | 1                   |              |              |  |  |

| 1   | 1                   |              |              |  |  |

| 2   | 5                   |              |              |  |  |

| 3   | 13                  |              |              |  |  |

| 4   | 29                  |              | 26           |  |  |

| 5   | 61                  | 52           | 38           |  |  |

| 6   | 125                 | 80           | 50           |  |  |

| 7   | 253                 | 100          | 62           |  |  |

| 8   | 509                 | 128          | 74           |  |  |

| 9   | 1021                | 152          | 86           |  |  |

| > 9 | $2^{c+1} - 3$       | 24(c+1) - 88 | 12(c+1) - 34 |  |  |

Table 2.2: Quantum Cost of an MCT gate

where c is number of control lines in an MCT gate; n is total number of lines in the circuit

#### 2.5.3 Number of Lines

The total number of qubits in a circuit indicates the number of lines required to implement the circuit. For example, the number of lines in the circuit shown in figure 2.8 is 4. For a reversible function, the number of lines is equal to the number of inputs. However in the case of classical irreversible functions, ancillary inputs and garbage output are added to realize a reversible circuit which increases this metric. Due to technology limitation, the number of qubits in a quantum circuit is restricted and thus different techniques have been presented and discussed in the literature to reduce the number of lines [41].

### 2.6 Summary

In this chapter, the preliminaries required to understand the work reported in the following chapters have been presented. The chapter introduced reversible logic functions and their characteristics along with procedure involved in the conversion of irreversible functions in to reversible ones. Different reversible gates and their properties, reversible gate libraries and reversible circuits have also been explained. Finally, mapping of reversible circuit to quantum circuits and cost functions used to evaluate these circuits have been discussed.

# Chapter 3

# Cube Decomposition Technique for Optimizing Reversible Logic Circuits

# 3.1 Introduction

As explained in Chapter 1, the existing synthesis algorithms/methods of reversible circuits typically generate sub-optimal circuits and thus optimization methods are applied to reduce circuit's cost. In this work, a decomposition technique that decompose pairs of gates to smaller gates while eliminating redundant gates is proposed. This technique is incorporated in Exclusive-OR Sum-of-Product (ESOP) based synthesis method which is then used to synthesize reversible functions. In the next section the background required to understand the decomposition technique and existing ESOP based synthesis methods are discussed.

# 3.2 Background

#### 3.2.1 Decomposition of an MCT/MPMCT gate

Any MCT/MPMCT gate can be decomposed into a network of smaller gates [49]. A fundamental decomposition method was presented in Lemma 7.3 of [49] by which an MCT/MPMCT gate of size m (where  $m \ge 5$ ) can be decomposed into a network of two gates, each of size p and two gates of size m - p + 1 each, given at least one unused line (line which is not a control or target line for the gate) in the circuit.

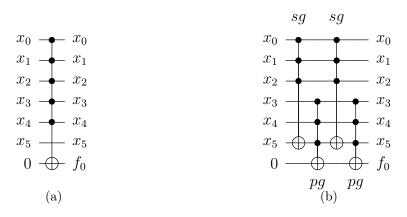

**Example 3.1.** Consider an MCT gate having 5 control lines,  $G = MCT(x_0, x_1, x_2, x_3, x_4; f_0)$ , shown in figure 3.1(a). According to Lemma 7.3 of [49], this gate can be decomposed into a network of four gates of size 3 (i.e., p = 3) as shown in figure 3.1(b).

Figure 3.1: Decomposition of MCT gate into network of four smaller gates

In this work, gates in the network that are realized on an unused line are termed as *secondary gates* (represented as sg in figure 3.1(b)) and the gates that are realized on the actual target line, i.e.,  $f_0$  are termed as *primary gates* (represented as pg in figure 3.1(b)). The decomposition network of a gate G can be written in terms of 'sg' and 'pg' as:

$$G = sg \circ pg \circ sg \circ pg$$

where ' $\circ$ ' denotes composition i.e. cascading of the gates/circuits.

# 3.2.2 Exclusive-Or Sum-of-Products (ESOP) based Reversible Circuit Synthesis

#### 3.2.2.1 Exclusive-Or Sum-of-Products (ESOP)

A traditional Sum-of-Product (SOP) is a method of representing a function using AND-OR expression, i.e., OR of several product terms. Likewise, an ESOP is a type of representation in AND-XOR expression, i.e., Exclusive-OR of several product terms [51]. The individual product terms in an ESOP expression are called *cubes* and the variables in its *positive* or *negative* polarity form are called *literals*. A *k*-variable function has different ESOP representations and thus many techniques, classified as exact and heuristic, are available in the literature to generate an ESOP expression. Exact technqiues [52–55] have been used to find ESOP expression with the smallest number of cubes but these techniques require large computation time and thus are applicable only for small functions. However, heuristic methods [56, 57] can find an ESOP expression even for large functions.

**Example 3.2.** Consider a function in SOP form as  $f = x_0\overline{x_1} + x_0x_2$ . The ESOP equivalent form of this function is  $f = x_0\overline{x_1} \oplus x_0x_1x_2$ . The term  $x_0\overline{x_1}$  and  $x_0x_1x_2$  in the function are termed as *cubes* and the variables  $x_0, x_1, \overline{x_1}, x_2$  are termed as *literals*.

In general the cubes are represented as a vector of inputs, i.e. for n variables, where  $x_0, x_1, \ldots, x_{n-1}$  are inputs and  $x_i \in \{0, 1, -\}$ , the cube  $C_i$  is represented as cube  $C_i = \langle x_0 x_1 \ldots x_{n-1} \rangle$ . The '-' in a cube indicates that the variable at that position has not appeared in the cube and is termed as a '*don't care*' literal. The ESOP functions are represented as a list of cubes called *cube lists*.

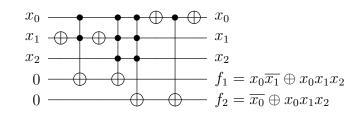

**Example 3.3.** Consider two functions  $f_1 = x_0 \overline{x_1} \oplus x_0 x_1 x_2$  and  $f_2 = \overline{x_0} \oplus x_0 x_1 x_2$ , where  $x_0, x_1$  and  $x_2$  are input variables and  $f_1$  and  $f_2$  are outputs. The cube list along with the cube outputs and representation of cubes for the functions  $f_1$  and  $f_2$  are shown in figure 3.2.

Figure 3.2: (a) Cube list and (b) representation of cubes for functions  $f_1 = x_0 \overline{x_1} \oplus x_0 x_1 x_2$ and  $f_2 = \overline{x_0} \oplus x_0 x_1 x_2$

#### 3.2.2.2 ESOP based Reversible Synthesis techniques

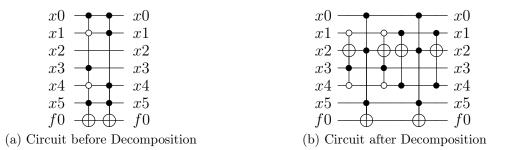

The ESOP based synthesis technique for reversible circuits has been introduced in [31] in which reversible as well classical functions can be synthesized in to reversible gate netlist. In this technique, the cubes corresponding to every output variable are mapped to an MCT gate. For example, considering the cube list shown in figure 3.2, the synthesized reversible circuit after applying this technique is shown in figure 3.3.

In order to reduce the quantum cost of synthesized circuits, different techniques have been presented [32–36]. A template matching approach has been presented in [32] by which different templates are applied on a cascade of MCT gates to reduce the quantum cost. A synthesis technique was presented in [33] which uses MPMCT gates

Figure 3.3: ESOP based Synthesis Technique presented in [31]

to eliminate the usage of NOT gates for negative literals in the cubes. Further, a set of transformation rules is defined to transfer the targets on outputs to some input lines which helps in reducing the number of lines in the circuit. An ordering based technique has been presented in [34] to reorder the ESOP cubes such that the number of NOT gates is reduced. In addition to this, a set of transformation rules has also been presented to improve the quantum cost of the circuit. Based on these transformation rules, a simulated annealing based approach has been developed in [35] to reduce the quantum cost of circuit. In order to reduce the number of CNOT gates used for sharing MCT gates among their outputs, a shared cube synthesis technique has been presented in [36] which finds multiple outputs that have the largest number of common cubes. These common cubes are first mapped on to respective MCT gates and then CNOT gates are added to share the common cubes between the outputs. All these techniques use EXORCISM-4 tool [57] to generate the cube list from truth tables or SOP expressions. There are few other techniques [58, 59] targeting only reversible circuits to generate cube lists.

## 3.3 Cube Decomposition Technique

#### 3.3.1 General Idea

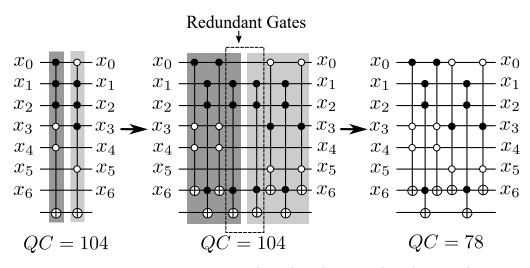

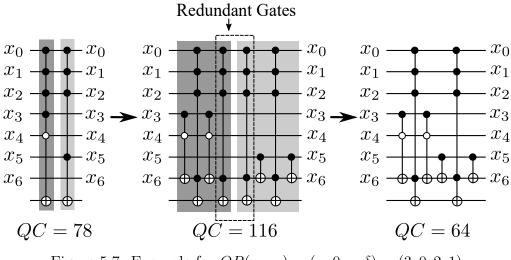

There are many optimization methods available in the literature for reversible circuits [17]. One of these methods decomposes an MPMCT gate in a reversible circuit into a network of smaller gates and removes redundant gates, if any. In general, this method is applied independently on individual gates and thus generation of maximum number of redundant gates may not happen. Rather than applying decomposition on individual gates, if the decomposition is applied on a pair of gates with a systematic approach, the chances of generation of redundant gates are higher. For example, considering a pair of gates shown in figure 3.4(a), two different types of decomposition for the same pair are shown in figures 3.4(b) and 3.4(c). The first decomposition is applied independently on individual gates without any constraints whereas the second decomposition is applied with a constraint to generate identical primary gates. The dotted box in figure 3.4(c) contains primary gates that are equal and thus redundant. Hence they can be removed from the circuit thereby reducing the quantum cost of the final decomposed circuit.

Figure 3.4: (a) Initial Circuit (QC=78) (b) Individual Gate decomposition (QC=98) (c) Pairwise decomposition (QC=62)

The following lemma proves different conditions by which redundant gates can be generated while decomposing a pair of gates. **Lemma 3.1.** Consider two MPMCT gates  $G_1$  and  $G_2$ . If the primary (or secondary) gates of two decomposed MPMCT gates,  $G_1$  and  $G_2$ , are identical or if one of the primary (or secondary) gates of  $G_1(G_2)$  is identical to other gate  $G_2(G_1)$ , then redundant gates can be generated which can be removed from the circuit.

*Proof.* Consider two MPMCT gates  $G_1$  and  $G_2$ . The decomposed network of these gates in terms of their primary and secondary gates can be represented as,

$$G_1 = sg_1 \circ pg_1 \circ sg_1 \circ pg_1$$

$$G_2 = sg_2 \circ pg_2 \circ sg_2 \circ pg_2$$

where  $pg_1$ ,  $pg_2$  represent primary gates and  $sg_1$ ,  $sg_2$  represent secondary gates for gates  $G_1$  and  $G_2$  respectively. The general circuit realization for the cascade of gates  $G_1$  and  $G_2$  is given as,

$$G_1 \circ G_2 = G_1 \circ G_2^{-1} \quad [:: MCT \text{ gates are self-inverse }]$$

$$= sg_1 \circ pg_1 \circ sg_1 \circ pg_1 \circ pg_2 \circ sg_2 \circ pg_2 \circ sg_2$$

(3.1)

If a pair of gates are equal and are adjacent, they can be removed from the circuit [24]. In Eq. (3.1) the primary gates of two MPMCT gates are equal and adjacent and thus can be removed from the netlist resulting in

$$G_1 \circ G_2 = sg_1 \circ pg_1 \circ sg_1 \circ sg_2 \circ pg_2 \circ sg_2 \tag{3.2}$$

Similarly, if the primary gates of one of the gates is equal to the other undecomposed

gate, then  $pg_1 \circ G_2 = \emptyset$ . Thus, the cascade of gate  $G_1$  and  $G_2$  can be reduced to

$$G_1 \circ G_2 = sg_1 \circ pg_1 \circ sg_1 \circ pg_1 \circ G_2$$

$$= sg_1 \circ pg_1 \circ sg_1$$

(3.3)

Thus from the above lemma, a systematic decomposition of MPMCT gates into a network of smaller gates can result in the reduction of cost of circuit implementation. Even though the decomposition technique discussed earlier is applied on MPMCT gates, it can also be applied on cubes because they can be directly realized using MPMCT gates. This means that the gate decomposition technique can be incorporated in to ESOP based synthesis techniques which are applied on cubes.

The MPMCT gate realization of a cube C, represented as G(C), can be decomposed into primary and secondary gates. The next subsection presents techniques to generate these primary and secondary gates for a given pair of cubes so as to satisfy Lemma 3.1.

# 3.3.2 Generation of Primary and Secondary gates for a Cube Pair

In order to generate the primary and secondary gates for a given pair of cubes, input variables of these cubes are assigned to three groups namely *equal*, *unequal* and *target* groups. The variables of a cube that are equal to the other cube (with same literal value) are assigned to *equal group* (E) and the variables of a cube that are not equal with the other cube are assigned to *unequal group* (U). The variables that are not present in the cube, i.e., variables with don't care term as values are assigned to *target*  group (T). The representation for these three groups is given as follows

$$E_a = E_b = \{x_i : a_i = b_i \neq `-`\}$$

$$U_a = \{x_i : a_i \neq b_i, a_i \neq `-`\} \& U_b = \{x_i : b_i \neq a_i, b_i \neq `-`\}$$

$$T_a = \{x_i : a_i = `-`\} \& T_b = \{x_i : b_i = `-`\}$$

where, the groups  $E_a$ ,  $U_a$  and  $T_a$  correspond to cube  $C_a$  and the groups  $E_b$ ,  $U_b$  and  $T_b$  correspond to cube  $C_b$ . The elements  $a_i$  and  $b_i$  indicate the value of input variable  $x_i$  in cubes  $C_a$  and  $C_b$  respectively.

**Example 3.4.** Consider two cubes,  $C_a = <10 - 101 >$  and  $C_b = <11 - -11 >$ . The equal, unequal and target groups of this cube pair are given as,

$$E_a = E_b = \{x_0, x_5\}$$

$$U_a = \{x_1, x_3, x_4\} \& U_b = \{x_1, x_4\}$$

$$T_a = \{x_2\} \& T_b = \{x_2, x_3\}$$

The variables in target group of a cube are taken as unused lines and they subsequently act as target lines for the generation of secondary gate. Considering that an unused line is represented as  $x_t$  and actual target line of an MPMCT gate is represented as t, the primary and secondary gates in terms of *equal* and *unequal* groups are given as,

$$pg = MPMCT(E, x_t; t) \& sg = MPMCT(U; x_t)$$

From the above expressions, E, U and t are known variables and the only unknown

variable that needs to be derived is  $x_t$ . Depending on the availability of  $x_t$  in target groups of a cube pair, there arise different cases that generate primary and secondary gates. These cases are discussed in the following subsections.

## **3.3.2.1** Case $1:T_a \cap T_b \neq \phi$

If  $T_a \cap T_b \neq \phi$ , then one of the variables (denoted as  $x_t$ ) from the set  $T_a \cap T_b$  can be chosen as target line for generation of secondary gates. Since a secondary gate's target line is also a primary gate's control line,  $x_t$  is added to the list of control lines of primary gates. Thus, the final primary and secondary gates representations are

$$sg_1 = MPMCT(U_a; x_t)$$

,  $sg_2 = MPMCT(U_b; x_t)$

$$pg_1 = pg_2 = MPMCT(E_a, x_t; t)$$

The following example illustrates generation of primary and secondary gates for a cube pair that satisfies this case.

**Example 3.5.** Consider two cubes  $C_a = <10 - 101 >$  and  $C_b = <11 - -11 >$ . The equal, unequal and target groups of this cube pair are

$$E_a = E_b = \{x_0, x_5\},\$$

$$U_a = \{x_1, x_3, x_4\} \& U_b = \{x_1, x_4\},\$$

$$T_a = \{x_2\} \& T_b = \{x_2, x_3\}$$

From the target groups  $T_a$  and  $T_b$ , it is evident that the variable  $x_2$  is common and can be used as a target line in generating secondary gates. Now, the primary and secondary gates are

$$sg_1 = MPMCT(x_1, x_3, x_4; x_2) , \ sg_2 = MPMCT(x_1, x_4; x_2)$$

$pg_1 = pg_2 = MPMCT(x_0, x_5, x_2; f_0)$

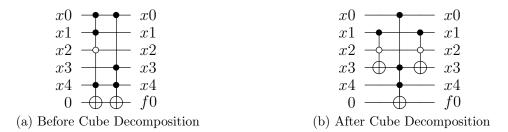

Since the primary gates of the cube pair are equal, the equivalent cube pair realization is  $G(C_a) \circ G(C_b) = sg_1 \circ pg_1 \circ sg_1 \circ sg_2 \circ pg_2 \circ sg_2$  from Lemma 3.1. The final circuit implementation of the cube pair  $C_a$  and  $C_b$  is shown in figure 3.5.

Figure 3.5: Gate decomposition for a pair of cubes with the same empty line as target line

#### **3.3.2.2** Case $2:T_a \cap T_b = \phi$

The previous case can be used only if there exists at least one common variable in both the target groups of cube pair. In this subsection, another technique is presented when there are no common variables in target groups, i.e.  $T_a \cap T_b = \phi$ . Here, two variables  $x_{ta}$  and  $x_{tb}$  are chosen from groups  $T_a$  and  $T_b$  respectively. These variables act as empty lines for generation of secondary gates and also as control lines for primary gates for their respective cubes. Thus the primary gates can be represented as

$$pg_1 = MPMCT(E_a, x_{ta}; t) \& pg_2 = MPMCT(E_b, x_{tb}; t)$$

From the above equations, it is evident that the primary gates of the cube pair are not equal. In order to make them equal, the variable  $x_{tb}$  is added to primary gate of the cube  $C_a$  and the variable  $x_{ta}$  is added to primary gate of the cube  $C_b$ . Since  $x_{tb}$  is a control line in primary gate of cube  $C_a$ , it can be removed from the unequal group. Similarly, the variable  $x_{ta}$  can be removed from the unequal group of the cube  $C_b$ . Thus the final gate realization of primary and secondary gates is

$$pg_1 = pg_2 = MPMCT(E_a, x_{ta}, x_{tb}; t)$$

$$sg_1 = MPMCT(U_a - \{x_{tb}\}; x_{ta}) \& sg_2 = MPMCT(U_b - \{x_{ta}\}; x_{tb})$$

The following example illustrates the generation of primary and secondary gates for a cube pair with no common variables in their target groups.

**Example 3.6.** Consider two cubes  $C_a = <10 - 101 >$  and  $C_b = <1 - 1011 >$ . The equal, unequal and target groups of these cubes are:

$$E_a = E_b = \{x_0, x_5\}$$

$$U_a = \{x_1, x_3, x_4\} \& U_b = \{x_2, x_3, x_4\}$$

$$T_a = \{x_2\} \& T_b = \{x_1\}$$

There is no common variable that exists in the target groups,  $T_a$  and  $T_b$ . Thus,  $x_2$  is selected for the generation of secondary gate for the cube  $C_a$  and  $x_1$  for the cube  $C_b$ , resulting in the primary and secondary gates as,

$$sg_1 = MPMCT(x_3, x_4; x_2), sg_2 = MPMCT(x_3, x_4; x_1)$$

$$pg1 = pg2 = MPMCT(x_0, x_5, x_1, x_2; f_0)$$

Since the primary gates of the cube pair are now equal, the cubes can be implemented as  $G(C_a) \circ G(C_b) = sg_1 \circ pg_1 \circ sg_1 \circ sg_2 \circ pg_2 \circ sg_2$  following Lemma 3.1. The final circuit implementation for the cube pair  $C_a$  and  $C_b$  is shown in figure 3.6.

Figure 3.6: Gate decomposition for a cube pair with different empty lines as target lines

#### **3.3.2.3** Case $3:pg_a = G(C_b)$ or $sg_a = G(C_b)$

As proved in Lemma 3.1, in a cascade of two MPMCT gates, if one of the gates' primary gate is equal to the other gate, the cost of circuit realization is reduced. For a pair of cubes, this condition is satisfied when one of the cubes' unequal group has only one variable (denoted as  $x_t$ ) and the same is present in the target group of the other cube. The cube with  $x_t$  in target group is decomposed in to primary and secondary gates as,

$$sg_1 = MPMCT(U_a; x_t)$$

$$pg_1 = MPMCT(E_a, x_t; t)$$

The following example illustrates the generation of primary and secondary gates for a cube pair with the condition discussed above.

**Example 3.7.** Consider two cubes  $C_a = <110 - 1 >$  and  $C_b = <1 - -11 >$ . The equal, unequal and target groups for this cube pair are

$$E_a = E_b = \{x_0, x_4\}$$

$$U_a = \{x_1, x_2\} \& U_b = \{x_3\}$$

$$T_a = \{x_3\} \& T_b = \{x_1, x_2\}$$

The unequal group of cube  $C_b$  has only one variable,  $x_3$ , which is also present in the target group of cube  $C_a$ . This variable can now act as a target line to generate secondary gate for cube  $C_a$  and is expressed as,

$$sg_1 = MPMCT(x_1, x_2; x_3)$$

$$pg_1 = MPMCT(x_0, x_4, x_3; f_0)$$

The gate implementation of cube  $C_b$  is  $G(C_b) = MPMCT(x_0, x_3, x_4; t)$ . Since the primary gate of one cube is equal to other cube's gate implementation, the cube pair can be realized as  $G_1 \circ G_2 = sg_1 \circ pg_1 \circ sg_1$  following Lemma 3.1. The final circuit implementation for the cube pair  $C_a$  and  $C_b$  is shown in figure 3.7.

#### 3.3.3 Algorithm for Cube Decomposition

In this section, the algorithm for cube decomposition technique is presented. The input to the algorithm is *cube\_list*, which has a list of cubes and output is reversible gate

Figure 3.7: Gate decomposition for a cube pair with  $pg_a = G(C_b)$

net-list *GateNetlist*. In the algorithm, initially a cube  $C_i$  from the given *cube\_list* is extracted. This cube is checked with the other cubes in the *cube\_list* for any possible decomposition using the function *CheckingDecomposition()*. This function returns true if the pair of cubes can be decomposed with any one of the proposed decomposition techniques else it returns false.

If the return value is false, then the gate realization of cube  $C_i$  is added to the GateNetlist. If the return value is true, the decomposed gate netlist,  $List_{deco}$ , and its cost,  $Cost_{deco}$ , are obtained using the function Decomposition(). After all the cubes in the  $cube\_list$  are checked for decomposition condition, the cube which has the least circuit cost after decomposition is termed as BestCube and its cost as BestCost. If the BestCost is less than the sum of the costs of gate realization of cube  $C_i$  and BestCube, the decomposed netlist of BestCube is assigned to BestDeco and is appended to the GateNetlist. If the BestCost is greater than the cost of gate realization of cube  $C_i$  plus the cost of BestCube, the gate realization of cube  $C_i$  is added to the GateNetlist. The pseudo code of this algorithm is given below:

This algorithm is illustrated with the following example.

**Example 3.8.** Consider the cube list,  $cube\_list$ , with four cubes,  $C_1, C_2, C_3$  and  $C_4$ , shown in figure 3.8 which is given as input to Algorithm 3.1.

In the first iteration,  $C_1$  is removed from the *cube\_list* and is checked for decom-

| Algorithm 3.1 | Cube Decom | position Algorithm |

|---------------|------------|--------------------|

|---------------|------------|--------------------|

```

1: Input: cube list

2: Output: Reversible GateNetlist

3: begin

4: while cube list is not empty do

flag = false

5:

C_i = pop(cube \ list)

6:

BestCost = \infty

7:

for each cube C_j \in cube\_list do

8:

if CheckDecomposition(C_i, C_i) is true then

9:

Cost_{deco}, List_{deco} = Decomposition(C_i, C_j)

10:

InitCost = MCTCost(C_i) + MCTCost(C_j)

11:

if min\{BestCost, InitCost\} > Cost_{deco} then

12:

flaq = true

13:

BestCost = Cost_{deco}

14:

BestCube = C_i

15:

BestDeco = List_{deco}

16:

end if

17:

end if

18:

end for

19:

if flaq is true then

20:

AddToArray(GateNetlist, BestDeco)

21:

DeleteCube(cube list, BestCube)

22:

23:

else

AddToArray(GateNetlist, GenerateMCT(C_i))

24:

25:

end if

26: end while

27: return GateNetlist

28: end

```

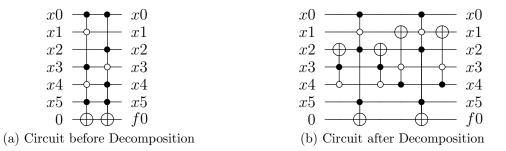

position with every other cube in the  $cube\_list$ . First, the cube  $C_2$  is checked with  $C_1$  for decomposition using the function CheckDecomposition. Since none of the cases discussed above is satisfied, this function return false and moves to next cube in the list i.e.,  $C_3$ . Similar to  $C_2$ , the cube  $C_3$  does not satisfy any of the cases, thus resulting in CheckDecomposition function returning false. However, this function returns true when checked with the cube  $C_4$  because it satisfies the condition described in *case 3*. Hence, the function Decomposition returns the decomposed gate netlist and its cost (27) after applying the decomposition technique as shown in figure 3.9. This cost is less than the sum of cost of implementation of cubes  $C_1$  and  $C_4$  individually i.e. 42 setting

|       | $x_0$            | $x_1$ | $x_2$ | $x_3$ | $x_4$ | f |