# **Energy Efficient Multicore Scheduling Algorithms for Real Time Systems**

### THESIS

Submitted in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY**

> by MAYURI A. DIGALWAR

Under the Supervision of

### Prof. Sudeept Mohan and

Prof. Biju K. Raveendran

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI 2016

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (Rajasthan)

### **CERTIFICATE**

This is to certify that the thesis entitled "**Energy Efficient Multicore Scheduling Algorithms for Real Time Systems**" and submitted by Mrs. Mayuri A. Digalwar, ID No. 2009PHXF432P, for award of Ph.D. degree of the institute embodies original work done by her under our supervision.

Signature of Co-Supervisor Name: BIJU K. RAVEENDRAN Designation: Assistant Professor Department of CSIS, BITS, Pilani, Goa Campus Date: Signature of Supervisor Name: SUDEEPT MOHAN Designation: Professor Department of CSIS, BITS, Pilani, Pilani Campus Date:

Dedicated to My Family

### Acknowledgement

My journey of Ph.D. required the countless and selfless support, generosity and time of many people in my personal and academic life. I am glad to take the opportunity to acknowledge and thank all of them.

I am deeply grateful to Prof. Sudeept Mohan, my supervisor, for his constant support, guidance and kindness during my pursuit in Ph.D. degree. This work would not have been possible without his guidance and involvement, his support and encouragement on daily basis from the beginning till this moment. His zeal of perfection and commitment towards work always inspired me to do more. He has always been a great advisor, teacher and mentor for me in my research as well as in my academic career. I am thankful to him for having long discussions with me and giving me invaluable suggestions which helped me to grow my understanding and gain maturity in research. I particularly appreciate him for finding time from his busy schedule whenever I asked for it. I deeply express my gratitude and thank him for his support and concern.

While many students are fortunate to have a single supervisor, I have been blessed with two. I am deeply grateful to Prof. Biju K. Raveendran, my co-supervisor, for his invaluable guidance and support throughout my Ph.D. work. He has been a constant source of encouragement to me. His expertise and experience further enriched my knowledge and understanding in research. The discussions with him have always shown me new directions and made me curious to go into the depth of concept. Since he is located in BITS Pilani, Goa campus, we use to interact with each other through skype calls and emails. I am thankful to him for making this research work successful under this constraint of location.

I am thankful to Prof. Souvik Bhattacharyya, Vice Chancellor, BITS Pilani and Prof. Ashoke Kumar Sarkar, Director, BITS Pilani, Pilani campus for giving me an opportunity to pursue my Ph.D. research with financial support. I am thankful to Prof. Sanjay Kumar Verma, Dean, and Prof. Hemant R. Jadhav, Associate Dean, Academic Research Division (Ph.D. Programme) for providing necessary guidelines and extending full support, which were very important for the successful completion of this thesis. I would like to thank Prof. S.C. Sivasubramanian, Dean, Administration and Prof. J.P. Misra, Unit Chief, Information Processing Centre for their encouragement and support during the entire duration of this research.

Besides my advisors, I would like to thank to my Doctoral Advisory Committee (DAC) members, Prof. S. Gurunarayanan, Dean, WILP and Dr. Abhishek Mishra, Assistant Professor in Computer Science and Information Systems for evaluating my work and giving me valuable comments and suggestions. I also thank all the reviewers of various conferences and journals for reviewing our research papers and providing their valuable comments and suggestions for improvement.

I am thankful to the Head of the Department, Prof. Rahul Banerjee for all his support in granting funds for attending conferences and his constant encouragement throughout. I would like to thank the Convener and all members of Doctoral Research Committee (DRC) for their constant support and guidance. My sincere thanks also go to Prof. Sundar Balasubramaniam, Prof. Navneet Goyal, Prof. Poonam Goyal and Dr. Virendra Singh Shekhawat. I am grateful to them for giving me valuable feedback and suggestions during the departmental seminars which had strengthen my work over time. I am also thankful to Mr. Sanwarmal for his administrative support throughout.

I thank my fellow colleagues who have been a constant source of motivation, encouragement and inspiration. Particularly, my friends, Vandana, Avinash and Asma were always been there to support me technically through stimulating discussions. I had received a big support from them in difficult situations during my research work. I would also like to acknowledge one of my past post-graduate students, Mr. Pravin Gahukar with whom I have worked on one of the problems in this thesis.

A special thanks to my family. Words cannot express how grateful I am to my mother-in-law, Sau. Ratna Digalwar and father-in-law, Shri. K. M. Digalwar for the sacrifices made by them on my behalf. Without their constant support and motivation right from the beginning till this moment, I would not have finished my work peacefully. I deeply owe to my parents, who motivated and helped me at every stage of my life. I miss a lot my father, Late. Shri. Nishikant Rajurwar who is not with me to share this moment of happiness. I would like to show my gratitude towards my mother, Smt. Maya Rajurwar for her love and trust which gave me strength throughout my life and in this Ph.D. work.

I owe thanks to a special person, my husband, Prof. Abhijeet Digalwar for his continued and unfailing love, support and understanding during my pursuit of Ph.D. degree that made completion of this thesis possible. He was always there with me in the moments when there was no one to solve my difficulties. I greatly value his contribution and deeply

appreciate his belief in me. Last but not the least, I appreciate my son, Akshat for the long lasting patience and understanding he showed during the entire Ph.D. work and thesis writing. I consider myself luckiest to have such a loving and caring son.

Lastly, I thank the Almighty for giving me strength and patience to work.

Mayuri

### Abstract

With the advancement of technology and ever increasing demand of portable, scalable and sophisticated embedded systems, managing energy consumption to prolong the battery life of embedded devices has become a big challenge. With the advent of multi-core processors in the embedded market, reducing the energy consumption is becoming increasingly important for multi-core processors as well.

Modern multi-core processors consume two types of energy, viz., dynamic and static energy. Dynamic energy is consumed due to switching activity whereas static energy is consumed due to increase in leakage current. These processors have capability to dynamically lower the supply voltage that reduces dynamic energy consumption. However, reducing supply voltage increases gate delay which requires one to lower operating frequency. As a consequence, the tasks take more time to execute. In this thesis, we have focused on real time embedded systems that execute hard and soft real time tasks. The major challenge for these systems is to optimize energy consumption using dynamic voltage and frequency scaling (DVFS) without missing the timing constraints of the hard real time tasks and responsiveness of the soft real time tasks. The energy saving achieved by DVFS is severely limited with the dramatic increase in leakage power consumption. Therefore, to minimize the overall energy consumption, there is a need to optimize dynamic as well as static energy consumption.

This thesis addresses the issue of overall energy optimization in real time embedded systems at the operating system level using efficient real time task scheduling algorithms. The proposed energy efficient scheduling algorithms, Energy Efficient Dynamic Voltage and Frequency Scaling (EEDVFS) and Energy Efficient Uni-Core Scheduler (EE-UCS) optimize dynamic energy consumption of uniprocessor. Another proposed energy efficient scheduling algorithm, Multi-Core Scheduler (MCS) optimizes dynamic energy consumption of homogeneous multi-core processors. These algorithms are capable of scheduling the hard and soft real time tasks together. They use dynamic voltage and frequency scaling technique to reduce dynamic energy consumption. The slack reclamation scheme devised to select the optimal frequency is very aggressive and achieves maximum energy saving. At the same time, the method of allocation and scheduling of soft real time tasks helps to achieve acceptable response time. But the limitation of these algorithms is that they are not capable

of reducing static energy consumption. Therefore, we proposed an energy efficient scheduling algorithm - Leakage Aware Multi-Core Scheduler (LAMCS), which is an extension to the previous algorithm MCS. The proposed LAMCS algorithm is capable of minimizing both dynamic and static energy consumption resulting in overall energy minimization. LAMCS is also capable of scheduling hard and soft real time tasks together. Along with DVFS technique, LAMCS uses dynamic shutdown and procrastination schemes to reduce dynamic as well as static energy consumption.

A full-fledged simulation tool has been developed as a significant part of this work in order to implement, test and evaluate the performance of the proposed algorithms. The simulation tool is divided into two major categories - Task Scheduling and Task Set Generation. Current simulator includes implementations of Earliest Deadline First (EDF), EDF with Total Bandwidth Server (TBS) and Deferrable Server (DS), cycle conserving EDF with TBS and DS for uniprocessor and multi-core processor platforms, DVFS based multi-core scheduler implementation for mixed work load (MCS), leakage aware scheduler, DVFS based leakage aware multi-core scheduler (LAMCS) etc. It has modules to generate synthetic task sets of two types: periodic task sets and mixed task sets. The mixed task sets contain hard and soft real time tasks. There are other modules which are responsible for the calculation of various performance metrics such as energy consumption, aperiodic task's response times, various decision counts such as scheduling points, preemption count, migration count, cache impact points etc.

The simulation tool is written in java programming language that makes use of object oriented paradigm. The graphical User Interface (GUI) of simulator is very user friendly and is easy to explore and use. The use of abstract classes facilitates addition of new scheduling algorithms in the current version of simulator. Finally, an important and novel aspect of simulator is its ability to produce analytical results of the algorithms by plotting various graphs.

The proposed algorithms in this work are extensively tested and evaluated using synthetically generated benchmark suites. The parameters of energy consumption used in all the experiments are taken from the Transmetta Crusoe processor.

## **Table of Contents**

| ACKNOWLEDGEMENT                   |                                                   | iii  |

|-----------------------------------|---------------------------------------------------|------|

| ABSTRACT                          |                                                   |      |

| LIST OF FIGURES<br>LIST OF TABLES |                                                   |      |

|                                   |                                                   |      |

| ACRON                             | NYMS                                              | xvii |

| 1. Intr                           | oduction                                          | 1    |

| 1.1                               | Motivation                                        | 1    |

| 1.2                               | Research Background                               | 3    |

|                                   | 1.2.1 Processor Energy Consumption                | 3    |

|                                   | 1.2.2 Hardware Platform                           | 4    |

|                                   | 1.2.2.1 Classification of Multi-core Processors   | 5    |

|                                   | 1.2.2.2 Memory Architecture                       | 5    |

|                                   | 1.2.3 Real Time Task Model                        | 7    |

|                                   | 1.2.4 Energy Efficient Real Time Task Scheduling  | 9    |

| 1.3                               | Research Objectives                               | 10   |

| 1.4                               | Methodology                                       | 10   |

| 1.5                               | Thesis Organization                               | 11   |

| 2. Lite                           | rature Review                                     | 13   |

| 2.1                               | Introduction                                      | 13   |

| 2.2                               | Background                                        | 14   |

|                                   | 2.2.1 Classification of Energy Aware Scheduling   | 14   |

|                                   | 2.2.2 Dynamic Energy Optimization                 | 14   |

|                                   | 2.2.3 Overall Energy Optimization                 | 16   |

| 2.3                               | Scheduling Algorithms for Uniprocessor Platform   | 17   |

|                                   | 2.3.1 Dynamic Energy Saving                       | 17   |

|                                   | 2.3.1.1 Periodic Task Model                       | 17   |

|                                   | 2.3.1.2 Mixed Task Model                          | 20   |

|                                   | 2.3.2 Overall Energy Saving                       | 24   |

| 2.4                               | Scheduling Algorithms for Multiprocessor Platform | 26   |

|                                   | 2.4.1 Non Energy Aware Scheduling                 | 26   |

|                                   | 2.4.1.1 Periodic Task Model                       | 27   |

|                                   | 2.4.1.2 Mixed Task Model                          | 27   |

|    |     | 2.4.2 Dynamic Energy Saving                                                     | 28 |

|----|-----|---------------------------------------------------------------------------------|----|

|    |     | 2.4.3 Overall Energy Saving                                                     | 30 |

|    | 2.5 | Scheduling Algorithms for Multi-core Processor Platform                         | 31 |

|    | 2.6 | Research Gaps and Challenges                                                    | 41 |

| 3. | Dyn | namic Voltage and Frequency Scaling Based Multi-Core Scheduling                 | 43 |

|    | 3.1 | Introduction                                                                    | 43 |

|    | 3.2 | System Model                                                                    | 45 |

|    |     | 3.2.1 Energy Model                                                              | 45 |

|    |     | 3.2.2 Processor and Task Model                                                  | 47 |

|    | 3.3 | Scheduling on Uniprocessor Systems                                              | 48 |

|    | 3.4 | Proposed Energy Efficient Uniprocessor based Scheduling Algorithm (EEDVFS)      | 50 |

|    |     | 3.4.1 Notations                                                                 | 50 |

|    |     | 3.4.2 EEDVFS Algorithm                                                          | 50 |

|    | 3.5 | Scheduling on Multi-core Systems                                                | 52 |

|    |     | 3.5.1 Task Allocation                                                           | 52 |

|    |     | 3.5.1.1 Partitioned Task Allocation Strategy                                    | 52 |

|    |     | 3.5.1.2 Global Task Allocation Strategy                                         | 55 |

|    |     | 3.5.1.3 Hybrid Task Allocation Strategy                                         | 56 |

|    |     | 3.5.2 Task Scheduling                                                           | 56 |

|    | 3.6 | Proposed Multi-Core Scheduling Algorithm (MCS)                                  | 58 |

|    |     | 3.6.1 Proposed Algorithm                                                        | 58 |

|    |     | 3.6.2 Schedule of Sample Task Set using MCS Algorithm                           | 62 |

|    |     | 3.6.3 Correctness Proof and Schedulability of MCS Algorithm                     | 65 |

|    |     | 3.6.4 Algorithmic Complexity of MCS Algorithm                                   | 67 |

|    | 3.7 | Parameters for Comparison                                                       | 68 |

|    |     | 3.7.1 Response Time                                                             | 68 |

|    |     | 3.7.2 Scheduling Decision Points                                                | 69 |

|    |     | 3.7.3 Preemption Count                                                          | 70 |

|    |     | 3.7.4 Migration Count                                                           | 70 |

|    |     | 3.7.5 Energy Consumption                                                        | 71 |

|    | 3.8 | Experimental Setup                                                              | 73 |

|    | 3.9 | Results and Discussions                                                         | 74 |

|    |     | 3.9.1 Performance Analysis of Proposed Uniprocessor based Scheduling Algorithms | 74 |

|    |     | 3.9.2 Performance Analysis of Proposed Multi-core Scheduling Algorithm (MCS)    | 78 |

|    |     | 3.9.2.1 Effect on Energy Consumption                                            | 78 |

|    |     |                                                                                 |    |

|    |      |        | 3.9.2.2           | Effect on Response Time                                        | 81  |

|----|------|--------|-------------------|----------------------------------------------------------------|-----|

|    |      |        | 3.9.2.3           | Effect on Scheduling Events                                    | 83  |

|    | 3.10 | Summ   | nary              |                                                                | 88  |

| 4. |      | -      | Aware D<br>System | ynamic Voltage and Frequency Scaling Based Scheduling for<br>s | 90  |

|    | 4.1  | Introd | uction            |                                                                | 90  |

|    | 4.2  | Syster | n Model           |                                                                | 91  |

|    | 4.3  | Shutd  | own Ove           | rhead                                                          | 93  |

|    | 4.4  | Propo  | sed Leak          | age Aware Multi-core Scheduling Algorithm (LAMCS)              | 94  |

|    |      | 4.4.1  | Task All          | ocation                                                        | 94  |

|    |      | 4.4.2  | Voltage           | and Frequency Scaling                                          | 94  |

|    |      | 4.4.3  | Procrast          | ination and Shutdown                                           | 96  |

|    | 4.5  | Sched  | ule of Sa         | mple Task Set using LAMCS Algorithm                            | 100 |

|    | 4.6  | Corre  | ctness Pr         | oof and Schedulability of LAMCS Algorithm                      | 104 |

|    | 4.7  | Algor  | ithmic C          | omplexity of LAMCS Algorithm                                   | 108 |

|    | 4.8  | Energ  | y Calcul          | ations for Proposed LAMCS Algorithm                            | 109 |

|    | 4.9  | Result | ts and Di         | scussions                                                      | 110 |

|    |      | 4.9.1  | Perforn<br>Tasks  | nance Analysis of Proposed LAMCS considering only Periodic     | 111 |

|    |      | 4.9.2  | Perform           | nance Analysis of Proposed LAMCS considering Mixed Task sets   | 113 |

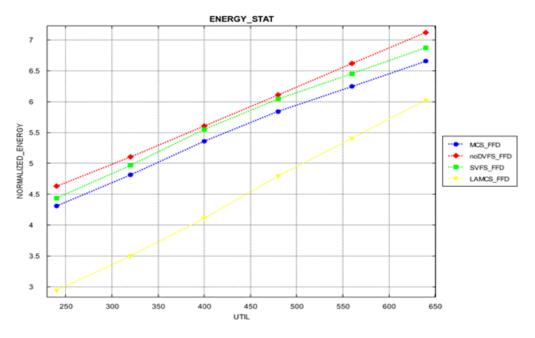

|    |      |        | 4.9.2.1           | Effect on Energy Consumption                                   | 113 |

|    |      |        | 4.9.2.2           | Effect on Response Time                                        | 118 |

|    |      |        | 4.9.2.3           | Effect on Scheduling Events                                    | 121 |

|    |      | 4.9.3  | Compa             | rison of Static Energy Consumption                             | 124 |

|    | 4.10 | ) Sumn | nary              |                                                                | 126 |

| 5. | Task | set G  | eneratio          | n and Scheduler Simulator: STREAM                              | 128 |

|    | 5.1  | Introd | uction            |                                                                | 128 |

|    | 5.2  | Backg  | ground            |                                                                | 129 |

|    | 5.3  | Archi  | tecture of        | f STREAM                                                       | 132 |

|    |      | 5.3.1  | General           | Purpose Design                                                 | 132 |

|    |      | 5.3.2  | Subsyste          | em Architecture                                                | 133 |

|    |      |        | 5.3.2.1           | System Modeler                                                 | 134 |

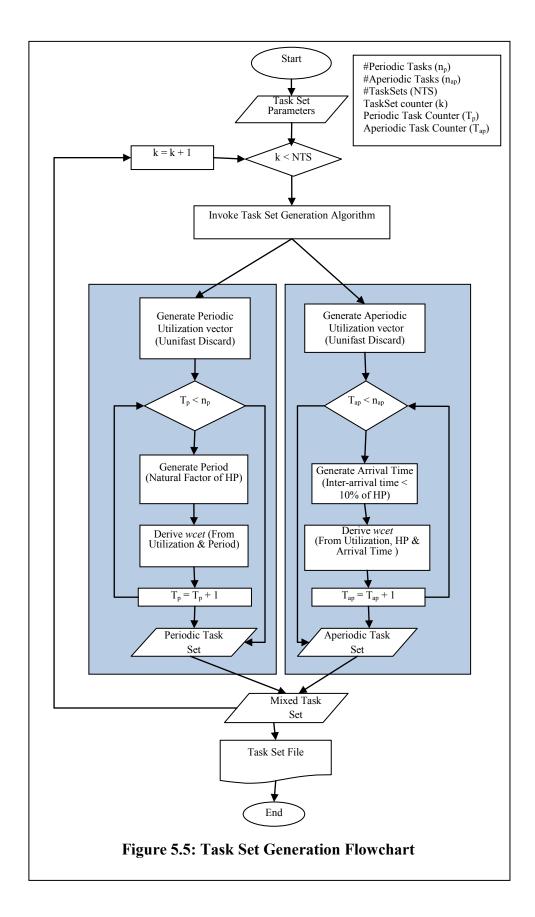

|    |      |        | 5.3.2.2           | Task Set Generator                                             | 137 |

|    |      |        | 5.3.2.3           | Schedulers, Controllers and Servers                            | 144 |

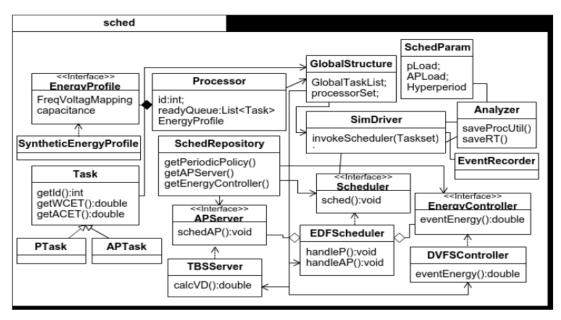

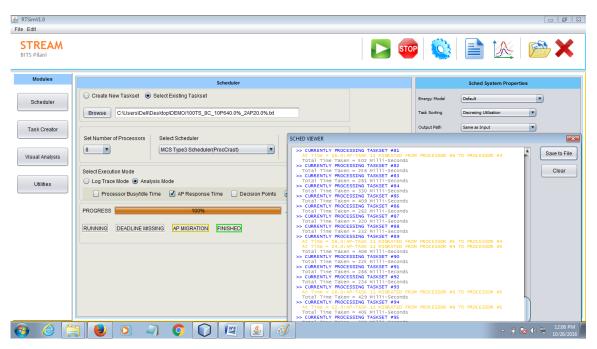

|    |      |        | 5.3.2.4           | Current Design of STREAM                                       | 145 |

|    |      |        | 5.3.2.5           | Output Subsystem of STREAM                                     | 148 |

| 5.3.2.6                                      | Performance Analyzer and Scheduling Profiler | 151 |

|----------------------------------------------|----------------------------------------------|-----|

| 5.3.2.7                                      | Visual Analyzer                              | 155 |

| 5.4 Summary                                  |                                              | 156 |

|                                              |                                              |     |

| 6. Conclusions and Fut                       | ture Work                                    | 158 |

| Appendix A                                   |                                              | 164 |

| References                                   |                                              | 177 |

| List of Publications                         |                                              | 197 |

| Brief Biography of Candidate and Supervisors |                                              | 198 |

# **List of Figures**

| Figure No. | Caption                                                                                                                       | Page No. |

|------------|-------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1        | Hierarchical Memory Architecture                                                                                              | 7        |

| 1.2        | Thesis Organization Roadmap                                                                                                   | 11       |

| 2.1        | Taxonomy of Energy Aware Real Time Scheduling                                                                                 | 15       |

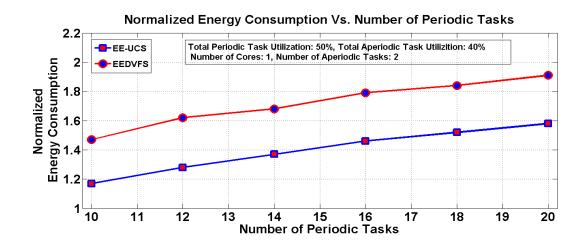

| 3.1        | Normalized Energy Consumption Vs. Number of Periodic Tasks (Uni-Core)                                                         | 75       |

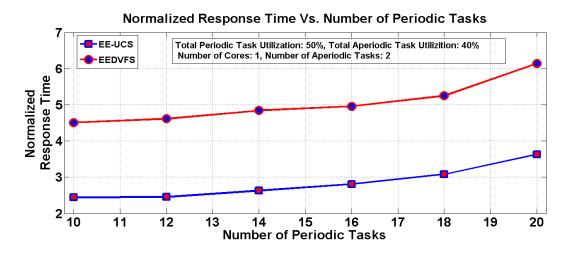

| 3.2        | Normalized Response Time Vs. Number of Periodic Tasks (Uni-Core)                                                              | 75       |

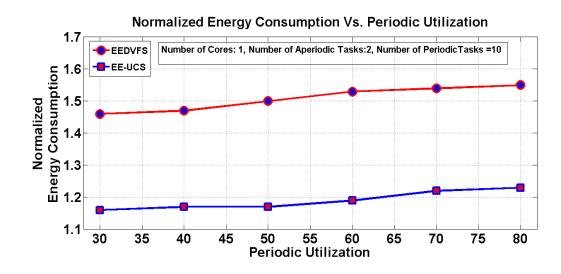

| 3.3        | Normalized Energy Consumption Vs. Periodic Utilization (Uni-Core)                                                             | 76       |

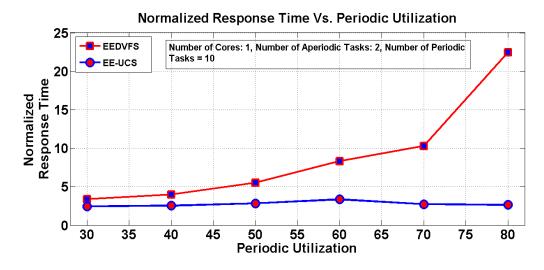

| 3.4        | Normalized Response Time Vs. Periodic Utilization (Uni-Core)                                                                  | 76       |

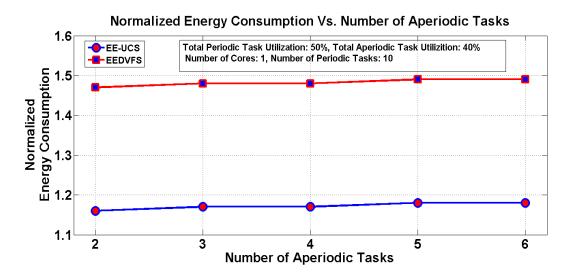

| 3.5        | Normalized Energy Consumption Vs. Number of Aperiodic Tasks (Uni-<br>Core)                                                    | 77       |

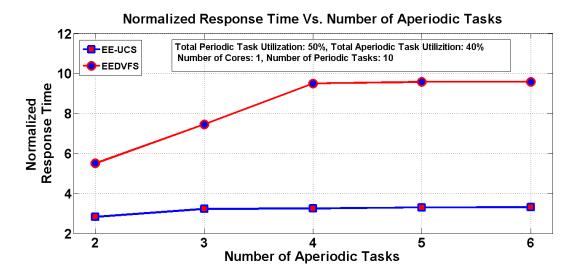

| 3.6        | Normalized Response Time Vs. Number of Aperiodic Tasks (Uni-Core)                                                             | 77       |

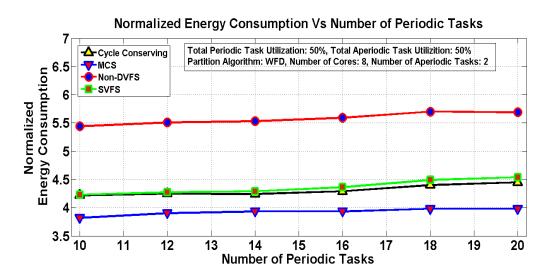

| 3.7        | Normalized Energy Consumption Vs. Number of Periodic Tasks                                                                    | 79       |

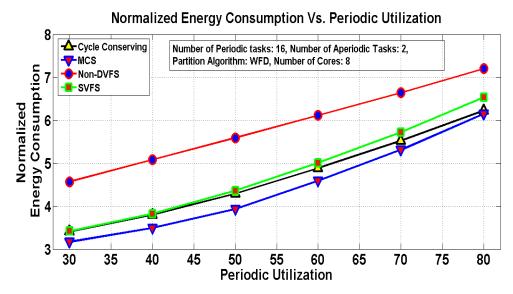

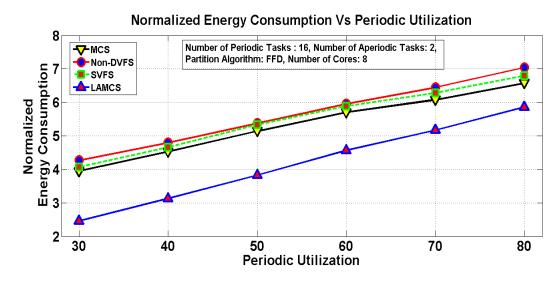

| 3.8        | Normalized Energy Consumption Vs. Periodic Utilization                                                                        | 79       |

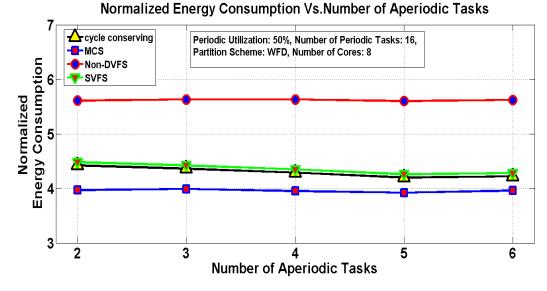

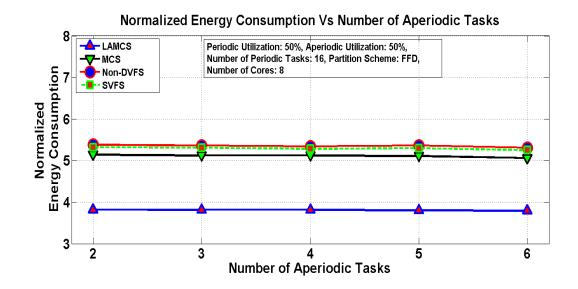

| 3.9        | Normalized Energy Consumption Vs. Number of Aperiodic Tasks                                                                   | 80       |

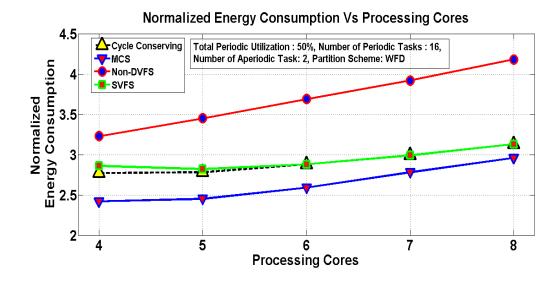

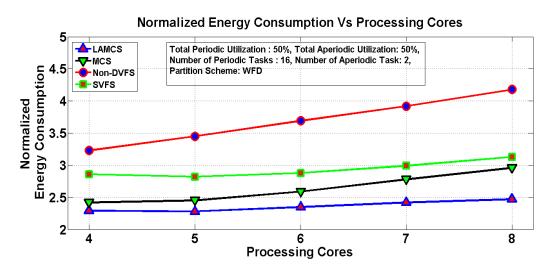

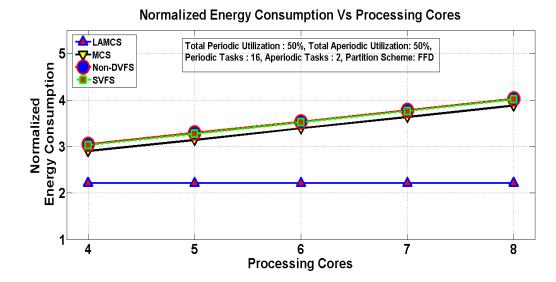

| 3.10       | Normalized Energy Consumption Vs. Processing Cores                                                                            | 80       |

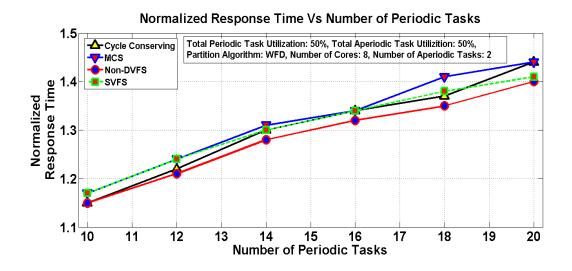

| 3.11       | Normalized Response Time Vs. Number of Periodic Tasks                                                                         | 82       |

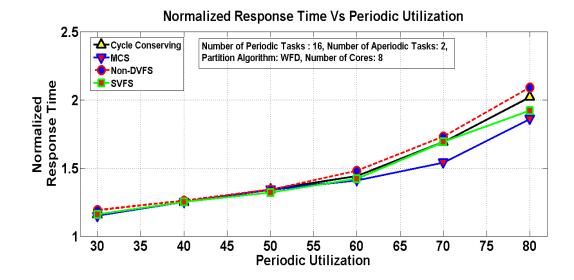

| 3.12       | Normalized Response Time Vs. Periodic Utilization                                                                             | 82       |

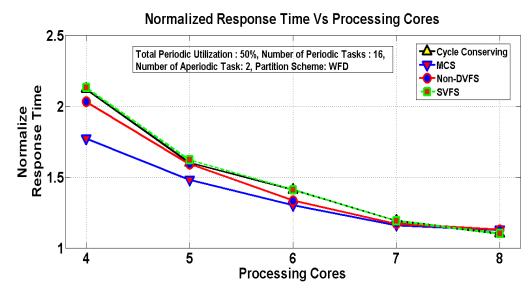

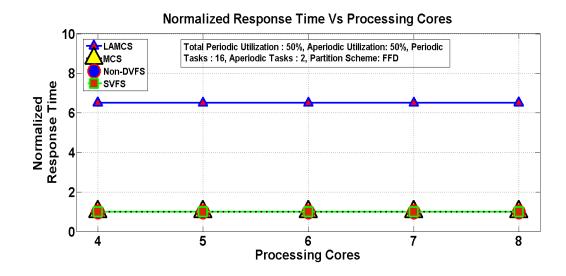

| 3.13       | Normalized Response Time Vs. Processing Cores                                                                                 | 83       |

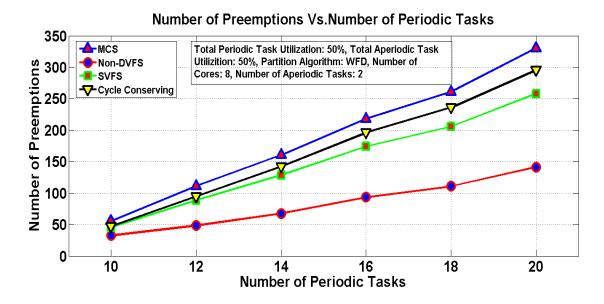

| 3.14       | Number of Preemptions Vs. Number of Periodic Tasks                                                                            | 84       |

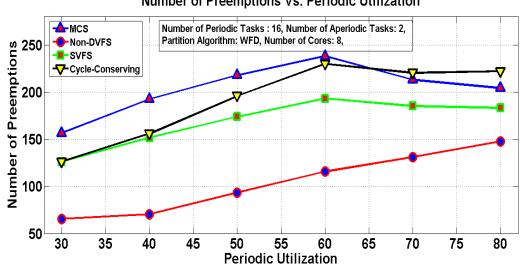

| 3.15       | Number of Preemptions Vs. Periodic Utilization                                                                                | 84       |

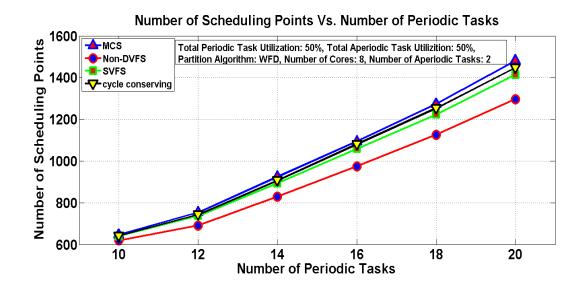

| 3.16       | Number of Scheduling Decision Points Vs. Number of Periodic Tasks                                                             | 85       |

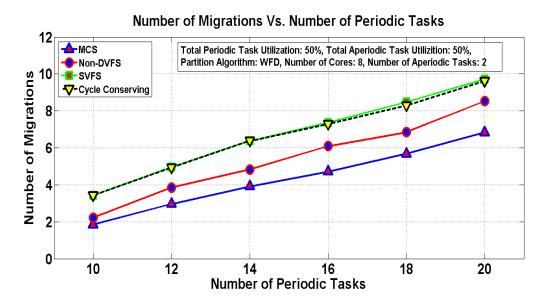

| 3.17       | Number of Migrations Vs. Number of Periodic Tasks                                                                             | 86       |

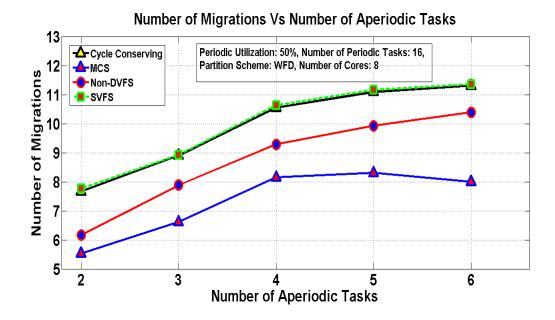

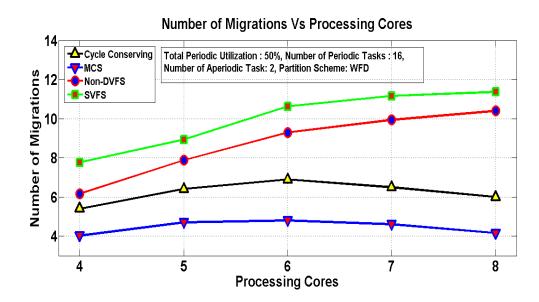

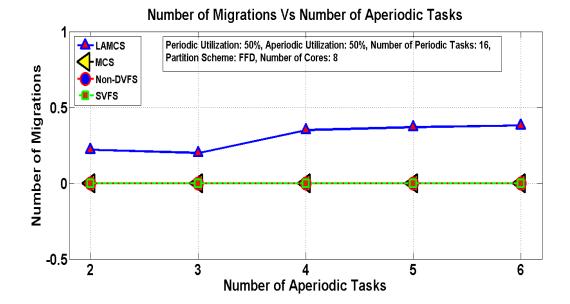

| 3.18       | Number of Migrations Vs. Number of Aperiodic Tasks                                                                            | 86       |

| 3.19       | Number of Migrations Vs. Processing Cores                                                                                     | 87       |

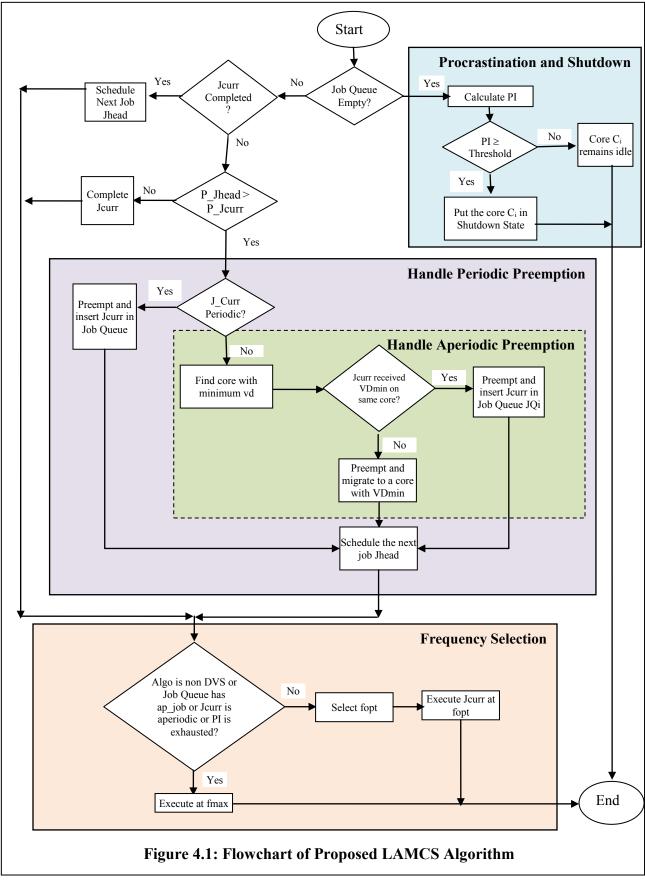

| 4.1        | Flowchart of Proposed LAMCS Algorithm                                                                                         | 99       |

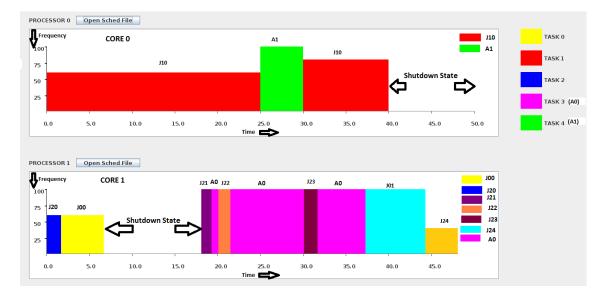

| 4.2        | Timing Diagram for the schedule on Core 0 and Core 1                                                                          | 104      |

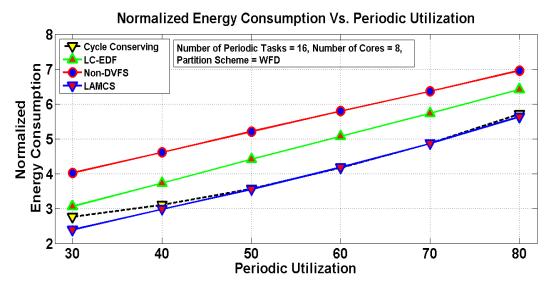

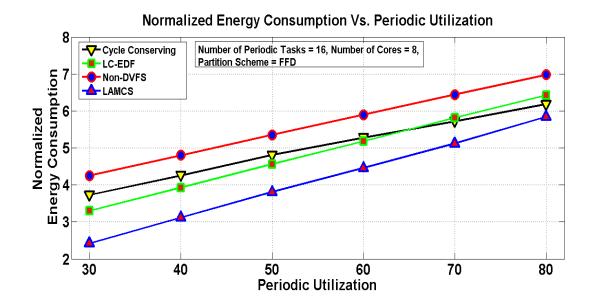

| 4.3        | Normalized Energy Consumption Vs. Periodic Utilization<br>(WFD partition scheme and task set constitutes only periodic tasks) | 112      |

| 4.4        | Normalized Energy Consumption Vs. Periodic Utilization<br>(FFD Partition scheme and task set constitutes only periodic tasks) | 112      |

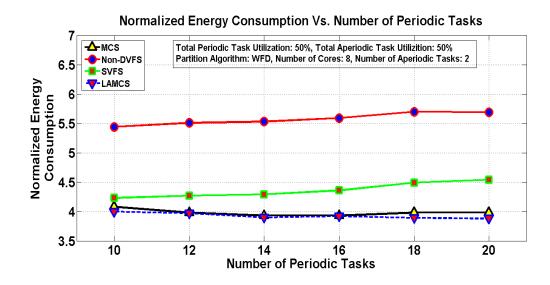

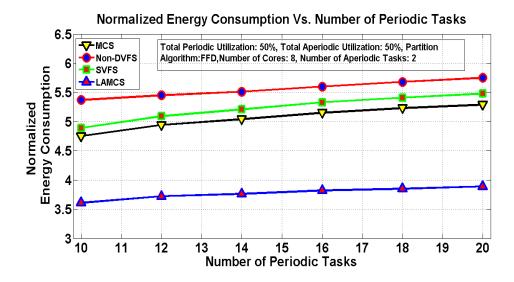

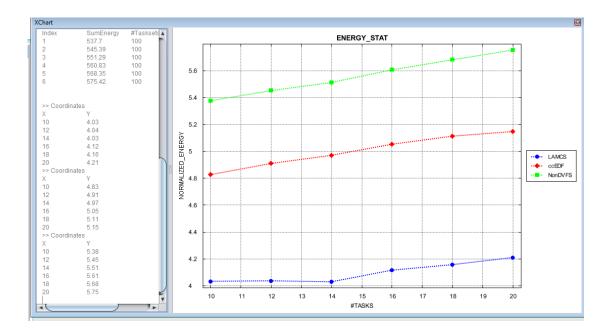

| 4.5        | Normalized Energy Consumption Vs. Number of Periodic Tasks (WFD Partition Scheme)                                             | 114      |

| 4.6        | Normalized Energy Consumption Vs. Number of Periodic Tasks (FFD Partition Scheme)                                             | 114      |

| 4.7        | Normalized Energy Consumption Vs. Periodic Utilization (FFD Partition Scheme)                                                 | 115      |

| Figure No. | Caption                                                                              | Page No |

|------------|--------------------------------------------------------------------------------------|---------|

| 4.8        | Normalized Energy Consumption Vs. Number of Aperiodic Tasks (FFD Partition Scheme)   | 116     |

| 4.9        | Normalized Energy Consumption Vs. Processing Cores (WFD Partition Scheme)            | 117     |

| 4.10       | Normalized Energy Consumption Vs. Processing Cores (FFD Partition Scheme)            | 117     |

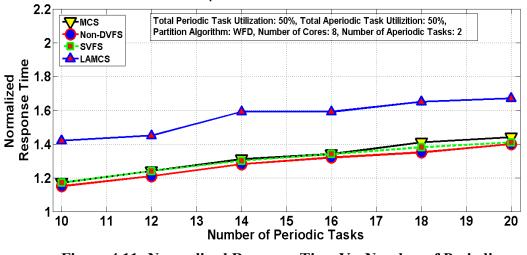

| 4.11       | Normalized Response Time Vs. Number of Periodic Tasks (WFD Partition Scheme)         | 119     |

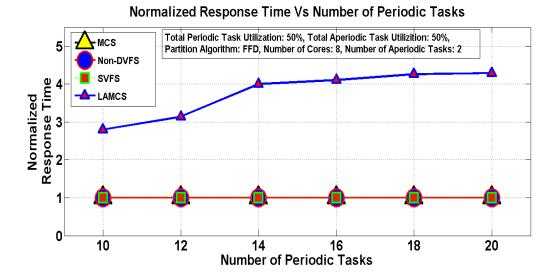

| 4.12       | Normalized Response Time Vs. Number of Periodic Tasks (FFD Partition Scheme)         | 119     |

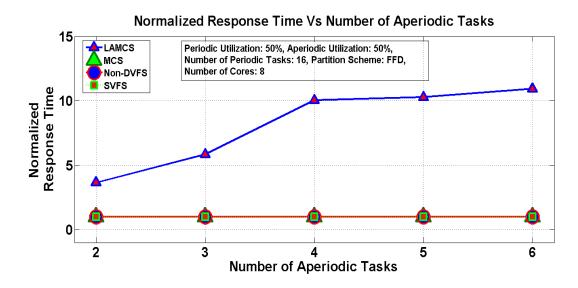

| 4.13       | Normalized Response Time Vs. Number of Aperiodic Tasks (FFD Partition Scheme)        | 120     |

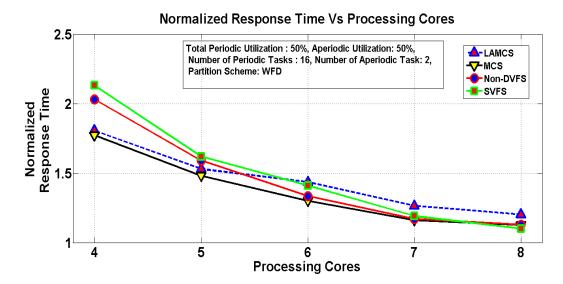

| 4.14       | Normalized Response Time Vs. Processing Cores (WFD Partition Scheme)                 | 120     |

| 4.15       | Normalized Response Time Vs. Processing Cores (FFD Partition Scheme)                 | 121     |

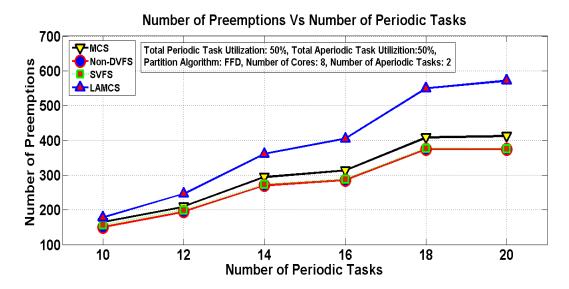

| 4.16       | Number of Preemptions Vs. Number of Periodic Tasks (Partition Scheme: FFD)           | 122     |

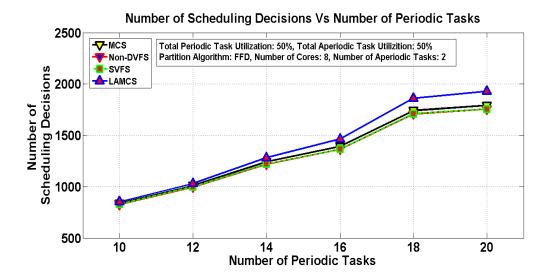

| 4.17       | Number of Scheduling Decisions Vs. Number of Periodic Tasks (Partition Scheme: FFD)  | 122     |

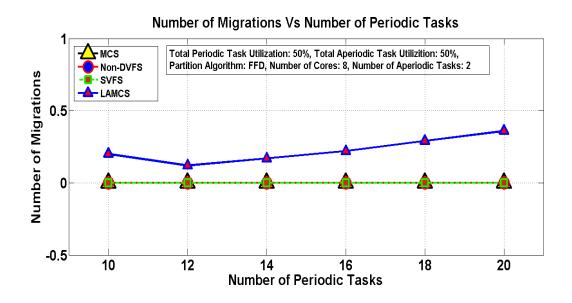

| 4.18       | Number of Aperiodic Migrations Vs. Number of Periodic Tasks (Partition Scheme: FFD)  | 123     |

| 4.19       | Number of Aperiodic Migrations Vs. Number of Aperiodic Tasks (Partition Scheme: FFD) | 123     |

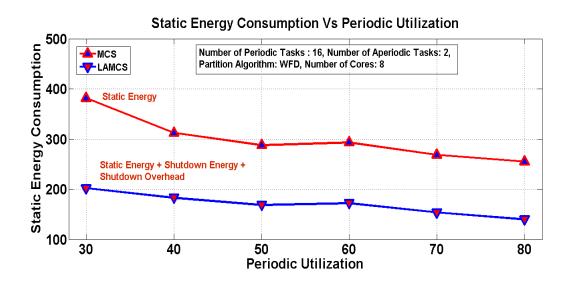

| 4.20       | Static Energy Consumption Vs. Periodic Utilization (Partition Scheme: WFD)           | 125     |

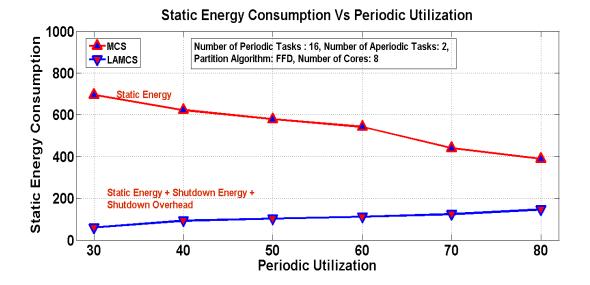

| 4.21       | Static Energy Consumption Vs. Periodic Utilization (Partition Scheme: FFD)           | 125     |

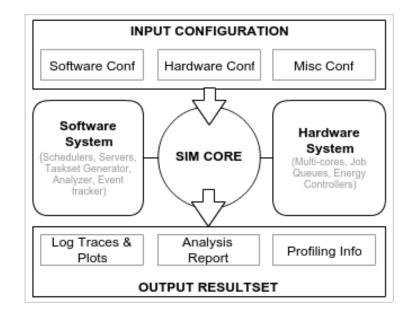

| 5.1        | Abstract Model of STREAM                                                             | 133     |

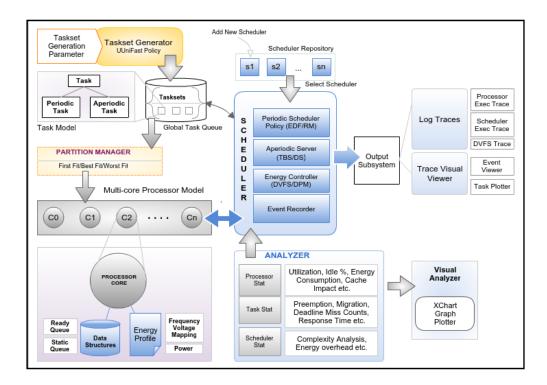

| 5.2        | Architecture of STREAM                                                               | 134     |

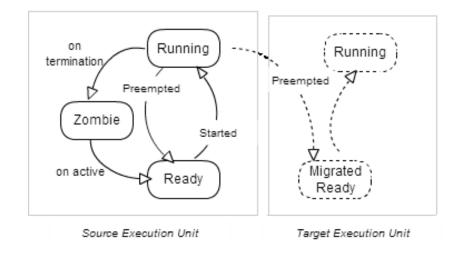

| 5.3        | Task State Transition Diagram                                                        | 135     |

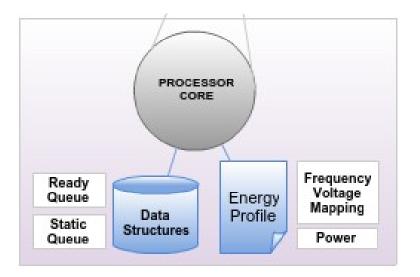

| 5.4        | Processor Entity Diagram                                                             | 136     |

| 5.5        | Task set Generation Flowchart                                                        | 142     |

| 5.6        | A Sample Task Set File                                                               | 143     |

| 5.7        | Class Diagram of Scheduler Module                                                    | 146     |

| 5.8        | A partial snapshot showing scheduler execution log trace                             | 149     |

| 5.9        | A partial snapshot showing parallel per-core execution trace                         | 150     |

| 5.10       | A partial snapshot of DVFS setting log trace                                         | 151     |

| 5.11       | Snapshot showing per-core utilization statistics                                     | 152     |

| 5.12       | Snapshot showing normalized response time values generated by STREAM per task set    | 153     |

| 5.13       | Snapshot showing different decision counts per task set                              | 154     |

| 5.14       | Snapshot showing energy consumption per task set                                     | 155     |

| Figure No. | Caption                                                                     | Page No. |

|------------|-----------------------------------------------------------------------------|----------|

| 5.15       | A line graph showing normalized energy consumption Vs. periodic utilization | 156      |

| A.1        | Snapshot of Main Screen of STREAM                                           | 165      |

| A.2        | Snapshot of a Task Generator                                                | 165      |

| A.3        | Snapshot showing generation of task sets in SCHED VIEWER                    | 166      |

| A.4        | Sample Task Sets File                                                       | 167      |

| A.5        | Scheduler Interface showing selection of input file                         | 168      |

| A.6        | Scheduler Interface showing selection of processor core count               | 169      |

| A.7        | Scheduler Interface showing selection of scheduling algorithm               | 169      |

| A.8        | Scheduler Interface showing selection of Task Allocation                    | 170      |

| A.9        | Scheduler Interface showing selection of Log Trace Mode                     | 170      |

| A.10       | Scheduler Interface showing selection of Analysis Mode                      | 171      |

| A.11       | Scheduler Interface showing Running state of Scheduler                      | 171      |

| A.12       | Scheduler Interface with SCHED VIEWER                                       | 172      |

| A.13       | Scheduler Interface when the execution is finished                          | 172      |

| A.14       | Sample output showing Energy Consumption                                    | 173      |

| A.15       | Sample output showing various Decision Points                               | 173      |

| A.16       | Sample output showing Aperiodic Response Time                               | 174      |

| A.17       | Visual Analyzer showing selection of Analysis Type                          | 174      |

| A.18       | Visual Analyzer showing selection of Output Files                           | 175      |

| A.19       | Visual Analyzer Labeling a line that will appear on the graph               | 175      |

| A.20       | Visual Analyzer showing Graph and the Text File corresponding to that graph | 176      |

### List of Tables

| Table<br>No. | Caption                                                                             | Page<br>No. |

|--------------|-------------------------------------------------------------------------------------|-------------|

| 2.1          | Classification of DVFS techniques and the target uniprocessor scheduling algorithms | 23          |

| 2.2          | Summary of Leakage Aware Uniprocessor Scheduling Algorithms                         | 26          |

| 2.3          | Summary of Energy Efficient Multiprocessor Scheduling Algorithms                    | 32          |

| 2.4          | Summary of Energy Efficient Multi-core Scheduling Algorithms                        | 40          |

| 2.5          | Observations and Research Gaps                                                      | 42          |

| 3.1          | Mixed Task Set (MCS)                                                                | 62          |

| 3.2          | Schedule on Core 0 using Proposed MCS Algorithm                                     | 63          |

| 3.3          | Schedule on Core 1 using Proposed MCS Algorithm                                     | 64          |

| 3.4          | Scheduler Time Constants                                                            | 72          |

| 3.5          | Frequency/Voltage Settings of 70nm Transmeta Crusoe Processor                       | 72          |

| 3.6          | Energy Consumption over a Hyper Period (MCS)                                        | 72          |

| 3.7          | Performance of the Proposed MCS Algorithm                                           | 87          |

| 4.1          | 70nm Technology Constants                                                           | 92          |

| 4.2          | Mixed Task Set (LAMCS)                                                              | 101         |

| 4.3          | Schedule on Core 0 using Proposed LAMCS Algorithm                                   | 102         |

| 4.4          | Schedule on Core 1 using Proposed LAMCS Algorithm                                   | 103         |

| 4.5          | Energy Consumption over a Hyper Period (LAMCS)                                      | 110         |

| 4.6          | Performance of the Proposed LAMCS Algorithm                                         | 126         |

| 5.1          | Summary of Existing Simulators                                                      | 130         |

# List of Algorithms

| <ul> <li>3.1 Proposed EEDVFS Algorithm</li> <li>3.2 Frequency Selection of Proposed EEDVFS Algorithm</li> <li>3.3 Frequency Selection of Proposed MCS Algorithm</li> <li>3.4 Proposed Multi-Core Scheduling Algorithm (MCS)</li> <li>4.1 Frequency Selection of Proposed LAMCS Algorithm</li> <li>4.2 Procrastination Interval Calculation in Proposed LAMCS Algorithm</li> </ul> | Page No. |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <ul> <li>3.3 Frequency Selection of Proposed MCS Algorithm</li> <li>3.4 Proposed Multi-Core Scheduling Algorithm (MCS)</li> <li>4.1 Frequency Selection of Proposed LAMCS Algorithm</li> </ul>                                                                                                                                                                                    | 51       |

| <ul> <li>3.4 Proposed Multi-Core Scheduling Algorithm (MCS)</li> <li>4.1 Frequency Selection of Proposed LAMCS Algorithm</li> </ul>                                                                                                                                                                                                                                               | 52       |

| 4.1 Frequency Selection of Proposed LAMCS Algorithm                                                                                                                                                                                                                                                                                                                               | 61       |

|                                                                                                                                                                                                                                                                                                                                                                                   | 61       |

| 4.2 Procrastination Interval Calculation in Proposed LAMCS Algorithm                                                                                                                                                                                                                                                                                                              | 96       |

|                                                                                                                                                                                                                                                                                                                                                                                   | 97       |

| 4.3 Proposed Leakage Aware Multi-core Scheduling Algorithm (LAMCS)                                                                                                                                                                                                                                                                                                                | 98       |

## Acronyms

| DVFS      | Dynamic Voltage and Frequency Scaling                  |

|-----------|--------------------------------------------------------|

| DPM       | Dynamic Power Management                               |

| wcet      | worst case execution time                              |

| aet       | actual execution time                                  |

| CMOS      | Complementary Metal Oxide Semiconductor                |

| EDF       | Earliest Deadline First                                |

| SNTA      | Stretching to Next Task Arrival                        |

| PBSS      | Priority Based Slack Stealing                          |

| UU        | Utilization Updating                                   |

| ccEDF     | Cycle conserving Earliest Deadline First               |

| laEDF     | Look ahead Earliest Deadline First                     |

| DS        | Deferrable Server                                      |

| SS        | Sporadic Server                                        |

| CBS       | Constant Bandwidth Server                              |

| TBS       | Total Bandwidth Server                                 |

| SNRT      | Stretching to Next Replenishment Time                  |

| BBSS      | Bandwidth Based Slack Stealing                         |

| POSD      | Periodic Only Slack Distribution                       |

| WSE       | Workload based Slack Estimation                        |

| BRS       | Basic Reclamation Scheme                               |

| MRS       | Mutual Reclamation Scheme                              |

| BSS       | Bandwidth Sharing Scheme                               |

| RARA      | Ratio based Aggressive Reclaim Algorithm               |

| EEDVFS    | Energy Efficient Dynamic Voltage and Frequency Scaling |

| GRUB – PA | Greedy Reclamation of Unused Bandwidth - Power Aware   |

| DFSA      | Deadline Based Frequency Scaling Algorithm             |

| LC-EDF    | Leakage Controlled Earliest Deadline First             |

| OWAA      | Optimal Workload Aware Algorithm                       |

| WFD       | Worst Fit Decreasing                                   |

| FFD      | First Fit Decreasing                                                                                 |

|----------|------------------------------------------------------------------------------------------------------|

| BFD      | Best Fit Decreasing                                                                                  |

| AMBFF    | Adaptive Minimal Bound First Fit                                                                     |

| HeLP     | Hetero Efficiency to Logical Processor                                                               |

| HeLP-TM  | Hetero Efficiency to Logical Processor - Temporal Migration                                          |

| GMF      | Growing Minimum Frequency                                                                            |

| LTF      | Largest Task First                                                                                   |

| MCS      | Multi-Core Scheduler                                                                                 |

| LAMCS    | Leakage Aware Multi-Core Scheduler                                                                   |

| SVFS     | Static Voltage and Frequency Scaling                                                                 |

| Non-DVFS | Non- Dynamic Voltage and Frequency Scaling                                                           |

| STREAM   | Simulation Tool for Real time Energy efficient scheduling and Analysis for Multi-<br>core processors |

| PLL      | Phase Locked Loops                                                                                   |

| LLREF    | Largest Local Remaining Execution time First                                                         |

# Chapter 1 Introduction

This chapter provides an introduction to the research work presented in this thesis. It explains the motivation for pursuing this work and describes the research background. In addition, it introduces the research work carried out in this thesis and finally, it presents the organization of the thesis.

#### **1.1 Motivation**

With the rapid growth in technology, the contemporary computing systems available in today's era are shrinking in size and weight, exhibiting high performance and are capable of communicating with each other over the network. This has made embedded systems common place in everyday life. Unlike general purpose systems, embedded systems receive input from different sources through sensors and provide output to different devices through actuators without human intervention. These systems are used in many diverse application areas namely, automated industry applications, automotive applications, avionics, defense applications, consumer electronics etc. Many of the embedded systems are specially made for performing real time tasks where the timing constraints are important. Such systems are known as real time embedded systems. For example, in a missile guided system, the highly critical hard real time tasks like target sensing and track correction require an independent system mounted on the missile to sense the target and correct the path of the missile. If these tasks are not completed in time, the missile may home onto unwanted area and cause disaster (Mall, 2010). The systems which are designed to run such critical applications need powerful processors which are capable of performing intensive computations. These powerful processors consume significant amount of energy. Majority of these real-time embedded systems operate on battery. Therefore, the key design issues of real time embedded systems are energy efficiency and code density as these systems are expected to perform complex functionalities within limited power budget and small memory foot print. In addition, the modern real time embedded systems run applications that are dynamic and

interactive in nature in which it is required to take input from the user while executing time constrained tasks. These interactive tasks, also known as aperiodic tasks, arrive arbitrarily in time and need quick response for good performance. Therefore, the responsiveness of the aperiodic tasks is also an important concern (Shin and Kim, 2006; Brandenburg and Anderson, 2007; Kato and Yamasaki, 2008).

Embedded systems are made up of one or more micro-processors / microcontrollers that are connected via interconnection network. The power supply is nonuniformly distributed over various components of the system which leads to variable power density. The components that are used frequently and do intensive computations consume more power than other components. The areas with more power density generate more heat and result in increase in temperature and may lead to system failure (Tiwari et al., 1996). In addition, heat dissipation becomes more challenging in embedded systems as compared to general purpose systems due to their small size. Therefore, energy optimization is an important issue in order to get longer battery life as well as for keeping the system free from failures.

Majority of the real time embedded systems now-a-days make use of sophisticated applications which require complex software and hardware. This raises the need of powerful processor design. In order to design such processors, the designers are not focusing on miniaturization of single processor since this leads to greater energy consumption and excessive heat dissipation. Instead, there is an increasing trend towards multi-core / multi-processor systems for real time embedded applications (Davis and Burns, 2011).

Realizing the ever increasing demand of high performance multi-core processors in battery operated real time embedded systems, many researchers have concentrated on the energy efficiency of these systems (Yang et al., 2005; Seo et al., 2008; Devdas and Aydin, 2010; Lu and Guo, 2011; Khandhalu et al., 2011; He and Muller, 2012a; Zhao et al., 2013). Efforts have been made to minimize the processor energy consumption at various levels such as architecture level, operating system level, compiler level, application and system program level etc (Saha and Ravindran, 2012). Many solutions have been proposed by hardware and software designers to deal with the problem of energy optimization in embedded systems and researchers are further working in this area.

This thesis addresses the issue of energy consumption of multi-core processor based real time embedded systems at the operating system level with the help of real time task scheduling and various energy optimization techniques. In this thesis, various energy efficient task scheduling algorithms are proposed for the optimization of both dynamic and static energy consumptions on uniprocessor and multi-core platforms. Realizing the importance of aperiodic tasks, all the proposed scheduling algorithms are capable of scheduling mixed task sets containing a mix of periodic and aperiodic tasks.

#### **1.2 Research Background**

The work presented in this thesis concentrates on the issue of energy consumption in multi-core processor based real time embedded systems.

#### **1.2.1 Processor Energy Consumption**

Viredaz and Wallach (2003) have stated that the processor cores consume majority of the energy as compared to other hardware components. The two main components of CMOS processor level energy consumption are static energy component due to leakage current and dynamic energy component due to switching activities (Duarte et al., 2002). There exist various strategies for reducing dynamic energy consumption like clock gating, power gating, transistor sizing, low power logic synthesis, DVFS etc (Benini et al., 1994; Tiwari et al., 1996; Borah et al., 1996; Macii et al., 2008; Li et al., 2011; Kim et al., 2002; Raja et al., 2006; Roy et al., 2003). Most of the modern processors in modern embedded systems are equipped with various levels of discrete voltages and frequencies which allow the execution of tasks at different voltages and frequencies (Burd and Brodersen, 1995). Such processors are named as DVFS enabled processors. By exploiting the DVFS feature, various energy efficient operating system scheduling algorithms were proposed for uniprocessor and multi-core platforms (Shin et al., 2001; Kim et al., 2002; Pillai and Shin, 2001; Shin and Kim, 2006; Chin, 2013; Seo et al., 2008; Devdas and Aydin, 2010; Lu and Guo, 2011; Khandhalu et al., 2011).

Another component of processor energy consumption is the static energy consumption which is present even when no logic operations are performed. The CMOS circuit technology is well known for its low static energy consumption. At the same time, there is a constant need of high performance and higher transistor density resulting in a continuous decrease in device dimensions in each technology generation (Borkar, 1999). As a result, there is constant electric field scaling which needs proportionate reduction in supply voltage. The reduction in supply voltage requires proportionate decrease in threshold voltage to maintain the desired gate delay. This leads to exponential increase in sub-threshold leakage current thereby giving rise to a significant amount of static energy consumption (Jejurikar et al., 2004). Dynamic Power Management (DPM) mechanisms like dynamic shutdown and procrastination can be used to reduce static energy consumption. DPM puts the processor in shut down mode whenever possible. The limitation of DPM is that it suffers from an overhead of mode switching which causes additional energy and latency penalty (Lee et al., 2003; Jejurikar et al., 2004; Niu and Quan, 2004; Chen and Kuo, 2007). Therefore, the processor is always turned to sleep mode whenever the idle interval is sufficiently larger than a certain threshold time duration called the breakeven time.

#### **1.2.2 Hardware Platform**

Due to increasing demand of higher processor performance and growing capacity for number of transistors after every 18 to 24 months as stated in Moore's law, processor designers focused on the circuit miniaturization to increase the clock frequency. But this has led to the problem of high energy consumption and excessive heat dissipation. For example, Intel canceled the launch of processor named Tejas in 2004 which was the successor of the Pentium P4 processor, due to its extremely high energy consumption. The problem of high energy consumption cannot be completely addressed by scaling the voltage and frequency alone as this would limit the maximum task execution frequency thereby restricting the performance. Therefore, in addition to DVFS, the solution to this problem also requires to use multiple cores on a single chip which can take better advantage of increasing transistor capacity and can achieve better performance by exploiting parallelism. In 2007, Intel released the first Core 2 Duo processor. Since then, there has been a paradigm shift towards the multi-core processors (Davis and Burns, 2011).

#### **1.2.2.1 Classification of Multi-core Processors**

With respect to the task scheduling, the multi-core processor platforms can be classified into three categories (Davis and Burns, 2011):

(1) *Homogeneous:* The processor cores are identical where the maximum operating frequency of all the processor cores is same.

(2) *Uniform:* The processor cores differ in their maximum operating frequency but it follows the same instruction set architecture (ISA). i.e., a task which executes at a speed of x on one core may execute at a speed of 2x on another core.

(3) *Heterogeneous:* The processor cores have different hardware configurations, frequencies, ISAs, private caches etc. The processor cores will not have inter-operability in executing tasks.

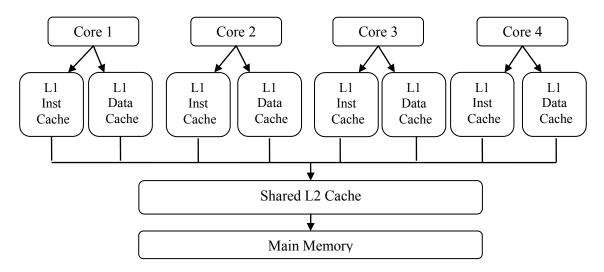

#### 1.2.2.2 Memory Architecture

Memory architecture is an important aspect of any processor platform as it is one of the most energy consuming parts. Memory architecture is also vital for designing task scheduling algorithms on multi-core platforms which has private and shared spaces. The two main categories of memory architecture are distributed and shared memory architecture (Stallings, 2014). In distributed memory architecture, each core maintains its own local queue and as a consequence, a processor cannot directly access the data/instructions stored on another core. On the other hand, in shared memory architecture, as all the cores have access to a central shared memory space, any processor core can access the data/instructions belonging to the task of any other processor core.

The memory architecture has a direct impact on the latency of task migration from one core to another (Schirmeister, 2007). In distributed memory architecture, as each core maintains its own local memory, if a task is required to be migrated from one core to another, it has to transfer the entire task context including instructions and data to another core. This transition is costly in terms of time consumption. In shared memory architecture, the instructions and data of all the tasks are stored in a central memory and are therefore available to all the cores. But serving the read/write requests of all the tasks simultaneously is time consuming. Moreover, the size of central shared memory should be much larger than the local memories in distributed memory architecture as it has to store the instructions and data of all the tasks. This may lead to slower memory access. Thus a single central memory in shared memory architecture lowers the overall system performance and is not scalable with increase in number of processor cores.

In order to overcome the limitations of single central memory in shared memory architecture, modern processors make use of *hierarchical memory* architecture (Schirmeister, 2007). In this architecture, levels of small and fast local memories called *caches* are placed between processor and central memory. This type of memory organization helps to reduce the memory access latency. The instructions and data of the running task are stored in cache memory resulting in higher availability of data/instructions at any time instance provided the task has not migrated to another core. Since the cache memories are small and cannot store all the instructions and data corresponding to a running task, the requested data/instruction which is not present in cache memory.

In modern processors, there are multiple levels of cache memories. Level 1 cache (L1) is the smallest and fastest private cache which is nearest to the processor. Level 2 cache is bigger and slower than L1 cache. It may be private or shared amongst the cores. Both L1 and L2 are generally made up of SRAM. Level 3 cache (L3) is usually made up of SRAM and DRAM. It is larger and slower than L2 cache and it may be placed on or off the chip. Hence, as the read/write request goes down the memory hierarchy, it takes more time to transfer the data from/to the processor.

In hierarchical memory architecture with one or two levels of cache as local to the core, the transfer of task context in case of migration is time consuming. Additional time is required for reloading the data at the target core from the shared higher level cache or from the shared central memory and invalidating the data in present core. Thus, in both types of the memory architectures, migration of a task incurs significant overhead because of the memory access latency. In case of task preemption, the data / instructions of a new higher priority task gets loaded into all levels of cache memories. When the previous task resumes, its context may not exist in cache which results in increasing execution time of the task. Both preemption and migration of a task result in overhead which may affect the performance of the system. The proposed scheduling algorithms

assume shared memory architecture with multiple levels of cache memories as shown in figure 1.

**Figure 1.1: Hierarchical Memory Architecture**

#### 1.2.3 Real Time Task Model

In real time systems, the unit of work which is executed by the processor is known as *job* and the set of related jobs is called a *task*. The real time applications are composed of real time tasks. These tasks are executed under timing constraints. The real time constraints (or deadlines) are defined as either hard or soft based on the functional criticality of the tasks, usefulness of late results and deterministic and probabilities nature of the constraints. The distinction between hard and soft timing constraints is quantitatively stated as a function of *tardiness* of a job. The tardiness of a job measures the lateness of that job with respect to its deadline. The tardiness is zero if a job completes its execution on or before its deadline. If a job is late, its tardiness is the difference between the completion time and its deadline. A job with hard deadline falls abruptly and may even cause disaster if the tardiness of such jobs is greater than zero. On the other hand, the usefulness of the result produced by a soft deadline job decreases with increase in tardiness. Other attributes of a real time task are release time; period/interrelease time and worst case execution time (*wcet*). *Release time* is the time at which the job is available for execution and *period/inter-release time* is the time when next job of the task is released. wcet is the maximum amount of time required to complete the execution of the job. It mainly depends on the complexity of the job and speed of the

processor. Since real time systems are deterministic in nature, the *wcet* of a task is known in prior through analysis and measurement but the actual execution time (*aet*) is not known. The *wcet* of a job is directly impacted by the structure of the program, type of processor, processor platform, memory architecture, communication network and the input data. The *worst case utilization* of a task is defined as the ratio of *wcet* and period of that task. It tells the percentage of processor time the task requires for its successful execution. The *total utilization* of a task set is the sum of utilizations of tasks in the task set. It is used for determining the schedulability of the task set. *Hyper period (H)* of a task set is defined as the least common multiple (LCM) of the periods of all the tasks in the task set. The number of jobs produced by the periodic tasks in each hyper period is equal to  $\sum_{i=1}^{n} H/p_i$  where *n* is the number of tasks in a task set and  $p_i$  is the period of i<sup>th</sup> task (Liu, 2008).

There exist three types of real time tasks: (1) Periodic tasks (2) Aperiodic tasks and (3) Sporadic tasks. The *periodic tasks* are the tasks whose jobs arrive at regular intervals and they have hard deadlines. For example, in a radar system, a task of transmitting/receiving the radio signals for object detection is a periodic task. As discussed earlier, the real time system is required to respond to external events that arrive arbitrarily in the periodic task system; these external events are modeled using aperiodic and sporadic jobs whose release times are not known apriori. A task is aperiodic if its jobs have either soft deadlines or no deadlines. The task which adjusts the sensitivity setting of the radar surveillance system is an example of aperiodic task. Even though, these tasks have no deadlines, there late response is annoying. Hence, it is important to optimize the responsiveness of the aperiodic jobs but never at the expense of hard deadline periodic jobs. In contrast, the tasks that arrive arbitrarily but have hard deadlines are called sporadic tasks (Liu, 2008). For example, in an automatically controlled train, if the task of applying brakes for stopping the train is not done as soon as the command to do so is made, it may cause disaster. In this case, the command to apply the brake is a sporadic job which arrives arbitrarily but has hard deadline.

In this thesis, the proposed energy efficient scheduling algorithms schedule mixed task sets that contain periodic and aperiodic tasks. These scheduling algorithms optimize energy consumption along with achieving good response time of aperiodic tasks without missing the deadlines of periodic tasks.

#### 1.2.4 Energy Efficient Real Time Task Scheduling

The energy efficient task scheduling can be implemented for processors that are equipped with discrete frequency and voltage settings and are capable of modifying the frequency and voltage dynamically at run time. The majority of the modern embedded systems use such processors (Chen and Kuo, 2007).

DVFS is an effective way of reducing the dynamic energy consumption of low power embedded systems (Kim et al., 2002). It adjusts the supply voltage and corresponding clock frequency of the processor dynamically without affecting the performance of the system. Since the energy consumption of CMOS based processor has quadratic dependence on supply voltage, lowering the supply voltage effectively reduces the energy consumption. Therefore, DVFS is popularly used to reduce the processor level energy consumption of the real time embedded systems (Chen and Kuo, 2007). It is integrated with the real time task scheduling where at each scheduling decision point, the frequency and voltage of the processor is decided. Such task scheduling algorithms are called DVFS based energy efficient task scheduling algorithms.

There exists another technique known as dynamic power management (DPM) for reducing static energy consumption (Jejurikar et al., 2004). Static energy dissipation takes place for all the time except when processor is in shutdown state. According to DPM technique, the processor can be dynamically shutdown when it is in idle state. However, putting the processor in shutdown state and then waking it up incurs some overhead because the processor loses temporal data stored in various forms of memory such as registers, caches, TLBs etc. Thus, before shutting down, all registers must be saved and dirty cache lines must be written back to the memory and upon wake up, all the saved data must be retrieved back to registers, cache lines etc. This results in additional memory accesses and hence additional energy consumption. In order to decide whether to shut the processor down or not, idle threshold interval is computed based on the idle state energy consumption and shutdown overhead. If the idle interval is less than the threshold, then it is not energy efficient to shutdown the processor.

#### **1.3 Research Objectives**

The aim of this research is to design and develop an energy efficient real time task scheduling framework for mixed task model containing a mix of hard and soft real time tasks on homogeneous multi-core processor platform. In order to achieve the aim of this research work, the following objectives were planned:

- Design and implementation of energy efficient real time scheduling algorithms for mixed task sets on uniprocessor platform.

- Design and implementation of energy efficient real time scheduling algorithm for dynamic energy optimization considering multi-core processor platform and mixed task sets.

- Design and implementation of a real time scheduling algorithm for the overall energy optimization which includes both static and dynamic energy consumed by multi-core processor for mixed task sets.

#### **1.4 Methodology**

The objectives defined in the previous section are achieved by the accomplishment of the following:

- 1. Study and analysis of the existing energy efficient real time scheduling algorithms for uniprocessor as well as multi-core/multi-processor platforms.

- 2. Generation of synthetic task sets containing both periodic and aperiodic tasks for various utilizations, number of tasks and hyper periods.

- 3. Design, implementation, validation and analysis of energy efficient scheduling algorithms for uniprocessor platform.

- 4. Design, implementation, validation and analysis of scheduling algorithm for multi-core platform.

- 5. Design, implementation, validation and analysis of scheduling algorithm for dynamic energy optimization for multi-core platform.

- Design, implementation, validation and analysis of a scheduling algorithm for the overall energy optimization which includes both dynamic and static energy for multi-core platform.

- 7. Design and development of a full-fledged software tool which includes the implementation of basic real time scheduling policies, existing energy efficient

scheduling policies, the scheduling algorithms proposed during the thesis work and the task set generation algorithm.

#### **1.5 Thesis Organization**

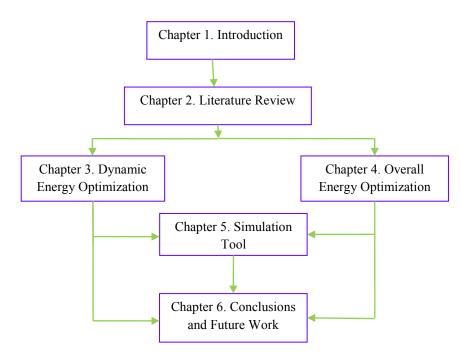

The structure of the thesis is illustrated in figure 1.2. This thesis is composed of six chapters.

Figure 1.2: Thesis Organization Roadmap

**Chapter 2** provides an overview of on-going research directions in energy aware task scheduling for uniprocessor, multi-core and multi-processor platforms. It reflects the diversity of the issue involved in making the task scheduling energy efficient. It discusses the fundamental study of energy optimization techniques, structure and function of multi-core processors etc that are necessary in this research work. Together, it provides a comprehensive overview of the existing literature and open issues to provide foundation for this research work.

**Chapter 3** presents the scheduling algorithms developed for reducing dynamic energy. It describes the DVFS based scheduling algorithms for mixed task set for uniprocessor and multi-core platforms. The algorithms discussed in this chapter are able to reduce dynamic energy consumption of the processor by meeting all the hard deadlines

of the periodic tasks and ensuring early response times of aperiodic tasks. But these algorithms do not take care of reducing the static energy consumption that exists in processor's idle state.

**Chapter 4** further extends the algorithms described in chapter 3 by reducing the static energy consumption along with the dynamic energy consumption. It integrates DPM and procrastination techniques with DVFS technique to reduce the overall energy consumption. The results and analysis show that there is further reduction in processor energy consumption. The hard deadline of periodic tasks and responsiveness of aperiodic tasks are taken care in addition to reduction in overall energy consumption.

**Chapter 5** illustrates the details of design and implementation of the software simulation tool called "STREAM". STREAM stands for "Simulation Tool for Real time Energy efficient scheduling and Analysis for Multi-core processors". It provides the indepth explanation of the architecture of the simulation tool, implementation of various scheduling algorithms and various other novel aspects that are implemented in STRAEM which are missing in other existing scheduler simulators.

**Chapter 6** concludes the thesis by discussing the overall contribution of the research in the context of the related work in this area. In addition, it discusses limitations of the work and points to future research directions.

# Chapter 2 Literature Review

This chapter provides an overview of previous research work on energy efficient real time scheduling algorithms. It introduces a variety of energy efficient scheduling algorithms existing in the literature on uniprocessor, multi-core and multiprocessor platforms. The real time task models considered in this literature review are periodic task model and mixed task model where periodic and aperiodic tasks are scheduled together. The main focus of the research described in this thesis is the energy efficient real time scheduling algorithms for mixed task model on multi-core platform.

#### **2.1 Introduction**

In the last decade, we have witnessed a paradigm shift in the embedded systems domain. The growing demand of portable and battery operated high performance embedded devices has essentially motivated the researchers to concentrate on two important aspects: energy optimization and multi-core processors.

The problem of energy consumption has been addressed at various levels architecture level, operating system level, compiler level, application program level and system program level (Saha and Ravindran, 2012). At the architecture level, energy consumption can be reduced by improving instruction set architecture, optimizing the memory subsystem and by managing I/O operations more efficiently. At the operating system level, energy consumption can be reduced by improving various aspects of operating systems such as task scheduling, inter-process communication, paging systems etc. Similarly, the energy consumed by application and system programs can be reduced by efficient use of data structures and by optimizing the programs using compilers.

Another major change in hardware design that can help in reducing energy consumption is the parallel execution of tasks on multiple cores rather than executing them sequentially on one processor at a very high speed. This is possible due to increasing growth of number of transistors on a fixed die size. The hardware designers realized that increasing the complexity of the hardware increases the performance at the cost of high energy consumption. Therefore, the trend has changed towards utilizing large number of transistors for constructing multiple cores/processors on a fixed die size thereby exploiting parallelism and reducing energy consumption.

In this chapter, we focus on energy saving mechanisms handled at the operating system level (particularly by using real time task scheduling) on uniprocessor, multi-core and multiprocessor platforms.

#### 2.2 Background

We present the research carried out in the area of energy aware real time scheduling in last two decades. The literature can be classified on the basis of the different processor platforms and the type of energy that is targeted for optimization. Early research in late 1990's focused on energy optimization for uniprocessor platform. Later, after year 2000, majority of the research in energy aware real time scheduling focused on multi-processor platform. In recent time (after year 2008 till now), researchers are working on different issues revolving around energy optimization on multi-core platform.

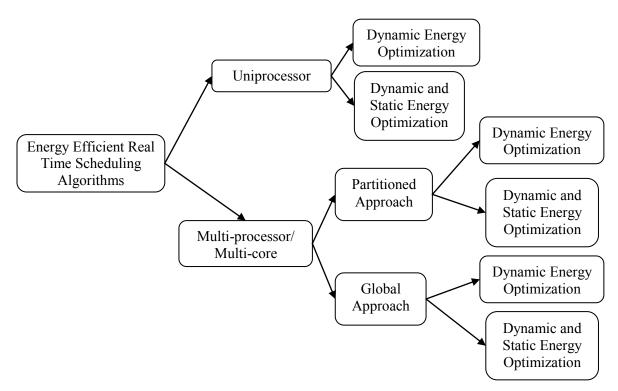

#### 2.2.1 Classification of Energy Aware Scheduling

Irrespective of the processor platforms, the existing research can be classified into two broad categories based on whether the scheduling techniques focus on reduction of dynamic energy consumption alone or on both dynamic and static energy consumption. Figure 2.1 shows taxonomy of the literature discussed in this chapter.

#### 2.2.2 Dynamic Energy Optimization

The tradeoff between performance and energy consumption can be addressed using energy optimization technique called DVFS. DVFS reduces dynamic energy consumption without hampering the performance of real time application. It is based on two important aspects:

• The modern CMOS based processors are equipped with multiple discrete voltage and frequency levels and are capable of varying operating frequency and supply voltage dynamically.

Figure 2.1: Taxonomy of Energy Aware Real Time Scheduling

• In majority of applications, high performance (or high frequency/speed) is required only for small fraction of time while rest of the time we can have low performance (or low frequency/speed).

DVFS technique works on the idea of varying operating frequency of processor which in turn varies supply voltage (Weiser et al., 1994). It lowers the frequency when the processor load (or utilization) is low and increases the frequency when the processor load (or utilization) increases. It exploits the fact that *aet* is most of the time less than or equal to *wcet* of a task. The difference between *wcet* and *aet* is called slack time. This available slack time is used for slowing down the processor to save energy. Since energy consumed per cycle with CMOS circuitry scales quadratically with the supply voltage, DVFS potentially reduces the processor energy consumption through voltage and frequency scaling. In order to decide, when to execute at higher frequency and when at lower frequency, it requires the cooperation of operating system scheduler with voltage and frequency selection circuit. Therefore, DVFS technique is always applied in coordination with operating system scheduler. When DVFS techniques are applied to submicron or deep submicron regimes, it leads to increase in static energy consumption, resulting in increase of total energy consumption (Lee et al., 2003; Jejurikar and Gupta, 2004). This is because, slowing down the processor execution beyond certain frequency increases leakage current which leads to increase in static energy consumption and thus increases total energy consumption. The operating frequency below which static energy consumption dominates dynamic energy consumption resulting in increase in total energy consumption is called *critical speed* (Jejurikar et al., 2004). Thus, DVFS technique is more energy efficient if it does not scale down below critical speed. If we assume that normalized operating frequency lies within a range of 0 to 1, then the critical slow down factor ( $\eta_{crit}$ ) can be defined as ratio of critical speed (or frequency) to maximum operating frequency. If slow down factor ( $\eta_i$ ) computed by any DVFS technique is less than  $\eta_{crit}$  then the computed slow down factor is raised to  $\eta_{crit}$  to save static energy consumption.

In real time embedded systems, the real time tasks should be executed under timing constraints. These tasks have hard or soft deadlines before which they should finish execution. Application of DVFS techniques on real time scheduling algorithm is challenging because slowing down the processor speed should not cause a task to miss the deadline.

#### 2.2.3 Overall Energy Optimization

DVFS limits energy optimization below critical speed due to the dominance of static energy consumption. In order to overcome this limit and reduce static energy consumption, shutting down the processor when it has enough idle time is proposed (also known as DPM mechanism) (Lee et al., 2003; Jejurikar and Gupta, 2004). As shutting down the processor during idle period may incur overhead, it is required to set a threshold called break even time to decide whether it is energy efficient to shutdown or not. For example, the breakeven time of a 70nm Transmeta Crusoe processor is 2 msec (Jejurikar and Gupta, 2004). In order to stretch the idle period to reduce the number of short shutdown intervals and also to reduce the shutdown overhead, a technique called procrastination can be used (Lee et al., 2003; Jejurikar et al., 2004) which delays the execution of jobs that arrive during idle period to increase the span of idle interval. In this

way, overall energy optimization can be achieved by the combination of slowdown, shutdown and procrastination techniques.

Identification of idle and procrastination intervals require the cooperation of operating system scheduling algorithm. Thus, both DVFS and DPM with procrastination techniques require the cooperation of scheduling algorithm. Both types of techniques are applied on real time scheduling algorithms to minimize the overall energy consumption of real time embedded systems.

#### 2.3 Scheduling Algorithms for Uniprocessor Platform