## **Reconfigurable Architecture in Resistive Switching Crossbar**

## THESIS

Submitted in partial fulfilment

of the requirements for the degree of

### **DOCTOR OF PHILOSOPHY**

by

### MANE PRAVIN SAKHARAM

Under the Supervision of

## Dr. Ramesha C. K.

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

#### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

## CERTIFICATE

This is to certify that the thesis entitled **Reconfigurable Architecture in Resistive Switching Crossbar** which is submitted by **Mane Pravin Sakharam** ID No **2009PHXF420G** for award of Ph.D. of the Institute embodies original work done by him under my supervision.

Signature of the Supervisor: Name in capital block letters : DR. RAMESHA C. K. Designation : ASSISTANT PROFESSOR Department of Electrical & Electronics Engineering Date :

## **Declaration**

I, Mane Pravin Sakharam, hereby declare that this thesis entitled "Reconfigurable Architecture in Resistive Switching Crossbar" submitted by me under the guidance and supervision of Dr. Ramesha C. K. is a bonafide research work. I also declare that it has not been submitted previously in part or in full to this University or any other University or Institution for award of any degree.

Signature of the Student:

Ruif

Name of the student : MANE PRAVIN SAKHARAM

Reg. No.: 2009PHXF420G

Date : 10.08.2016

## Abstract

Major reasons behind inferior performance of FPGA over ASIC in terms of delay, area and power consumption are extensive use of SRAM and programmable interconnects. In order to improve the performance gap between ASIC and FPGA so as to increase the share of FPGAs in the market, new emerging devices are being investigated as a replacement for SRAM and programmable interconnection switches. Memristor is one of the most attractive device which can act as nonvolatile memory (by storing data in the form of resistance) and as logic (switching) element. But it is passive device and CMOS circuits are required to implement functions using it.

Out of the available models, VTEAM model found to be more simple, accurate and flexible, and hence used in the work carried out in this research. Stateful NOR, an universal logic gate, can be implemented with memristors. Memristors are seldom used as standalone devices and are fabricated in the form of crossbar over CMOS layer using nanoimprint lithography. Implementation of stateful NOR gate on memristive crossbar requires write, evaluate (imply) and read operations, but memristors can not be isolated from crossbar for these operations.

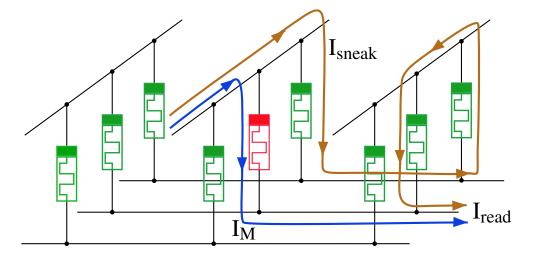

Memristive crossbar arrays are analyzed for write and evaluate (imply) operations in order to find the effect of them on contents of memristors of crossbar that are not part of logic and limitations on the size of crossbar to keep them unaltered. Sneak path problem is common in such crossbar and analysis of read operation has confirmed that the size of crossbar has to be restricted in order to read the state of memristor correctly. Specialized memristive architectures which logically restricts the size of crossbar array are also investigated for use in implementation of NOR operation.

Crossbar array made up of Complementary Resistive Switches (CRSs) are free from sneak path problem. Novel stateful NOR operation with CRSs using a single voltage source is proposed in this work. The analysis of write, read and evaluate (NOR) operations on CRS crossbar to implement stateful NOR gate is carried out in order to find the effect of such operations on CRS cells that are not involved in operation. The integrity of such cells can be maintained in CRS crossbar by size restriction on crossbar and self-resetting read scheme.

Memristive/CRS crossbar based 3-input pipelined reconfigurable logic block architecture has been proposed in this work for implementation of logic functions. For logic function with more than three inputs, the multiplexing of proposed 3-input logic blocks for its implementation is explained.

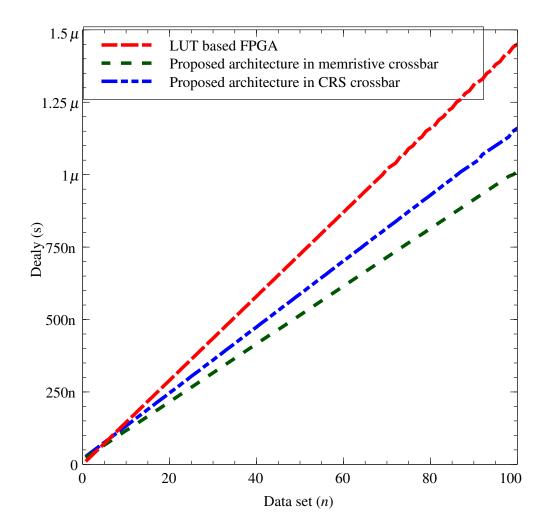

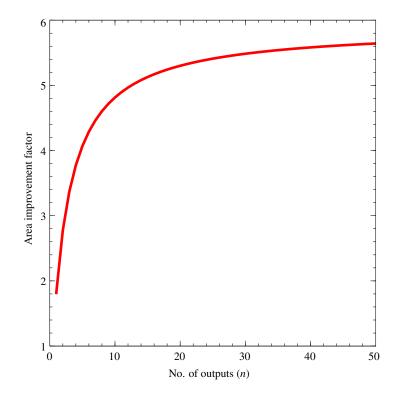

Automation algorithm for proposed 3-input logic block architecture and its multiplexing are also presented.

CRS crossbar is the most natural choice for implementation of proposed architecture as it is free from sneak path problem. The performance analysis of implementation of proposed architecture on memristive and CRS crossbar is carried out with respect to delay, power and area, and is compared with performance of LUT based CLB architecture used in many commercial FPGAs. For array size of  $128 \times 128$ , memristive crossbar implementation has shown 1.45 times improvement in delay for large data set, 2.68 times improvement in power while CRS crossbar implementation has shown 1.28 times improvement in delay (for large data set), 2.04 times improvement in power, over LUT based CLB architecture. For area, this improvement is from 1.8 times to 5.6 times in both type of crossbars.

## Acknowledgment

I would like to express my sincere gratitude to my supervisor and mentor Dr. Ramesha C. K. for the continuous support in conducting this research, for his patience and motivation. He had whole heartedly helped me in this endeavor at all stages of this work. His guidance helped me in all the time of research and writing of this thesis. From bottom of my heart, I extend my sincere thanks to him for all his efforts and help at various levels without which this work not have been completed.

I am very grateful to members of my Doctoral Advisory Committee for thesis mentorship and guidance, Prof K. R. Anupama and Dr. Narayan Manjarekar for sparing their valuable time in reviewing my thesis and giving constructive suggestions to improve it. Their valuable suggestions have helped in greatly enhancing the quality of the thesis.

I would extend my sincere thanks to Prof. M.K. Deshmukh, Professor and Head, Dept.of EEE for his constant support and encouragement at various levels.

I thank Prof. Sauvik Bhattacharya Vice-Chancellor, BITS Pilani, Prof. Sasikumar Punnekkat, Director, BITS Pilani-K. K. Birla Goa Campus, Prof. K. E. Raman, Former Director, BITS Pilani-K. K. Birla Goa Campus, Prof. Ashoke Kumar Sarkar, Director, BITS Pilani - Pilani Campus, Prof. G. Raghurama, Former Director, BITS Pilani - Pilani Campus, Prof. S. K. Verma, Dean, ARD, BITS Pilani - Pilani Campus, Prof. Prasanta Kumar Das, Associate Dean, ARD, Prof. Sunil Bhand, Dean, SRCD, Prof. D. M. Kulkarni, Dean, Administration, BITS, Pilani - K. K. Birla Goa Campus, and Prof. S. D. Manjare for giving me an opportunity to carry out research studies at the institute and also by providing necessary infrastructure and facilities to carry out my work.

I would extend my sincere thanks to Prof. V.K. Deshpande, former-Head, Dept.of EEE for his constant support at various levels.

I also extend my sincere thanks to Dr. Nitin Sharma, DRC Convener, for support and motivation.

I also thank Prof. Dipankar Pal, Dr. Amalin Prince, Dr. Gautam Bacher, Dr. Anita Agrawal, Dr. Chandram, Mr. C. Balakrishna Moorthy, Mr.Meghanand Bhamare, Mr. Sarang Dhongdi, Mr. Sankhar Reddy, Ms. Meetha Shenoy for their constant support, motivation and suggestions.

I acknowledge with due gratitude to Mr. Nishil Talati, Ameya Riswadkar, Mr. Ramesh Raghu, Mr. Sudeep Mishra, Mr. Ravish Deliwala, Mr. Vikas Khairnar, Mr. Abhishek Joshi for their constant support and motivation.

I would extend my sincere thanks to Mr.Pusharaj Paradkar, Mr. Sameer Chodankar, Mr. Anil Lamani and Mr.Shivaraj Rathod, lab technicians for their constant help during my research work carried out in the lab.

I acknowledge all my colleagues for their continuous support, encouragement and motivation.

I would like to express my sincere gratitude to my loving parents Mr. Sakharam Mane and Mrs. Ratnamala Mane, for always believing in me, for their continuous support, encouragement, motivation and prayers.

I thank my wife Mrs. Swati for taking responsibilities of family on my behalf and giving encouragement in carrying out work. I thank my beloved son, Pratyush Mane. Without their support, I could not have made it here.

I thank my family members Mrs. Prabhavati Jagtap, Mrs. Suvarna Patil, Ms. Shrutika Shinde, Mrs. Pooja Sawant, Mrs. Shradha Dalvi, Ms. Tirtha, Ms. Shreya and all other members for their pertinence and patience during this research. They deserve special thanks for their continuous encouragement and motivation.

I am thankful to all my friends and relatives who directly or indirectly helped me in completing my thesis.

Above all, my gratitude towards the almighty that worshiped me with blessings and mercy.

Mane Pravin Sakharam

# Contents

| Cer              | ificate                   | i                               |

|------------------|---------------------------|---------------------------------|

| Dec              | aration                   | ii                              |

| Abs              | ract                      | iii                             |

| Ack              | nowledgment               | v                               |

| Con              | tents                     | vii                             |

| List             | of Figures                | xi                              |

| List             | of Tables                 | xiv                             |

| Abb              | reviations                | XV                              |

| Sym              | bols x                    | vii                             |

| 1<br>1<br>1<br>1 | ntroduction.1Introduction | 1<br>1<br>2<br>5<br>7<br>8<br>9 |

| 4                | .1 Introduction           | <b>11</b><br>11<br>12           |

|   | 2.3   | Summary                                                 | 20        |

|---|-------|---------------------------------------------------------|-----------|

| 3 | Intro | oduction to Memristor                                   | 22        |

|   | 3.1   | Introduction                                            | 22        |

|   | 3.2   |                                                         | 22        |

|   | 3.3   | Memristor Models and Window Functions                   | 26        |

|   |       |                                                         | 29        |

|   |       |                                                         | 31        |

|   | 3.4   | 5                                                       | 33        |

|   | 5.1   | 8                                                       | 34        |

|   |       | I B B B B B B B B B B B B B B B B B B B                 | 36        |

|   |       |                                                         | 37        |

|   | 3.5   |                                                         | 38        |

|   | 3.6   |                                                         | 38        |

|   | 5.0   | Summary                                                 | 50        |

| 4 | 0     | r · · · · · · · · · · · · · · · · · · ·                 | 40        |

|   | 4.1   |                                                         | 40        |

|   | 4.2   | 5                                                       | 42        |

|   | 4.3   |                                                         | 42        |

|   | 4.4   | Analysis of Operations on Memristive Crossbar           | 44        |

|   |       | 4.4.1 Write Operation                                   | 45        |

|   |       | 4.4.1.1 Floating Write Scheme                           | 45        |

|   |       | 4.4.1.2 1/3 Write Scheme                                | 50        |

|   |       | 4.4.2 Read Operation                                    | 52        |

|   |       | 4.4.3 Evaluate Operation (Stateful-NOR Operation)       | 53        |

|   | 4.5   | Logic Implementation on Specialized Memristive Crossbar | 65        |

|   | 4.6   |                                                         | 68        |

| 5 | Logi  | c Implementation on CRS Crossbar Array                  | 70        |

| J | 0     | · ·                                                     | 70        |

|   | 5.2   |                                                         | 71        |

|   | 5.3   |                                                         | 73        |

|   | 5.4   | 6                                                       | , 3<br>80 |

|   | 5.4   |                                                         | 80<br>81  |

|   |       | 1                                                       | 81        |

|   |       | ε                                                       | 81<br>85  |

|   |       |                                                         | 83<br>87  |

|   |       | C                                                       |           |

|   |       | 1                                                       | 92        |

|   |       |                                                         | 93        |

|   |       | 8                                                       | 96        |

|   |       | 1                                                       | 99        |

|   | 5.5   | Summary                                                 | 05        |

| 6 | Reco  | onfigurable Architecture 10                             | 08        |

|   | 6.1   | Introduction                                            | 08        |

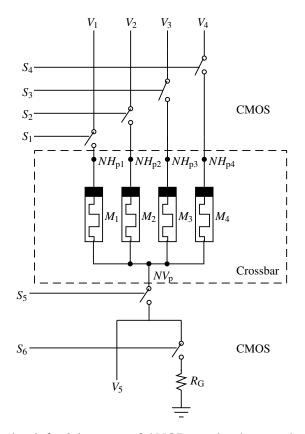

|   | 6.2  | Common Circuit Blocks in CMOS Layer                                                  | 109    |

|---|------|--------------------------------------------------------------------------------------|--------|

|   |      | 6.2.1 Write Circuit                                                                  | 109    |

|   |      | 6.2.2 Evaluate Circuit                                                               | 109    |

|   |      | 6.2.3 Read Circuit                                                                   | 110    |

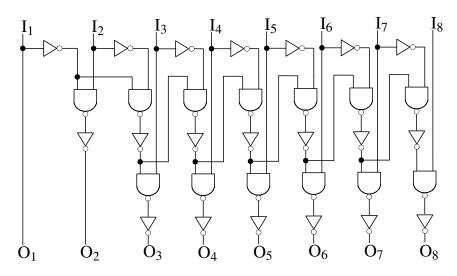

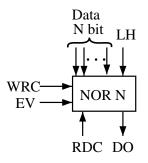

|   |      | 6.2.4 Priority Logic                                                                 | 112    |

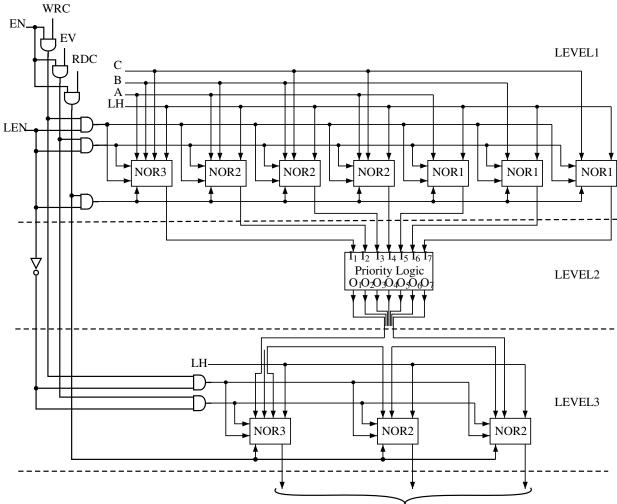

|   | 6.3  | Reconfigurable Architecture using Stateful NOR                                       | 112    |

|   |      | 6.3.1 Architecture Description                                                       | 114    |

|   |      | 6.3.2 Automation Algorithm for 3-input Logic Block Architecture                      | 117    |

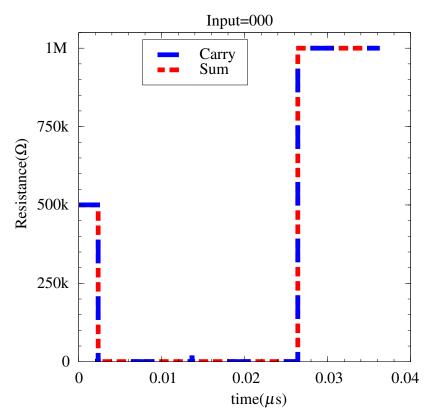

|   |      | 6.3.3 Simulation of 3-input Function using Proposed Architecture                     | 118    |

|   | 6.4  | <i>n</i> -Input Function Implementation                                              | 120    |

|   | 011  | 6.4.1 Automation Algorithm for Generalized Architecture for <i>n</i> -Input Function | 120    |

|   |      | Implementation                                                                       | 125    |

|   | 6.5  | Summary                                                                              | 129    |

|   | 0.0  | Summary                                                                              | 127    |

| 7 | Perf | ormance Analysis                                                                     | 131    |

|   | 7.1  | Introduction                                                                         | 131    |

|   | 7.2  | Timing Analysis                                                                      | 131    |

|   | 7.3  | Power Analysis                                                                       | 138    |

|   | 7.4  | Area Analysis                                                                        | 140    |

|   | 7.5  | Summary                                                                              | 144    |

|   | ,    | 2 mining 9                                                                           |        |

| 8 | Sum  | mary and Future Scope of Work                                                        | 146    |

|   | 8.1  | Summary                                                                              | 146    |

|   | 8.2  | Scope for future work                                                                | 150    |

|   |      |                                                                                      |        |

|   |      |                                                                                      |        |

| A | Men  | nristor Models and Window Functions                                                  | 152    |

|   | A.1  | Memristor Models                                                                     | 152    |

|   |      | A.1.1 Linear Ion Drift Model                                                         | 152    |

|   |      | A.1.2 Nonlinear Ion Drift Model                                                      | 154    |

|   |      | A.1.3 Simmons Tunnel Barrier Model                                                   | 154    |

|   |      | A.1.4 Boundary Condition Memristor (BCM) Model                                       | 156    |

|   |      | A.1.5 Other Models                                                                   | 157    |

|   | A.2  | Window Functions                                                                     | 157    |

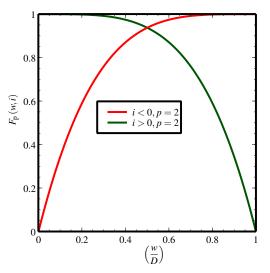

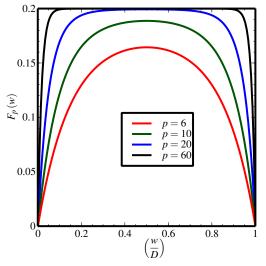

|   |      | A.2.1 Joglekar's Window                                                              | 158    |

|   |      | A.2.2 Biolek's Window                                                                | 159    |

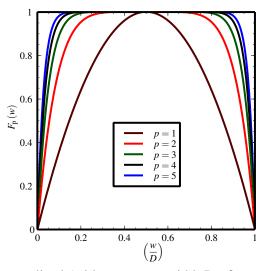

|   |      | A.2.3 Prodomakis' Window                                                             | 160    |

|   |      |                                                                                      | 100    |

| B | Imp  | ly Logic Analysis                                                                    | 161    |

| С | Snec | cialized Memristive Crossbar Array                                                   | 165    |

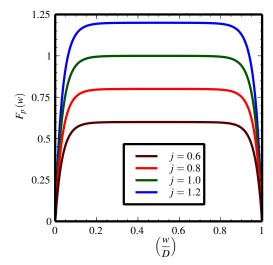

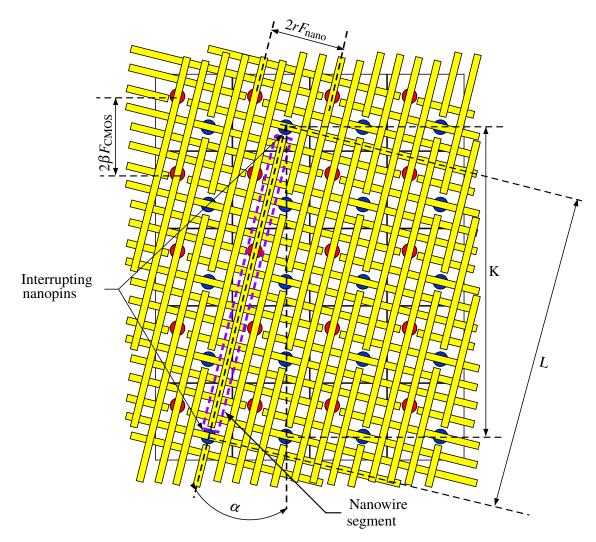

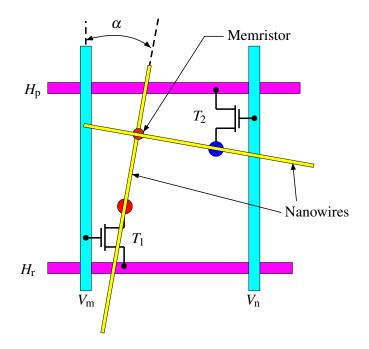

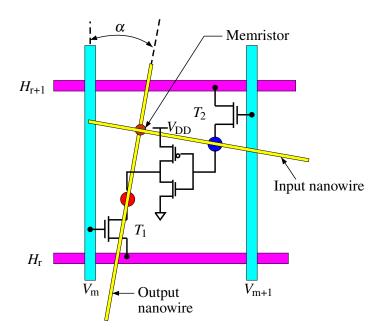

| v | C.1  | CMOL Architecture                                                                    | 165    |

|   |      |                                                                                      |        |

|   |      | HPNI Architecture                                                                    | 1 // 1 |

|   | C.2  | FPNI Architecture                                                                    | 170    |

| E Materials and Properties        | 184 |

|-----------------------------------|-----|

| Bibliography                      | 189 |

| Publication Based on Present Work | 207 |

| Brief Biography of the Candidate  | 208 |

| Brief Biography of the Supervisor | 209 |

# **List of Figures**

| 1.1  | Generic Homogeneous FPGA                                                           |

|------|------------------------------------------------------------------------------------|

| 1.2  | Heterogeneous FPGA                                                                 |

| 1.3  | Conventional FPGA CLB Structure                                                    |

| 1.4  | Programmable Interconnection Switch (Version 1)                                    |

| 1.5  | Programmable Interconnection Switch (version 2)                                    |

| 2.1  | Conceptual mrFPGA Architecture                                                     |

| 2.2  | The Stacking CBs and SBs over LBs in mrFPGA Architecture                           |

| 2.3  | The Tile of mrFPGA where CBs and SBs are Placed Over LB                            |

| 2.4  | Nanocrossbar Concept                                                               |

| 2.5  | Nanopin Structure in CMOL                                                          |

| 2.6  | CMOL Fabric with CMOS Interface                                                    |

| 2.7  | Lateral View of FPNI Fabric.    19                                                 |

| 2.8  | Top View of FPNI Fabric.    19                                                     |

| 3.1  | Memristor Definition                                                               |

| 3.2  | Memristor Structure                                                                |

| 3.3  | Idealized I-V Characteristics of Memristor                                         |

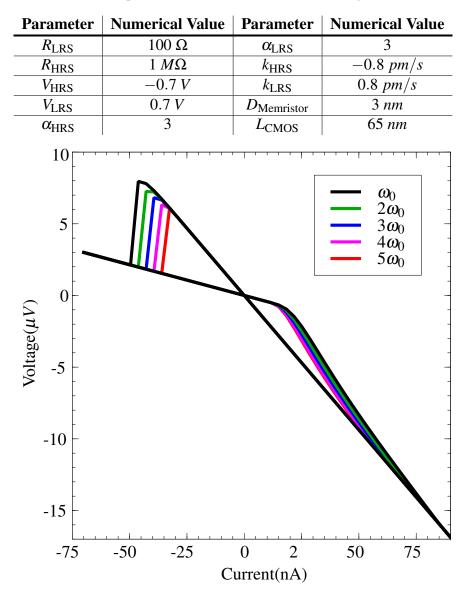

| 3.4  | I-V Characteristics of Memristor using TEAM Model                                  |

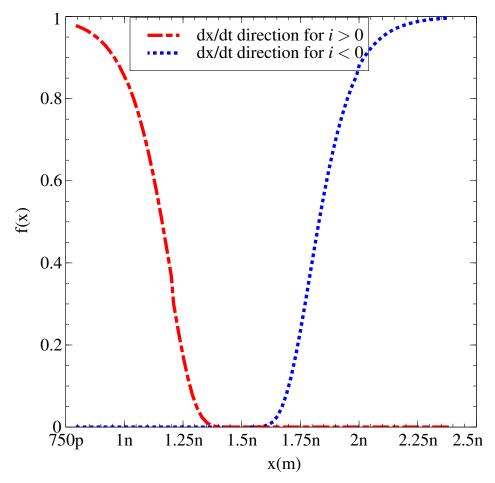

| 3.5  | Kvatinsky's Window Function                                                        |

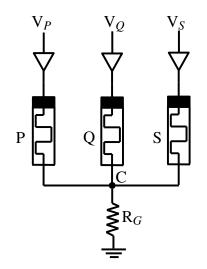

| 3.6  | Imply Gate using Memristors                                                        |

| 3.7  | Simulation of IMPLY Logic                                                          |

| 3.8  | Stateful NAND Gate using Material Implication.    36                               |

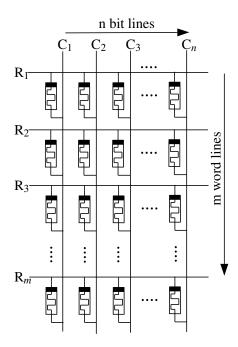

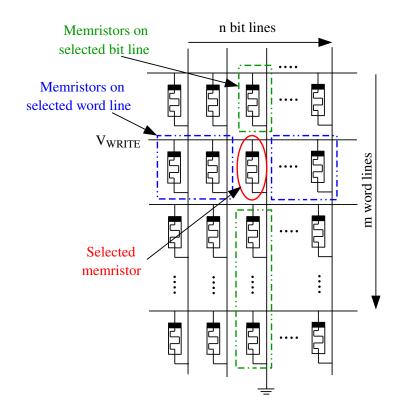

| 4.1  | Memristive Crossbar                                                                |

| 4.2  | Memristive Crossbar Sneak Path Problem                                             |

| 4.3  | Resistance Equivalent of Memristor                                                 |

| 4.4  | The Floating Write Scheme for Memristiv Crossbar                                   |

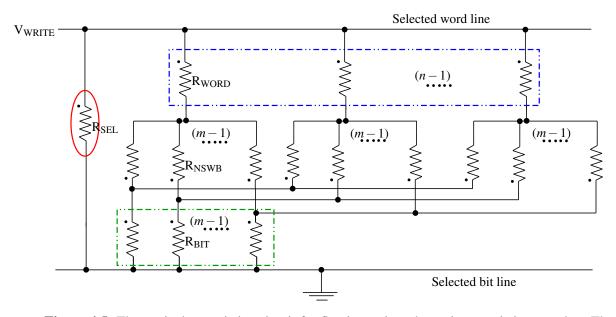

| 4.5  | Resistive Equivalent Circuit for Floating Write Scheme in Memristiv crossbar 47    |

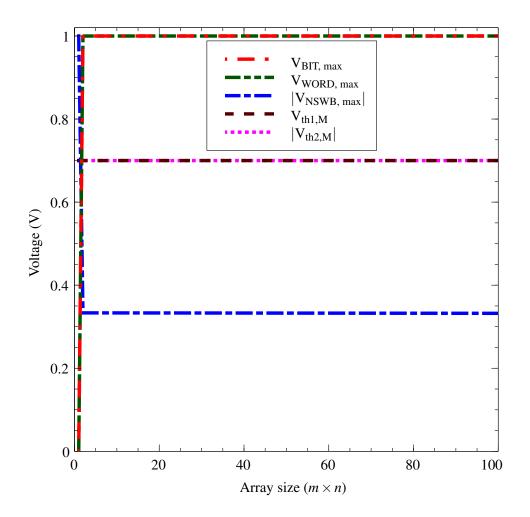

| 4.6  | Floating Write Scheme: Voltage Variations - Writing LRS in Memristive Crossbar. 49 |

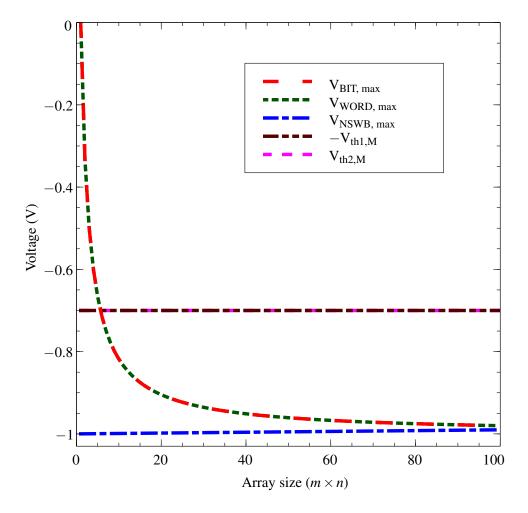

| 4.7  | Floating Write Scheme: Voltage Variations - Writing HRS in Memristive Crossbar. 50 |

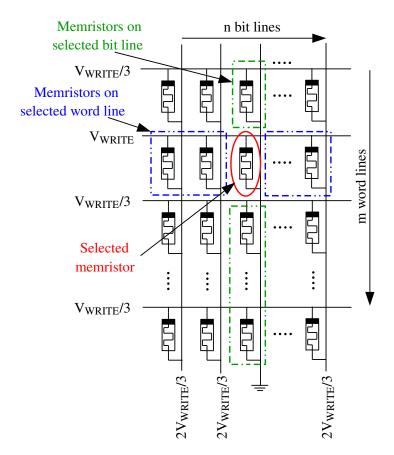

| 4.8  | 1/3 Write Scheme for Memristive Crossbar                                           |

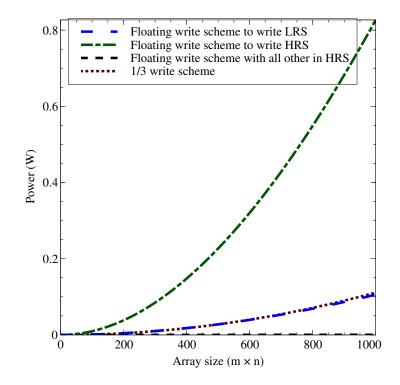

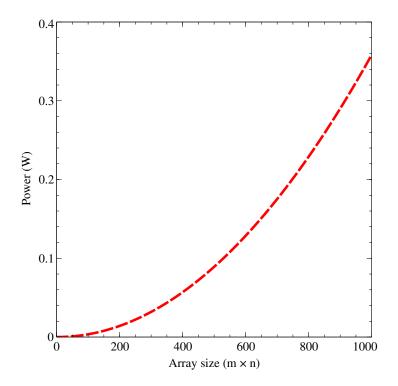

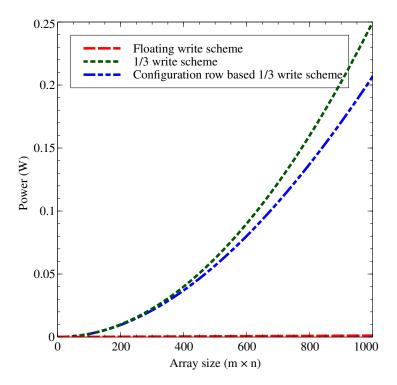

| 4.9  | Power Consumption for Write Schemes in Memristive Crossbar                         |

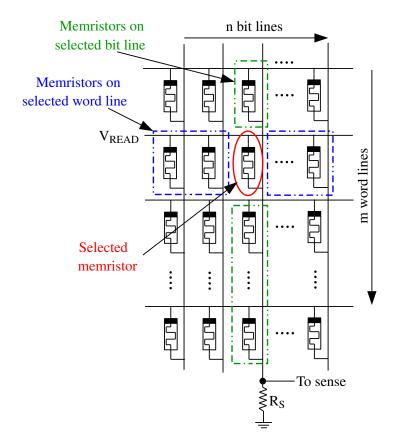

| 4.10 | Read Operation in Memristive Crossbar. 53                                          |

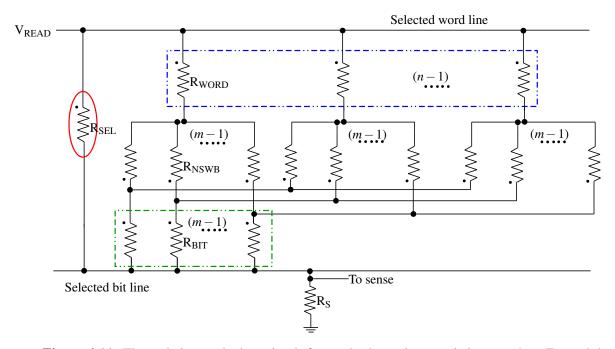

| 4.11 | Resistive Equivalent Circuit for Read Scheme in Memristive Crossbar 54             |

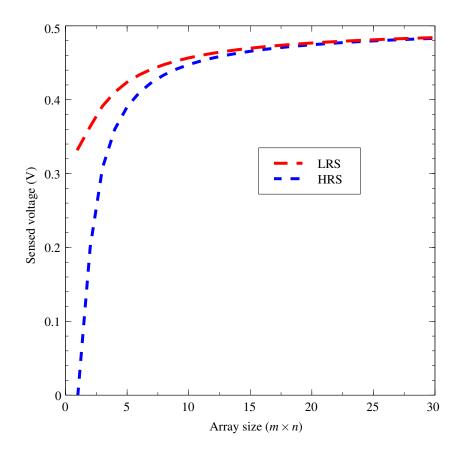

| 4.12 | The Readout Voltage in Memristive Crossbar                                         |

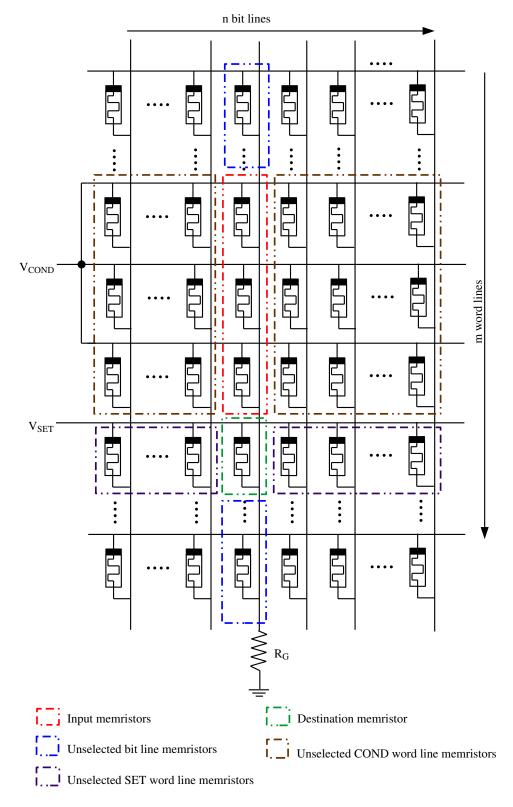

| 4.13 | Stateful NOR Operation on Memristive Crossbar.                               | 56  |

|------|------------------------------------------------------------------------------|-----|

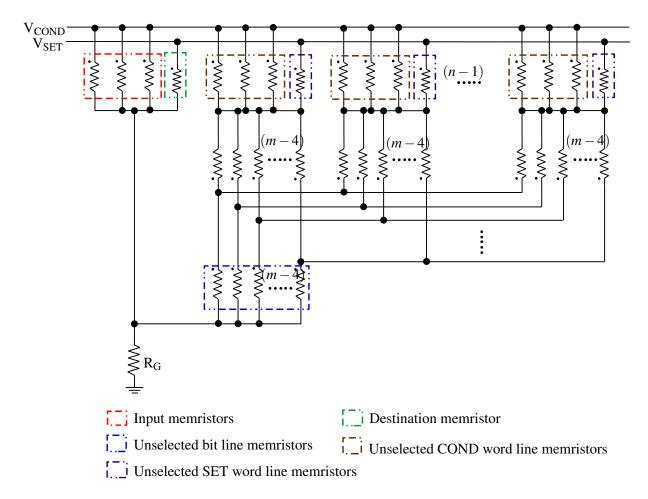

| 4.14 | Resistive Equivalent Circuit for Stateful NOR in Memristive Crossbar.        | 57  |

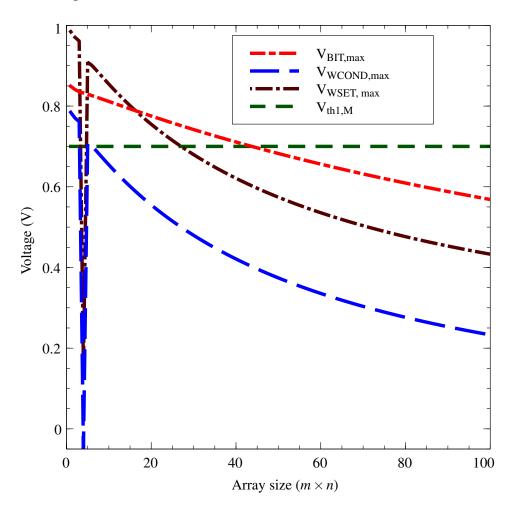

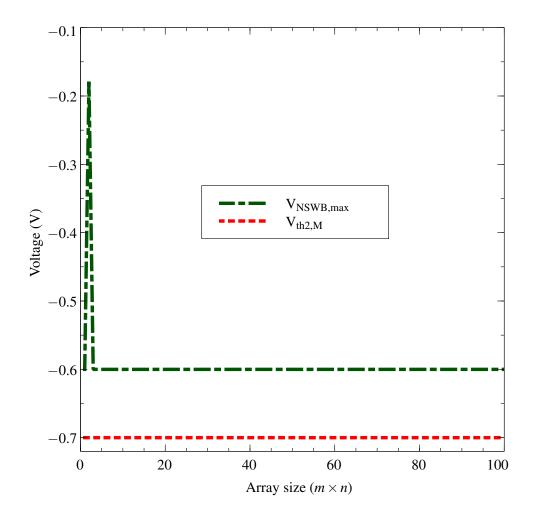

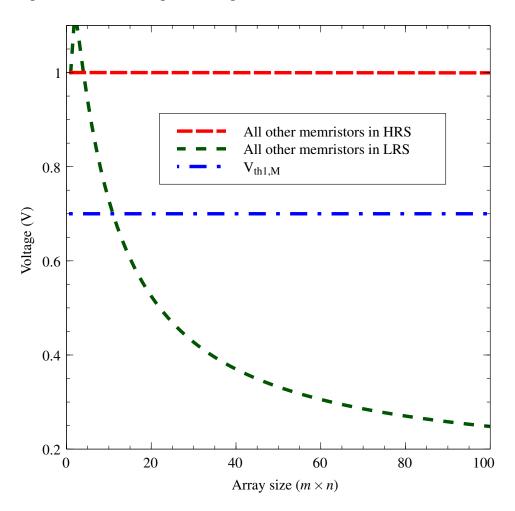

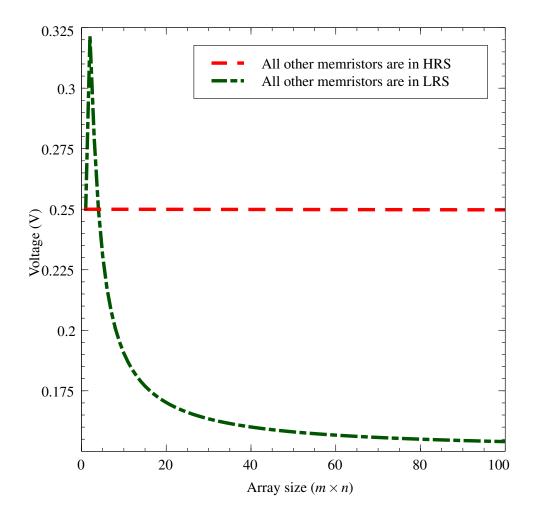

|      | Stateful NOR: Voltage across Memristors on Selected Word & Bit Lines.        | 59  |

| 4.16 | Stateful NOR: Voltage across Memristors on Unselected Word & Bit Lines       | 61  |

| 4.17 | Stateful NOR: Voltage across Destination Memristor, Others in HRS.           | 62  |

|      | Stateful NOR: Voltage across Destination Memristor, Others in LRS            | 64  |

|      | Power Consumption in Stateful NOR.                                           | 65  |

|      | Equivalent Circuit for Stateful NOR Implemented on CMOL.                     | 66  |

|      | Stateful NOR Implementation on CMOL.                                         | 67  |

|      |                                                                              |     |

| 5.1  | CRS from Memristors.                                                         | 72  |

| 5.2  | Memristor Switching from HRS to LRS.                                         | 73  |

| 5.3  | Memristor Switching from LRS to HRS.                                         | 73  |

| 5.4  | CRS Switching from HRS-LRS to LRS-HRS                                        | 74  |

| 5.5  | CRS Switching from LRS-HRS to HRS-LRS                                        | 74  |

| 5.6  | Ideal Hysteretic I-V Characteristic of CRS.                                  | 75  |

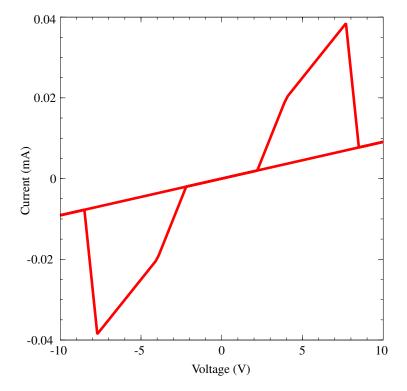

| 5.7  | Simulated Hysteretic Characteristics of CRS using TEAM Model                 | 76  |

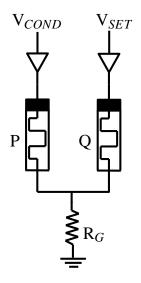

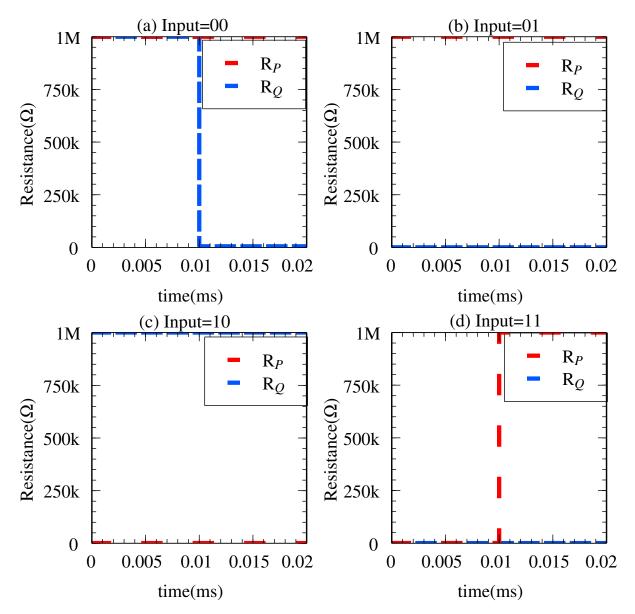

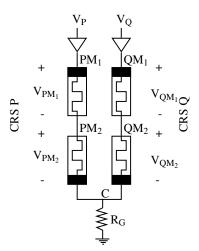

| 5.8  | 2-input NOR Gate using CRS.                                                  | 77  |

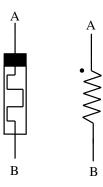

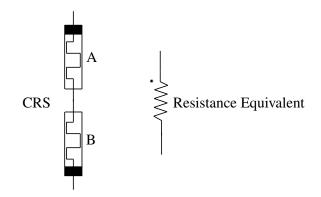

| 5.9  | Resistance Equivalent Symbol for CRS.                                        | 81  |

| 5.10 | Floating Write Scheme for CRS Crossbar.                                      | 82  |

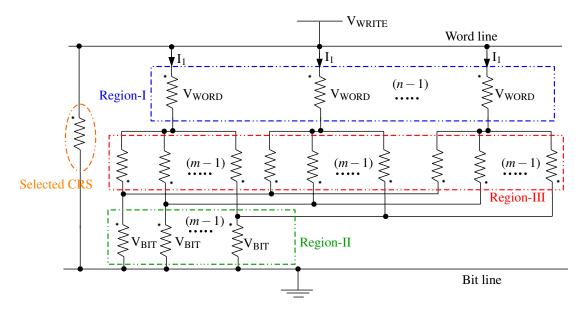

| 5.11 | Resistive Equivalent Circuit for Floating Write Scheme in CRS Crossbar       | 83  |

| 5.12 | Floating Write Scheme: Voltage Variations - Writing LRS-HRS in CRS Crossbar. | 85  |

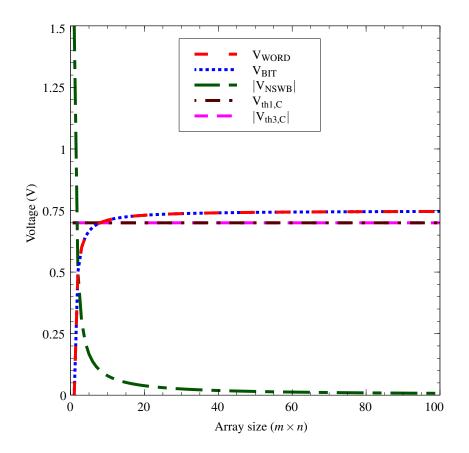

| 5.13 | Floating Write Scheme: Voltage Variations - Writing HRS-LRS in CRS Crossbar. | 86  |

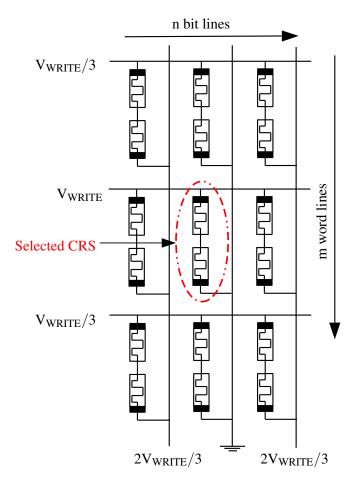

| 5.14 | 1/3 Write Scheme for CRS Crossbar.                                           | 87  |

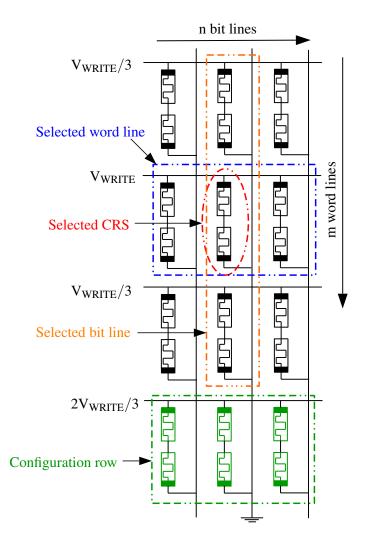

| 5.15 | Configuration Row Based 1/3 Write Scheme for CRS Crossbar                    | 88  |

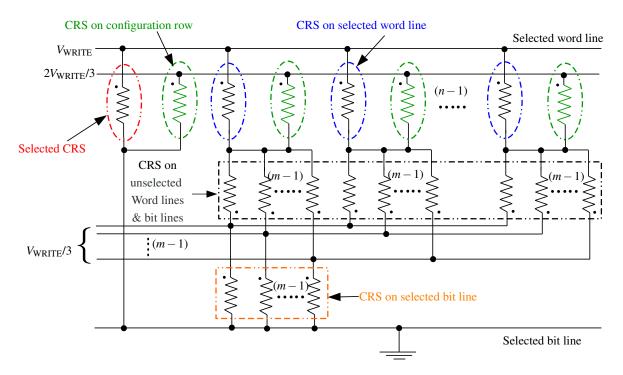

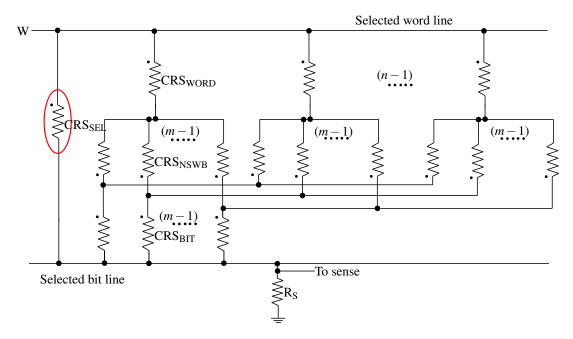

| 5.16 | Resistive Equivalent Circuit for Configuration Row 1/3 Write Scheme          | 89  |

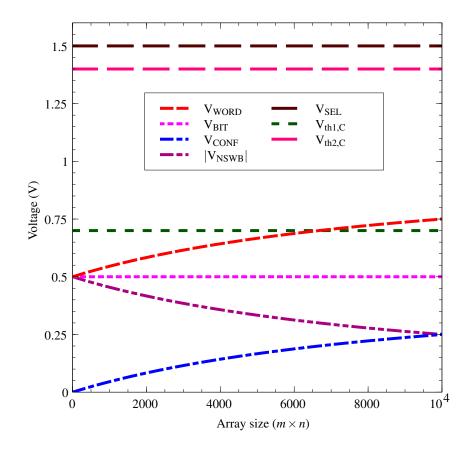

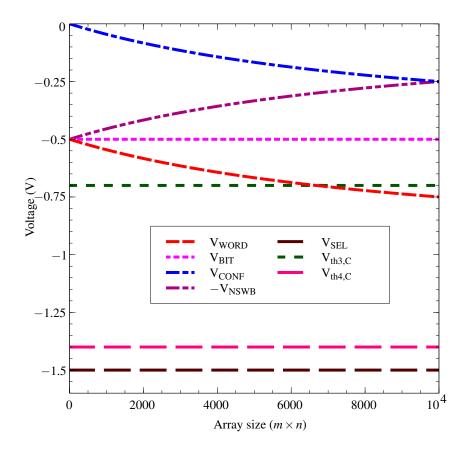

| 5.17 | Configuration Row 1/3 Write Scheme: Voltage Variations - Writing LRS-HRS     | 92  |

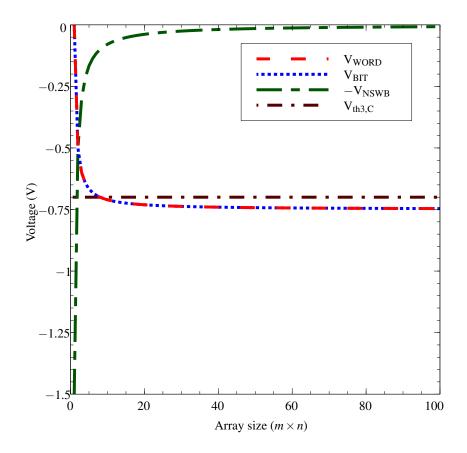

| 5.18 | Configuration Row 1/3 Write Scheme: Voltage Variations - Writing HRS-LRS.    | 93  |

| 5.19 | Power Consumption in Write Schemes for CRS Crossbar.                         | 94  |

| 5.20 | Conventional Read Scheme for CRS Crossbar.                                   | 95  |

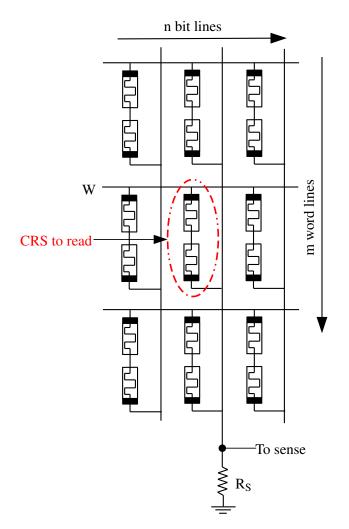

| 5.21 | Resistive Equivalent Circuit for Conventional Read Scheme in CRS Crossbar    | 96  |

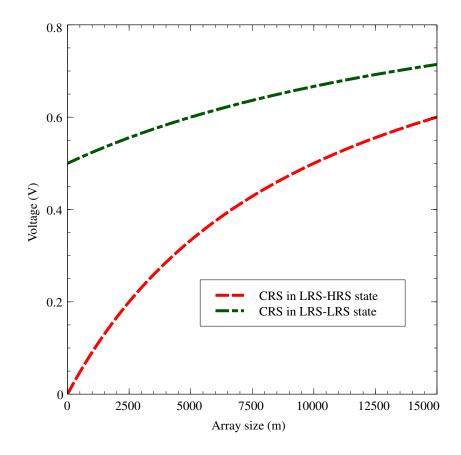

| 5.22 | Sensed Voltage while Reading LRS-LRS and LRS-HRS States                      | 97  |

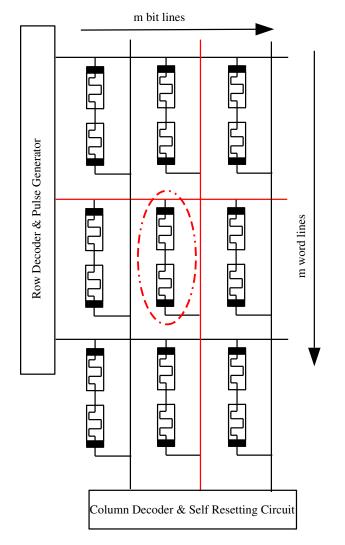

| 5.23 | Generalized Structure of CRS Crossbar with Self-resetting Read Mechanism     | 99  |

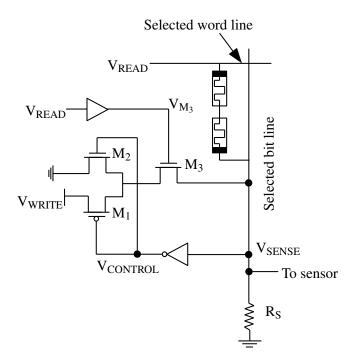

| 5.24 | Self-resetting Read Scheme Circuit.                                          | 100 |

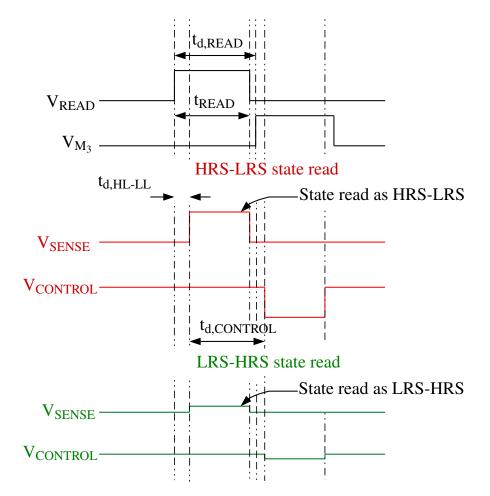

| 5.25 | Timing Diagram for Self-reset Read Scheme.                                   | 101 |

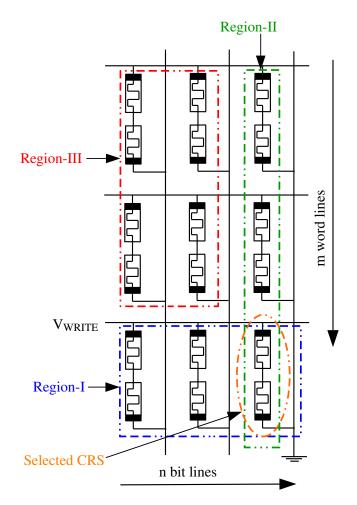

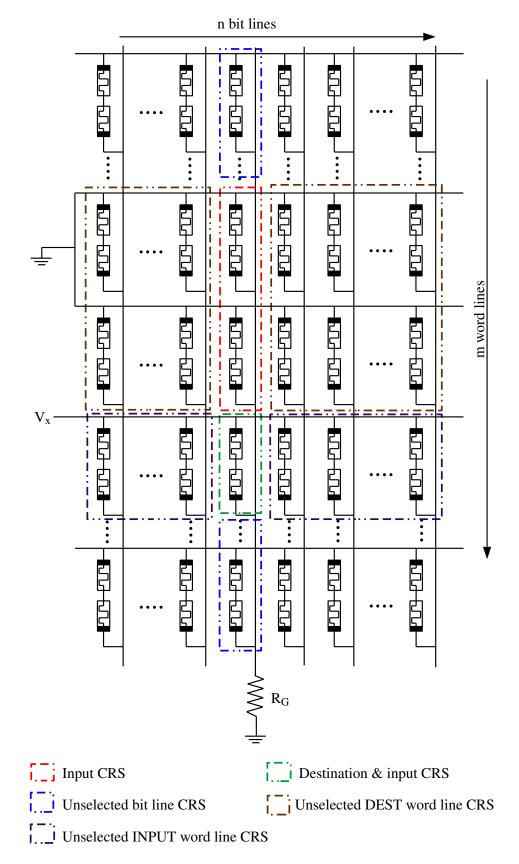

| 5.26 | Implementation of 3-input Stateful NOR Logic on CRS Crossbar.                | 102 |

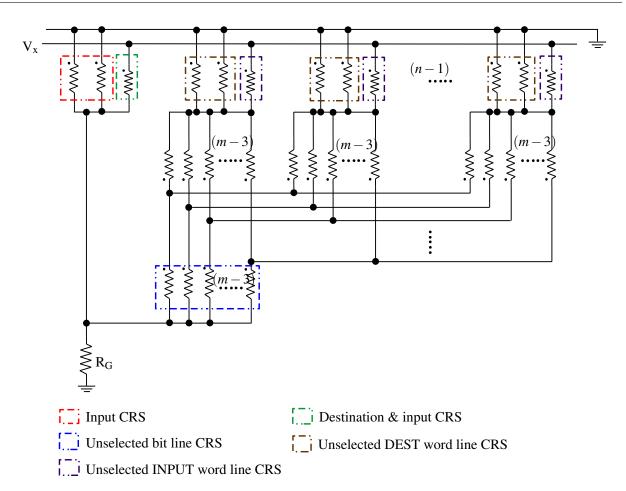

| 5.27 | Resistive Equivalent Circuit of 3-input Stateful NOR Logic on CRS Crossbar   | 103 |

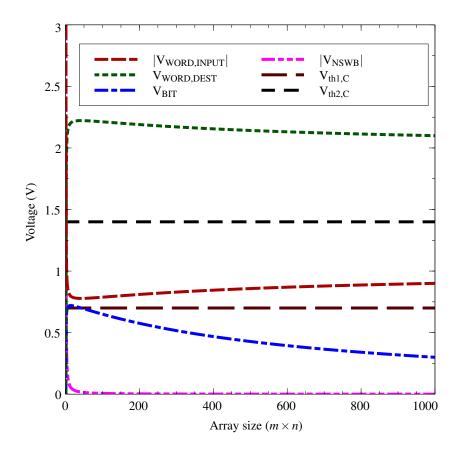

|      | Stateful NOR on CRS: Voltage across CRSs Before Destination CRS Switching    | 104 |

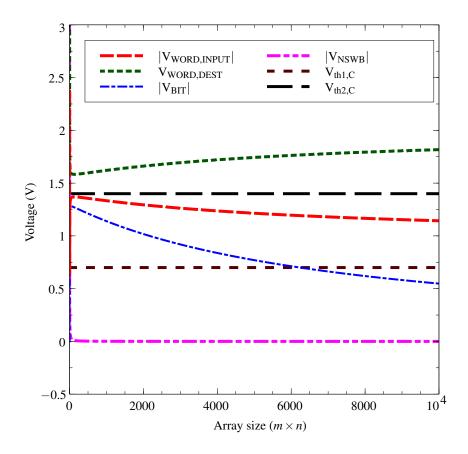

|      | Stateful NOR on CRS: Voltage across CRSs After Destination CRS Switching     | 106 |

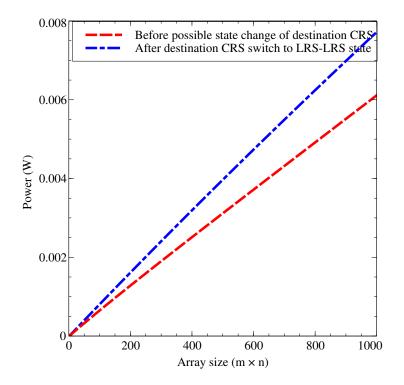

|      | Power Consumption in Stateful NOR Operation on CRS Crossbar                  | 107 |

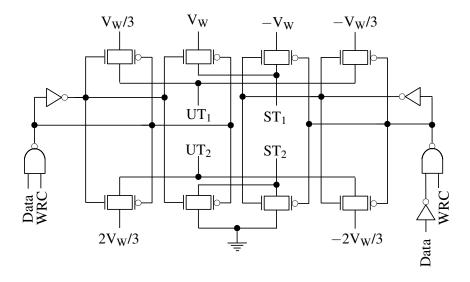

| 61   | Write Circuit for 1/2 Write Scheme                                           | 110 |

| 6.1  | Write Circuit for 1/3 Write Scheme.                                          | 110 |

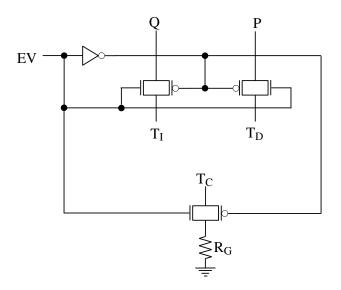

| 6.2  | Evaluate Logic Circuit to Implement Stateful NOR                             | 110 |

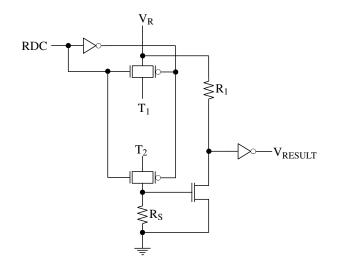

| 6.3  | Read Circuit to Detect State of Memristor or CRS.                            | 111 |

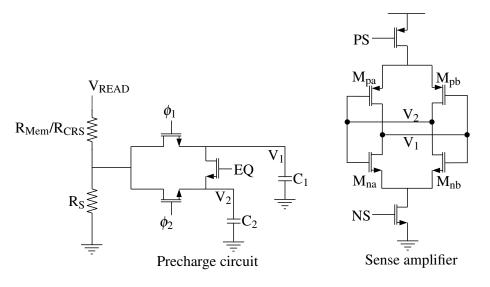

| 6.4  | Sense Amplifier Based Read Circuit.                                          | 112 |

| 6.5  | Priority Circuit.                                                             | 113 |

|------|-------------------------------------------------------------------------------|-----|

| 6.6  | NOR Logic Block Symbol.                                                       | 113 |

| 6.7  | Reconfigurable, Pipelined 3-input Logic Block Architecture.                   | 115 |

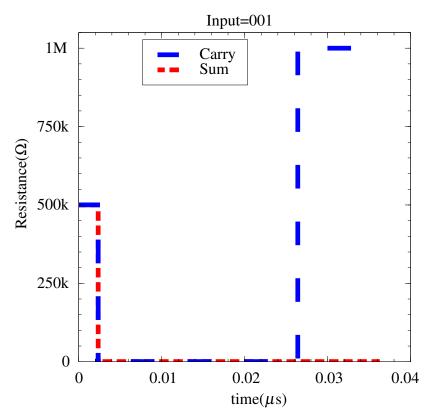

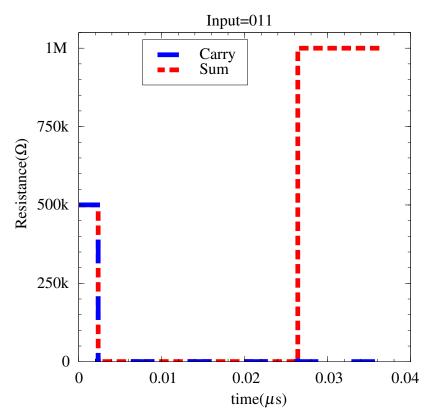

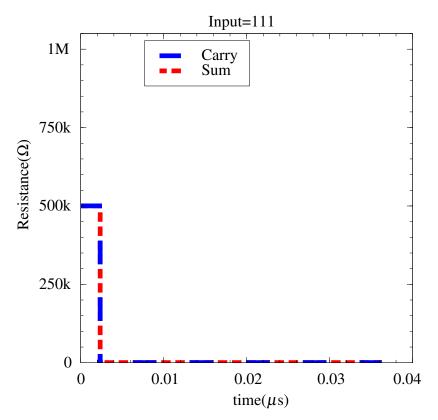

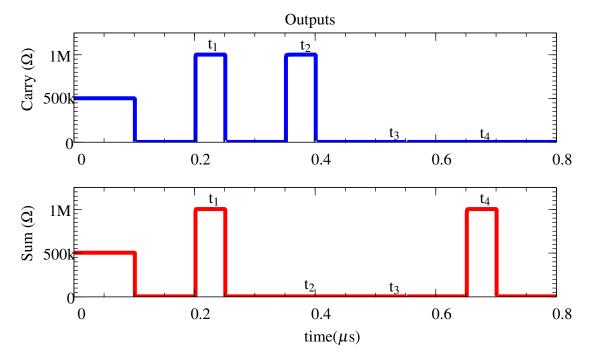

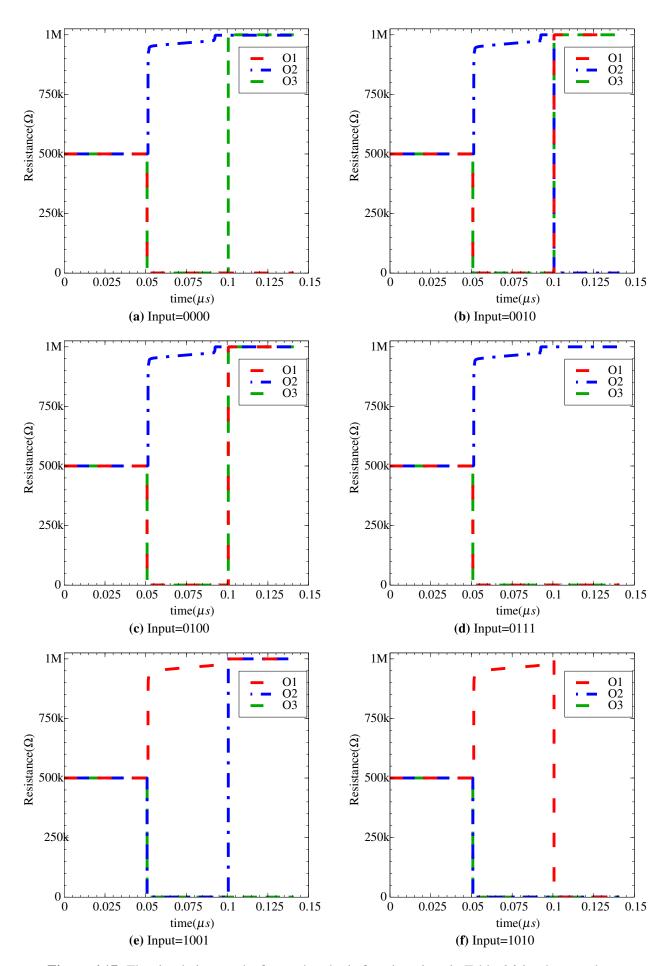

| 6.8  | Simulation Results for 1-bit Full Adder with Inputs='000'                     | 120 |

| 6.9  | Simulation Results for 1-bit Full Adder with Inputs='001'                     | 121 |

| 6.10 | Simulation Results for 1-bit Full Adder with Inputs='011'                     | 122 |

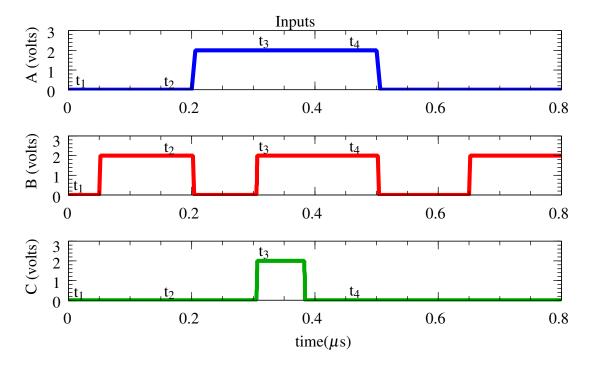

| 6.11 | Simulation Results for 1-bit Full Adder with Inputs='111'                     | 123 |

| 6.12 | Input Applied to 1-bit Pipelined Full Adder.                                  | 123 |

| 6.13 | Output of 1-bit Pipelined Full Adder                                          | 124 |

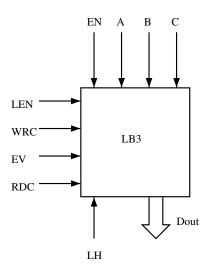

| 6.14 | 3-input Logic Block (LB3) Symbol                                              | 124 |

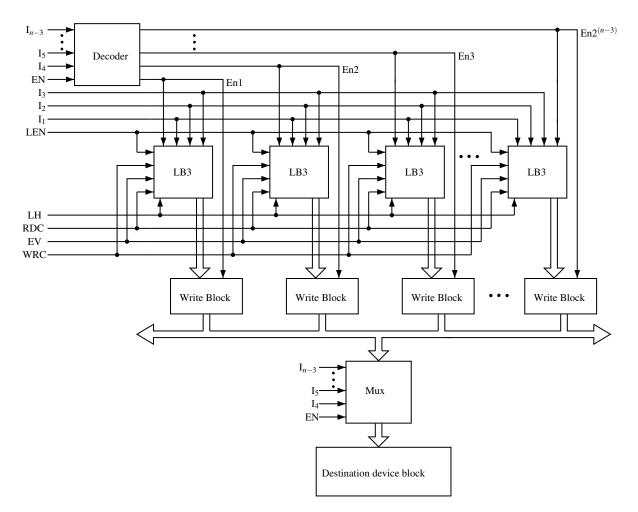

| 6.15 | Generalized Architecture using 3-input Logic Block(LB3)                       | 125 |

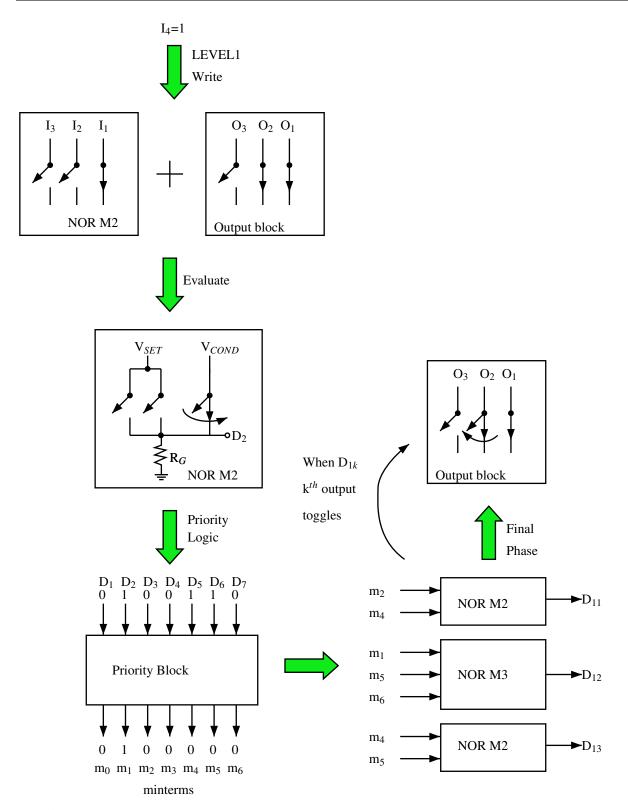

| 6.16 | Example Function Implementation Flow using Generalized Architecture.          | 127 |

| 6.17 | Simulation Results of Logic Function Implemented on Generalized Architecture. | 128 |

| 7.1  | Example ReRAM Structure.                                                      | 132 |

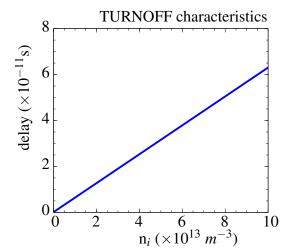

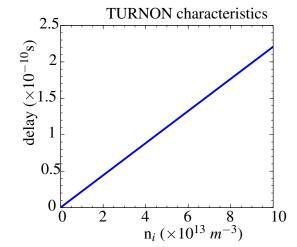

| 7.2  | Turn-off Delay of Memristor.                                                  | 134 |

| 7.3  | Turn-on Delay of Memristor.                                                   | 134 |

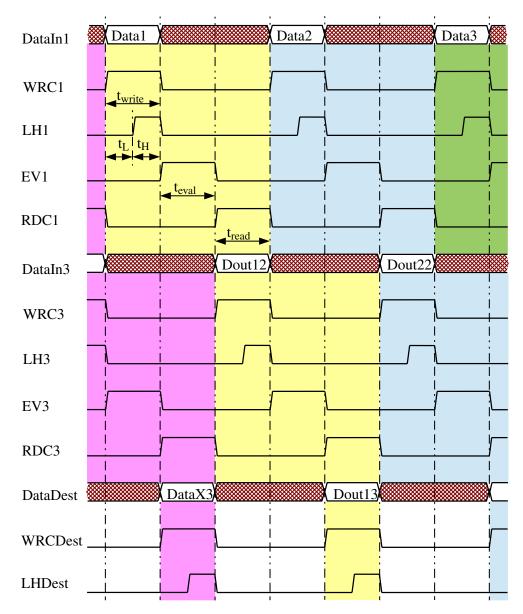

| 7.4  | Timing Diagarm for Proposed Reconfigurable Architecture.                      | 137 |

| 7.5  | Delay Versus Data $Set(n)$ for Different Reconfigurable Architectures         | 139 |

| 7.6  | Area Improvement Versus no. of Outputs for Proposed Architecture              | 144 |

| A.1  | Joglekar's Window Function.                                                   | 158 |

| A.2  | Biolek's Window Function.                                                     | 159 |

| A.3  | Prodomakis' Window Function for Different Values of <i>j</i> Parameter        | 160 |

| A.4  | Prodomakis' Window Function for Different Values of $p$ Parameter             | 160 |

| C.1  | Generic CMOL Architecture Top View.                                           | 168 |

| C.2  | Accessing Single Memristor in CMOL.                                           | 169 |

| C.3  | Structure of CMOL Cell.                                                       | 169 |

| C.4  | Example Implementation of Wired-NOR Gate in CMOL.                             | 170 |

| C.5  | The Equivalent Wired-NOR Gate in CMOL                                         | 170 |

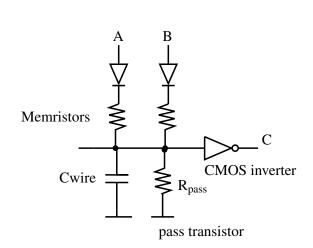

| C.6  | Example Implementation of NAND Function in FPNI Fabric.                       | 171 |

# **List of Tables**

| 2.1 | Area Breakdown of Xilinx Virtex-4 Platform FPGAs.                              | 13  |

|-----|--------------------------------------------------------------------------------|-----|

| 2.2 | mrFPGA Area Breakdown.                                                         | 15  |

| 3.1 | Memristor Models Comparison.                                                   | 31  |

| 3.2 | Values of Parameters Used for the Simulation Using VTEAM Model.                | 32  |

| 3.3 | IMPLY Gate Truth Table                                                         | 34  |

| 3.4 | Stateful NAND Logic Implementation Steps.                                      | 36  |

| 3.5 | Stateful NOR Gate: Truth Table in Terms of Resistance.                         | 37  |

| 3.6 | Steps to Implement Stateful NOR Logic                                          | 37  |

| 4.1 | Notations Used in Analysis of Memristive Crossbar for Write Operation          | 45  |

| 4.2 | Notations Used in Analysis of Memristive Crossbar for Stateful NOR Operation.  | 55  |

| 4.3 | Stateful NOR Execution Sequence in CMOL.                                       | 67  |

| 4.4 | Contol Signals for Stateful NOR Execution Sequence in CMOL                     | 68  |

| 5.1 | States of CRS                                                                  | 75  |

| 5.2 | Summary of Voltage in 2-input NOR Operation Using CRS                          | 78  |

| 5.3 | State Transitions of Memristors Involved in CRS based 2-input NOR Gate         | 79  |

| 5.4 | Truth Table for CRS Based 2-input NOR Logic.                                   | 80  |

| 5.5 | Notations Used in the Analysis of Operations on CRS Crossbar.                  | 82  |

| 6.1 | Stepwise Implementation of 3-input Logic Function Using Proposed Architecture. | 116 |

| 6.2 | Truth Table of a Random Logic Function.                                        | 126 |

| 7.1 | Delay in Different Operation on Memristive/CRS Crossbar.                       | 136 |

| 7.2 | Delay in Conventional FPGA.                                                    | 136 |

| 7.3 | Delay in Reconfigurable Architectures                                          | 138 |

| 7.4 | Power Consumption in Operations on Memristive/CRS Crossbar                     | 140 |

| 7.5 | Power Consumption in Conventional FPGA                                         | 140 |

| 7.6 | Power Consumption in Reconfigurable Circuits.                                  | 141 |

| 7.7 | Transistor Count for LUT Based CLB Used in Conventional FPGAs                  | 141 |

| 7.8 | Transistor Count for Interconnection Switch Used in Conventional FPGAs         | 141 |

| 7.9 | Device Count for Proposed Memristive/CRS Crossbar Based Architecture           | 142 |

| E.1 | Materials Used in Anion Devices.                                               | 184 |

| E.2 | Materials Used in Cation Devices.                                              | 187 |

| E.3 | Switching Material Properties.                                                 | 188 |

# Abbreviations

| VLSI  | Very Large Scale Integration            |

|-------|-----------------------------------------|

| FPGA  | Field Programmable Gate Array           |

| ASIC  | Application Specific Integrated Circuit |

| LUT   | Look Up Table                           |

| CLB   | Configurable Logic Block                |

| SRAM  | Static Random Access Memory             |

| ALU   | Arithmetic Logic Unit                   |

| CMOS  | Complementary Metal Oxide Semiconductor |

| LB    | Logic Block                             |

| СВ    | Configuration Block                     |

| SB    | Switch Block                            |

| BLE   | Basic Logic Element                     |

| CPU   | Central Processing Unit                 |

| CRS   | Complementary Resistive Switch          |

| LRS   | Low Resistance State                    |

| HRS   | High Resistance State                   |

| ReRAM | Resistive Random Access Memory          |

| NEM   | Nano Electro Mechanical                 |

| NVM   | Non Volatile Memory                     |

| MRAM  | Magnetic Random Access Memory           |

| FeRAM | Ferroelectric Random Access Memory      |

| PCRAM | Phase Change Random Access Memory       |

| PCM   | Phase Change Memory                     |

|       |                                         |

| MLC   | Multi-Level Cell                         |

|-------|------------------------------------------|

| SLC   | Single-Level Cell                        |

| CMOL  | CMOS/ MOLecular                          |

| FPNI  | Field Programmable Nanowire Interconnect |

| FPSLA | Field Programmable Stateful LogicArray   |

| TEAM  | ThrEshold Adaptive Memristor             |

| BEOL  | Back End Of Line                         |

|       |                                          |

# **Symbols**

| R                       | resistance                                                       | Ω  |

|-------------------------|------------------------------------------------------------------|----|

| С                       | capacitance                                                      | F  |

| L                       | inductor                                                         | Η  |

| i, I                    | current                                                          | A  |

| v, V                    | voltage                                                          | V  |

| q                       | charge                                                           | С  |

| $\phi$                  | flux                                                             | Vm |

| p, P                    | power                                                            | W  |

| t                       | time                                                             | S  |

| R <sub>HRS</sub>        | resistance of memristor in OFF state (High Resistance State)     | Ω  |

| <i>R</i> <sub>LRS</sub> | resistance of memristor in ON state (Low Resistance State)       | Ω  |

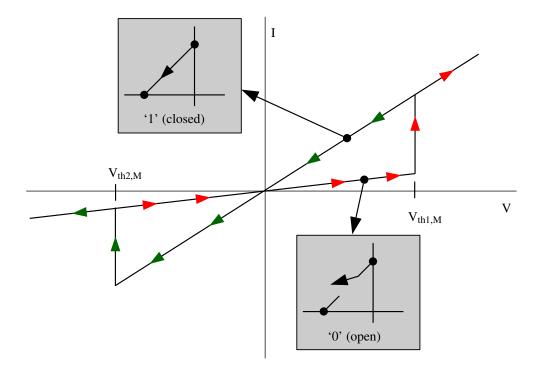

| V <sub>th1,M</sub>      | threshold voltage of memristor to switch from HRS to LRS         | V  |

| V <sub>th2,M</sub>      | threshold voltage of memristor to switch from LRS to HRS         | V  |

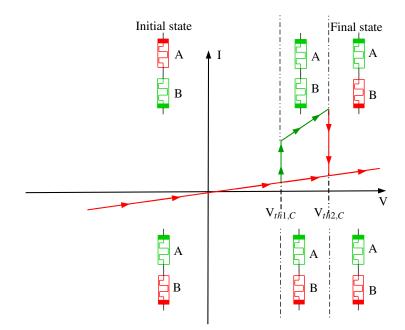

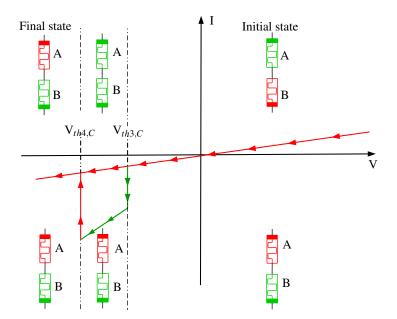

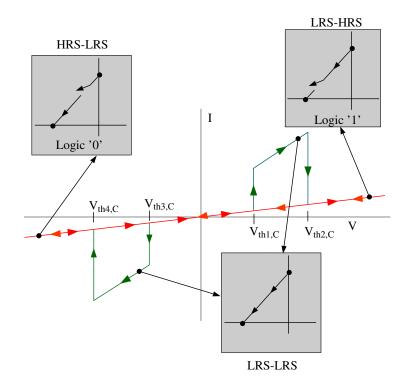

| V <sub>th1,C</sub>      | threshold voltage of CRS to switch from HRS-LRS to LRS-LRS state | V  |

| V <sub>th2,C</sub>      | threshold voltage of CRS to switch from HRS-LRS to LRS-HRS state | V  |

| V <sub>th3,C</sub>      | threshold voltage of CRS to switch from LRS-HRS to LRS-LRS state | V  |

| V <sub>th4,C</sub>      | threshold voltage of CRS to switch from LRS-HRS to HRS-LRS state | V  |

## Chapter 1

# Introduction

### **1.1 Introduction**

Three approaches are available for design of applications in digital domain.

- ASIC based approach.

- General purpose microprocessor based approach.

- FPGA based approach.

In ASIC approach, the application is implemented using dedicated hardware. The optimization is carried out with respect to one or more parameters like speed (delay), area (density), power consumption, cost, noise margin etc. These circuits are generally the fastest, the densest and the most power efficient for the specific application. However, such circuits are becoming increasingly expensive with progress in technology (fabrication cost is increasing exponentially due mask cost, quality of materials required in processing, environmental requirements in fabrication lab, stringent requirements over the light sources used in photo-lithography). Leakage current is posing a problem in continuing with Moore's law. Also, the implementation of application on ASIC takes longest time.

Microprocessors are prefabricated circuits, which are programmed by a series of instructions for specific applications. These instructions are stored in memory while data may be present in memory or provided by input devices. A control unit in the form of built-in finite state machine reads instructions from memory and executes them sequentially in the specific order defined in the program. All arithmetic and logical computations are performed in datapaths consisting of an arithmetic logic unit (ALU), a floating-point unit, and a load-store unit. This approach has advantages like flexibility and short application development time because of higher level of abstraction used for application design. However performance and energy efficiency of such system is severely affected by processor-memory bottlenecks and computing overhead.

FPGAs combine some of the best properties of microprocessors and ASICs. Like microprocessors, they are prefabricated and programmable circuits and hence very cost-efficient. Similar to ASICs, they can be customized for efficient datapaths *i.e.* they can be fine grain customized. Also massively parallel operations can be efficiently implemented on FPGA.

#### **1.2 FPGA: Basic Architecture**

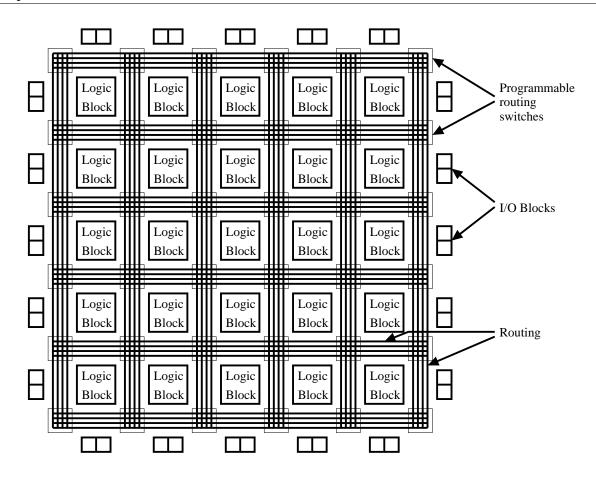

Figure 1.1 shows generic high-level architecture of an FPGA having uniform structure consisting of logic blocks, interconnection network and input/output blocks. Logic blocks are used to implement logic functions, may be in the form of sea-of-gates, look-up tables (LUT) or programmable NAND and NOR planes. The LUT based logic block structures are commonly used in most commercial FPGAs. If large size functions (many inputs and/or many outputs) are to be implemented, then interconnections between logic blocks are necessary and is done by programmable interconnects. The interconnection of data to input/output devices is done through I/O blocks.

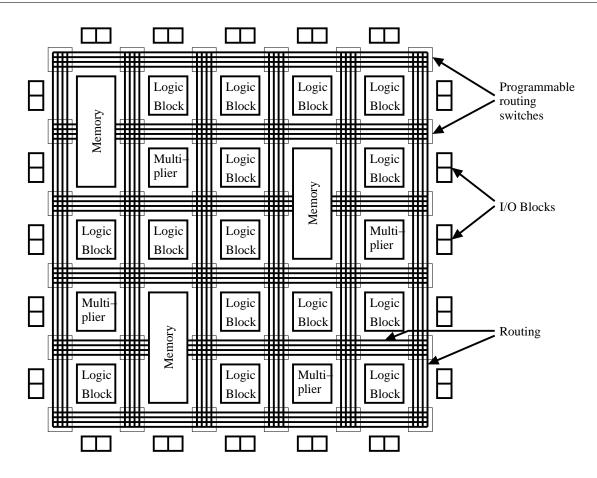

Multiplication is very common and frequent operation in many applications. When implemented on generic FPGA, it occupies more area with more delay from input to output. Hence dedicated hardwired multiplier blocks optimized for speed, area and power consumption are embedded in the architecture of FPGA. Dedicated memory blocks are also the part of architecture of most commercial FPGAs. Some FPGAs have processor cores in it hence hardware-software co-design approach can be used to improve the overall system performance. Critical functions are

**Figure 1.1.** Generic homogeneous FPGA consisting of logic blocks, programmable interconnects and I/O blocks [1].

implemented on logic blocks and multiplier blocks while other functions can be simultaneously handled by embedded processors. Such heterogeneous high-level FPGA architecture is shown in Figure 1.2.

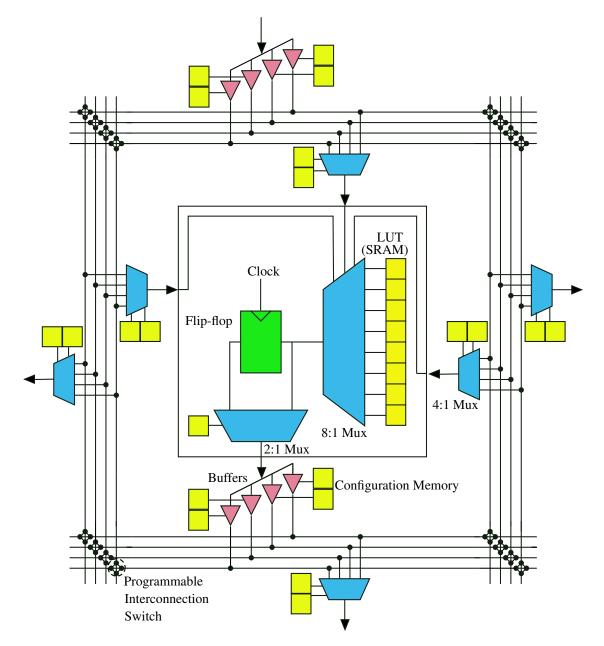

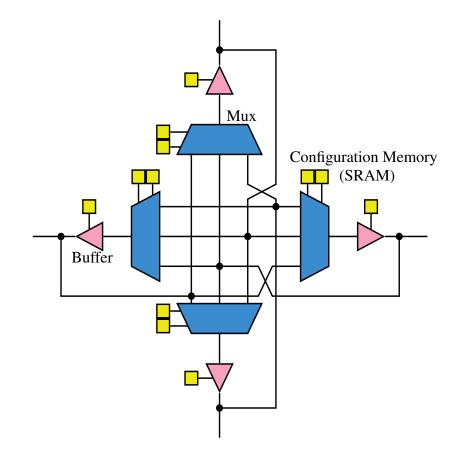

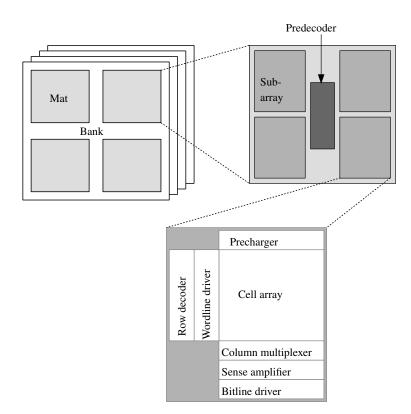

The simplified architecture of CLB with 3-input LUT is given in Figure 1.3 along with surrounding interconnection network. LUT is essentially a  $k \times 2^n$  memory array, where k is size of each memory location in bits and n is number of address lines. In Figure 1.3, k = 1 and n = 3. LUT can be viewed as programmable logic gate, which can perform *n*-input k-output logic function by storing its truth table. Input data to such gate is used as binary address to read the contents of addressed memory location and put it on output lines through multiplexer. The output of multiplexer is either made available directly on any interconnection lines or through flip-flop for sequential operations with the help of multiplexer. Tristate buffers are used to select the output lines to put results of logic block.

**Figure 1.2.** Heterogeneous FPGA consists of embedded memory blocks, dedicated hardware blocks (and processor blocks not shown here) along with logic blocks, programmable interconnects and I/O blocks [1].

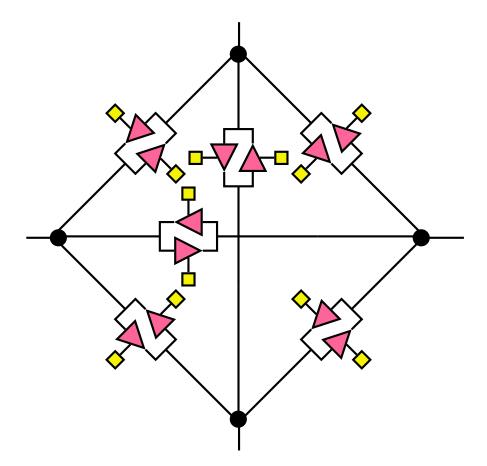

Figures 1.4 and 1.5 show programmable interconnection switch which can be used to electrically connect any horizontal (vertical) line segment to adjacent horizontal and/or vertical line segment in desired way through configuration bits [3]. Inputs to CLB may be fetched from any of the four adjacent vertical or horizontal wires by configuring the input multiplexer. Similarly output from CLB can be routed to any horizontal segment through tristate buffers programmed through configuration bits. All of these configuration bits are implemented using SRAM cells. The circuit required for programming these bits is not shown in figure for simplicity. Programming FPGA for certain functionality i.e. loading configuration data and running computation on it after configuration are two independent tasks. Generally loading of configuration information is done using serial method for less area overhead.

**Figure 1.3.** Conventional FPGA CLB Structure consisting of LUTs, multiplexers, flip-flop, configuration memory and programmable interconnects [2].

#### **1.3** Advantages of FPGA Approach

The important features like programmability after fabrication in microprocessor and fine-grain customization in ASICs are combined in FPGA. In applications where functionality can be divided into small independent modules, concurrent executions can be implemented efficiently on FPGA due to fine grain customization. In applications such as network processing, signal and image processing, scientific computing, bioinformatics etc., this style is very useful. The execution time can be greatly reduced as a result of parallel execution. Also, in applications like Boolean

**Figure 1.4.** Programmable interconnection switch (version 1) consisting of buffers and programmable memory bits to control connectivity and direction of data within interconnects [3].

satisfiability (SAT) solvers, cryptography, and logic emulation, fine-grain customization at bit level is very effective. Fine-grain customization at word level has shown 90 % decrease in power dissipation in comparison to fixed-word-length implementation [4].

In applications where functions cannot be divided into independent modules, FPGAs can be used for such applications using pipelining and throughput can be improved by overlapping the execution. For example, in deeply pipelined implementations of finite impulse response filters, Fourier transforms and discrete cosine transform, FPGAs are standard platform [4].

In applications where information to be processed is not known in advance (e.g. keys in encryption algorithms, signatures by deep packet network inspectors etc.), FPGA implementation may be even denser than ASICs. In FPGA, such information is used for reconfiguration while ASICs makes use of dedicated general-purpose multipliers, decryption circuitry, or pattern-matching engines and thus has hardware overhead [4].

**Figure 1.5.** Programmable interconnection switch (version 2) consisting of multiplexers, buffers and configuration memory bits [3].

FPGAs have faster time-to-market as no layout, masks or other manufacturing steps are needed. Its design cycle is simple as the software handles much of the routing, placement, and timing tasks. The project cycle is more predictable because of elimination of potential re-spins, wafer capacities, etc. Non-recurring expenses (NRE) are not involved in FPGA designs. Also, new bitstream can be uploaded remotely due to field-programmability.

### 1.4 Challenges in FPGA Approach

The major challenges of FPGA approach is delay, power dissipation and area (density) overheads associated with configurability. Configuration bits occupy large portion of the configurable fabric and can be as high as 50 % [5] while majority of the remaining area is devoted to configurable routing. The available area for logic implementation is very less (from 5 % to 15 % of the total chip area) [5, 6]. Because of configurability, ASICs are two to three times denser than FPGAs, for

same function implementation [5]. The interconnect resources can not be reduced beyond certain limit as it affects routability.

Also, loading configuration information in configuration memory is slow process as writing to such memory is done sequentially to reduce area overhead of writing circuit. Also configuration word length is much higher for FPGAs. In applications where same operations is to be carried out on large set of data, FPGAs have been preferred as less reconfiguration is required. If frequent reconfiguration is required, FPGA is not good choice for such applications.

In spite of disadvantages specified above, FPGAs are a more attractive option than ASICs for certain applications is mainly because of post-fabrication programmability (so that new functionality can be added or old function can be modified), less time-to-market for application (typically much shorter (weeks) compared to that of ASICs (months)). Also, non-recurring cost is not involved in application design.

The major reason behind the inferior performance of FPGA is programmable routing fabric and extensive usage of SRAM cells in their architecture. Performance gap between ASIC and FPGA needs to be improved in order to increase the share of FPGAs in the market. New emerging devices are being investigated as a replacement for SRAM and programmable interconnection switches. Memristor is one of the most attractive device which can act as nonvolatile memory (by storing data in the form of resistance) and as logic (switching) element. But it is passive device and CMOS circuits are required to implement functions using it. In the present work, memristive devices in nanocrossbar are investigated for the development of reconfigurable architecture.

### **1.5 Objectives of Research Work**

Several efforts have been made in the past to improve the performance of FPGA. These efforts can be broadly classified in one or combinations of the following methods :

1. Optimizing the conventional CMOS based FPGA architecture with respect to one or more parameters like area, delay, cost, power dissipation etc. by changing the number of inputs to logic element, by changing the size of cluster, by changing the size of wire segments etc.

- Using 3D integration technology in CMOS process to reduce the size of footprint and making them denser.

- 3. Keeping the logic elements as it is in conventional SRAM based FPGAs and modifying the programmable interconnects by replacing the switching elements (CMOS transistors) and/or configuration memory (SRAM) by new emerging devices.

- 4. Modifying the design of logic elements by using emerging devices.

Objectives of the research work carried out in this thesis are listed below:

- 1. To study the memristor as logic element and as memory cell in order to use it in building the reconfigurable architecture (reconfigurable architectures require logic elements as well as configuration memory cells).

- 2. To analyze the implementation of universal logic gate using memristors on passive memristive crossbar in order to investigate the limitation on the size of crossbar due to sneak path problem commonly found in memristive crossbar. Also analysis will help in determining the size of crossbar for maintaining the integrity of memristor cells not involved in logic operation.

- 3. To develop universal logic gate using CRSs that can be implemented on CRS crossbar, which are free from sneak path problem, and to investigate the effect of implementation of developed universal gate on other CRSs that are not part of logic in CRS crossbar.

- 4. To develop reconfigurable architecture using universal logic gate as basic building block that can be implemented on memristive/CRS crossbar, along with its automation algorithm.

- 5. To compare the performance of developed reconfigurable architecture with conventional LUT based CLB commonly used in most FPGAs.

#### **1.6 Organization of Thesis**

The thesis is organized as follows :

- **Chapter 1:** This chapter explains the basic architecture of LUT based FPGA, advantages of FPGA approach over ASIC in application design and the challenges in improving the FPGA performance. Objectives of research work are also listed in the end.

- Chapter 2: As an overview of methods adopted in the past to improve the performance of reconfigurable circuits (FPGAs), detailed literature review is presented in this chapter.

- **Chapter 3:** This chapter explains the working of memristor in general, its model and window function used in this work, and use of memristor as logic element to built universal gate (stateful NOR).

- Chapter 4: In order to implement stateful NOR gate on passive memristive crossbar, a detailed analysis of all basic operations required to perform stateful NOR is carried out in this chapter. The limitations on size of crossbar due to sneak path problem so as to perform operations without error, and in order to maintain the integrity of memristors not involved in operation are also investigated.

- Chapter 5: Passive CRS crossbar free from sneak path problem are analyzed for implementation of stateful NOR gate on it in this chapter. Also limitations on size of crossbar are investigated in order to maintain the integrity of CRS not involved in operation.

- **Chapter 6:** In this chapter, novel stateful NOR logic based pipelined reconfigurable architecture is proposed which can be implemented on memristive/CRS crossbar. Also, the automation algorithm for proposed architecture is presented.

- Chapter 7: In this chapter, performance analysis of proposed pipelined reconfigurable architecture implemented on memristive/CRS crossbar is carried out and compared with LUT based CLB used in conventional FPGA.

- **Chapter 8:** The outcomes of research work carried out are summerized in this chapter. Also, further improvements that can be done in this research area are listed.

## Chapter 2

# **Literature Survey**

### 2.1 Introduction

There are mainly three types of commercial FPGAs [7]:

- Antifuse-based FPGAs : These are non-volatile FPGAs but are not reconfigurable i.e. they can be programmed only once. Examples of antifuse-based FPGAs are Axcelerator family of FPGA manufactured by Actel.

- Flash-based FPGAs : These are reconfigurable and also non-volatile but their integration

with CMOS process is very difficult. Also low logic density, inadequate performance, and

the lack of bit-level programmability prevent flash-based FPGAs to be widely used [8]. They

consume less power and more tolerant to radiation effects. Unauthorized bitstream copying

can be avoided using flash-based FPGAs. Examples of flash-based FPGAs are Igloo and

ProASIC3 family of FPGA manufactured by Actel.

- SRAM-based FPGAs : These are volatile FPGAs and can be reconfigured many times during their lifetime. They can be fabricated using standard CMOS process and are currently very popular. They suffer from long configuration-loading time and excessive leakage power during stand-by. Xilinx Virtex and Spartan families, Altera Stratix and Cyclone are examples of SRAM-based FPGAs.

#### 2.2 Literature Review

Area, delay and power consumption of FPGAs are 21 times, 4 times and 12 times higher than those of ASICs, respectively [9] and the main reason of it is programmable routing structure [5, 10–12] which account for up to 90 % of the total area [5], up to 80 % of the total delay [10, 11] and up to 85 % of the total power consumption [12]. If FPGA routing structure is improved by replacing SRAM (which is main cause of performance inferiority) with alternative memory having properties better than SRAM, the performance gap between FPGA and ASIC can be reduced.

The efforts made in the past to improve the performance of FPGA in terms of delay, area, power consumption and cost using different techniques are given below.

- Changing the size of LUT and cluster [11, 13–15] has shown limited improvement in performance of FPGA.

- Three Dimensional (3D) integration in ICs can increase the performance in terms of functionality, density and speed, and has emerged as promising means to handle the interconnection related problems and thereby has improved the performance of FPGA [16–19]. Because of smaller tile area of FPGA and shorter interconnect distance between tiles, it provided 1.7 times performance gain. However, the use of monolithic stacking is currently limited as high temperature required in the fabrication of transistors in an upper layer may destroy the transistors and metal layers already fabricated in the lower layer [20]. Also, 3D stacking will result in excessive increase in heat density and corresponding degradation in performance if proper thermal solution is not provided [21].

- C. Chen et al. [22] replaced SRAM with NEM relays in programmable routing of FPGA. NEM relay has zero leakage power and potentially low ON-resistance. Also its fabrication is a low-temperature process and can be safely monolithically integrated above CMOS layer. This 3D NEM based FPGA has provided 43.6% footprint area reduction, 37% leakage power reduction and up to 28% critical path delay reduction compared to SRAM-based FPGA with CMOS technology at 22 nm node [23]. Also, apart from experimentally verified zero leakage, NVM on-resistance values were predicted to be smaller than that of the NMOS pass transistors [24, 25]. However its mechanical switching delay is large (>1 ns) [24, 26].

This drawback can be avoided if NEM relays are used only in FPGA routing switches as they do not change their states after configuration.

• Emerging technologies, especially non-volatile memory (NVM) technologies with zero boot-up delay, real-time reconfigurability and superior energy efficiency, are being explored as possible candidate for replacement of SRAM and it include MRAM, FeRAM, PCRAM and ReRAM [27]. Generally they provide high logic density and moderate to high performance compared with existing technologies. They also have the desirable property of non-volatility and can be turned off during stand-by to save power. But their manufacturing require usually new materials and separate processes, and thus complicate the fabrication of FPGA. Y. Chen et al. [20] proposed 3D Non-Volatile FPGA ARchitecture (3D-NonFAR) using Phase Change Memory (PCM) as universal replacement for SRAM in FPGA. PCM is high performance, high density and highly scalable non-volatile memory with bit-level programmability, the feature not available in flash memory [28, 29]. Multi-Level Cell (MLC) type PCM, which has slightly slower write speed than Single-Level Cell (SLC) but higher density (16 times to that of SRAM [30]) was used for configuration memory in LBs, CBs and SBs as writing to these bits only happen at configuration time. SLCs were used in embedded RAM blocks as read/write speed of them is critical for the performance of FPGA. Area breakdown of Xilinx Virtex-4 FPGA is given in Table 2.1 and it can be seen that only replacing SRAM with PCM can significantly improve the density (by around 14%) apart from improvement due to 3D technology.

| _ | Logic<br>Block (LB) |        |                 | Routing<br>ources ( |        |       |      |         |                |

|---|---------------------|--------|-----------------|---------------------|--------|-------|------|---------|----------------|

| - | Logic               | Memory | Switch<br>boxes | Inter-<br>connects  | Memory | BRAM  | DSP  | PowerPC | Clock +<br>I/O |

| - | 4.6%                | 8.1%   | 15.1%           | 9.9%                | 20.3%  | 14.9% | 5.3% | 10.6%   | 11.2/%         |

**Table 2.1.** Area breakdown of Xilinx Virtex-4 Platform FPGAs. In 3D-NonFAR, SRAM has beenreplaced by nonvolatile, highly dense and bitwise programmable PCM [20].

• Among the emerging NVM technologies, ReRAM is considered to be the most promising and is made up of memristors. Memristor is scalable below 30 *nm* [31] and can be programmed within 5 *ns* at 180 *nm* technology node [32]. Its fabrication is compatible

with CMOS and its size can be as small as  $F^2$  (*F* is the feature size) [33]. Because of these features, efforts have been made to use memristors in system integration [34–37]. Fabrication of memristor do not require high temperature and thus will not destroy the transistors and metal wires already fabricated below memristor layer and can be integrated with back-end-of-line (BEOL) compatible fabrication [22, 33, 38–40]. Like PCM [20], memristors have been used to replace SRAM in FPGA [36] and have shown 1.1 times and 2 times overall performance improvement before and after 3D integration. Abid et al. [41] proposed nMOS logic family using memristor which has provided 4 times density improvement over CMOS logic with similar delay and power dissipation. 3D CMOS/Nanomaterial hybrid FPGA was proposed by C. Dong et al. [21] where the transistors of interconnects were seperated from those of logic blocks and redistributed them into different dies. Nanowire crossbars and face-to-face 3D integration technology was used to provide connections between these dies. With certain power overhead brought by the large capacitance of crossbar array, this architecture has provided 2.6 times performance gain compared to the conventional FPGA architecture [21].

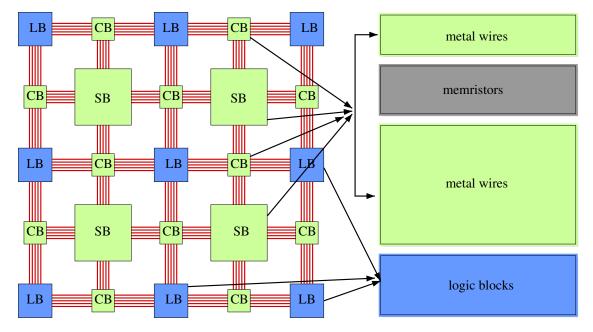

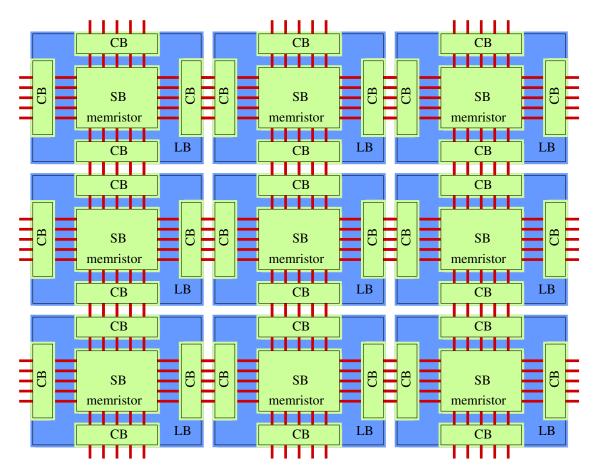

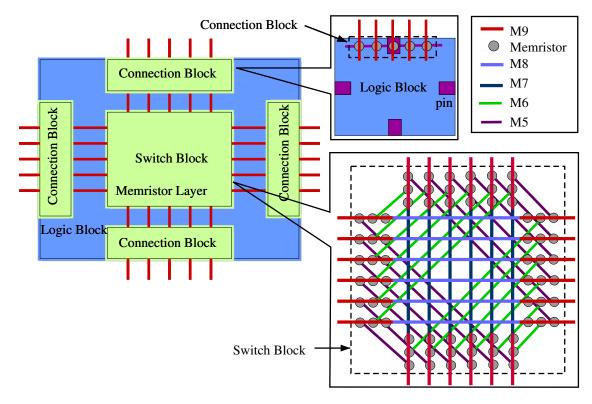

• J. Cong and B. Xiao introduced new memristor based reconfiguration FPGA (mrFPGA) [42]. The concept is shown in Figure 2.1. The programmable interconnects consisting of CBs and SBs were made up of only memristors and metal wires, and were fabricated over logic blocks in the same die as shown in Figure 2.2. The nonvolatile state of memristor (high resistance state (HRS) or low resistance state (LRS)) will decide the connectivity and is programmable. The detailed design of CBs and LBs in mrFPGA is shown in Figure 2.3. This structure is feasible for fabrication and CMOS compatible [39]. The total area of mrFPGA will be approximately equal to total area of logic blocks and is only 10 % to 20 % of the conventional FPGA area [5] as shown in the Table 2.2. This 2D architecture has shown 5.18 times area savings, 2.28 times speedup and 1.63 times power savings over conventional FPGA. The improvement in speed is primarily because of reduction in interconnection delay. The reduction in tile area by 5.5 times has reduced the length of wire segments and programmable interconnects by 2.35 times, contributing to reduction of 5.5 times in RC delays of wire segments. Replacement of transistors in the programmable interconnects (multiplexers and SRAM) by nonvolatile memristor and less capacitance on routing path due to capacitance shielding effect of memristor, average 40 % power savings has been achieved. Further if several mrFPGA stacks are integrated together using 3D technology, at least 10 times density and 4.5 times speedup improvement is possible [19].

**Figure 2.1.** Conceptual presentation of mrFPGA architecture. Programmable interconnects (CBs and SBs) were made up of only memristors and metal wires and are placed over the logic blocks [42].

**Table 2.2.** Total area of mrFPGA is approximately equal to total area of logic block which is around 10% to 20% of area of conventional FPGA (area in  $\mu m^2$ ) [42].

|                                 | Logic Block | Switch Block +<br>Connection Block | Buffer | Total   |

|---------------------------------|-------------|------------------------------------|--------|---------|

| Conventional<br>FPGA (Virtex-6) | 2082.6      | 11911                              | -      | 13993.6 |

| mrFPGA<br>(unbuffered)          | 2082.6      | -                                  | -      | 2082.6  |

| mrFPGA<br>(buffered)            | 2082.6      | -                                  | 464.86 | 2547.46 |

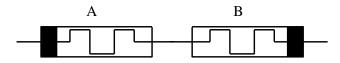

Many architectures integrating nanowire crossbar and CMOS chip have been proposed [43–46]. The major challenges in these architectures were splitting the functionality between nanowire crossbar and CMOS, and making the interconnections between CMOS and nano layers. In some architectures, demultiplexers were implemented in nanocrossbar layer to control large number of nanowires using small number of pins [43, 47, 48]. Although the work has been carried out in this direction [49–52], they present architectural challenges because simultaneously they have to configure selected nanowire junction and

**Figure 2.2.** The programmable interconnects made up of CBs and SBs were placed over logic blocks in the same die in mrFPGA Architecture [42].

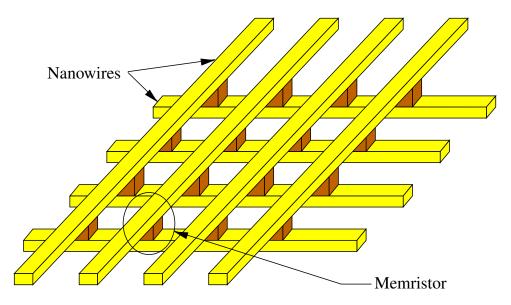

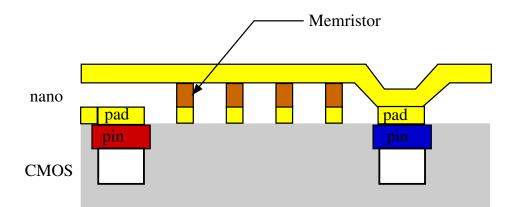

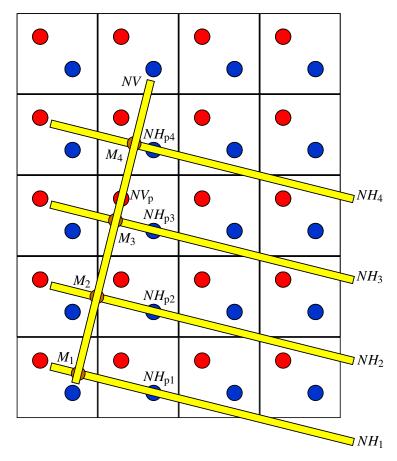

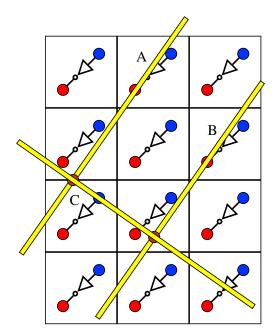

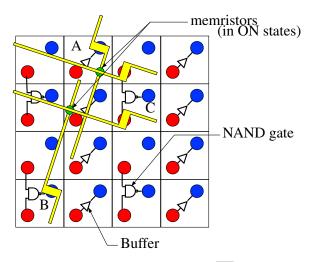

move the data between CMOS and nanolayers. Also demultiplexers are difficult to design without nonlinear devices. D. B. Strukov and K. K. Likharev proposed CMOL hybrid reconfigurable architecture [46, 53] where demultiplexing, logic inversion and gain functions were implemented in CMOS layer while signal routing and wired-OR logic were implemented in nanocrossbar layer. It consists of lower CMOS layer and upper two layers of parallel nanowires perpendicular to each other. Each crosspoint of nanowire has memristor as shown in Figure 2.4. Tapered nanopins were used to connect CMOS with nanowires as shown in Figure 2.5 where each connect exactly to one nanowire. This reconfigurable architecture is uniform fabric as shown in Figure 2.6 of four-transistor CMOS cells at semiconductor level and memristors layer above it. CMOL FPGA architecture provided approximately double density in comparison to conventional CMOS FPGAs with similar performance [53]. However, CMOL presents some operational and fabrication issues. The nanopins with just few nanometers diameters are difficult to fabricate. The wired-OR logic requires diode like nonlinear devices at nanowire junctions.

**Figure 2.3.** The tile of mrFPGA where CBs and SBs were placed over LB. The detailed structure of CB and SB is given. LB uses M1-M4 metal layers while interconnects use M5-M9 metal layers, memristors fabricated between M8-M9 [42].

**Figure 2.4.** The nanocrossbar with two sets of parallel nanowires perpendicular to each other and memristor at every crosspoint

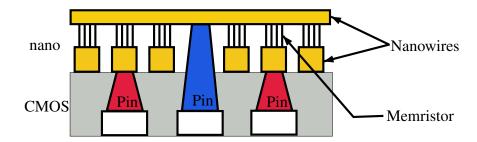

• FPNI [54] architecture is generalization of CMOL architecture. In it, all logic is implemented in CMOS and routing interconnects only in nanowires. Memristors at crosspoint were fabricated using nanoimprint technology [55]. The nanowire at CMOS

**Figure 2.5.** Tapered nanopins used in CMOL architecture to connect CMOS with nanowires. Each pin connects exactly to one nanowire [46, 53].

**Figure 2.6.** CMOL structure where CMOS layer is uniform fabric of 4 cells and nanocrossbar above it. Red and blue colored pins connect CMOS layer to nanowires [46, 53].

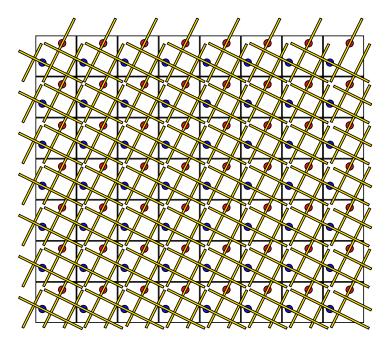

nanowire contact were broadened into pads such that the alignment of nanowire and CMOS pin requires accuracy no more than CMOS. The pin structure in FPNI is shown in Figure 2.7 while the top view of FPNI fabric is shown in Figure 2.8. In this fabric also one pin connects to only one nanowire. FPNI architecture is easy to fabricate, provide flexibility in the selection of nanoscale devices and it is possible to use more conservative process parameters. Its has shown 8 times to 25 times improvement in area, reduced power consumption, slightly lower clock speeds when standard benchmark circuits were compiled on it. Also in comparison to defect free chip, FPNI with 20% defective junctions and 20% broken nanowires has an effective yield of 75% without significant degradation of speed along critical path.

• K. Kim et. al [56] proposed stateful logic pipelined architecture using memristive switches.

Figure 2.7. Crossbar on top of CMOS gates and buffers in FPNI. The pads are used to avoid the tapering of CMOS pins as in CMOL. CMOS level accuracy is sufficient for fabrication of nontapered pins [54].

**Figure 2.8.** The nanowires are flattened into pads so that CMOS pins can be used to connect CMOS with nanowire without tapering. The resolution required will be of CMOS process in this FPNI architecture [54].

The architecture was mapped to FPNI fabric to produce FPSLA. All logic functions were implemented in nanocrossbar by configuring nonvolatile switches (memristors) while CMOS control switches were used to isolate stateful logic units so that multiple logic operations can be executed in parallel. Due to fan-out limitations of material implication, a basic stateful logic operation, new basic AND operation has been proposed to duplicate output. A large fan-in OR or NOR gates were implemented concurrently in nanocrossbar

to execute the given functionality. When implementing multilevel logic circuit, FPSLA can achieve logic density similar to that of FPNI. If inherent latches in FPSLA pipeline were taken into account, its density has been three times more. However the logic duplication overhead is very large.

### 2.3 Summary

The literature survey is summerized below.

- To develop low cost applications rapidly, the performance of FPGAs needs to be improved so that they can be preferred over ASICs.

- The main cause for performance gap between popular conventional SRAM-based FPGAs and ASICs in terms of area, speed and power consumption is programmable interconnects and extensive use of SRAM. The improvement in performance gap by changing the number of inputs to LUT and/or by changing the size of cluster in clustered FPGAs is limited. Also, with improvement in technology, handling leakage power is becoming difficult in conventional CMOS process and hence sustaining the Moore's law is becoming impossible day by day. Even though footprint size can be improved by 3D integration, the problem of leakage power remains the same in SRAM-based volatile FPGA in addition to handling of power density in 3D technology.

- High performance embedded blocks like multipliers, transceivers, block memory, processor cores etc. have been added to heterogeneous FPGAs to improve the performance of FPGA, but balancing their percentage is very difficult and if not used in application, that area of FPGA is wasted and can not be used in reconfiguration.

- Efforts have been made to improve the performance of FPGA by modifying programmable routing structure. The SRAM is replaced by devices having better performance parameters. NEM in place of SRAM in routing has shown improvement in terms of area and power dissipation but switching delay limits its usage. With the invention of memristor as nonvolatile switching device and its compatible fabrication with CMOS process, it has been used as replacement of SRAM in programmable routing as in mrFPGA and FPNI

architecture. Although this technique has shown improvement in FPGA, the use of memristor as logic element has not been explored in these architectures. The diode like behavior requirement of memristors for wired-OR logic implementation on CMOL architecture limits its use in reconfigurable architectures as such memristors are difficult to fabricate.

Apart from its use as nonvolatile switch in programmable interconnect, memristor is used as

logic element to implement universal NOR/NAND function. Any multilevel logic operation

can be implemented using these universal gates. But as material implication operation with

memristor can not fan-out (as output of logic operation is in the form of resistance state),

overhead of AND operation to duplicate result will add up wherever the output goes as input

to multiple pins as in FPSLA architecture. This limits the performance of architecture. But

this kind of logic implementation enables to think of in-memory calculations, a technique

against von-Neumann architecture.

At this time, any technique to implement logic functions only using nanocrossbar is not known. In this work, attempt have been made to explore other architectural possibilities using hybrid CMOS/Nanomaterial technology in order to improve the performance in terms of area, speed and power consumption. The basic blocks should be repeatable and should be generated during runtime in nanocrossbar with the help of CMOS layer to implement logic functions. At other times, the nanocrossbar can be used as resistive RAM.

Memristor is used in the design of reconfigurable architecture. Next chapter explains fundamentals of memristor, its model used in the simulation and its use as logic element.

# Chapter 3

# **Introduction to Memristor**

## 3.1 Introduction

Memristor is emerging as an alternative candidate for SRAM cell. Unlike SRAM, where information is stored in the form of voltage, memristor stores data in the form of resistance. Also it is possible to perform logical operations using memristors and hence there is possibility of in-memory calculations.

This chapter is organized as follows: The memristor structure, its working and ideal hysteretic characteristics are explained in the following section. In order to utilize memristors in design of memory and logic circuits sufficiently accurate, computationally efficient model should be available. Next section describes in detail the model used in simulation along with window function necessary to incorporate observed nonlinarity at boundary in fabricated memristors. The use of memristor as basic logic element is described at the end.

# **3.2 Memristor Fundamentals**

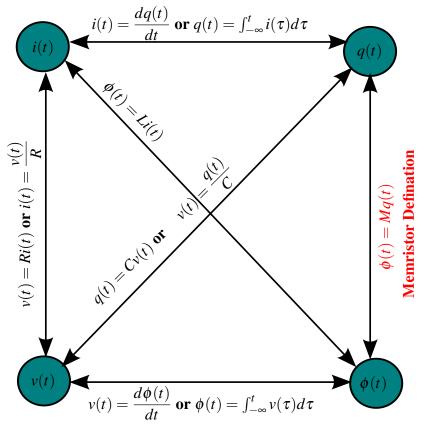

There are three traditional fundamental passive circuit elements namely resistor (R), capacitor (C) and inductor (L), and four basic circuit variables namely the current (*i*), voltage (*v*), charge (*q*) and flux ( $\phi$ ). The relationship between any two circuit variables is either defined as fundamental

passive circuit element (R = dv/di, C = dq/dv,  $L = d\phi/di$ ) or time dependent definition of circuit variables (i = dq/dt,  $v = d\phi/dt$ ). Thus out of six one-to-one possible relationships between above four circuit variables, five were well defined. For the sake of completeness, Leon Chua in 1971 first postulated the existence of sixth relationship in terms of fourth passive basic circuit element and named it memristor, contraction for memory resistor [57]. In this seminal paper, he proved passivity, uniqueness, existence of memristor and electromagnetic interpretation of its characteristics based on Maxwell's equations. The memristance M of memristor is defined as

$$M = \frac{d\phi}{dq}.$$

(3.1)

The defining relationship diagram is given in Figure 3.1.

**Figure 3.1.** Out of six one-to-one relationships between four circuit variables viz. current (*i*), voltage (*v*), charge (*q*) and flux ( $\phi$ ), five were well defined in terms of three passive elements resistor (R), capacitor (C) and inductor (L), and time dependent circuit variables ( $i = dq/dt, v = d\phi/dt$ ). The missing sixth relationship was postulated by Leon Chua in terms of memristor as fourth passive element.

To establish the link between this theoretical definition and physical realization of memristor, it took almost 40 years. Research group at HP lab successfully fabricated memristor and presented its

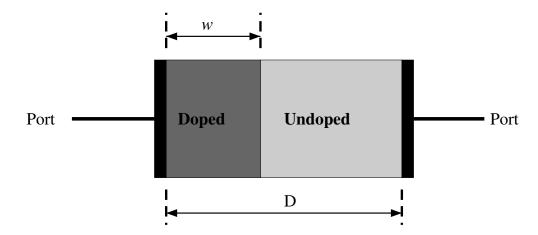

physical model in 2008 [58]. This memristor has two-layer nanoscale structure, the bottom layer consists of stoichiometric titanium dioxide (TiO<sub>2</sub>), which is an electrical insulator and the upper layer also consists of TiO<sub>2</sub> but doped with oxygen deficiencies and thus forming TiO<sub>2-x</sub> layer with high conductance [59]. The conceptual diagram is given in Figure 3.2. The TiO<sub>2</sub>-TiO<sub>2-x</sub> layers are sandwiched between two platinum plates.

**Figure 3.2.** Memristor consist of memristive material sandwiched between metal plates, for example,  $TiO_2$  sandwiched between two platinum plates. One part of  $TiO_2$  is doped with oxygen deficiencies to form  $TiO_{2-x}$  and becomes good conductor while remaining part is  $TiO_2$  which is insulator. The boundary between these regions move in either directions based on the polarity of applied voltage. When whole area between metal plates is occupied by doped region, the memristor will be in LRS state, otherwise it will be in HRS.

If strong enough electric field is applied across memristor, dopants can be shifted bidirectionally by changing the direction of electric field [59]. The oxygen vacancies are electron donors, so vacancies are positively charged. When a positive voltage is applied to metal plate on  $TiO_{2-x}$  side, it will repel the oxygen vacancies towards  $TiO_2$  side, increasing the width of  $TiO_{2-x}$  region and reducing width of  $TiO_2$  region. The application of negative voltage will have opposite effect. The position of separating area between undoped and doped region decides the memristance (resistance) of memristor. Apart from  $TiO_2$  [60–62] such memristive effect is observed in nickel oxide [39, 63] and other materials [64–66]. The memristive effect becomes very dominant in nanometer scale than in micrometer scale, hence thickness of layers between electrodes is in nanometer range [58]. Due to nanometer thickness, most of the materials show only two distinct values of resistance:  $R_{HRS}$  or  $R_{LRS}$ , where  $R_{HRS}$  is resistance of memristor in High Resistance State (OFF state resistance) and  $R_{LRS}$  is resistance of memristor in Low Resistance State (ON state resistance). The reported values of  $R_{LRS}$  and  $R_{HRS}$  in TiO<sub>2</sub> material are of the order  $10^2 \Omega$  and  $10^6 \Omega$ , respectively [67]. All these materials show characteristic hysteresis curve in their I-V plots due to change in resistance.

Memristive property arises naturally in systems for which the electronic and dopant equations of motion in a semiconductor are coupled in the presence of an applied electric field. Regardless of materials or physical mechanisms utilized, all two-terminal nonvolatile memory devices based on resistive switching effects (ReRAM), are essentially memristors [68]. The first intentional working examples of these devices, along with a simplified physics-based working model (to explain the working principle), were described in 2008 [58, 69].

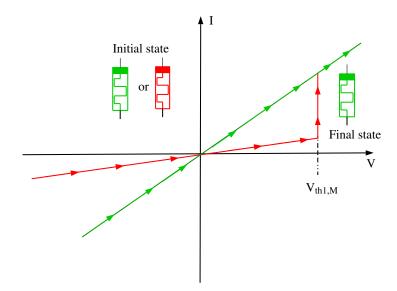

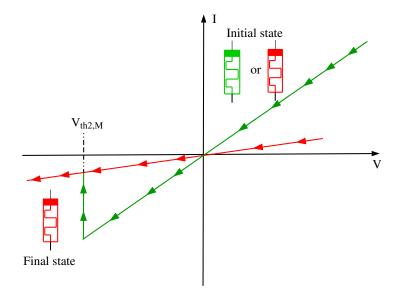

Figure 3.3 shows idealized current-voltage characteristics of memristor having two distinctive resistance states, the resistance with low-resistance state ( $R_{LRS}$ ) and with high-resistance state ( $R_{HRS}$ ). A voltage pulse of sufficient width and amplitude higher than the threshold voltage  $V_{th1,M}$  will switch the memristor to  $R_{LRS}$  state, while pulse with amplitude smaller than threshold voltage  $V_{th2,M}$  will switch it to  $R_{HRS}$  state. In the notations used for threshold voltage, the letter M in suffix indicate that it is for memristor. On the other hand, for the applied voltage with amplitude between  $V_{th1,M}$  and  $V_{th2,M}$ , the device remains in its previous state with no change of resistive state. Memristive materials show unipolar or bipolar behavior to switching [67]. Various materials showing memristive property along with the electrodes used are given in Appendix E. For unipolar memristors both  $V_{th1,M}$  and  $V_{th2,M}$  are positive with  $V_{th2,M} < V_{th1,M}$ , while for bipolar memristor  $V_{th1,M}$  is positive and  $V_{th2,M}$  is negative. Memristor acts as nonvolatile memory with information stored in the form of resistance.

Certain materials shown analog behavior i. e. they show gradual change in their resistance when they operated with low voltages and display a controllable hysteresis in their I-V characteristic [58, 67] e.g. tungsten oxide [70]. Other materials show discrete behavior, i.e. they show two state resistance values ( $R_{HRS}$  or  $R_{LRS}$ ) when overdriven by large voltages and/or current as explained in ideal I-V characteristics. The resistance values at the two states are usually two orders of magnitude apart [39], or even up to six orders of magnitude apart [40].

The magnitude of the nonlinear charge dependent component of memristance in a semiconductor film is proportional to the inverse square of the thickness of the film (as in (A.7)), and thus becomes very dominant at the nanometer scale [58]. Hence memristor phenomena is available in nanometer-scale devices.

**Figure 3.3.** Ideal I-V characteristics of memristor showing hysteresis. When voltage across the memristor in HRS state is increased (shown by red arrows), it will switch to LRS state as the voltage across it crosses positive threshold voltage $V_{th1,M}$ . If it is in LRS, state will not change upon increasing voltage across it. Similarly when voltage across the memristor in LRS state is decreased (shown by green arrows), it will switch to HRS state as the voltage across it crosses negative threshold voltage $V_{th2,M}$ . If it is in HRS, state will not change upon decreasing voltage across it.

In Figure 3.2, variable *w* is width of doped region and D is total width of memristor. When w = 0 the memristor is in HRS state and when w = D, memristor will be in LRS state.

## **3.3** Memristor Models and Window Functions