# Iris Localization in Iris Recognition System: Algorithms and Hardware Implementation

#### **THESIS**

Submitted in partial fulfilment of the requirements for the degree of

#### **DOCTOR OF PHILOSOPHY**

by

#### **VINEET KUMAR**

Under the Supervision of **Dr. Abhijit Asati**

Prof. Anu Gupta

BIRLA INSTITUTE OF TECHNOLOGY & SCIENCE PILANI

PILANI - 333031 (RAJASTHAN) INDIA

2016

#### **BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI**

### **CERTIFICATE**

This is to certify that the thesis entitled "Iris Localization in Iris Recognition System: Algorithms and Hardware Implementation" submitted by Vineet Kumar, ID. No. 2008PHXF433P for award of Ph.D. of the Institute embodies original work done by him under my supervision.

(Signature of the Supervisor)

(Signature of the Co-Supervisor)

(Signature of the Co-Supervisor)

(Signature of the Co-Supervisor)

(PROF. ANU GUPTA

Assistant Professor

Birla Institute of Technology & Science Pilani

Pilani - 333031 (Rajasthan) INDIA

Pilani - 333031 (Rajasthan) INDIA

Date:

## **Abstract**

The iris recognition is now becoming a common authentication method in handheld consumer electronics devices, such as cellphones and tablets. The iris being a biometric parameter is a way better than password protection because of its uniqueness for each individual. The embedded iris recognition system is in demand, which will give the advantages of portability, light weight and small size. This kind of embedded system would be using in general the low speed and low power CPU, which may not give the real-time performance for the iris recognition as it involves computational-intensive image processing tasks, such as the iris localization. The iris localization is first step in the iris recognition, which is followed by the feature extraction and the iristemplate matching, but the iris localization is most time consuming task in an iris recognition system with not having too big database size. Therefore, the hardware acceleration for iris localization can be very useful for obtaining the real-time performance. The field programmable gate array (FPGA) technology is preferred for realizing such a hardware accelerator.

The accuracy of iris recognition is most important for the applications demanding high security, where confidential data/resources must not be compromised. In order to make iris recognition algorithms more accurate, in general, the complexity of the processing is increased by adding more computational stages. However, when implementing these complex signal processing algorithms on embedded systems with limited processing resources, the challenge of achieving real-time performance arises.

Iris localization is an important stage in an iris recognition system, which involves image processing. The accuracy and speed of iris recognition depends on the iris localization algorithm. In this thesis, two aspects of iris localization are addressed: (a) Accurate and fast algorithms for the iris localization; and (b) FPGA based hardware accelerator for a selected iris localization algorithm. The objective of this research is to improve the performance of iris localization algorithms and implement the dedicated hardware for iris localization task without compromising accuracy. This dedicated hardware can be used to accelerate the iris localization task in more accurate and more affordable embedded iris recognition systems. Implementing dedicated

hardware for iris localization algorithm requires several embedded memory blocks (block RAMs) of FPGA, which makes it memory-intensive. This thesis work proposes a new hardware architecture, which is memory-efficient. Moreover, to improve accuracy, additional image preprocessing steps are implemented in the hardware, which further increases hardware complexity. Although, the iris localization algorithms proposed in the thesis use standard techniques, but additional image preprocessing steps have been introduced, which improves the overall performance.

This thesis is composed of seven chapters. Chapter 1 introduces the research field of the thesis and discusses about motivation behind carrying out this thesis work along with scope and objectives of the thesis. After presenting literature review in chapter 2, the main research work is exposed in chapter 3, 4, 5 and 6. Chapter 7 presents conclusion, main contributions derived from the work and future directions.

# Acknowledgements

Foremost, I would like to express my humble gratitude and sincere thanks to my supervisors Dr. Abhijit Asati and Dr. Anu Gupta for their valuable guidance, encouragement, suggestions, and moral support throughout the period of this research work. It has been a privilege for me to work and learn under them.

Next, I would like to express my deep sense of satisfaction to BITS Pilani, Deemed University, for providing all the necessary facilities and support to complete the research work. My special thanks to Prof. V.S. Rao, Acting Vice Chancellor, BITS Pilani, and Prof. A.K. Sarkar, Director, BITS Pilani, Pilani campus, for giving me an opportunity to pursue my research successfully.

I am thankful to Prof. S.K. Verma, Dean, and Prof. Hemant R. Jadav, Associate Dean, Academic Research (Ph.D. Programme) for providing all necessary guidelines and extending full support which were crucial for the completion of this thesis.

I would like to thank members of Doctoral Advisory Committee, Prof. S. Gurunarayanan and Prof. Surekha Bhanot, for their critical comments, which helped me improve the quality of manuscript.

Thanks are due to the faculties of Dept. of Electrical & Electronics Engineering, especially Prof. Chandrashekhar, Prof. Vinod Kumar Chaubey and Prof. Navneet Gupta, for their constant motivation and encouragement.

# **List of Acronyms**

1D : One-Dimensional

2D : Two-Dimensional

3D : Three-Dimensional

ASIC : Application Specific Integrated Circuit

BRAM : Block RAM

CASIA : Chinese Academy of Sciences Institute of Automation

CHT : Circular Hough Transform

CILV3 : CASIA-Iris-Lamp, Version 3.0

CITHV4 : CASIA-Iris-Thousand, Version 4.0

CIV1 : CASIA-Iris, Version 1.0

CPU : Central Processing Unit

FIFO : First In, First Out

FPGA : Field Programmable Gate Array

HDL : Hardware Description Language

HT : Hough Transform

IDO : Integro-Differential Operator

MMUV1 : Multimedia University, Version 1.0

NIR : Near Infrared

OTP : One Time Password

PC : Personal Computer

ROM : Read Only Memory

UBIRIS : University of Beira Interior Iris Database

USB : Universal Serial Bus

VW : Visible Wavelength

# **Table of Contents**

| Abstract                                 | i   |

|------------------------------------------|-----|

| Acknowledgements                         | iii |

| List of Acronyms                         | iv  |

| Table of Contents                        | v   |

| List of Figures                          | ix  |

| List of Tables                           | xiv |

| Chapter 1. Introduction                  | 1   |

| 1.1 Iris Biometric System                | 1   |

| 1.2 Motivation and Scope                 | 3   |

| 1.3 Objectives of Thesis                 | 6   |

| 1.4 Workflow                             | 6   |

| 1.5 Organization of Thesis               | 8   |

| 1.6 Concluding Remarks                   | 9   |

| Chapter 2. Literature Review             | 10  |

| 2.1 Iris Recognition                     | 10  |

| 2.1.1 Structures of Eye and Iris         | 10  |

| 2.1.2 Iris as a Biometric Trait          | 13  |

| 2.1.3 Iris Image Acquisition             | 14  |

| 2.1.4 Iris Image Database                | 14  |

| 2.1.5 Stages of Iris Recognition         | 17  |

| 2.2 Embedded System for Iris Recognition | 21  |

| 2.2.1 Definition of Embedded System      | 22  |

| 2.2.2 Architectures for Embedded Systems                               | 22 |

|------------------------------------------------------------------------|----|

| 2.2.3 Existing Works on Embedded Iris Recognition Systems              | 24 |

| 2.3 Gaps in Existing Research                                          | 27 |

| 2.4 Algorithms for Iris Localization                                   | 29 |

| 2.4.1 Daugman's IDO                                                    | 29 |

| 2.4.2 Wildes' Method                                                   | 29 |

| 2.4.3 Other Methods                                                    | 30 |

| 2.5 Hardware Implementation of Iris Localization                       | 33 |

| 2.6 Concluding Remarks                                                 | 34 |

| Chapter 3. IDO Based Iris Localization for NIR Images                  | 35 |

| 3.1 Daugman's Method                                                   | 35 |

| 3.2 The Proposed Method                                                | 37 |

| 3.2.1 Reflections Removal                                              | 37 |

| 3.2.2 Pupillary Boundary Detection                                     | 38 |

| 3.2.3 Limbic Boundary Detection                                        | 40 |

| 3.2.4 Performance Evaluation                                           | 41 |

| 3.2.5 Comparison with Other Methods                                    | 43 |

| 3.3 Concluding Remarks                                                 | 44 |

| Chapter 4. CHT Based Iris Localization for NIR Images                  | 45 |

| 4.1 Wildes' Approach                                                   | 45 |

| 4.1.1 Pupillary Boundary Detection                                     | 46 |

| 4.1.2 Limbic Boundary Detection                                        | 49 |

| 4.1.3 Performance Evaluation                                           | 50 |

| 4.2 The Proposed Method                                                | 53 |

| 4.2.1 Pupillary Boundary Detection                                     | 53 |

| 4.2.2 Limbic Boundary Detection                                        | 57 |

| 4.2.3 Performance Evaluation                                           | 60 |

| 4.3 Comparison                                                         | 63 |

| 4.4 Concluding Remarks                                                 | 65 |

| Chapter 5. Hardware Implementation of Iris Localization for NIR Images | 66 |

| 5.1 CHT Hardware                                                       | 66 |

| 5.1.1 Proposed CHT Method                                              | 67 |

|            | 5.1.2 Memory Requirements                                                         | 69  |

|------------|-----------------------------------------------------------------------------------|-----|

|            | 5.1.3 CHT Hardware Architecture                                                   | 70  |

|            | 5.1.4 Hardware Control Flow                                                       | 75  |

|            | 5.1.5 Accuracy Evaluation of Proposed CHT Architecture                            | 76  |

|            | 5.1.6 FPGA Implementation Results                                                 | 79  |

|            | 5.1.7 Performance Results and Discussion                                          | 80  |

|            | 5.1.8 Comparison with Other CHT Architecture                                      | 82  |

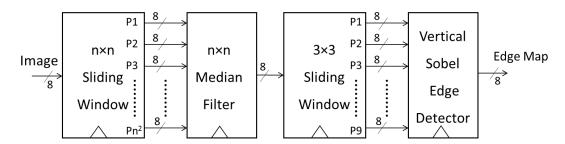

|            | 5.2 Edge-Map Generation Hardware for Pupillary Boundary                           | 85  |

|            | 5.2.1 Proposed Hardware Architecture                                              | 86  |

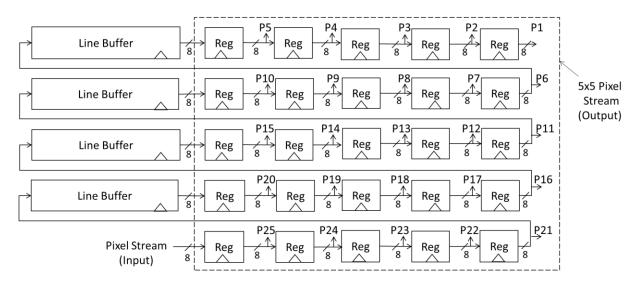

|            | 5.2.2 Sliding Window                                                              | 86  |

|            | 5.2.3 Gaussian Filter                                                             | 89  |

|            | 5.2.4 Sobel Edge Detector                                                         | 90  |

|            | 5.2.5 Image Binarization                                                          | 92  |

|            | 5.2.6 FPGA Implementation Results                                                 | 92  |

|            | 5.2.7 Performance Results and Discussion                                          | 93  |

|            | 5.3 Edge-Map Generation Hardware for Limbic Boundary                              | 96  |

|            | 5.3.1 Proposed Hardware Architecture                                              | 97  |

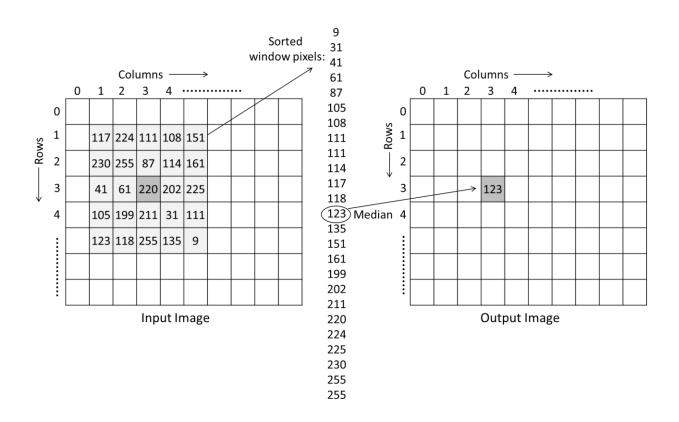

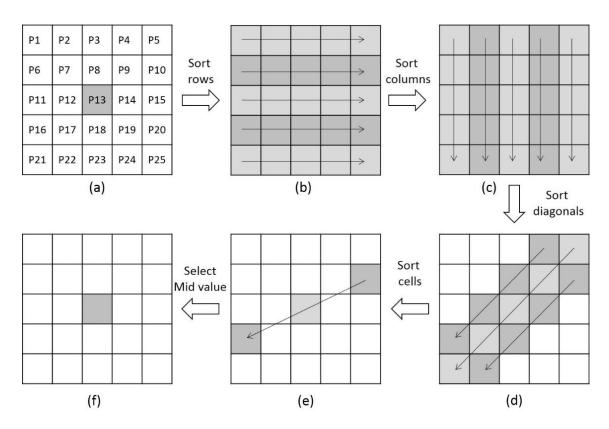

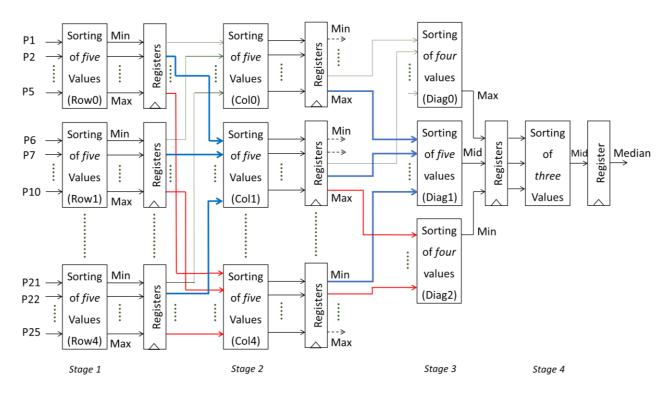

|            | 5.3.2 Median Filter Architecture                                                  | 98  |

|            | 5.3.3 Vertical Sobel Edge Detector                                                | 103 |

|            | 5.3.4 FPGA Implementation Results                                                 | 104 |

|            | 5.3.5 Performance Results and Discussion                                          | 106 |

|            | 5.3.6 Comparison of Median Filter Architectures                                   | 107 |

|            | 5.4 Adaptive CHT for Limbic Boundary Detection                                    | 108 |

|            | 5.5 Accuracy Evaluation of Iris Localization Hardware                             | 108 |

|            | 5.5.1 Datasets Used                                                               | 109 |

|            | 5.6 Concluding Remarks                                                            | 110 |

| Chapter 6. | . Preliminary Work towards Hardware Implementation of Iris Localization VW Images |     |

|            | 6.1 Proposed Iris Localization Method for VW Images                               | 112 |

|            | 6.1.1 Limbic Boundary Detection                                                   | 113 |

|            | 6.1.2 Pupillary Boundary Detection                                                | 114 |

|            | 6.1.3 Performance Evaluation                                                      | 116 |

|            | 6.1.4 Comparison with Other Methods                                               | 119 |

|            |                                                                                   |     |

| 6.2 Concluding Remarks                      | 119 |

|---------------------------------------------|-----|

| Chapter 7. Conclusion and Future Directions | 121 |

| 7.1 Summary of Contributions                | 121 |

| 7.2 Future Directions                       | 123 |

| References                                  | 125 |

| List of Publications                        |     |

| Brief Biography of Candidate                | 133 |

| Brief Biography of Supervisor               |     |

| Brief Biography of Co-Supervisor            |     |

# **List of Figures**

| Figure 1.1. Functioning of iris biometric system.                                                                     | 2              |

|-----------------------------------------------------------------------------------------------------------------------|----------------|

| Figure 1.2. Personal biometric tokens: (a) Techshino fingerprint USB token; (b) Fingerprint-based H                   | łYPR           |

| Biometric OTP                                                                                                         | 4              |

| Figure 1.3. Algorithms and hardware development flow of thesis.                                                       | 7              |

| Figure 2.1. Human eye: (a) Location of iris in eye image; (b) Structure of human eye.                                 | 11             |

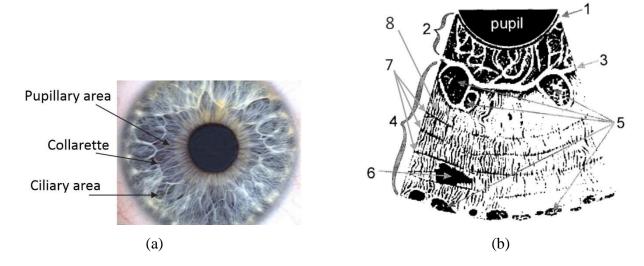

| Figure 2.2. Human iris: (a) Picture of human iris.; (b) Visible features on surface of the human ir                   | is: 1-         |

| Pigment frill, 2-Pupillary area, 3-Collarette, 4-Ciliary area, 5-Crypts, 6-Pigment spot, 7-Conce                      | entric         |

| furrows, 8-Radial furrows.                                                                                            | 12             |

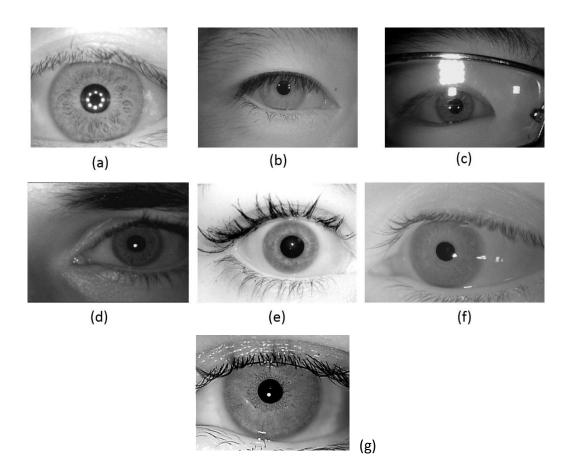

| Figure 2.3. Sample images from NIR databases: (a) CASIA-Iris-Interval, version 3.0; (b) CASIA                         | \-Iris-        |

| Lamp, version 3.0; (c) CASIA-Iris-Thousand, version 4.0; (d) MMU, version 2.0; (e) ICE-2005; (f) V                    | WVU            |

| (off-angle image); (g) IITD, version 1.0.                                                                             | 16             |

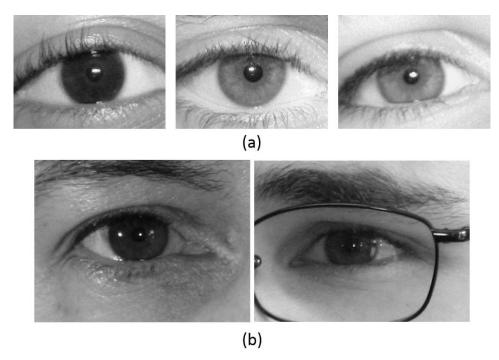

| Figure 2.4. Sample images from VW databases: (a) UBIRIS.v1; (b) UBIRIS.v2                                             | 17             |

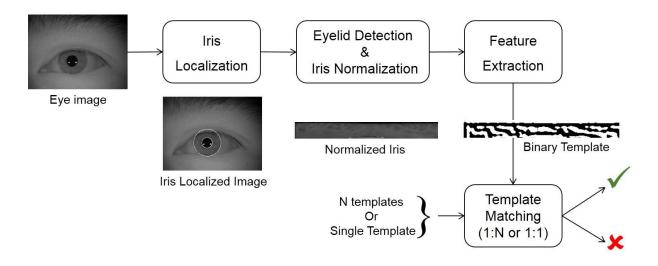

| Figure 2.5. Stages of an iris recognition system.                                                                     | 18             |

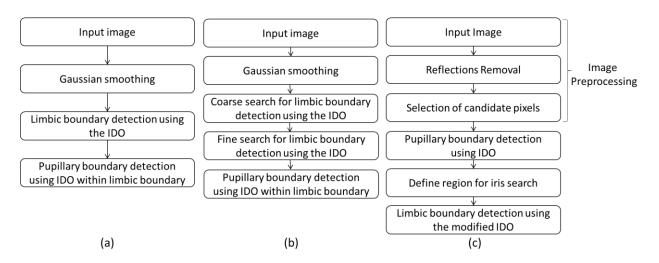

| Figure 3.1. Iris localization based on IDO: (a) Original method [Daugman, 1993]; (b) Modified method [Daugman, 1993]; | ethod          |

| [Daugman, 2004]; (c) Proposed method.                                                                                 | 36             |

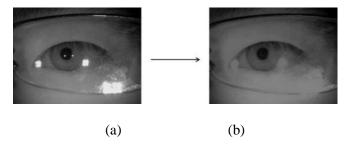

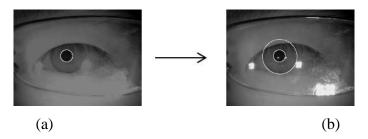

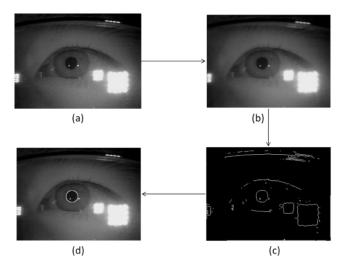

| Figure 3.2. Reflections removal: (a) A noisy image from CITHV4; (b) The preprocessed iris i                           | mage           |

| obtained from (a)                                                                                                     | 37             |

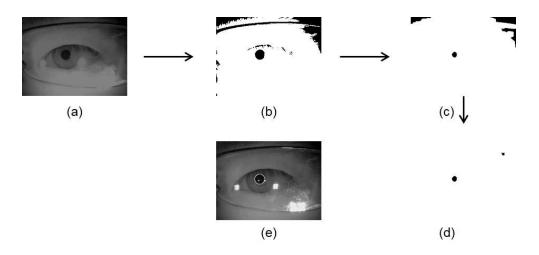

| Figure 3.3. Pupillary boundary detection: (a) Preprocessed iris image; (b) Binarized-image obtained                   | after          |

| thresholding; (c) Binary image after image cleanup step; (d) After removing pixels close to image b                   | order          |

| in (c); (e) Pupil localized image by the IDO.                                                                         | 38             |

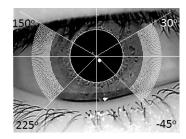

| Figure 3.4. Selection of iris search region in the image.                                                             | 40             |

| Figure 3.5. Limbic boundary detection: (a) Input is preprocessed iris image with pupil center known                   | n; <b>(b</b> ) |

| Iris localized image obtained using modified IDO.                                                                     | 41             |

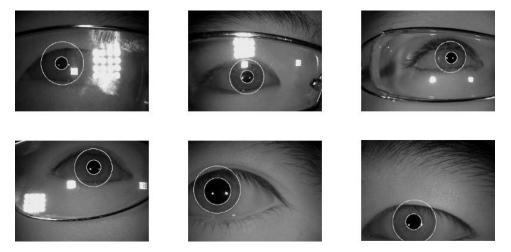

| Figure 3.6. Examples of accurately localized irises in CITHV4 images using the proposed method                        | 42             |

| Figure 3.7. Examples of accurately localized irises in MMUV1 images using the proposed method                         | 43             |

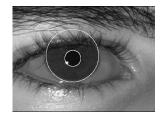

| Figure 4.1. Iris localization: (a) Wildes' approach; (b) Proposed approach                                            | 46             |

| Figure 4.2. Pupillary boundary detection: (a) Input image; (b) Gaussian smoothed image; (c) Edge                      | -map           |

| for pupillary boundary detection; (d) Pupil localization using CHT.                                                   | 47             |

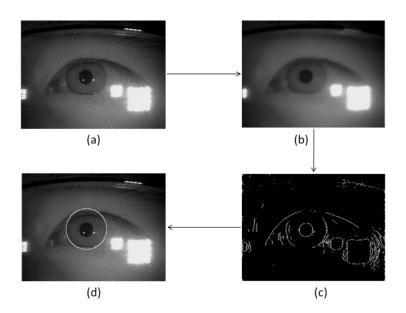

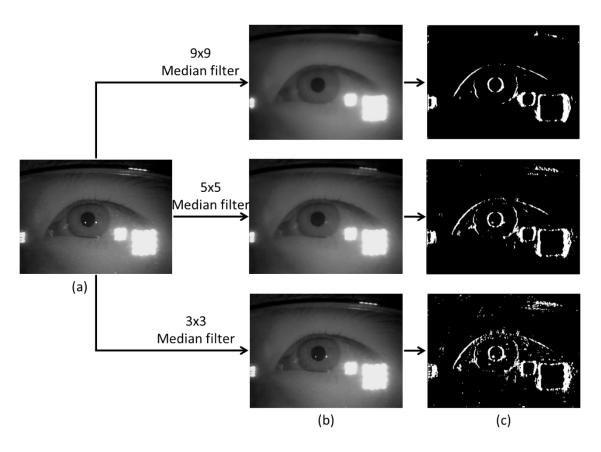

| <b>Figure 4.3.</b> Limbic boundary detection: (a) Input image; (b) 9×9 median filtered image; (c) Edge-map for      |

|---------------------------------------------------------------------------------------------------------------------|

| limbic boundary detection; (d) Limbic boundary localization using CHT                                               |

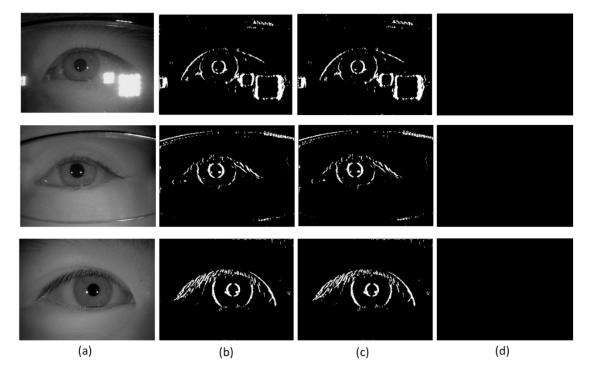

| Figure 4.4. Examples of wrong iris localization in CITHV4 images due to lighting reflections: (a) Edge-             |

| map for pupillary boundary detection; (b) Wrong iris localization                                                   |

| Figure 4.5. Examples of wrong iris localization in CILV3 images due to eyelids, eyelashes and eyebrow               |

| hair: (a) Edge-map for pupillary boundary detection; (b) Wrong iris localization                                    |

| Figure 4.6. Wrong limbic boundary detection: (a) Edge-map for limbic boundary detection; (b)                        |

| Wrong limbic boundary detection, but correct pupillary boundary detection                                           |

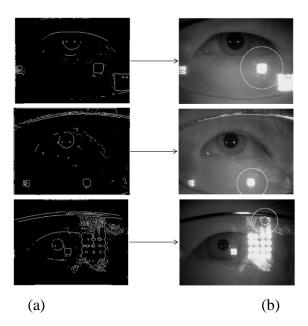

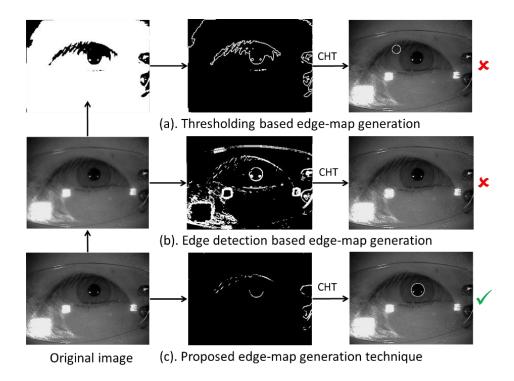

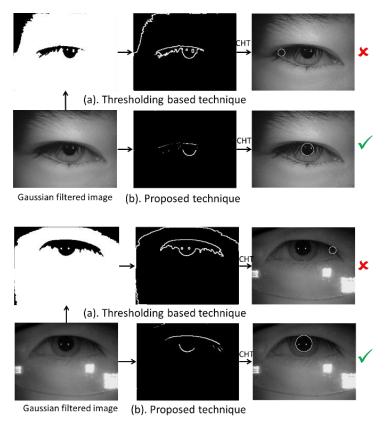

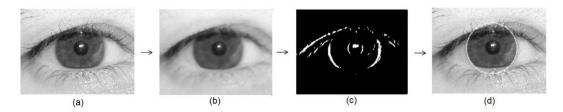

| Figure 4.7. Edge-map generation techniques for pupillary boundary detection: (a) Thresholding based                 |

| technique resulting in wrong pupil localization; (b) Edge detection based technique resulting in wrong              |

| pupil localization; (c) Proposed technique that combines the edge-maps of (a) and (b) using logical                 |

| ANDing, which results in correct pupil localization                                                                 |

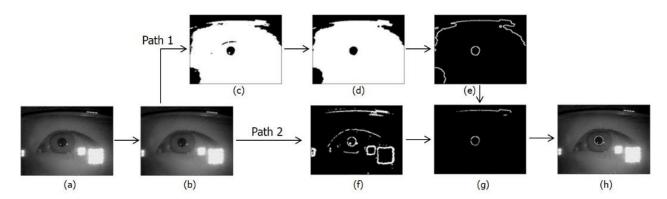

| Figure 4.8. Edge-map generation for pupil boundary detection: (a) Iris image (320×240) from CITHV4;                 |

| (b) Gaussian smoothed iris image ( $\sigma = 1.0$ , k=5); (c) Binary image after applying intensity thresholding on |

| (b); (d) Cleaned binary image obtained from (c) using hole filling followed by image opening (se='disk',            |

| k=7); (e) Edge image obtained after applying Sobel edge detector without thinning on (d); (f) Edge image            |

| obtained after applying Sobel edge detector without thinning on (b); (g) Edge-map obtained by                       |

| intersection (logical AND) operation on (e) and (f); (h) Iris image with pupil detection (shown by white            |

| circle) obtained after applying CHT on (g)                                                                          |

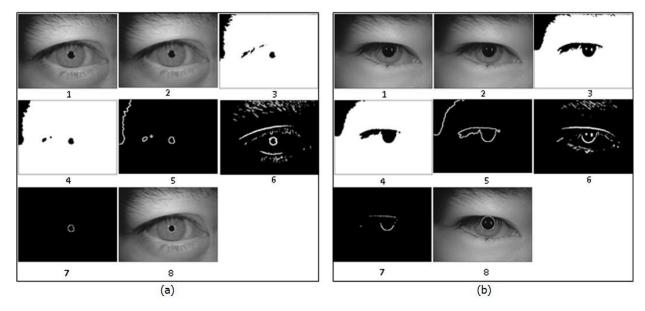

| Figure 4.9. Edge-map generation for pupil boundary detection: (a) Ideal edge-map (image 7) that contains            |

| pupil boundary edges only; (b) Edge-map (image 7) that contains pupil boundary edges as well as false               |

| edges; [the images in (a) and (b) are: 1. Iris image from CILV3; 2. Smoothed iris image; 3. Binary image            |

| after thresholding 2; 4. Cleaned binary image obtained from 3; 5. Edge image of 4; 6. Edge image of 2; 7.           |

| Edge-map obtained by intersection operation on 5 and 6; 8. Pupil localized iris image obtained after                |

| applying CHT on 7]56                                                                                                |

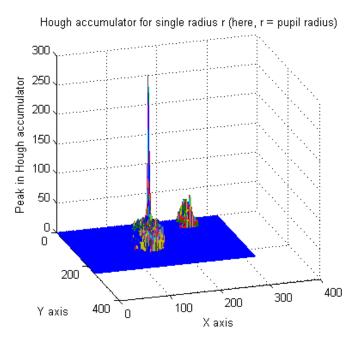

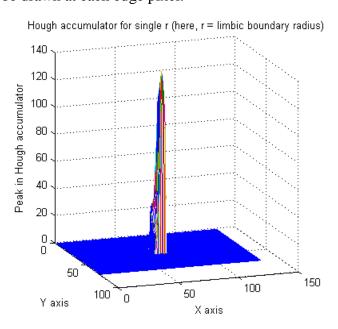

| Figure 4.10. The surface plot of the 2D accumulator array corresponding to one radius after voting 57               |

| Figure 4.11. Limbic boundary detection: (a) Iris image (320×240) after pupil boundary detection; the                |

| rectangle in white indicates the size of subimage to be processed for limbic boundary detection; (b) The            |

| subimage (130×65) extracted from the iris image using the rectangle in (a); (c) Filtered subimage after             |

| applying a median filter of size 9×9 on (b); the two rectangles in white on left and right sides of the pupil       |

| are used to cover the iris's vertical contours; (d) Edge-map obtained after applying Sobel edge detection           |

| without thinning in horizontal direction inside the two rectangles in (c); (e) Circle detection after applying      |

| the adaptive CHT on (d); (f) Iris localized image (320×240)                                                         |

| Figure 4.12. A set of two vertical arcs that the adaptive CHT finds in an image                                     |

| Figure 4.13. The surface plot of 2D accumulator array in the adaptive CHT corresponding to one radius               |

| after voting. [voting space is a 10×10 rectangle centered at pupil center]                                          |

|                                                                                                                     |

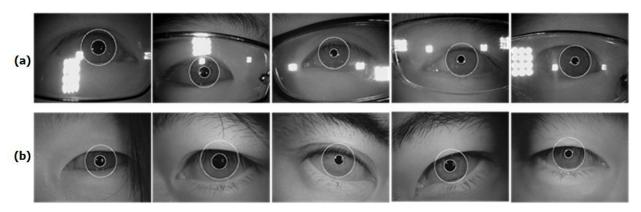

| Figure 4.14. Accurately localized irises in the iris images from two CASIA databases: (a) CITHV4; (b)           |

|-----------------------------------------------------------------------------------------------------------------|

| CILV3                                                                                                           |

| Figure 4.15. Examples of wrong pupil localization using thresholding based technique, which is corrected        |

| by the proposed technique                                                                                       |

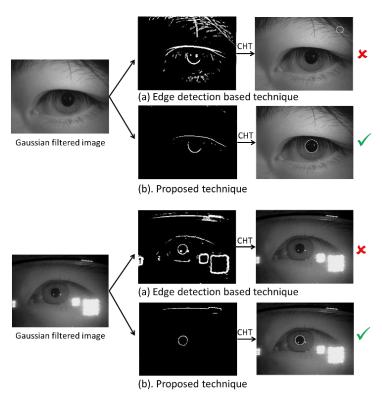

| Figure 4.16. Examples of wrong pupil localization using edge detection based technique, which is                |

| corrected by the proposed technique                                                                             |

| <b>Figure 5.1.</b> Pseudo code for voting process in general (direct) CHT algorithm                             |

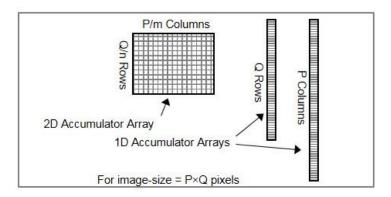

| <b>Figure 5.2.</b> Voting space structure in the proposed CHT                                                   |

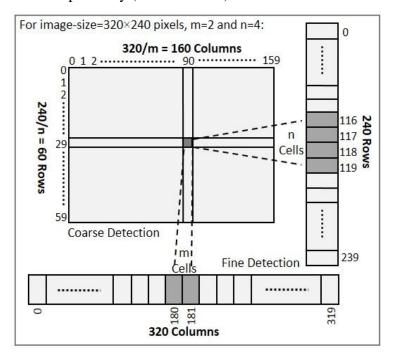

| <b>Figure 5.3.</b> Coarse to fine detection strategy for the circle center in the proposed CHT                  |

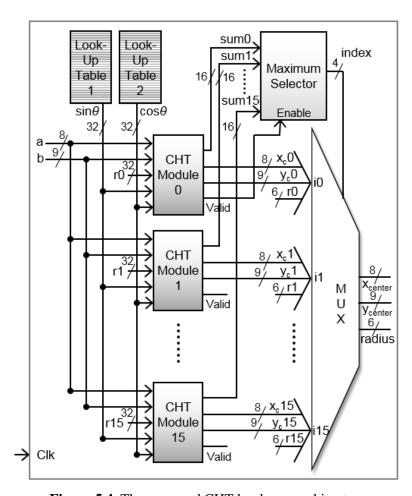

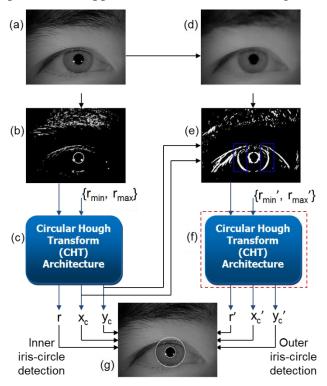

| <b>Figure 5.4.</b> The proposed CHT hardware architecture                                                       |

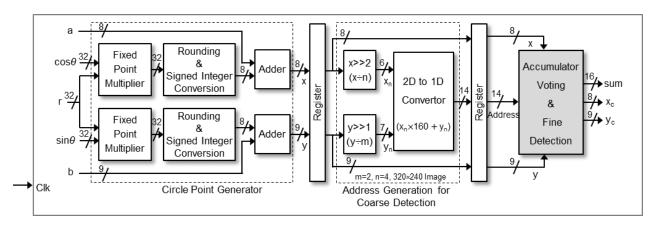

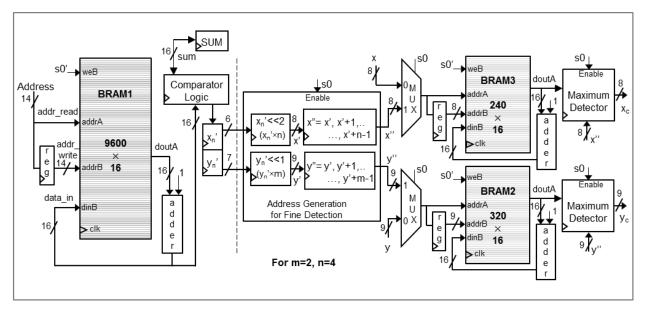

| <b>Figure 5.5.</b> Hardware block diagram of a single CHT module                                                |

| <b>Figure 5.6.</b> Accumulator voting and fine detection unit                                                   |

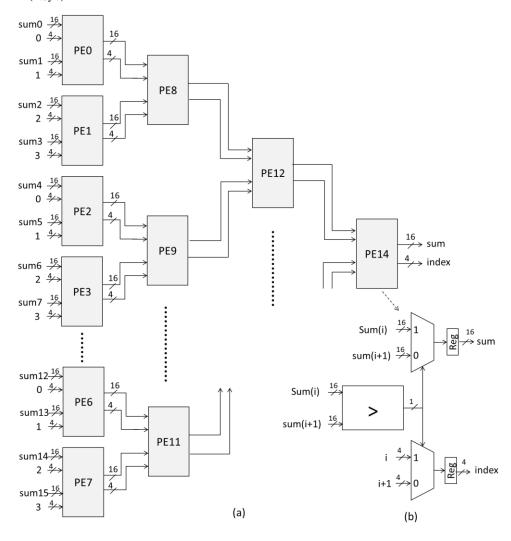

| Figure 5.7. Maximum selector: (a) Architecture; (b) Processing element (PE) used in (a)                         |

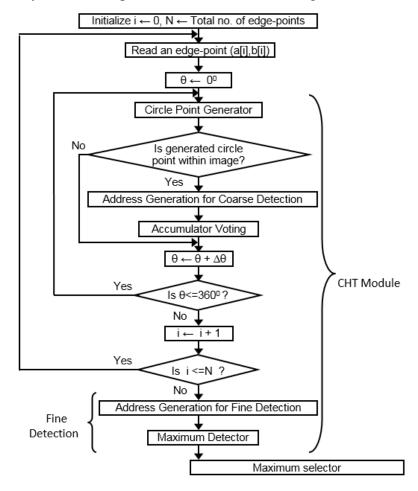

| <b>Figure 5.8.</b> Hardware control flow of the proposed CHT architecture                                       |

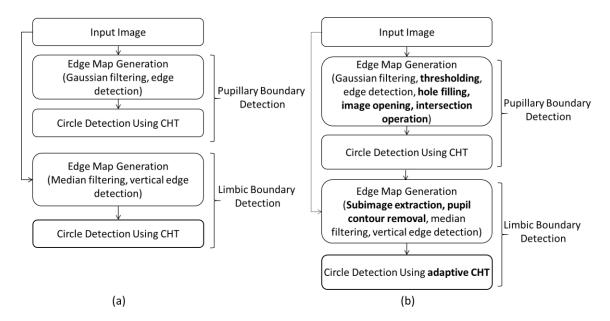

| Figure 5.9. Accuracy evaluation of the proposed CHT architecture: (a) Input iris image; (b) Edge-map for        |

| pupillary boundary detection obtained after applying Sobel edge detector without thinning on (a) in both        |

| horizontal and vertical directions; (c) CHT architecture to detect circle in (b); (d) Smoothed image of (a)     |

| obtained using median filter; (e) Edge-map of (d) obtained using vertical Sobel edge detector without           |

| thinning: The edge-points covered by two rectangles (in blue) are used for limbic boundary detection; (f)       |

| The CHT architecture used for pupillary boundary detection is used again for limbic boundary detection          |

| also                                                                                                            |

| Figure 5.10. (a) Testing of CHT hardware on FPGA; (b) Iris localized images using the proposed CHT              |

| architecture                                                                                                    |

| Figure 5.11. Accuracy comparison of the proposed CHT with the [Ngo et al., 2014] CHT for inner and              |

| outer iris-circle (iris-boundary) detection in CITHV4 and CIV1 images                                           |

| Figure 5.12. Edge-map generation technique for pupillary boundary optimized for hardware                        |

| implementation: (a) Original iris image (320×240) from CITHV4; (b) Gaussian smoothed iris image (σ              |

| =1.0, k=3); (c) Edge image obtained after applying Sobel edge detector without thinning on (b); (d)             |

| Binary image after applying intensity thresholding on (b); (e) Edge image obtained after applying Sobel         |

| edge detector without thinning on (d); (f) Edge-map obtained by intersection (logical ANDing) operation         |

| on (c) and (e)                                                                                                  |

| <b>Figure 5.13.</b> Proposed edge-map generation hardware architecture for pupillary boundary                   |

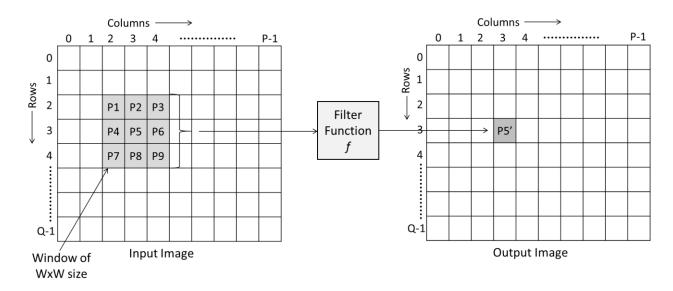

| <b>Figure 5.14.</b> Window filter. The shaded pixels represent the input window located at P5 that produces the |

| filtered value, P5' for the corresponding location in the output image. Each possible window position in        |

| the input image generates the corresponding pixel value in the output image                                     |

| <b>Figure 5.15.</b> Window based image filtering: (a) Filter kernel; (b) Pseudo-code of 3×3 convolution for     |

| image filtering using filter kernel of (a); (c) 3×3 image window.                                               |

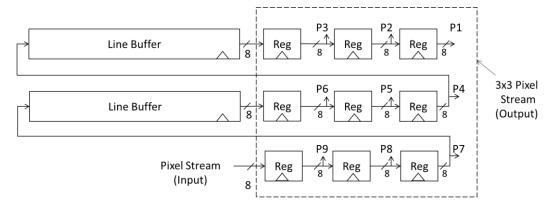

| Figure 5.16. 3×3 sliding window architecture.                                                     | 88              |

|---------------------------------------------------------------------------------------------------|-----------------|

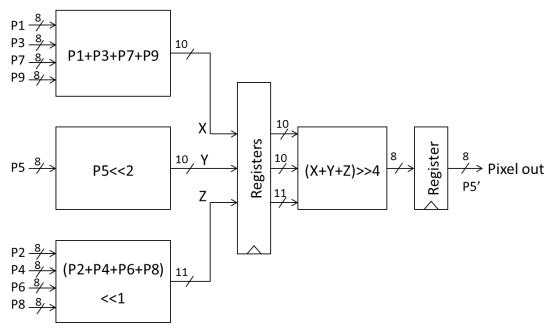

| Figure 5.17. Gaussian filter architecture.                                                        | 90              |

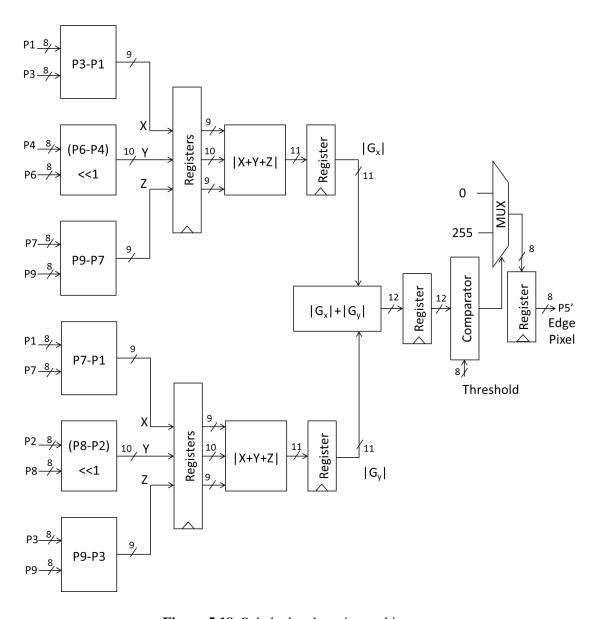

| Figure 5.18. Sobel edge detection architecture.                                                   | 91              |

| Figure 5.19. Image binarization hardware.                                                         | 92              |

| Figure 5.20. Set-up to test the edge-map generation hardware for pupillary boundary on FPGA       | 93              |

| Figure 5.21. Accuracy-test of edge-map generation hardware for pupillary boundary: (a) Test image | age; (b)        |

| Edge-map generated using the edge-map generation hardware executing on FPGA; (c) Ed               | lge-map         |

| generated using equivalent MATLAB code of edge-map generation hardware; (d) Difference imag       | ge of (b)       |

| and (c). The images (320×240) are taken from CITHV4 and CILV3 database.                           | 94              |

| Figure 5.22. Edge-map generation for limbic boundary: (a) Input image; (b) Median filtered im     | age; (c)        |

| Edge-map obtained using vertical Sobel edge detection                                             | 96              |

| Figure 5.23. Proposed edge-map generation hardware architecture for limbic boundary               | 97              |

| Figure 5.24. 5×5 sliding window architecture.                                                     | 98              |

| <b>Figure 5.25.</b> Working of 5×5 median filtering.                                              | 99              |

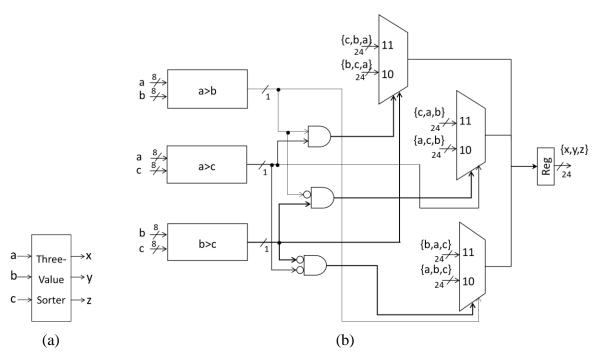

| <b>Figure 5.26.</b> Algorithm for finding median of 5×5 values.                                   | 100             |

| <b>Figure 5.27.</b> The proposed 5×5 median filter hardware architecture.                         | 101             |

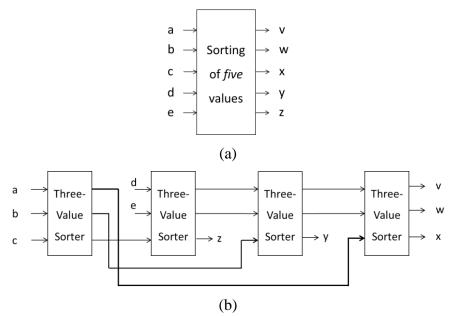

| Figure 5.28. Example of sorting of five values using a three-value sorter                         | 101             |

| Figure 5.29. Sorting of five values: (a) Sorting module; (b) Circuit that uses three-value sorter | 102             |

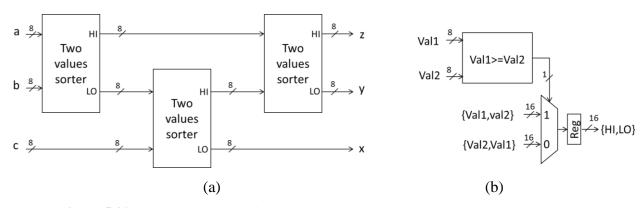

| Figure 5.30. Three-value sorter: (a) Conventional sorter; (b) Two-value sorter used in (a)        | 102             |

| Figure 5.31. Proposed three-value sorter: (a) Sorting module; (b) Circuit diagram                 | 103             |

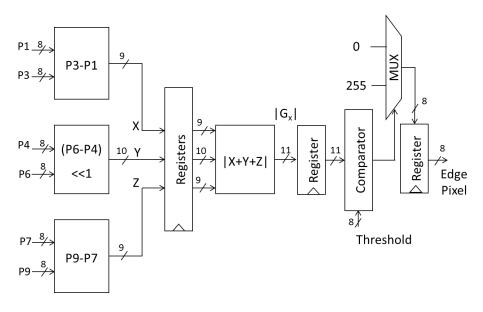

| Figure 5.32. Vertical Sobel edge detector                                                         | 104             |

| Figure 5.33. Accuracy-test of edge-map generation hardware for limbic boundary: (a) Test image    | age; (b)        |

| Edge-map generated using the edge-map generation hardware running on FPGA; (c) Edge-map ge        | enerated        |

| using equivalent MATLAB code of edge-map generation hardware; (d) Difference image of (b)         | and (c).        |

|                                                                                                   | 105             |

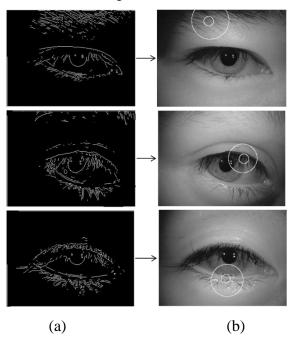

| Figure 6.1. Limbic boundary detection for VW images: (a) Original Image; (b) Smoothed imag        | e of (a)        |

| obtained using 5×5 median filter; (c) Edge-map for limbic boundary detection, obtained by a       | pplying         |

| vertical Sobel edge detector on (b) without thinning operation; (d) Limbic boundary detected      | 1 image         |

| obtained on applying adaptive CHT on (c).                                                         | 113             |

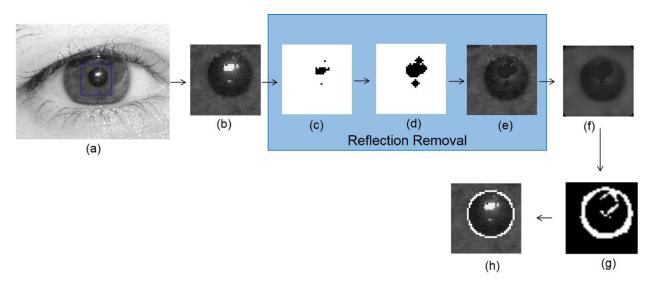

| Figure 6.2. Pupillary boundary detection for VW images: (a) Original image after limbic be        | oundary         |

| detection. The rectangle in blue contains the subimage to be processed for pupil boundary detect  | ion; <b>(b)</b> |

| The subimage extracted from (a); (c) Reflection map of subimage; (d) Enhanced-reflection map, or  | btained         |

| using dilation operation on (c) with circular structuring element of radius two; (e) Reflection   | ons free        |

| subimage; (f) Smoothed image after median filtering on (e); (g) Edge-map, obtained by applying    | ng both         |

| horizontal and vertical Sobel edge detection on (f); (h) Pupillary boundary detected image obtain | ed after        |

| applying CHT on (g).                                                                              | 114             |

| Figure 6.3. Images with wrong pupillary boundary detection.                                       | 115             |

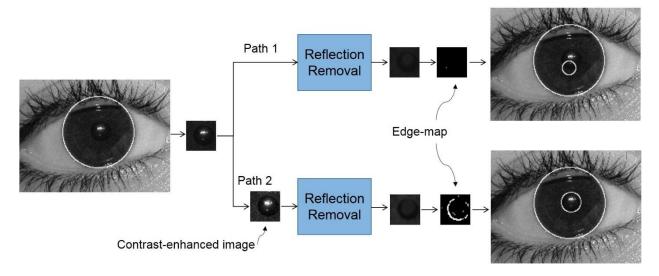

| Figure 6.4. Pupillary boundary detection corrected. Path 1 results in wrong detection of pupillar      |

|--------------------------------------------------------------------------------------------------------|

| boundary; Path 2 results in correct detection of pupillary boundary by introducing a contrast-enhance  |

| image                                                                                                  |

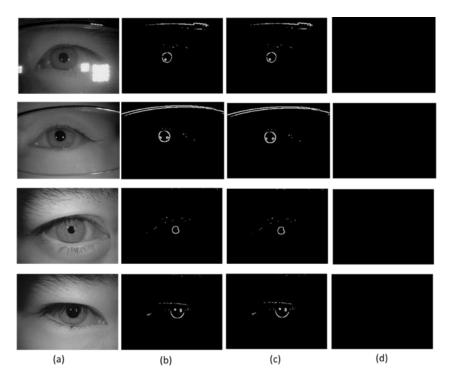

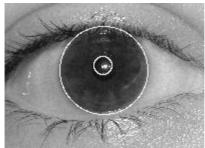

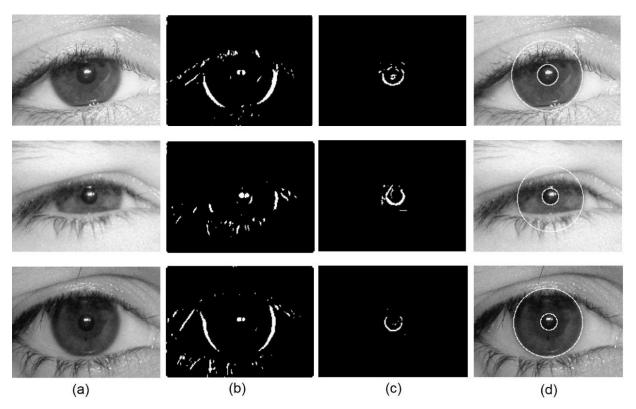

| Figure 6.5. Iris localization in 200×150 pixel images from UBIRIS.v1: (a) Original image; (b) Edge-mag |

| for limbic boundary detection; (c) Edge-map for pupillary boundary detection; (d) Iris localized image |

|                                                                                                        |

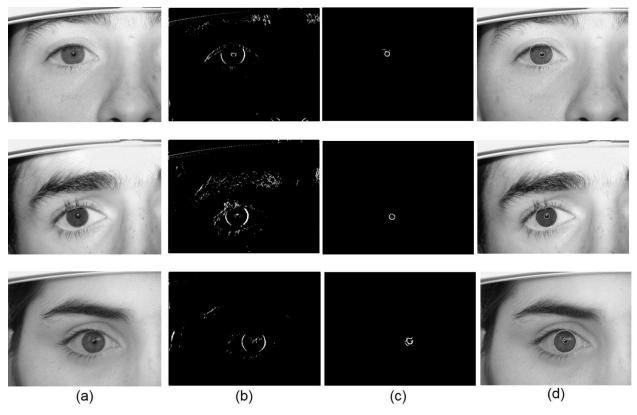

| Figure 6.6. Iris localization in 640×480 pixel images from UBIRIS.v1: (a) Original image; (b) Edge-mag |

| for limbic boundary detection; (c) Edge-map for pupillary boundary detection; (d) Iris localized image |

|                                                                                                        |

| Figure 6.7. Images with wrong iris localization by the proposed method.                                |

# **List of Tables**

| Table 2.1. Iris localization/segmentation methods                                                            | 31 |

|--------------------------------------------------------------------------------------------------------------|----|

| Table 3.1. Simulation results                                                                                | 13 |

| Table 3.2. Comparison of the results of proposed method with the published results for CITHV4 databa         | se |

| images                                                                                                       | 13 |

| Table 3.3. Comparison of accuracy of proposed method with published results (accuracy results in the         | he |

| table are taken from [Ibrahim et al., 2012])                                                                 | 14 |

| Table 4.1. Performance of Wildes' Approach (Simulation results)                                              | 50 |

| <b>Table 4.2.</b> Performance of the proposed iris localization method (Simulation results)                  | 53 |

| Table 4.3. Comparison of iris localization methods.                                                          | 54 |

| Table 4.4. Comparison with published iris localization results.    6                                         | 54 |

| Table 5.1. Memory requirements in the proposed CHT.                                                          | 59 |

| Table 5.2. Inner iris-circle (pupillary boundary) detection results                                          | 78 |

| Table 5.3. Outer iris-circle (limbic boundary) detection results.                                            | 78 |

| Table 5.4. Iris localization (inner + outer iris-circle detection) results                                   | 79 |

| Table 5.5. Synthesis results of the proposed CHT architecture                                                | 79 |

| Table 5.6. Utilization of number of block RAMs (synthesis results)                                           | 30 |

| Table 5.7. Processing time of the proposed CHT hardware architecture    8                                    | 31 |

| Table 5.8. Average processing time                                                                           | 32 |

| Table 5.9. Comparison of iris localization (inner + outer iris-circle detection) results                     | 33 |

| Table 5.10. Comparison with other CHT implementation                                                         | 34 |

| Table 5.11. Synthesis results of proposed edge-map generation hardware architecture for pupilla              | ry |

| boundary                                                                                                     | €  |

| <b>Table 5.12.</b> Clock cycle latency of the proposed edge-map generation hardware for pupillary boundary 9 | €  |

| Table 5.13. Processing time per image of the proposed edge-map generation hardware for pupilla               | ry |

| boundary                                                                                                     | €  |

| Table 5.14. Synthesis results of the proposed edge-map generation hardware for limbic boundary using         | ng |

| 5×5 median filter                                                                                            | )4 |

| Table 5.15. Synthesis results of the proposed edge-map generation hardware for limbic boundary using         | ng |

| 3×3 median filter                                                                                            | )5 |

| Table 5.16. Clock cycle latency of the proposed edge-map generation hardware for limbic boundary 10 |                    |

|-----------------------------------------------------------------------------------------------------|--------------------|

| Table 5.17. Processing time/ image of the proposed edge-map generation hardware f                   | or limbic boundary |

|                                                                                                     | 106                |

| <b>Table 5.18.</b> 5×5 window median filter architectures                                           | 107                |

| Table 5.19. Difference between the method used for iris localization hardware impl                  | ementation and the |

| proposed method described in chapter 4                                                              | 108                |

| Table 5.20. Accuracy results of iris localization methods                                           | 109                |

| Table 6.1. Variants of edge detection plus CHT based iris localization                              | 118                |

| <b>Table 6.2.</b> Comparison with published results for UBIRIS.v1 database                          | 119                |

This page was left blank intentionally.

### Chapter 1

# Introduction

#### 1.1 Iris Biometric System

In the recent years, the field of automated human identification have grown with advent of different types of biometric systems, such as fingerprint, face, iris, voice and hand etc., which use sensors, image processing, pattern recognition and computers [Jain and Kumar, 2012], [Faundez-Zanuy, 2006]. These systems identify or authenticate the individuals for security and access control purposes based on their biometric characteristics (physiological or behavioral). The authentication systems based on biometrics determine the user's identity on the principle that some physiological or behavioral characteristics are unique for each person and hence, provide absolute authentication. For example, no two persons have the same iris-patterns even the identical twins; also, the left and right eye irises of the same person are different. Moreover, the iris pattern remains stable and does not change throughout one's life provided no injury happens to the eye. In contrast to biometrics, traditional methods of authenticating persons based on (a) what they carry, such as identity card, driving license, passport and magnetic stripe card; and (b) what they know, such as username, passwords and pin number are less secured methods because they can be stolen, lost, forgotten, misplaced or forged. Automated biometric systems such as fingerprint or iris recognition have been successfully deployed in several large-scale public applications, increasing reliability and convenience for users and reducing identity fraud [Jain and Kumar, 2012].

An iris recognition system is a computer-assisted system that identifies individuals based on comparisons of iris-patterns [Ross, 2010]. The iris recognition is considered one of the most secure and reliable technologies among currently existing biometric modalities and finds application where high level of security is required, such as countering terrorism or providing access control for accessing important information. The iris recognition system consists of an automatic iris segmentation system that extracts the iris region from eye image. The extracted iris

region is then unwrapped into a rectangular block with constant dimensions. The iris features are extracted with a feature extraction method to encode the unique pattern of the iris into biometric template. The generated iris template is compared with the previously stored (recorded) iris templates to find a match based on a match-threshold.

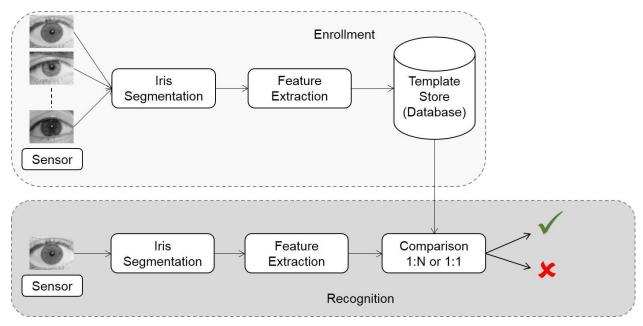

The two processes are involved in the use of biometric systems as shown in Figure 1.1: (a) enrollment and (b) recognition (verification). The enrollment is a process of creating the biometric template and storing it in the template store (database), whereas comparison (template matching) is done in recognition process in addition to the template creation. The enrollment for a user is generally done once and recognition is done every time a security check is performed.

**Figure 1.1.** Functioning of iris biometric system.

A biometric system is used to perform two kinds of recognition tasks [Liu-Jimenez et al., 2011], [Faundez-Zanuy, 2006], [Bowyer et al., 2008]: (a) identification; and (b) authentication. These tasks are also known as modes of operation of a biometric system. In identification mode, the user does not provide any user identity (e.g. card or identification (ID) number) and the biometric system finds the user from a database of biometric data (templates). This process carries out a maximum of 1:N comparisons of the input template (biometric data) with the *N* templates stored in the database. In contrast to identification, authentication mode involves 1:1 comparison to recognize a user, but the user has to provide either his biometric data in form of a smart card (biometric token) or an ID number referring to his template stored in the database. Therefore, a biometric system for authentication task can be designed using two approaches [Liu-

Jimenez et al., 2011]: (a) online, which requires communication with central databases to access biometric data; and (b) offline, wherein biometric data is stored on personal biometric tokens. The online approach must deal with serious security and privacy issues, as the communication between the system and the central database can be attacked, and the identity may be stolen or altered. For this reason, offline systems are recommended, as long as the data is kept securely in the personal biometric token.

#### 1.2 Motivation and Scope

#### A) Motivation

The iris recognition systems are available as both stationary devices (usually equipped with standard personal computers (PCs)) and portable devices, but usually the implementation of iris recognition algorithms is carried out using high-performance serial microprocessors working at clock frequencies in the GHz range. These devices are designed with an advanced architecture based on several pipeline stages, cache memory, high-speed communication buses and additional units that facilitate rapid execution of complex algorithms. However, such software implementations could restrict the application of biometrics to specific markets because of the microprocessor cost, complete system cost, system size and high power consumption. In order to spread the biometric security, it is needed to develop the embedded biometric systems that can be easily integrated into any kind of product such as mobile phones, automatic teller machines, laptops, personal digital assistant devices, access control systems, etc. It is worth to emphasize that realization of iris recognition using reliable and handheld embedded systems remains an open problem in the biometrics because of the complexity of the computational tasks [Grabowski and Napieralski, 2011].

Devices available in the low-cost consumer market are generally too slow for applications requiring intensive computations. For example, an iris recognition algorithm running on an ARM922 T at 160 MHz executes in 3162 ms, which is about 80 times slower than the execution of the same code on a high-performance microprocessor [Lopez et al., 2011]. The use of dedicated hardware is an alternative for implementing operations that require high-speed parallel processing. For example, under certain conditions, an image enhancement routine usually employed in a fingerprint recognition algorithm can be processed in dedicated hardware faster than on a Pentium clocked at a frequency 30 times higher [Lopez et al., 2011]. However, the speed benefits are obtained at the cost of chip area and design efforts. Designing a dedicated

hardware solution may not be justifiable always specifically for the algorithms that majorly contain sequential operations and hinder the parallel and pipelined implementation. Therefore, sometimes, an embedded system architecture based on dedicated hardware units and serial microprocessor called as hardware-software (HW-SW) co-design can provide the optimized solution as described in [Lopez et al., 2011] for iris recognition application. However, sometimes, the complete algorithm can also be implemented using dedicated hardware units without using HW-SW co-design approach [Liu-Jimenez et al., 2011].

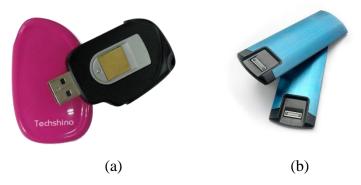

**Figure 1.2.** Personal biometric tokens: (a) Techshino fingerprint USB token; (b) Fingerprint-based HYPR Biometric OTP.

Sources: (a) http://www.techshinobiometrics.com (b) https://www.hypr.com

An important and interesting application of small size, light weight and low power embedded iris recognition systems is token-based biometric systems that falls in the category of the offline biometric authentication, where the biometric data is stored in a smart card (token) instead of the centralized database [Liu-Jimenez et al., 2011]. The two different types of personal biometric tokens are used in offline biometric authentication: 1) the token only provides the biometric template of a person stored in it and does not perform the task of authentication; and 2) the token not only provides the biometric template, but also performs the authentication (verification) task and supplies the result. The tokens of second type avoid the external access to the user's biometric template, which is a better strategy for security and privacy point of view. Such tokens (second type) for fingerprint biometrics are available in the market having Universal serial bus (USB) interface or Bluetooth enabled communication with host machine (Figure 1.2). The Bluetooth enabled token is also known as biometric one time password (OTP), which is used for log in purpose as an alternative of traditional username and password-based log in. These are being used for access control in the applications such as online banking, mobile payments, electronic trading and computer unlocking. These tokens provide password-less authentication while improving users' experience, but they are also being used as an additional security check along with traditional username and password, personal identification number (PIN) or OTP based authentication. For example, OTP is generated only when biometric check is passed using the token. USB token and biometric OTP (Bluetooth dongle) produced by Techshino and HYPR companies respectively are shown in Figure 1.2 having about size of today's pen drives. USB token is a compact plug and play design; can be used instantly upon insertion, empowered with on-device template matching and extendable fingerprint template storage that is can be used more than one persons.

These fingerprint tokens (Figure 1.2) are embedded system comprising of mainly a sensor and low power microprocessors to do the computations. Such biometric tokens for fingerprint biometrics are available in market, but are not yet developed for iris biometrics; the reason being that the fingerprint trait has higher acceptability rate [Jain et al., 1997]. The acceptability measures the people's acceptance level for the use of a biometric trait in their daily lives. The development of biometric token based on iris trait is current topic of research. The authors in [Liu-Jimenez et al., 2011] have proposed an optimized hardware solution for development of such iris biometric tokens, which is a dedicated hardware design on field programmable logic array (FPGA) as discussed later in chapter 2. However, it has limitations of reduced accuracy and not implementing iris segmentation task. The issues in the development of tokens-based complete biometric systems are low computational power (processing capability), less space and limited resources.

In the development of aforementioned embedded iris recognition systems, the usage of FPGA based platform plays an important role due to inexpensive nature for development, optimizing feasibility, reconfigurability and shorter time-to-market.

#### B) Scope

This thesis focuses on the iris localization stage of iris recognition system. The work carried out in the thesis can be divided in two parts. The first part of thesis describes the iris localization algorithms for localizing irises in less constrained images captured under near infrared (NIR) light. These algorithms show improved performance in terms of accuracy and time performance. The second part of thesis presents the dedicated hardware implementation of iris localization task on FPGA. This dedicated hardware for iris localization can work as a hardware accelerator in the embedded iris recognition systems, such as a biometric token, which may be having a low speed and low power CPUs operating in MHz. The hardware module for iris localization can be used in

such systems to meet the real-time performance. The thesis also presents preliminary work towards hardware implementation of iris localization for visible wavelength (VW) images.

Iris localization was chosen because it is the slowest process among all the stages in an iris recognition algorithm provided that the template database is not too large, otherwise template matching stage may become the slowest process [Lopez et al., 2011], [Grabowski and Napieralski, 2011]. The iris localization is very first stage in iris recognition that is performed on the captured eye image, therefore, its accuracy affects the stages following it and a wrong iris localization will fail the whole process of recognition. This thesis describes the algorithms for iris localization that are accurate and fast. However, only one selected algorithm is used for hardware implementation due to its reduced complexity in terms of memory requirement and yet offering more accurate and faster localization. This thesis work offers solution to one of the problems that is a dedicated hardware implementation for iris localization task, which can help in improving the speed and accuracy of iris recognition systems.

#### 1.3 Objectives of Thesis

The objectives of this thesis were set after literature review and identification of research gap in the existing work, which is described in chapter 2. The main objectives of this thesis are:

- 1. To explore and improve the performance (speed and accuracy) of iris localization algorithms for NIR images in presence of image noise, such as eyelids and eyelashes occlusion, lighting reflections, non-uniform illumination, low contrast and eyebrow hair.

- 2. Comparison of results with previous iris localization algorithms and testing of the algorithms for different NIR image databases.

- 3. To implement selected algorithm on FPGA after algorithm optimization, which will work as dedicated hardware or hardware accelerator for iris localization. Comparison with previous work for hardware implementation of iris localization.

- 4. Preliminary work towards hardware implementation of iris localization for VW images.

#### 1.4 Workflow

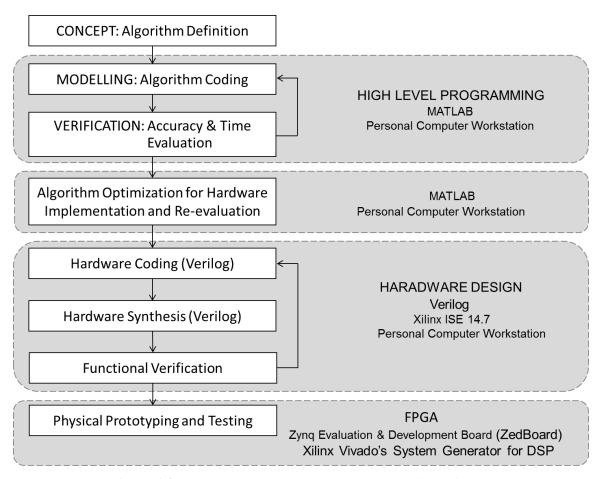

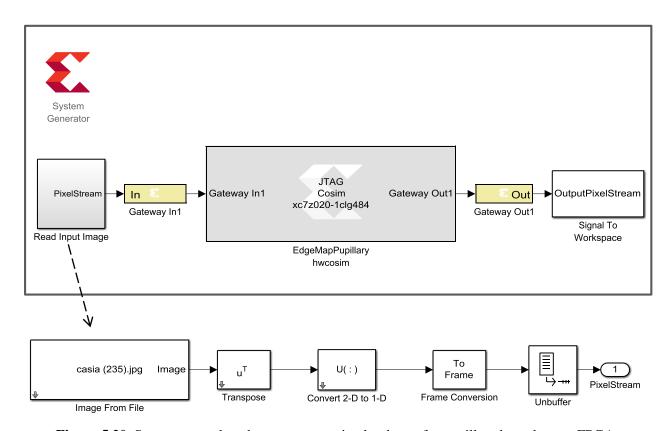

The task of algorithm development and its hardware implementation in this thesis was accomplished using the flow described in Figure 1.3. This flow was used for all the tasks as simple as edge-detection or as complex as circle detection in an image. Three main stages were used to carry out the work in this thesis:

1. In the first stage, a thorough study of existing algorithms was done for the iris localization task and then we have proposed algorithms to achieve better accuracy and time performance. The implementations of these algorithms were done using high-level computing and programming language; and MATLAB was used for algorithm coding, data visualization and performance evaluation under a personal computer platform. The built-in MATLAB functions for image processing, such as 'edge ()' for edge detection were also used while coding the algorithm. After the initial composition of the algorithm, as set of iterative loops is carried out in order to tune the algorithm to the properties of accuracy and speed.

**Figure 1.3.** Algorithms and hardware development flow of thesis.

2. In second stage, the algorithm proposed in stage 1 was optimized for its hardware implementation by using steps, such as the optimized algorithm may be using reduced filter size for making the hardware resource efficient. The optimized algorithm was coded in MATLAB and its accuracy was evaluated to compare with the original algorithm proposed in stage 1. The optimized algorithm was again coded in MATLAB, but this time

- the built-in functions of MATLAB were not used. For example, we wrote the code for convolution operation for performing edge detection on image instead of using built-in function 'edge ()' of MATLAB.

- 3. In third stage, the flowchart of the algorithm was explored, main functions (operations) were identified and its hardware architecture was drawn with pen and paper, which was then modelled using Verilog Hardware Description Language (HDL). The hardware design had to go through a number of iterations to meet the functionality of the algorithm. After that, synthesizable design was ported on the FPGA for testing.

#### 1.5 Organization of Thesis

This thesis is organized in seven chapters. After the introductory chapter, which presents the research topic and the main scope of this work, the thesis addresses each one of the following aspects in the next chapters.

Chapter 2 provides the literature review on iris recognition and embedded system development for iris recognition; and explores research gap, which helps in framing objectives of this thesis. This chapter also describes in detail the existing algorithms of iris localization and the main techniques used in iris localization. The existing work on FPGA based hardware implementation of iris localization has also been reviewed.

Chapter 3 discusses the iris localization based on integro-differential operator (IDO) and describes a method proposed by us that uses IDO to localize iris boundaries in the images captured under NIR light and contain significant noise. The method has been evaluated for its accuracy and time performance, and also compared with the previous methods. The algorithm was coded and tested in MATLAB installed on a personal computer (PC).

Chapter 4 describes the iris localization based on circular Hough transform (CHT). This chapter discusses implementation of Wildes' approach [Wildes, 1997] and a new method proposed by us for less constrained NIR images. The extensive evaluation of the algorithms has been done on different databases and results are compared with the existing algorithms. The algorithms were coded and tested using MATLAB on a PC platform.

Chapter 5 is devoted to the hardware implementation of an iris localization algorithm based on CHT for NIR images. The algorithm was first optimized for hardware implementation and impact of optimization has been evaluated. The hardware simulation and synthesis results targeting Xilinx's Zynq 7000 FPGA device are presented.

Chapter 6 describes the preliminary work towards hardware implementation of iris localization for VW images. We have proposed an iris localization algorithm for VW images, which is optimized for hardware implementation.

Chapter 7 concludes the thesis and presents the research contributions of this thesis. This chapter also discusses about the future directions of the work presented in the previous chapters.

#### 1.6 Concluding Remarks

This chapter has introduced the research field of this thesis. The scope of development of new embedded systems for iris recognition, such as a biometric token, has motivated to carry out this thesis work to support such systems. The scope of this thesis has been discussed, which is about iris localization stage. Finally, the work methodology used in this thesis and focus of the different chapters was described.

### Chapter 2

# **Literature Review**

This chapter first discusses the literature review on iris recognition, the various stages of iris recognition and embedded systems for iris recognition. This preliminary literature review helped in identifying iris localization stage as a main research gap, which is the major hurdle in improving the performance of the embedded iris recognition system; and also helped in setting up the objectives of the thesis. Subsequently, a detailed literature review on iris localization algorithms and its hardware implementation has been presented.

#### 2.1 Iris Recognition

The iris recognition technique is used for automatic identification (or authentication) of persons by converting their irises into mathematical representations. An iris has features that make this modality appropriate for recognition purposes. This section presents an introduction to iris recognition and provides a literature review on the techniques that are being used in iris recognition systems.

#### 2.1.1 Structures of Eye and Iris

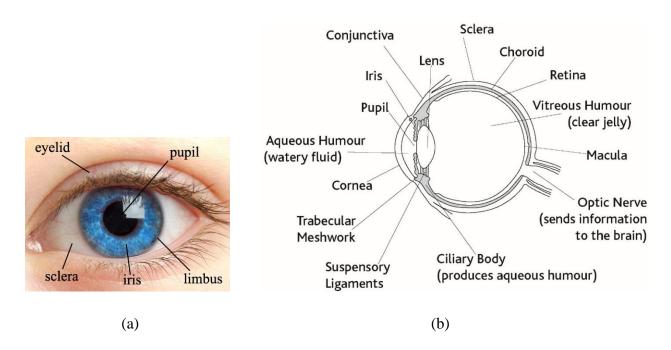

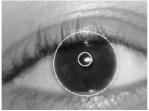

In this subsection, we start with the description of the human eye structure, followed by a detailed description of the iris. The detail of the iris structure is necessary to know, since it becomes important to understand these for an iris based automatic identification process. Figure 2.1(a) shows the location of iris in a captured eye image. The iris is a ring-like structure fitted between pupillary and limbic boundaries and it is surrounded by sclera, pupil, eyelids and eyelashes.

#### A) Structure of Eye

The human eye is a ball-like structure as shown in Figure 2.1(b). The sclera is a tough, white and opaque outer coat of eye and the surface of sclera is covered by a thin skin layer called the conjunctiva. The front part of the eye, where the outer coat of eye is transparent, is called the cornea and behind the cornea is the iris. The iris is the colored part of the eye and it has the pupil at its center forming a hole. The most important function of the iris is that it controls the size of the pupil with help of its muscles. The size of pupil is sensitive to the light entering the eye. The pupil becomes larger in the dim light and smaller in the bright light. The light passes through the lens that helps focus the light from the pupil onto the retina. The light that has passed through the cornea and pupil now passes through the lens that helps focus the light onto the retina. The retina is light sensitive layer inside the back of the eye on which what is being seen is focused. The retina has high density of light-sensitive cells at its center and this part of retina is called macula. The photoreceptor cells of retina coverts light into a series of electrical signals. These signals pass to the brain via optic nerve, where the final image is processed.

**Figure 2.1.** Human eye: **(a)** Location of iris in eye image; **(b)** Structure of human eye. Source: http://www.glaucoma-association.com/about-glaucoma/the-eye

The space between the retina and lens is filled with vitreous humour through which the light passes to the retina. Also, there is an aqueous humour filled between cornea and the lens

that maintains the pressure of eye. The aqueous humour is produced by ciliary body. The layer of eye under the retina is choroid that provides the blood supply to the retina cells.

#### **B)** Visible Features of Iris

The tissue of the iris is soft and loosely woven and it is called stroma [Muron and Pospisil, 2000]. The density of stroma is one of the factors that determine the color of iris. The visible pattern of iris displays various distinctive features. The whole surface of the human iris is divided into the pupillary area and the ciliary area as shown in Figure 2.2(a). The collarette represent the zigzag boundary between the pupillary area the ciliary area and it is the thickest part of the iris. A few of the visible features of the human iris are shown in Figure 2.2(b), which are important features used for identifying a person. These are mainly pigment related features, features controlling the size of the pupil, pigment frill and collarette.

**Figure 2.2.** Human iris: **(a)** Picture of human iris.; **(b)** Visible features on surface of the human iris: 1-Pigment frill, 2-Pupillary area, 3-Collarette, 4-Ciliary area, 5-Crypts, 6-Pigment spot, 7-Concentric furrows, 8-Radial furrows.

Sources: (a) John Daugman's home page: https://www.cl.cam.ac.uk/~jgd1000; (b) [Muron and Pospisil, 2000].

The crypts and the pigment spots belong to the pigment related features. The crypts are very dark colored areas and the iris is relatively thin in these areas. They appear like sharply demarcated excavations and their presence is near the collarette or/and the periphery of the iris. The pigment spots are called as moles and freckles having nearly black colour. They are random

concentrations of pigment cells and generally appear in the ciliary area [Muron and Pospisil, 2000].

The iris features that control the size of the pupil are radial and concentric furrows. These furrows are called contraction furrows. The radial furrows may start near the pupil and extend in the ciliary area through the collarette. The concentric furrows are generally circular and concentric with the pupil. These furrows appear in the ciliary area and near the periphery of the iris. The pigment frill represents the boundary between the pupil and the iris.

The iris grows from the ciliary body and its colour is given by the amount of pigment and by the density of the iris tissue, which means from blue to black.

#### 2.1.2 Iris as a Biometric Trait

The properties of the iris that enhance its suitability for use in high confidence identification systems are discussed in this section [Daugman, 1993], [Daugman, 2004]. The advantages and disadvantages of using iris as a biometric identifier are discussed below.

#### **Advantages:**

- 1. Iris is a highly protected, internal organ of the eye. It is inherently isolated and protected from the external environment. It is impossible to surgically modify it without unacceptable risk to vision.

- 2. Iris is stable throughout the person's life. The human iris begins to form during the third month of gestation. The structure is complete by the eighth month of gestation. However, the pigmentation continues into the first year after birth.

- 3. There is high level of randomness in iris pattern (structure), which makes the iris unique for each person and hence, a reliable automatic biometric identifier.

- 4. A live detection test of iris can be performed with ease to avoid spoofing of the system using a photograph or video of iris, because the iris responds to the light and the changing size of pupil confirms natural physiology.

- 5. Images of the iris are adequate for personal identification with very high confidence. They can be acquired from distances of up to about 3 feet.

- 6. The iris image is captured at some distance from a subject without physical contact, which makes the identification process unobtrusive.

- 7. There is no genetic determination of iris pattern. The identical twins have different iris patterns; and the left and right eye irises of the same person are also different.

#### **Disadvantages:**

- 1. Iris is a small target to capture from a distance (>1m).

- 2. Iris is a moving target in non-cooperative iris recognition, which is difficult to acquire.

- 3. Iris is obstructed by eyelids, eyelashes and reflections that make the automatic iris recognition algorithms more complex.

- 4. NIR illumination is preferred to capture the iris; illumination should not be visible or bright.

#### 2.1.3 Iris Image Acquisition

Image acquisition set up determines quality of the iris image data. Different choices of the camera sensor, lens, illumination and capture distance will result in data of varying quality [Wildes, 1997]. Almost all commercial iris recognition systems are using near infrared (NIR) illumination sources and NIR cameras. This is because color cameras are not as effective as NIR cameras in terms of capturing the textural information in iris. Visually dark brown (almost black) irises do not display much color variation and thus contain almost no information useful for iris recognition. Due to the requirement to be low cost, the iris recognition systems often involve inexpensive and thus low quality sensors and optics. This considerably limits capture distances as well as quality of captured data. In order to protect the eye from overheating and thus from damage, the strength of the NIR illumination is required not to exceed a predetermined threshold [Matey et al., 2006]. As was mentioned before, the NIR iris images are traditional input to iris recognition system, but in recent years, biometricians turned their attention to visible wavelength (VW) iris images acquired in the visible band of electromagnetic spectrum [Proenca et al., 2010]. This trend is supported by a variety of factors: (1) optical cameras in visible range are cheap and characterized by a very high resolution; (2) these cameras may capture face or iris images from a longer distance, which further may be used to authenticate a suspicious or violent individual; (3) today's smartphones would not need additional NIR camera for running iris recognition application; (4) the NIR wavelength may be hazardous because the eye does not instinctively respond with its natural mechanisms (aversion, blinking, and pupil contraction) [Proenca, 2010].

#### 2.1.4 Iris Image Database

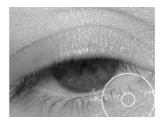

This section describes a number of iris image databases that are public and free available online. These databases are being used in the research on iris recognition to evaluate the performance of algorithms developed for this application. These databases have been developed under two different types of illuminations: (1) NIR; and (2) VW. The images in different databases contain different level of obstructions and noises, such that an algorithm giving accurate results for one database may not be accurate for other database [Bowyer et al., 2008].

Some of the databases have been developed under constrained environment and with user's full cooperation. For example, these database images have minimum obstructions by eyelids and eyelashes, reflections confined to pupil area only, uniform illumination and frontal view that is user was looking straight towards camera while capturing the image, etc.

A few databases have been developed under unconstrained environment and contain nonideal images, such as the images having the reflection spots appearing anywhere in the image, eyeglasses, non-uniform illumination, low contrast and heavy obstructions by eyelids, eyelashes and eyebrow etc. One more type of non-ideality is that the images have the off-angled irises (non-frontal view), which are captured while the user is not looking straight towards the camera.

The quality of the iris images decides both complexity and accuracy of the iris recognition algorithms [Bowyer et al., 2008]. The most popular NIR and VW image databases that are being used to evaluate today's iris recognition algorithms are described below.

#### A) NIR Image Databases

Most of the available iris image databases are the NIR images [Bowyer et al., 2008] because iris patterns are well pronounced in these images. The most commonly used NIR image databases are the CASIA Iris Image Databases (CASIA-Iris), which were developed by the Center of Biometrics and Security Research group in China [CASIA Iris Database]. The four versions (sets) of databases, CASIA-IrisV1 to CASIA-IrisV4, have been released by this research group since 2002 and each set has different subsets also. Up to thousands of images are contained in a subset, for example a subset CASIA-Iris-Thousand, version 4.0 (CITHV4) database contains 20000 images collected from 1000 persons and a subset CASIA-Iris-Lamp, version 3.0 (CILV3) database contains 16212 images from 811 persons.

The examples of other NIR databases are Multimedia University (MMU), Iris Challenge Evaluation (ICE)-2005, West Virginia University (WVU) and Indian Institute of Technology Delhi (IITD) databases. The summary of these databases except IITD database are provided in [Bowyer et al., 2008], where the information regarding the image capturing device (camera), size of database, way to get the database and links to download the database are given. A few sample images from these databases are shown in Figure 2.3. The two versions of the MMU database are

available: (1) Multimedia University, version 1.0 (MMUV1); and (2) Multimedia University, version 2.0 (MMUV2).

**Figure 2.3.** Sample images from NIR databases: (a) CASIA-Iris-Interval, version 3.0; (b) CASIA-Iris-Lamp, version 3.0; (c) CASIA-Iris-Thousand, version 4.0; (d) MMU, version 2.0; (e) ICE-2005; (f) WVU (off-angle image); (g) IITD, version 1.0.

The iris images from the NIR databases can be categorized into two types: (1) High close-up and constrained iris images, such as CASIA-Iris-Interval, version 3.0 database images (Figure 2.3(a)); and (2) Medium close-up and less constrained iris images, such as CITHV4 database images (Figure 2.3(c)).

#### **B) VW Image Databases**

The most famous iris image database developed under visible wavelength illumination is University of Beira Interior iris database (UBIRIS) [UBIRIS Image Database]. It was developed with the purpose that this database would work as a helping tool to evaluate the feasibility of visible wavelength iris recognition. First version of UBIRIS was released in 2004 and is called

UBIRIS.v1 [Proença and Alexandre, 2005], whereas the second version, UBIRIS.v2 [Proenca et al. 2010] was developed in 2009. These databases are public and free available. The example images from these databases are shown in Figure 2.4.

Figure 2.4. Sample images from VW databases: (a) UBIRIS.v1; (b) UBIRIS.v2.

The UBIRIS.v1 database is composed of 1877 images collected from 241 eyes. These images were acquired under less constrained imaging conditions as compared to UBIRIS.v2. The UBIRIS.v2 database has over 11000 images (and continuously growing) and it contains more realistic noise factors. The images in this version were captured at a distance and on the move.

#### 2.1.5 Stages of Iris Recognition

The typical stages of an iris recognition algorithm are shown in Figure 2.5. The rectangular boxes in this figure denote the different stages and function performed in each stage is written in the box. The first stage of an iris recognition algorithm is iris localization, which takes input from image acquisition system that deals with capturing the eye (iris) image using a digital camera as discussed before. In the iris localization stage, the inner (pupillary) and outer (limbic) boundaries of the iris are detected. The localized iris is then converted to a fixed size rectangular strip to compensate variations in pupil size and in the image capturing distances. This step is known as iris normalization. The iris is generally occluded by the eyelid (s) in the captured image; hence,

an eyelid detection step is carried out after the iris localization, so that the eyelid(s) can be avoided in further processing. The eyelid detection step combined together with the iris localization stage is also called iris segmentation. The normalized iris acts as the input for feature extraction stage. The feature extraction is a process that creates the binary template of iris. This process is known as isolation of distinctive features and the encoding phase. The final stage of iris recognition is template matching in which the comparison between the iris templates is made, producing a numeric dissimilarity value (d). If this value (d) is lower than a threshold (t), the system outputs a decision of match found, which means that both templates were extracted from the same iris. Otherwise, the system outputs a decision of match not found, meaning that the templates belong to different irises. The matching stage is required to do 1:1 (one is to one) comparison or 1:N (one is to many) comparisons depending on the mode of operation of iris recognition system that is verification or identification respectively as discussed in section 1.1 of chapter 1.

Figure 2.5. Stages of an iris recognition system.

Having defined the different stages of iris recognition system, these stages are described next in detail and a review on the most relevant approaches to perform each stage has been discussed.

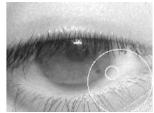

#### A) Iris Localization

The purpose of iris localization is to locate the iris in the eye image for further processing. Iris localization is a very important stage in iris recognition systems because all the subsequent stages

depend on its accuracy. The pupillary and limbic boundaries of iris are considered as two circles in the frontal view (zero off angle) images, but these circles are not necessarily concentric. The frontal view images are obtained when user looks ahead towards the camera while capturing the images. Most of the iris localization methods model iris as a set of two non-concentric circles, but presence of different kinds of noise in the eye images, such as lighting reflections, occlusions by the eyelids and eyelashes, eyeglasses, low contrast and eyebrow hair etc., make iris localization difficult.

The iris localization methods in the commercial iris recognition systems are typically based on Daugman and/or Wildes's algorithms [Daugman, 1993], [Wildes, 1997]. Daugman proposed an integro-differential operator (IDO) that acts as a circular edge detector to localize the iris boundaries, whereas Wides' method uses the Hough transform (HT) to detect the circular edges. However, these iris localization methods work under the controlled environments and their performance deteriorates when dealing with the noisy data [Jan et al., 2014]. After Daugman and Wildes's methods, the researchers have proposed several iris localization methods with the improved accuracy and speed for different databases. Some of the methods are tabulated in [Shah and Ross, 2009], which shows that most of the iris localization methods still use the HT and IDO based techniques along with additional steps to improve the performance of previous algorithms. Some of the recent methods to localize the irises in the NIR and VW images are described in [Jan et al. 2012], [Jan et al., 2014], [Wang et al., 2014], [Zuo and Schmid, 2010] and [Li et al., 2010], [Proenca, 2010], [Sahmoud and Abuhaiba, 2013] respectively.

The more detailed review on existing iris localization methods has been presented in section 2.4 later in this chapter.

#### B) Eyelid Detection and Iris Normalization

#### i) Eyelid Detection

The upper and/or lower eyelids(s) may be occluding the iris in the eye images. One of the solutions to this problem is that exclude the upper and lower most parts of each iris that is expected to be covered by eyelids, which is done after the iris localization step. The eyelids are checked for their presence within the localized iris, so the region of interest for eyelid detection is inside the limbic boundary. The Daugman's IDO can also be used to detect the eyelids by changing path of contour search from circular to arculate [Daugman, 1993]. The upper and lower eyelids are also modelled as parabolic arcs as suggested by [Wildes, 1997], where the eyelids are

detected by using a HT based technique. The other methods for eyelids detection are based on parabola polynomial fitting [Basit and Javed, 2007], line fitting and line detection based on HT approach [Masek and Kovesi, 2003].

#### ii) Iris Normalization

The purpose of iris normalization step is to prepare appropriate input for the feature extraction stage. The different images of the same eye have different sizes of the iris because the distance between the user and image capturing device (camera) can vary. Moreover, the pupil size also varies on varying intensity or position of lighting source, which causes variations in the iris patterns of same eye. Therefore, a proper normalization technique is required to compensate these variations. The circular ring-like iris is unwrapped into a fixed size rectangular strip in the iris normalization step, but the iris boundaries are not concentric circles, which increases the complexity of this process. The most common methods for iris normalization are based on rubber sheet model [Daugman, 2004], which is used to counter the size variations of irises as discussed above.

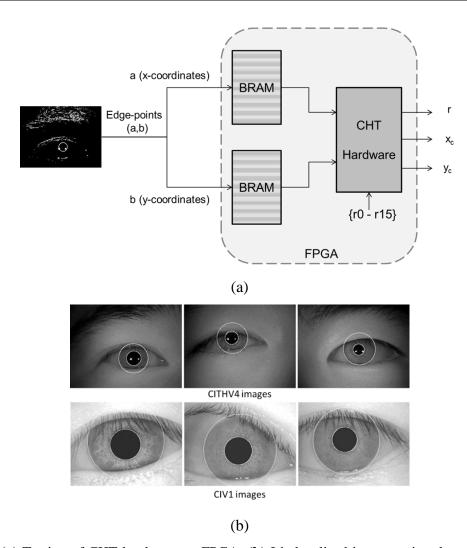

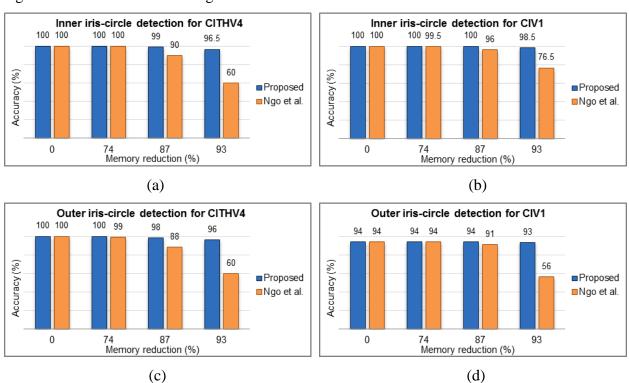

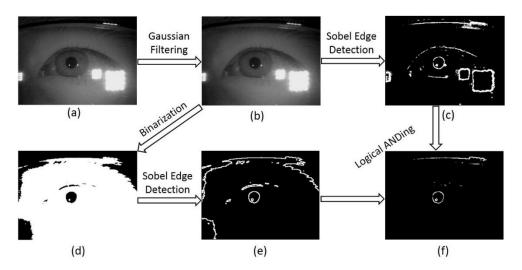

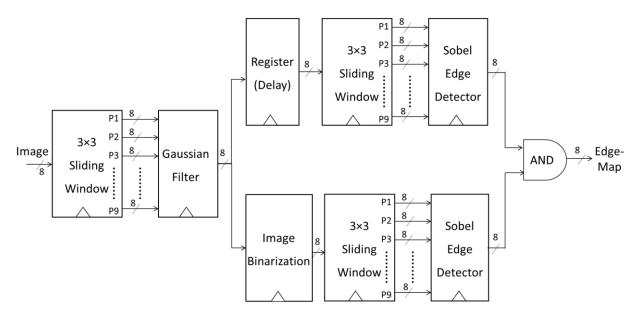

#### **C)** Feature Extraction