# FORMALIZATION OF VERTICAL TRANSFORMATIONS IN A MODEL BASED DESIGN FRAMEWORK

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY by

Anup Kumar Bhattacharjee (Student ID: 2002PHXF406)

Under the Supervision of

Prof. R.K. Shyamasundar School of Technology & Computer Science Tata Institute of Fundamental Research

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN) INDIA 2008

#### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI RAJASTHAN

#### CERTIFICATE

This is to certify that the thesis entitled FORMALIZATION OF VERTICAL TRANSFORMA-TIONS IN A MODEL BASED DESIGN FRAMEWORK and submitted by ANUP KUMAR BHATTACHARJEE, ID.No.2002PHXF406 for award of Ph.D. Degree of the Institute, embodies original work done by him under my supervision.

> Name: PROF. R.K. SHYAMASUNDAR Designation: SR. PROFESSOR SCHOOL OF TECHNOLOGY & COMPUTER SCIENCE TATA INSTITUTE OF FUNDAMENTAL RESEARCH MUMBAI

Date :

### Acknowledgment

This research work would not have been possible without support from many people.

First of all, I would like to thank my supervisor, Prof. R. K. Shyamasundar for encouraging and guiding me throughout this work. I remember his first talk at a tutorial at TRDDC, Pune (in 1992) where he introduced me to the world of *synchrony* and I fell in love with *Esterel*. He is a very gifted and dedicated researcher. I am fortunate to have worked under him and I only wish that a small portion of his talents has touched me during our many meetings and discussions together. He has been always kind and patient with my shortcomings. I could never give my best as he expected.

Next to him, I would like to thank my superior colleague, Mr. S. D. Dhodapkar, Outstanding Scientist and Head, Software Reliability Section, BARC. He inducted me into the world of computer science after I joined BARC. It was his initiative that I first went into learning *lex* and *yacc* when my contemporaries were learning C. He is a man of remarkable capability of seeing things which most of us would have overlooked. I owe him for providing me the best support during my formative years in BARC. I wish to thank him for encouraging me to take up this research work and providing me with all organizational support.

I wish to thank BITS, Pilani for providing me financial support during this work without which this would not have been possible. In particular, I wish to thank Prof. V.S. Rao for encouraging me during my qualifying interview and later providing me support from BITS. I wish like to thank Prof Rahul Banerjee and and Prof Sundar Balasubramanian of Department of Computer Science & Engineering, for agreeing to be members of my Doctoral Advisory Committee. Their careful reading and comments have increased the quality of the thesis. I wish to thank Prof Ravi Prakash, Dean Research & Consultancy Division and Prof. Regalla Srinivasa Prakash, Asst. Dean, Research & Consultancy Division for their support from BITS. I also wish to thank Mr. Dinesh Kumar, Mr. Sharad Shrivastava and other staff members of Research & Consultancy Division who directly or indirectly assisted me during this period.

I wish to thank Mr. B.B. Biswas, Head Reactor Control Division, BARC, Mr. R.K. Patil, Associate Director (E&I Group), BARC and Mr. G.P. Srivastava, Director (E&I Group), BARC, for providing me the organizational support in BARC. I wish to thank Mr. R.K. Patil, Associate Director (E&I Group), BARC for taking personal interest in my research work. I also wish to thank Mr. G. Govindarajan ,Group Director , (E&I Group), BARC (now retired) for allowing me to take up the doctoral work.

I wish to thank Prof. S. Ramesh of IIT Bombay (now with GM R &D Lab, Bangalore) for constructive discussions during many of our collaborative projects and explaining me few finer aspects of Synchrony. I also wish to thank him for encouraging me to take up academic research work and register for Ph.D.

Thanks are also due to my colleagues Mr. Asif lqbal (now with Honeywell), Mr. Ajith K. John and Mr. Amol Wakankar who helped me with some of the implementations. It has

been wonderful to work with all of them as they made the lab environment lively.

I wish to thank my parents for providing me with good education and making me a good human being. They always gave me the best that they could afford.

I wish to thank my parent-in-laws for supporting me. They are wonderful people who sacrificed many things for us and supported me during all my difficult days of parenthood.

I also wish to thank my elder brother (Dada) who did lot of hand holding during my school days. He taught me Physics and Mathematics during my formative years and initiated me into the world of scientific learning.

My son Arijit deserves lot of thanks for being a wonderful son. I am grateful to him for having patience with me when I did not spend the time that I should have spent with him. He kept us in good humour with  $\forall$  and  $\exists$ .

Lastly, no word of appreciation is good enough for my wife Ruby. She supported me during most difficult days and kept me in good spirit. She is a brave lady who could face many daunting task and has a spirit that never gives up. I cannot repay my dues when she suffered the most during our early days of parenthood while I was away at IIT Kharagpur.

### Abstract

Model-based design methods emphasize concurrency, communication abstractions, and temporal aspects, rather than only procedural interfaces. A successful model based design is a methodology based on mathematical and visual methods and addresses the problems associated with designing complex information and control systems. The model-based design paradigm is significantly different from the traditional design methodology. Rather than using complex structures and extensive software code, designers can now define advanced functional characteristics using building blocks which are defined in terms of primitive functions having precise meanings. These built models along with appropriate simulation, automatic code generation and verification tools can lead to rapid prototyping, software testing and verification.

In this thesis, we address few issues in a model based design framework concerning enrichment of modeling languages, transformation of the modeling language to a framework which eases verification and code generation, detection of run-time execution errors and validation of translation from high level language to low level implementation.

The key areas of focus in this thesis are:

- Formalization of translation of the graphical (UML oriented) notations typically used in in model based designs.

- A language to model choreography of service oriented computing for distributed systems.

- Type system of weakly typed language like C to detect run time errors.

- A scheme for translation validation to validate the assembly code produced by the compiler.

We show formalization of two graphical notations namely Statecharts and Activity Diagrams which are used in model based design methodologies. Statechart is a class of hierarchal statemachine and is one of the modeling language used for specifying the reactive behaviour of an entity based on it's response to events. Statecharts are commonly used in the specification and design of embedded systems. However no formal treatment of the semantics of Statecharts has been given as a part of the OMG standard. Without a formal semantics, specifications in Statecharts are not amenable to analysis and automatic code generation.

Activity Diagram used in UML and STATEMATE encapsulates activities performed by the system and is used to show graphically a process view of a system in terms of interactions between processes. It can be used to depict the high level processing view of the system which is a composition of distributed components, each performing local activities.

We show how these visual notations can be realized in a synchronous language framework. This underlying synchronous semantics allows verification of the models created in these notations. It also allows high level imperative style code generation using compilers for synchronous languages. Since the model can be verified and code is generated from the verified model using provably correct transformation, our approach addresses the concerns of correct-by-construction approach in vertical model transformation.

The traditional semantics proposed in OMG standards lacks features to model reactive behaviour of workflows. It also needs semantic enrichment when each of the activities is prone to failure and need compensating actions. Such extensions have wide applications in modeling and debugging complex business processes. We have proposed extension to Activity Diagrams to model failure and compensations.

Service oriented computing is a new emerging paradigm for distributed computing. Services are autonomous computational entities and web services are the most common application of service oriented computing. The terms *orchestration* and *choreography* are used to define two different flavors of service oriented computing. While orchestration is used to describe a single view point model, choreography is about specifying the service orchestration in a global model. Choreographs define the sequence of exchanging messages between two (or more) independent participants or processes by describing how they should cooperate. We focus on structuring choreography as a set of message exchanges among various participating roles as conversations. In this thesis, we also define a language framework, which integrates orchestration with scripting to abstract conversations leading to an effective modular specification of service choreography.

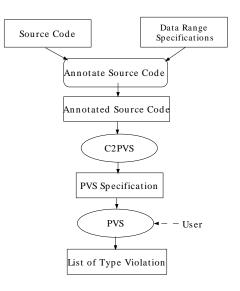

We address the inadequacy of a type system in a language like C popularly used in embedded system design as a part of the back end tool chain. We show a method of defining a type system of C in a deductive framework. The method is based on a novel model of C programs: each C program is modeled as a typed transition system encoded in the specification language accepted by PVS theorem prover. Since the specification is strongly typed, proof obligations are generated, for possible type violations in each statement in C, when loaded in the PVS theorem prover which need to be discharged. The technique does not require execution of the program to be analysed and is capable of detecting typical type errors such as array bound errors, divide by zero, arithmetic overflows and underflows etc.

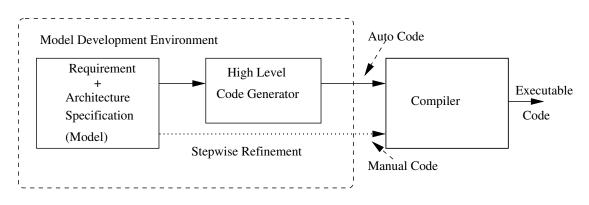

We describe a methodology and a system for the validation of translation of a simple HLL to assembly language programs. Our method consists of converting the high level language (HLL) program and its object code to a common semantic representation such as Fair Transition System (FTS), and then establishing that the object code is a refinement of the HLL program. We show that the the proof of refinement can be performed using a theorem prover. In our examples, we have used Stanford Temporal Prover (STeP) as the theorem prover. The proposed approach also has the additional advantage that the embedded system remains unaffected by compiler revisions/updates.

# Contents

| 1 | Introduction |                            |   |  |

|---|--------------|----------------------------|---|--|

|   | 1.1          | Motivation                 | 1 |  |

|   | 1.2          | Related Work               | 3 |  |

|   | 1.3          | Benefits of the Approach   | 6 |  |

|   | 1.4          | Contribution of the Thesis | 7 |  |

|   | 1.5          | Outline of the Thesis      | 8 |  |

### **I** Visual Modeling Notations for Reactive & Workflow Systems: Formalization and Realization

9

| 2 | Stat | echarts : Visual Modeling Notation for Reactive Systems                      | 10 |

|---|------|------------------------------------------------------------------------------|----|

|   | 2.1  | Introduction                                                                 | 10 |

|   | 2.2  | The Synchronous Approach                                                     | 11 |

|   |      | 2.2.1 A Brief Introduction to ESTEREL                                        | 13 |

|   | 2.3  | Components of a Statechart                                                   | 14 |

|   | 2.4  | STATEMATE Semantics                                                          | 15 |

|   | 2.5  | Formalization of STATEMATE Semantics of Statecharts                          | 15 |

|   |      | 2.5.1 Synchronous STEP Semantics                                             | 18 |

|   | 2.6  | Summary                                                                      | 20 |

| 3 | Rea  | lization of Statecharts in the Textual Formalism of $\operatorname{Esterel}$ | 21 |

|   | 3.1  | Introduction                                                                 | 21 |

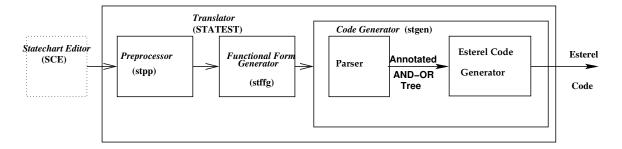

|   | 3.2  | Structure of the Translator                                                  | 21 |

|   | 3.3  | Semantic Transformation of Statecharts into ESTEREL                          | 22 |

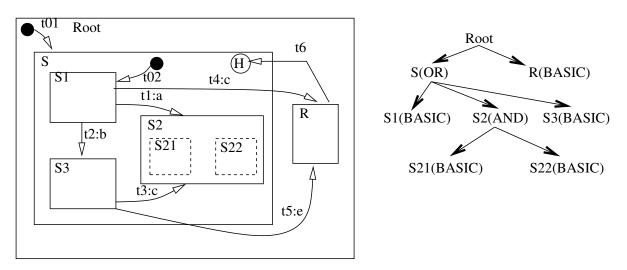

|   |                                                        | 3.3.1    | AND-OR Tree Representation of Statecharts                                             | 22 |  |

|---|--------------------------------------------------------|----------|---------------------------------------------------------------------------------------|----|--|

|   |                                                        | 3.3.2    | Node-Labeling Algorithm                                                               | 24 |  |

|   |                                                        | 3.3.3    | Labeling for Transition Conflict Resolution                                           | 25 |  |

|   |                                                        | 3.3.4    | Structure of the $Esterel$ Code $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 25 |  |

|   |                                                        | 3.3.5    | ${\rm Esterel} \ {\sf Code} \ {\sf Generator} \ . \ . \ . \ . \ . \ . \ . \ . \ . \ $ | 27 |  |

|   | 3.4                                                    | Code-G   | Generation Algorithm                                                                  | 30 |  |

|   |                                                        | 3.4.1    | Algorithm:GenCode                                                                     | 31 |  |

|   |                                                        | 3.4.2    | Algorithm : TranslateTransition                                                       | 33 |  |

|   |                                                        | 3.4.3    | Generation of STEP signal                                                             | 34 |  |

|   | 3.5                                                    | History  |                                                                                       | 35 |  |

|   | 3.6                                                    | Summa    | ary                                                                                   | 36 |  |

| 4 | Visu                                                   | ial Forr | nalism for Communicating Reactive Systems                                             | 37 |  |

|   | 4.1                                                    | Introdu  | iction                                                                                | 37 |  |

|   | 4.2                                                    | Comm     | unicating Statecharts                                                                 | 38 |  |

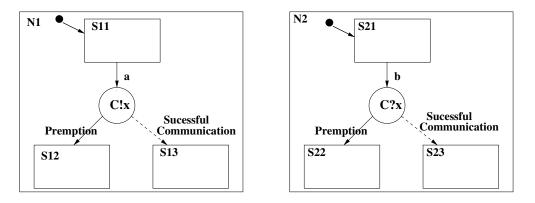

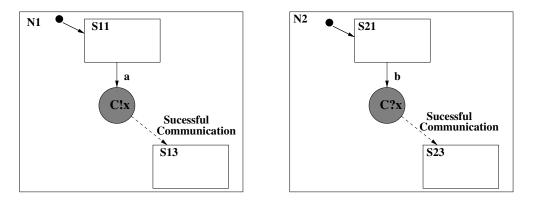

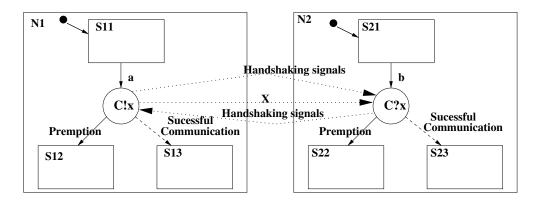

|   |                                                        | 4.2.1    | Synchronous Communication State                                                       | 38 |  |

|   |                                                        | 4.2.2    | Asynchronous Communication State                                                      | 39 |  |

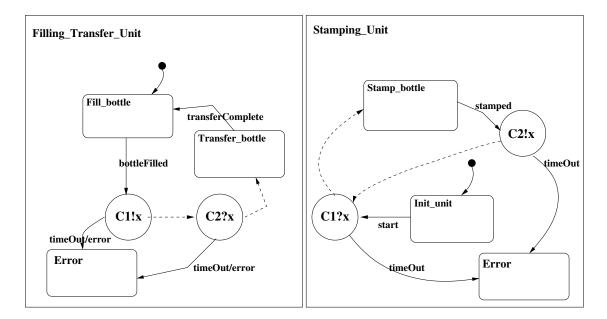

|   |                                                        | 4.2.3    | Modeling in CS: An Example of a Simple Plant Controller                               | 41 |  |

|   | 4.3                                                    | Model    | Verification for Safety & Liveness                                                    | 42 |  |

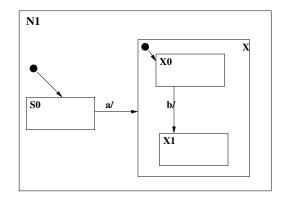

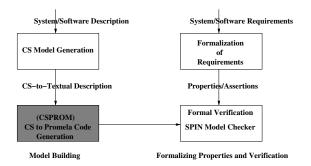

|   |                                                        | 4.3.1    | Scheme for Verification                                                               | 42 |  |

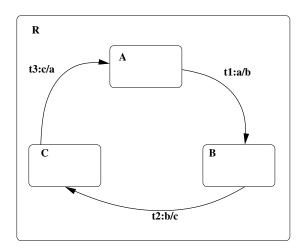

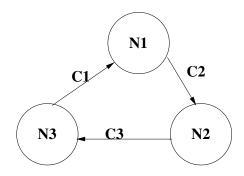

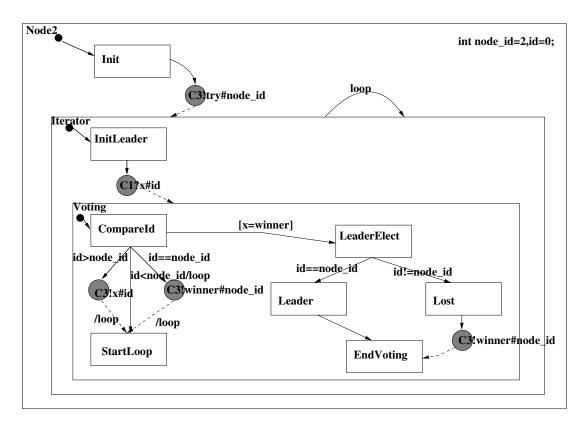

|   | 4.4                                                    | Model    | of 3-node leader election ring                                                        | 45 |  |

|   |                                                        | 4.4.1    | Verification for Correctness                                                          | 46 |  |

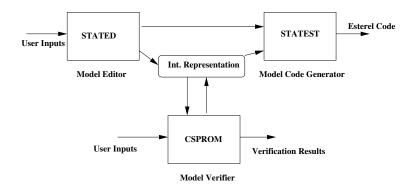

|   | 4.5                                                    | Model    | Code Generation                                                                       | 47 |  |

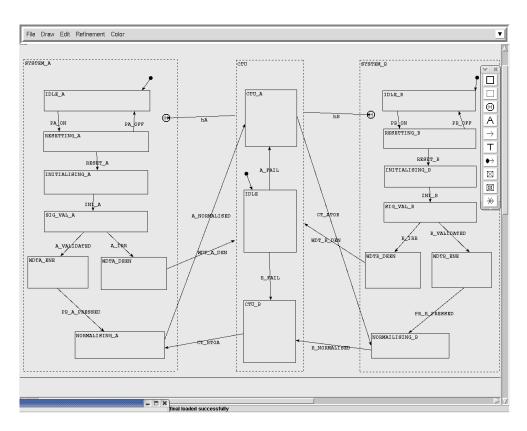

|   | 4.6                                                    | Implem   | nentation of a Tool                                                                   | 50 |  |

|   | 4.7                                                    | Summa    | ary                                                                                   | 52 |  |

| 5 | Modeling Business Processes through Activity Diagram 5 |          |                                                                                       |    |  |

|   | 5.1                                                    | Introdu  | uction                                                                                | 53 |  |

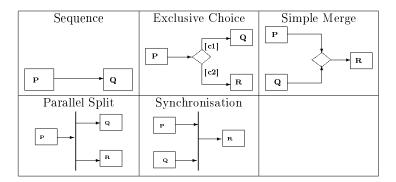

|   | 5.2                                                    | Activity | y Diagrams: Interpretation in Process Algebra                                         | 55 |  |

|   |                                                        | 5.2.1    | Synchronisations in Various Control Flow Patterns                                     | 55 |  |

|   |                                                        | 5.2.2    | Handling Interrupts                                                                   | 57 |  |

|   | 5.3                                                    | Model    | ing Business Processes as Activity Diagram                                            | 59 |  |

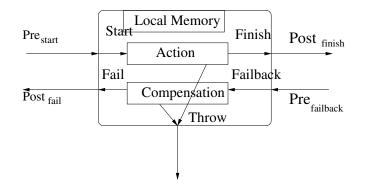

|   | 5.4 | Modeli   | ng Failures in Activity Diagrams                                                      | 60 |

|---|-----|----------|---------------------------------------------------------------------------------------|----|

|   |     | 5.4.1    | Semantics of Activity Diagrams with Failures in Enriched CSP Frame-work               | 61 |

|   | 5.5 | Summa    | ary                                                                                   | 64 |

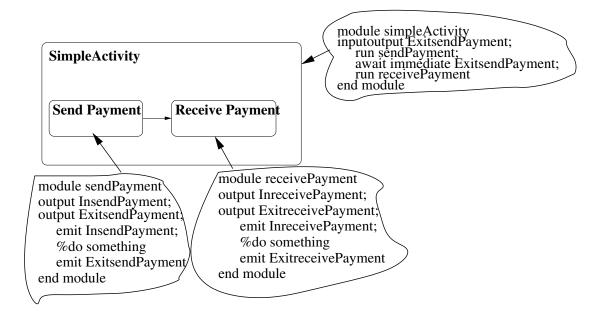

| 6 | lmp | lementa  | ation of Activity Diagrams in ESTEREL                                                 | 65 |

|   | 6.1 | Introdu  | ction                                                                                 | 65 |

|   | 6.2 | Basic C  | Constructs of Activity Diagram and their Implementation in $\operatorname{Esterel}$ . | 66 |

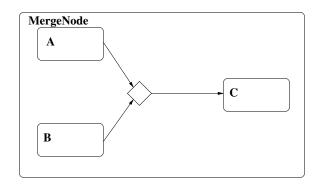

|   |     | 6.2.1    | Modeling Merge Node                                                                   | 66 |

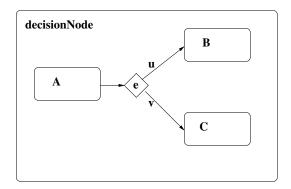

|   |     | 6.2.2    | Modeling Decision Node                                                                | 68 |

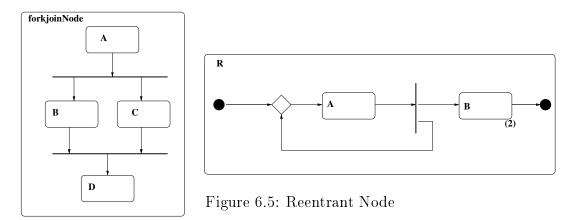

|   |     | 6.2.3    | Modeling ForkJoin Node                                                                | 68 |

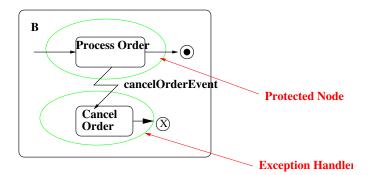

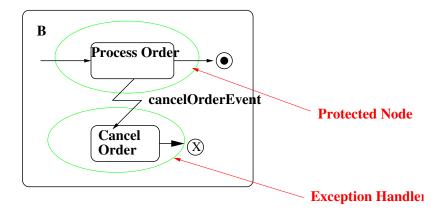

|   |     | 6.2.4    | Modeling Exception                                                                    | 71 |

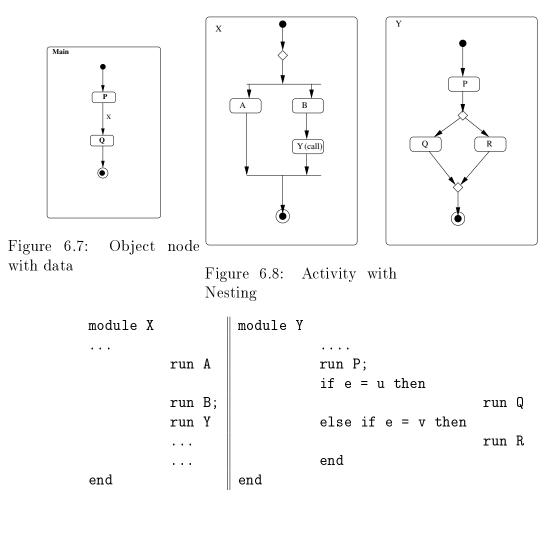

|   | 6.3 | Activity | with Data and Nesting                                                                 | 72 |

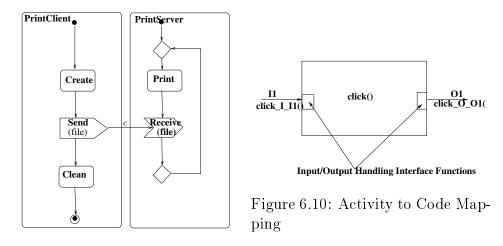

|   | 6.4 | Commi    | unication in Activity Diagrams                                                        | 74 |

|   | 6.5 | Simulat  | tion and Code Generation                                                              | 74 |

|   |     | 6.5.1    | Code Generation                                                                       | 75 |

|   | 6.6 | Verifica | ation                                                                                 | 76 |

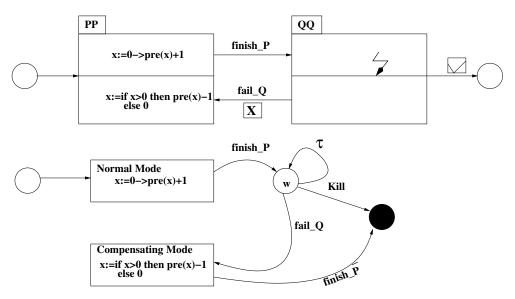

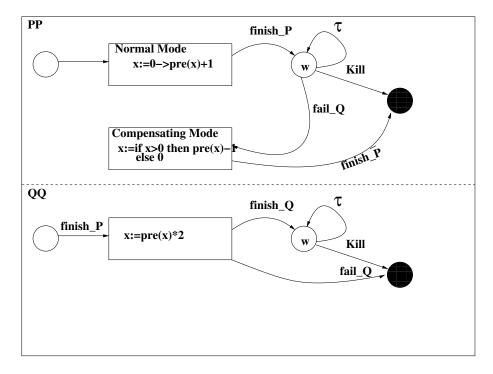

|   | 6.7 | Implem   | entation Model for Compensating Activities                                            | 76 |

|   | 6.8 | Summa    | ary                                                                                   | 77 |

| 7 | A S | pecifica | tion Language for Choreography in Distributed Systems                                 | 80 |

|   | 7.1 | Introdu  | ction                                                                                 | 80 |

|   | 7.2 | Backgr   | ound                                                                                  | 81 |

|   | 7.3 | Modeli   | ng conversations as patterns of communication among processes                         | 82 |

|   | 7.4 | ScriptC  | Orc: A Language Abstraction for Choreography                                          | 85 |

|   |     | 7.4.1    | Operational Semantics of ScriptOrc                                                    | 88 |

|   |     | 7.4.2    | Clock Expressions in ScriptOrc                                                        | 90 |

|   | 7.5 | Choreo   | graphy of Speaker, hotel and Flight                                                   | 90 |

|   | 7.6 | Summa    | ary                                                                                   | 92 |

|   |     |          |                                                                                       |    |

## II Type Correctness and Translation Validation of Model Gen-

### erated Code

| 8  | Мос   | lel Trai                                                                   | nsformation: Type Correctness of High Level Language ( | Code | 94  |  |

|----|-------|----------------------------------------------------------------------------|--------------------------------------------------------|------|-----|--|

|    | 8.1   | Introdu                                                                    | iction                                                 |      | 94  |  |

|    | 8.2   | Type Ir                                                                    | nferencing Method                                      |      | 95  |  |

|    | 8.3   | Modeli                                                                     | ng C Programs in PVS                                   |      | 98  |  |

|    |       | 8.3.1                                                                      | Modeling Datatypes of C in PVS                         |      | 98  |  |

|    |       | 8.3.2                                                                      | Modeling Execution Semantics of C in PVS               |      | 100 |  |

|    | 8.4   | Proving                                                                    | g TCCs in PVS and Tracing RTEs to Source Code          |      | 103 |  |

|    | 8.5   | $Example  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |                                                        |      |     |  |

|    | 8.6   | Summa                                                                      | ary                                                    |      | 105 |  |

| 9  | Tra   | nslatio                                                                    | n Validation of a HLL Compiler                         |      | 107 |  |

|    | 9.1   | Introdu                                                                    | iction                                                 |      | 107 |  |

|    | 9.2   | Transla                                                                    | ation Validation: An Overview                          |      | 109 |  |

|    |       | 9.2.1                                                                      | Fair Transition System                                 |      | 110 |  |

|    | 9.3   | An Ove                                                                     | erview of the OCV Method                               |      | 110 |  |

|    | 9.4   | Formal                                                                     | Description of the OCV Method                          |      | 111 |  |

|    |       | 9.4.1                                                                      | Correctness of Translation                             |      | 112 |  |

|    |       | 9.4.2                                                                      | Proof of Validation using STeP                         |      | 114 |  |

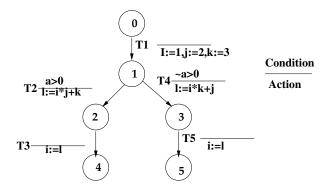

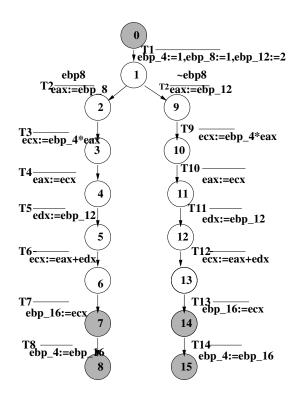

|    | 9.5   | lllustra <sup>.</sup>                                                      | tive Example with Translation Error                    |      | 116 |  |

|    | 9.6   | System                                                                     | for OCV: Implementation Features                       |      | 120 |  |

|    |       | 9.6.1                                                                      | Generating SPL/FTS for the HLL Source                  |      | 121 |  |

|    |       | 9.6.2                                                                      | Generating FTS for the Object Code                     |      | 122 |  |

|    | 9.7   | Summa                                                                      | ary                                                    |      | 123 |  |

| 10 | Con   | clusion                                                                    | s, Future Work and Main Contribution                   |      | 124 |  |

|    | 10.1  | Conclu                                                                     | sion                                                   |      | 124 |  |

|    | 10.2  | Limitat                                                                    | tions and Future Work                                  |      | 125 |  |

|    | 10.3  | Main C                                                                     | Contribution                                           |      | 126 |  |

| Re | feren | ices                                                                       |                                                        |      | 128 |  |

| Α   | Rep   | resentation of Statecharts and Data Structures used in STATEST | 137 |

|-----|-------|----------------------------------------------------------------|-----|

| В   | Brie  | f Introduction to CSP, PVS and STeP                            | 144 |

|     | B.1   | Brief Discussion on CSP                                        | 144 |

|     | B.2   | A Brief Discussion on PVS                                      | 145 |

|     | B.3   | A Brief Discussion on STeP                                     | 146 |

| Pu  | blica | tions                                                          | 148 |

| Bio | odata | a of Candidate & Supervisor                                    | 150 |

# List of Figures

| 2.1  | An Example Specification of a Real Time System            | 12 |

|------|-----------------------------------------------------------|----|

| 2.2  | Statechart Specification of a Stopwatch                   | 14 |

| 3.1  | Schematic Diagram of the Translator                       | 22 |

| 3.2  | Statechart and its AndOr Tree Representation              | 23 |

| 3.3  | Translation of T4 Type Transition                         | 30 |

| 3.4  | Cyclic Transitions                                        | 35 |

| 4.1  | Rendezvous sender and receiver states                     | 39 |

| 4.2  | Asynchronous communication sender and receiver states     | 40 |

| 4.3  | A Simple Bottling Plant                                   | 41 |

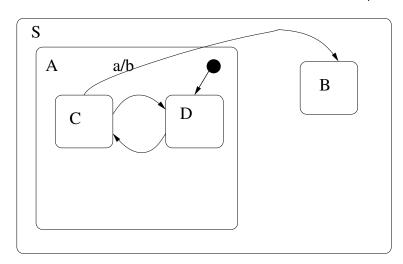

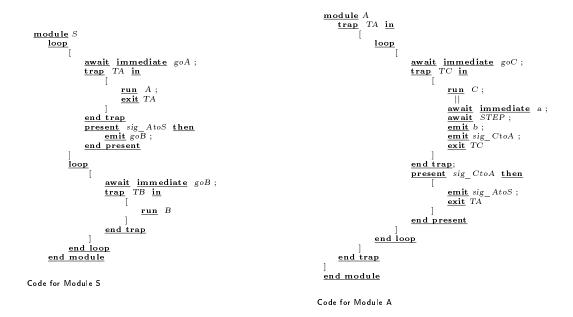

| 4.4  | Simple Example showing model translation                  | 43 |

| 4.5  | Leader Election Protocol: Nodes and channels connectivity | 46 |

| 4.6  | A typical node modeled in CS                              | 47 |

| 4.7  | Rendezvous sender and receiver states                     | 48 |

| 4.8  | Tool Architecture                                         | 51 |

| 4.9  | Tool Editor                                               | 51 |

| 4.10 | The use of CSPROM in formal verification                  | 52 |

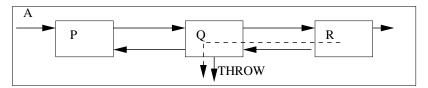

| 5.1  | Simple Activity Diagram                                   | 54 |

| 5.2  | Basic Constructs of Activities                            | 56 |

| 5.3  | Activity with Exception Handlers                          | 58 |

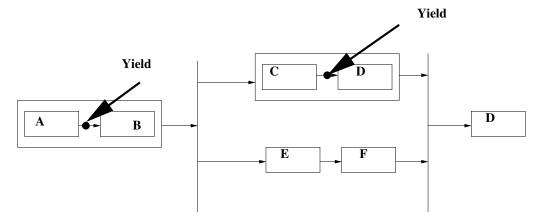

| 5.4  | Activity with Yielding Points                             | 58 |

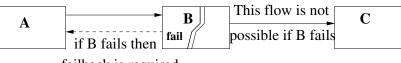

| 5.5  | Activity with Failure                                     | 59 |

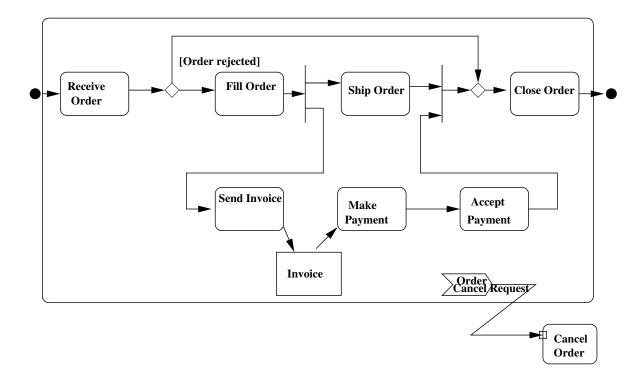

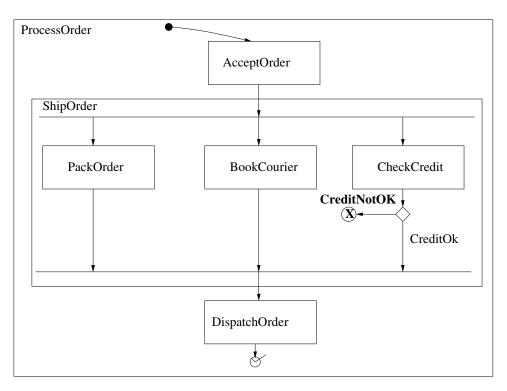

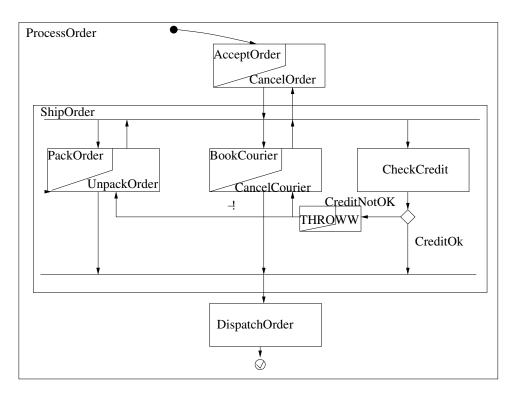

| 5.6  | Order Processing                                          | 59 |

| 5.7  | Activity with Compensation                       | 61  |

|------|--------------------------------------------------|-----|

| 5.8  | Composition of Compensating Activities           | 61  |

| 5.9  | Stack of Compensation Activities                 | 63  |

| 5.10 | Activity with Compensation                       | 64  |

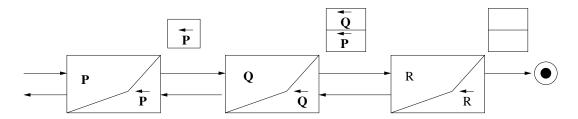

| 6.1  | Simple node                                      | 67  |

| 6.2  | Merge Node                                       | 67  |

| 6.3  | Decision Node                                    | 67  |

| 6.4  | Fork Join Node                                   | 68  |

| 6.5  | Reentrant Node                                   | 68  |

| 6.6  | Exception Node                                   | 72  |

| 6.7  | Object node with data                            | 73  |

| 6.8  | Activity with Nesting                            | 73  |

| 6.9  | Object node with communication                   | 75  |

| 6.10 | Activity to Code Mapping                         | 75  |

| 6.11 | Verification Screen                              | 78  |

| 6.12 | Output of Verification                           | 78  |

| 6.13 | Mode Automata for Activity with Compensation     | 79  |

| 6.14 | Composition of Mode Automata                     | 79  |

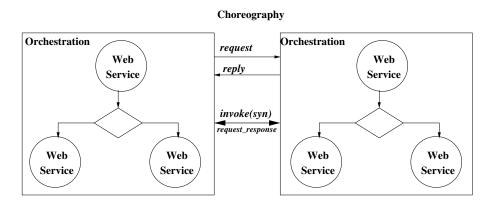

| 7.1  | Orchestration+Choreography                       | 81  |

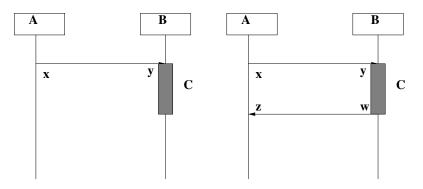

| 7.2  | Request and Request-Response Operations          | 87  |

| 8.1  | Process of Type Checking C Programs              | 96  |

| 8.2  | Example Program                                  | 97  |

| 8.3  | Annotated Program                                | 97  |

| 9.1  | Two Main Steps from Specification to Realization | 107 |

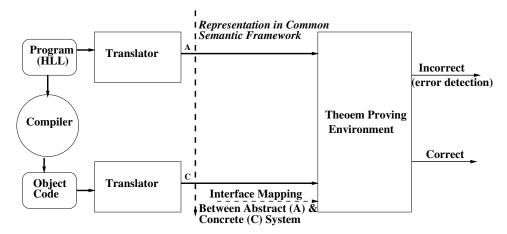

| 9.2  | Overall Object Code Verification Scheme          | 111 |

| 9.3  | Transition System for the Abstract System        | 112 |

| 9.4  | Transition System for the Concrete System        | 113 |

# List of Tables

| 7.1 | Syntax of ScriptOrc                                                                                       |

|-----|-----------------------------------------------------------------------------------------------------------|

| 8.1 | Formal annotations and their syntax                                                                       |

| 8.2 | The C constructs and their PVS transformations $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $102$         |

| 8.3 | The TCCs, their significance and proofs for function average $\ldots$ $\ldots$ $\ldots$ $105$             |

| 9.1 | HLL-SPL mapping                                                                                           |

| 9.2 | Assembly Instructions to FTS mapping $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $122$ |

## Chapter 1

## Introduction

### 1.1 Motivation

Designing software for safety-critical systems such as those used in aerospace, control of nuclear reactors, medical systems, large distributed web applications etc., is a complex and challenging task. This requires a systematic approach involving modeling, analysis and simulation techniques as have been used beneficially in other branches of engineering. This approach supported by verification is expected to achieve improvements in dependability of software designs.

Model-based architecture and design [91] methodology is increasingly becoming popular in software used in safety-critical applications. A model enables to analyse the properties of a proposed design solution for a system before actually realising it in software and/or hardware. The methodology is based on the representation, composition, and manipulation of models during the design process. An emerging common requirement in model-based software and systems design is that modeling languages need to be domain-specific (Domain Specific Modeling Language (DSML)), offering software/system developers abstractions and notations that are tailored to characteristics of their application domain.

Models once created should be amenable to rigorous analysis (model analysis) to check that their behaviour meet the actual system requirements. It is also essential to be able to generate efficient implementation (model based code generation) of the system from the model. Model analysis and model-based code generation require the precise semantics of modeling language. One of the most commonly used modeling language in software specification and design is Unified Modeling Language (UML) [92]. The Unified Modeling Language (UML) is a general-purpose visual modeling language that is designed to specify, visualize, construct and document the artifacts of a software system. UML is used in specifying software systems from embedded applications to business process applications. Considerable effort is required to ensure the correctness of the specification in terms of simulation and testing. However simulation and testing only show the desired behaviour but cannot prove the absence of an undesirable behaviour. Approaches based on formal verification techniques have been found to be successful in handling such requirements and it is being increasingly used (particularly in hardware)to find corner cases (difficult bugs) as a complementary effort to testing. It is required to have a rigorous semantics behind such graphical notations which allows rigorous verification of the models. Additionally, if the actual implementation of the specification is not derived from the model on which verification is done, the implementation will have potential to diverge from the specification. Hence there is a requirement of automatic code generation from the models through a process of model transformation.

Model based design typically works as a phase wise model transformation and refinement. The transformation works at two levels: Vertical and Horizontal. Vertical transformation is typically synthesis of a new artifact from a description at a more abstract level. Horizontal transformation is more like refactoring an implementation for efficiency or portability. Continuous verification in these phases needs to be a part of the model based design, which ensures correctness-by-construction [52]. The verification requirements are with respect to

- 1. Correctness of the model with respect to certain system invariants.

- 2. Correctness of mapping model to a high level language implementation.

- 3. Type correctness of the implementation.

- 4. Correctness of the translation to a machine language.

These are most demanded by software developments in safety-critical systems. As demands for safety-critical software increase, future requirements will necessitate strategies to support these in a tool driven environment and hence needs to be addressed as part of the vertical transformations in a model based design environment.

While UML is rapidly becoming the industry standard for modeling, its standard definition does not contain a precise semantics which helps in model verification and code generation.

The main objective of this thesis is to provide a formal interpretation of some of the graphical notations typically used in UML, within a framework of synchronous methods and process calculus. This will address requirement of precise specification of UML models and can support continuous verification. It will allow formal model analysis and model-based code generation in a vertical model transformation framework. We show formalization of two graphical notations namely Statecharts [56, 57] and Activity Diagrams [92] which are used in model based design methodologies. Statecharts and Activity Diagrams are extensively used in UML notations, although the actual syntax used in UML are slight variation of the syntax used for this thesis. We also discuss a formal language based on a reactive framework for describing choreography in distributed service oriented systems.

As a part of the vertical transformation, the high level model is progressively transformed into a High Level Programming Language (HLL) like C which can be efficiently compiled into a machine executable binary. Such model generated code should be *type safe*. This

is particularly true if automatic code generation from models is employed in safety-critical systems. One of the issues with types arise because of arithmetic with finite precision. The inability of computers to represent an infinite range of values is well known. For example, in the case of signed or unsigned integers, it is useful to define a valid range, within which all values are guaranteed to lie after the result of an assignment or initialization on that integer type. It is necessary to define a type system policy to be enforced in the event that a resulting assignment or initialization to variables through evaluation of expressions lie inside the valid range.

It is important to ensure that the High Level Language (HLL) code generated from the model is translated correctly to a machine language by a compiler. In several key safetycritical embedded applications, it has become mandatory to verify the process of translation by compilers since usually compilers are only certified rather than verified. We have explored the application of Translation Validation [98] in the verification of compiled code against the input source program.

This thesis, in addition to the formalization of the Statecharts, Activity Diagrams, also addresses the type correctness issues of the high level code from the model and correctness of translation to machine language implementation.

### 1.2 Related Work

Several domain specific notations and methods have been developed to help the designer specify clear and unambiguous system requirements, verify that the requirements are consistent and correct, and verify that the refined design meets its specification. Notable among these are Unified Modeling Language(UML) [92], Systems Modeling Language (SysML) [69], Simulink/Matlab [61] and Business Process Modeling Notation(BPMN) [93]. Most of the notations like that of UML, which are used in industry are based on graphical syntax. However many of these notations do not have a rigorous semantics because of which the specifications created using these cannot be subjected to rigorous analysis. The advantage of such analysis notably results in proving some of the required design properties of safety and liveness [29]. Automatic 100% code generation from the modeling language is also not possible if the modeling language lacks a precise semantics. Lack of semantics also leads to model and code going out of sync, if there is a change in requirement or a change in manually developed code from the model.

The area of research in semantics of visual languages for state based model driven design has been very active during the last decade [76, 57, 4, 55, 36]. Andre [4] has presented a formal semantics of hierarchical statemachines in a synchronous framework. However the presentation does not include the complete syntax of Harel's Statecharts [57]. Formal semantics of Statecharts to that presented here covers the complete syntax (restricted to input deterministic class) of Statecharts.

The suitability of activity diagrams for modeling business process has been argued in

[109]. To the best of our knowledge, the first formal semantics of UML Activity Diagram (UML AD) was proposed by Eshuis [41, 42]. Eshuis proposes the semantics at the following two levels :*Requirement Level* and *Implementation Level*. The first level is based on Statechart like semantics and is transformed into a transition system for model checking by NuSMV [30]. The second level is based on STATEMATE [54] semantics of Statecharts extended with properties to handle data. The semantics covers activity charts of UML 1.5 but not of activity diagrams of UML 2.0<sup>1</sup>. A token flow semantics based on Petri Nets was proposed in [106] by mapping activities into *procedural Petri nets*, which excludes data type annotations but includes control flow. Storrle [105] has defined mappings to *procedural Petri nets* to prevent multiple calls which otherwise would result in infinite nets. However these approaches do not address the automatic code generation as may be required in a tool driven environment. Semantics based on synchronous language was proposed in [15] which allows a validated code generation from the notation.

A process algebraic formulation of workflow is proposed in [117]. A theoretical foundation of flow composition languages is given by Bruni in [24]. Fu [48], presented an approach of converting BPEL Web services into guarded statement and further into PROMELA/SPIN for verification. Similar approaches based on Finite State Processes (FSP) [80] and CCS were presented in [46] and [74]. However they didn't consider failure and subsequent compensation and hence not suitable for modeling business processes. Business Process Execution Language (BPEL) support the notion of compensation in case of a service failure. An activity can be associated with another activity that acts as its compensation action. This compensation handler can be invoked either explicitly or by the default compensation handler of the enclosing scope. In this sense, UML Activity Diagrams need to be enriched with additional semantic constructs to model such compensating actions. The extensions of Compensating Activity Diagrams proposed in this thesis is inspired by Hoare [107] and is based on a flow composition language introduced in [25]. The notion of compensation was perhaps first introduced as Sagas in handling Long Running Transactions by Garcia-Molina and Salem [49]. A formal model for compensable transactions has been defined by Li [78]. Verification approaches for incorporating compensating transactions were reported in [5, 40, 45].

Orchestration and choreography are emerging standards for creating business processes from multiple Web services. Solutions are required to have a good modeling support to specify such applications. The idea of Scripting as an abstract language for modeling conversation based on communication patterns was presented in [47]. Research in these area is very active in terms of orchestration languages based on a process calculus model [73, 86, 114] and verification issues [38, 40].

Another area of focus in this thesis was to formulate a formal language to capture the global choreography in distributed service oriented computing. WS-CDL [111] is the first choreography language proposed by W3C in 2005. WSCI [110] is another language targeted toward building a global interconnection model linking service operations but is not actually a chore-

<sup>&</sup>lt;sup>1</sup>It should be pointed out that UML 2.0 is a significantly re-engineered version of UML 1.5, particularly in the context of activity diagrams.

ography language. An excellent theoretical framework for service choreography is discussed in [99]. Orchestration is the prime language abstraction supported by various programming languages such as BPEL [64], BPML [90]. Another elegant formalism referred to as Orc [86] has been proposed for orchestration. Conformance validation between Choreography and Orchestration has been reported in [77]. As pointed out in [86], a reactive semantics for web services will provide a good basis for static and dynamic resource discovery and exploitation as it leads to good dynamic monitoring schemes. The later is also one of the aims of our study and proposal.

We also focus our attention to type correctness and correctness of translation of high level code via model transformation. Most of the model based design tools produce High Level Language (HLL) programs e.g., in C Language. It is well known that C has weak type system and cannot guarantee absence of *Run Time Error(RTE)*. Static Analysis tools like SPLint [43] are very useful in detecting RTEs in C, related to buffer overflow and pointer arithmetic but they do not address RTEs associated with arithmetic expressions. The program supervision tools e.g. those built using Valgrind [89] require target program execution and suffer from the same limitations as that of testing. Semantic Analysis based on Abstract Interpretation [33] is a more rigorous approach to detect runtime errors statically. This technique is based on data flow analysis which computes program properties by converting programs into equations over data types represented as lattices and then solving these equations over these lattices. Tools such as PolySpace [62], ASTREÉ [32] use the abstract interpretation technique for the detection of runtime errors in C programs. However these tools work on an abstract model (sound but not complete) of a program and are prone to *false positives* which are possible errors requiring further effort to investigate. Commercial tools also do not allow tuning to reduce false positives. There are also excellent research works on software model checking like BLAST [58], SLAM [8] etc., which are used for checking specifications related to software interfaces, shared resources in device drivers etc. These tools model check specified property and do not specifically address the issues of arithmetic runtime errors in a global manner.

It has remained a grand challenge to establish the correctness of a compiler [59]. For establishing the correctness of a compiler, one has to prove that the compiler always produces target code that correctly implements the source code. Owing to the intrinsic complexities of compiler verification, an alternative referred to as *Translation validation* has been explored in [98]. In this approach, each individual translation (i.e. a run of the compiler) is followed by a validation phase which verifies that the target code produced on this run correctly implements the source program. Such a possibility is particularly relevant for embedded systems where there is a need to execute a finite set of target programs. It must be pointed out that the validation task becomes increasingly difficult with the increase of sophistication and optimizations methods like scheduling of instructions as in RISC architectures or methods of code generation/optimization for super-scalar machines[88]. In [98], the authors demonstrated the the practicability of translation validation for a translator/compiler that translates the synchronous language Signal to C without any optimizations<sup>1</sup>. We have demonstrated in [14] the application of translation validation in validating translations of High Level Language (HLL)

<sup>&</sup>lt;sup>1</sup>In [97], extension of the approach for TNI SIGNAL compiler is explored.

compilers like C and Ada for a restricted class of programs.

### **1.3** Benefits of the Approach

Model-based design methods emphasize concurrency, communication abstractions, and temporal properties, rather than only procedural interfaces. A successful model based design is a methodology based on mathematical and visual methods and addresses the problems associated with designing complex information and control systems. The model-based design paradigm is significantly different from the traditional design methodology. Rather than using complex structures and extensive software code, designers can now define advanced functional characteristics using building blocks which are defined in terms of primitive functions having precise meanings. These built models along with some simulation tools can lead to rapid prototyping, software testing and verification. For example, domain-specific models for embedded systems might represent physical processes using ordinary differential equations [61], signal processing using dataflow models [72, 50], and decision logic using finite-state machines (FSM)[[12]. Model-based design methods address system specification, model transformation, synthesis of implementations, model analysis ,validation, execution, and design evolution. Model based design methodology is now also being sought and advocated for large distributed software development for managing business processes.

Model-based design of software uses formal, composable and manipulable models in the design, implementation and system integration process. Modeling languages introduce layers of abstractions in the design flow that are synergistic with the design objectives and the nature of the system to be designed. This is partly achieved by meta-modeling languages and meta-models describing the abstract syntax (concepts, relationships and well-formedness rules) of such modeling languages.

Synchronous language framework [51, 11, 75] is a sound methodology to address embedded software and hardware design, validation, and implementation. The advantage lies in rigorous mathematical semantics of synchronous languages, which allows one to argue about the consistency and correctness of the model and it's correct realization as a compilable implementation. The overall idea is to generate correct-by-construction [52, 53], deterministic implementation from high-level rigorous specifications. The advantage is in increasing quality while decreasing design and validation costs. In the correct-by-construction approach the process of software development is treated as in other branches of engineering, and are based on development of mathematical models, design, verification and refinement. A system is deterministic, if it always reacts in same way to the same inputs occurring with the same timing. On the contrary, a nondeterministic system can react in different ways to the same inputs, actual reaction depending on internal choices or computation timings. It is known that determinism is a must in safety critical system software.

A sound methodology is most sought after in the development of control applications like aerospace, nuclear, chemical, automotive and robotic applications. It is also being increasingly used in development of software used in business processes involving transactions. It provides an efficient approach for the five key elements of the development process cycle ("V" diagram): Requirements capturing, Specification, Development, and Deployment of the system, thus integrating all these phases and providing a common framework for communication throughout the entire design process. To support this, it is beneficial to have a sound framework to model, verify and derive the implementation seamlessly directly from the specification.

### 1.4 Contribution of the Thesis

The main contribution of the thesis are highlighted below:

- 1. Formalization of semantics of Statecharts based on an imperative synchronous semantics of ESTEREL : We present algorithms [18] [RESS01] for the translation of Statecharts into Esterel. This allows us to use other backend tools in the synchronous family for verification and high level code generation for implementation.

- Extending the Statecharts to model communication: We present an extension in Statecharts to model communication through channels. The new language allows us to model communicating reactive systems. We also present an alternate translation [66] [SAFECOMP2003] scheme to Promela used in the verification tool SPIN. We also show how such a specification can be realized [19] [IT2008] in the imperative synchronous language Esterel.

- Formalization of Activity Diagrams in Esterel: We present a reactive semantics of the various activity patterns using Esterel. We show that this semantics allows us to carry verification and code generation using tools used for family of synchronous languages [15] [ICDCIT2005].

- 4. Compensating Activity Diagrams: Although the Activity Diagrams can model most of the workflow patterns used in business process, however it cannot model failures in business processes. We show a possible extension of activity diagrams to model compensations required in such business process logic [JOT].

- 5. Language to Model Choreography in Distributed Service Oriented Computing: Choreographs define the sequence of exchanging messages (conversations) between two (or more) independent participants or processes by describing how they should cooperate. In [16, 17], we have explored the use of Scripts in describing conversational aspect of choreography. We show a formal language framework which integrates orchestration with scripting to abstract conversations leading to an effective modular specification of service choreography [16], [17] [APSCC08,ICWS08].

- 6. Type systems for C: Most of the model based design tools generate the implementation in C language. This is particularly true for tools used in embedded systems. However it is

known that there is no proper type system for C and hence C programs may not be typesafe (e.g. array index overflow, arithmetic overflows). We show a deductive technique based on PVS for verifying type safety of C progarm. We also show an implementation for checking type safety for a restricted class of C programs based on a type system implementation in PVS [67][SAFECOMP07].

7. Object Code Validation: The code generated from a model using a model compiler needs to be ultimately translated to a machine level code using a HLL compiler. It is known that compiler verification is an undecidable problem. We show how an alternate methodology based on Translation Validation can be used to verify fragments of High Level Language programs e.g C and it's correct translation to an object code (assembly instructions) [14][FTRTFT00].

### 1.5 Outline of the Thesis

The thesis is presented as follows: It is divided into two major parts: Part I describes the visual notations, their semantics and translation algorithms and Part II describes the work related to type safety of model generated High Level Language (HLL) and translation validation for a HLL compiler.

Part I is organized as follows: Chapter 2 introduces the general definition of reactive systems, Statecharts as a notation to model reactive systems and its semantics. The formalisation of translation of Statecharts in a synchronous language framework of ESTEREL is presented in Chapter 3. An extension of communication in Statecharts to model communicating reactive processes(CRP) is presented in Chapter 4. Chapter 5 presents a formalization of Activity Diagrams in a process algebraic framework and introduces an extension of Activity Diagrams to model compensations in business process logic. An implementation of Activity Diagrams is presented in Chapter 6. Chapter 7 presents the language framework to define service choreography.

Part II is organized as follows: In chapter 8, a methodology to build a type system for C programs is presented. In chapter 9, we present a methodology for compiler validation based on the framework of Translation Validation.

# Part I

# Visual Modeling Notations for Reactive & Workflow Systems: Formalization and Realization

# Chapter 2

# Statecharts : Visual Modeling Notation for Reactive Systems

### 2.1 Introduction

Reactive systems are computer systems that react continuously to their environment, at a speed determined by the latter. This class of systems contrasts, on one hand with transformational systems (classical programs whose inputs are available at the beginning of their execution and which deliver their outputs when terminating: for instance compilers), and on the other hand with interactive systems (which react continuously to their environment but at their own speed: for instance operating systems). Among reactive systems are most of the industrial real-time systems (control, supervision, and signal-processing systems), as well as man-machine interfaces. These systems have the main following characteristic:

- Parallelism. The design must take into account the parallelism between the system and its environment. It is convenient and natural to design such systems as sets of parallel components that cooperate to achieve the intended behavior.

- Determinism. These systems always react in the same way to the same inputs. This property makes their design, analysis, and debugging easier. Thus, it should be preserved by the implementation.

- Temporal requirements. These requirements concern both the input rate and the input/output response time. They are induced by the environment and must imperatively be matched. Hence, they must be expressed in the specifications, they must be taken into account during the design, and their satisfaction must be checked on the implementation.

- Reliability. This is perhaps their most important feature as these systems are often critical ones. For instance, the consequences of a software error in an aircraft automatic

pilot or in a nuclear plant controller are disastrous. Therefore, these systems require rigorous design methods as well as formal verification of their behavior.

A language well suited to the specification and design of reactive systems should, therefore, allow specification of parallel and deterministic behaviours and allow formal behavioural and temporal verification.

### 2.2 The Synchronous Approach

Synchronous languages have been introduced in the 80s to make the programming of reactive systems easier [12]. The purpose of these languages is to give the designer ideal time primitives, thus reducing the chance of programming misconceptions. Instead of the interleaving paradigm, they are based on the simultaneity principle: All parallel activities share the same discrete time scale. Concretely, this means that  $a \parallel b$  is viewed where a and b are simultaneous. Each activity can then be dated on the discrete time scale; this has the following advantages:

- Temporal reasoning is made easier.

- Interleaving based nondeterminism disappears, which makes program debugging, testing, and validating easier.

Concerning the implementation, the idea is to project this discrete time scale onto physical time. As the scale is discrete, nothing occurs between two consecutive instants: Everything must happen as if the processor running the program were infinitely fast. This is the outcome of *synchrony hypothesis* which can be stated as

- 1. the system evolves through an infinite sequence of successive atomic reactions indexed by a global logical clock,

- 2. during a reaction each component computes new events for all its output signals based on the presence/absence of events computed in the previous reaction and,

- 3. the communication of events among components occur instantaneously between two successive reactions.

Although such an infinitely fast processor does not exist, but it suffices that any input be treated before the next one. In order to verify this condition, one only needs to know the maximal input frequency, and an upper bound on the execution time of the object program. For this purpose, synchronous languages have deliberately restricted themselves to programs that can be compiled into a finite deterministic interpreted automaton, a control structure whose transitions are deterministic sequential programs operating on a finite memory. Each transition, whose execution time is statically computable, corresponds to the system reaction to an input. There are numerous languages based upon the synchrony hypothesis: ESTEREL [12], LUSTRE [50], SIGNAL [9], STATECHARTS [56], etc. Significant advantages of the family of synchronous languages include the availability of idealized primitives for concurrency, communication and preemption, a clean rigorous semantics, a powerful programming environment with the capability of formal verification. The advantages of these languages are nicely paraphrased by Gerard Berry, the inventor of ESTEREL, as follows: *What you prove is what you execute*.

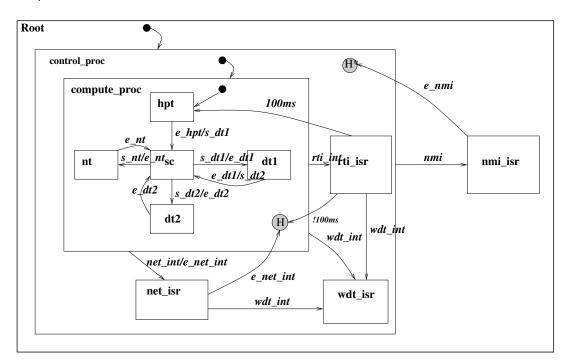

Textual and graphical formalisms have their own intrinsic merits and demerits. For instance consider the following reactive specification of control flow (switching of tasks) among various computing tasks and interrupt service tasks in a control software. The computing tasks switch from one to another in cyclic fashion and are shown as substates of *compute\_proc*. The interrupt service tasks are entered as a result of the occurrence of interrupt events. The history notation has been used to indicate that on return from interrupt tasks, the system returns to last executing compute task (except when event *100ms* occurs, the control returns to compute task *hpt*). Such systems can be specified using graphical formalisms easily. The Statechart

Figure 2.1: An Example Specification of a Real Time System

for the above system is shown in Figure 2.1. Lets us consider the intended behaviour: When the event wdt\_int occurs on system failure, the state of the system will be in state wdt\_isr and subsequently the system will toggle between states wdt\_isr and nmi\_isr. Arguing the correctness of this intended behaviour from such descriptions, however, is not easy. Our work is concerned with methods that will combine advantages of using graphical formalisms for the design of reactive systems with that of using formal verification tools in textual formalisms.

Statecharts is a visual formalism which can be seen as a generalization of the conventional finite automata to include features such as hierarchy, orthogonality and broadcast communication between system components. Being a formalism rather than a language, there is no unique semantics in the various implementations and further Statechart specifications can be nondeterministic. For these reasons, even though there are powerful programming environments for Statecharts such as STATEMATE (which includes simulators), environments lack formal verification tools. The primary motivation incorporating the Statecharts-to-Esterel translator tool was to open up possibilities of formal verification which seemed easily possible via ESTEREL route, the code generation/optimization capability coming as a bonus. In fact, the implementation of the tool has been found to have the important advantage of using Statecharts or ESTEREL for the specifications/modeling of different components of the same system.

#### 2.2.1 A Brief Introduction to ESTEREL

For a better understanding of the synchrony hypothesis, let us study some examples in ES-TEREL . ESTEREL is an imperative synchronous programming language. Besides variables, the language manipulates signals: A signal can be valued or pure, and can be an input signal (its presence can be tested), an output signal (it can be emitted), or a local signal (it can be emitted and its presence can be tested). The communication mechanism is the synchronous broadcast: any signal emitted by someone at a given instant is received by everybody at the same instant. Moreover, the temporal primitives of ESTEREL are intuitive, which will make the following examples easy to understand: Since control is passed instantly from a finishing statement to the next one, the statement await 5 Second; await 5 Second is equivalent to await 10 Second.1 For the same reason, in the statement

```

every 60 MINUTE do

emit HOUR;

end every

```

the signal HOUR is simultaneous with the 60th occurrence of the signal MINUTE. There is no notion of physical time inside a synchronous program, but rather an order relationship between events (simultaneity and precedence). The physical time is thus an external signal, like any other external signal. As a result, one can write either abort TRAIN when 10 METER or abort TRAIN when 5 SECOND. In the statement

```

present A then

% something

end present;

present B then

% something else

end present

```

each component of the parallel construct can react independently to its signal. As a consequence, the program reacts either to A alone, B alone, or A and B at the same time.

These small examples show that the synchrony hypothesis leads to very natural code. Providing the designer with ideal temporal primitives greatly reduces the number of programming errors. The drawback is that, once compiled, the execution time of the program must match the temporal specifications. But of course the same problem arises with an asynchronous programming language like ADA. Finally, it is important to note that the synchronous approach has been validated through several real-life projects.

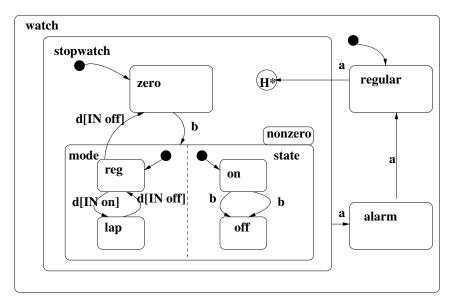

Figure 2.2: Statechart Specification of a Stopwatch

### 2.3 Components of a Statechart

**States:** There are three types of states; *Basic state*, *Or-state* and *And-state*. Basic states are those states which do not contain any other state, eg., *lap* is a basic state.

An *Or-state* is a compound state containing two or more other states. To be in an *Or-state* is to be in one of its component states. In this presentation, we will use *Or-State* synonymously with XOR-state, i.e., we can be in only one of the component states at a given time. An example of an *Or-state* in Figure 2.2 is *stopwatch*.

An And-state is also a compound state and staying in an And-state implies staying in each one of its substances. This is provided to model concurrency. The substates of an And-state may contain transitions which may be executed simultaneously. The state nonzero shown in Figure 2.2 is an And-state.

**Transitions:** A Transition in the Statechart is a five-tuple (source, target, event, action, condition). The arrow on the Statechart goes from source to target and is labeled as e[C]/a,

meaning that event e triggered the transition when condition C was valid and action a was carried out when the transition was taken. In general, a could be a list of actions to be taken.

**History and Defaults:** Statechart incorporates the idea of a history state in an OR-State. The history state keeps track of the substate most recently visited. This is denoted by H in a Or-state, as in the or-state stopwatch in Figure 2.2. A default state, marked by a shaded circle, is a substate of an or-state such that if a transition is made to the or-state and no other condition (e.g. enter-by-history) is specified, then that substate must be entered by default, e.g. *regular* is the default substate for the watch. In Figure 2.2, we have a deep-history state, which means that a transition to that state implies being in the maximal most recent set of basic substates. This can be represented by history states in each one of the Or-substates.

### 2.4 STATEMATE Semantics

The informal semantics of the STATEMATE version of Statecharts is provided through rules describing the semantics of a step. The main rules are listed below. For detailed discussions, the reader is referred to [57].

- 1. Reactions to external/internal events and changes that occur in a step can be sensed only after completion of the step.

- 2. Events are "live" for the duration of the step following the one in which they occur only.

- 3. Calculations in a step are based on the situation at the beginning of the step.

- 4. If two transitions are in conflict, then priority is given to that transition whose scope is higher in the hierarchy. The scope as defined in [57] is: The scope of a transition tr is the lowest Or-state in the hierarchy of states that is a proper common ancestor of all sources or targets of tr, including non-basic states that are explicit sources or targets of transition tr.

- 5. Each step follows the Basic Step Algorithm as described in [57].

## 2.5 Formalization of STATEMATE Semantics of Statecharts

Finite State machines (FSM) are widely used in the modeling in various areas. They are used to represent the flow of control and are amenable to formal analysis based on model checking technique.

Definition 2.5.1 A FSM consists of

- a finite set of Q of states,

- a finite alphabet  $\Sigma$ ,

- an initial state  $q^I \in Q$ ,

- a final state  $q^F \in Q$ ,

- a set  $\rightarrow \subseteq Q \times \Sigma \times Q$  of transitions,

Given a word  $\rho = \sigma_0 \sigma_1 \cdots \sigma_n$  over the alphabet  $\Sigma$ , an accepting run of the FSM M over  $\rho$  is sequence

(2.1)

$$q_0 \stackrel{\sigma_0}{\to} q_1 \stackrel{\sigma_1}{\to} \cdots \stackrel{\sigma_n}{\to} q_{n+1}$$

such that  $q_0$  equals the initial state  $q^I$  and  $q_{n+1}$  equals to the final state  $q^F$  and for  $0 \le i \le n, (q_i, \sigma_i, q_{i+1}0 \text{ is a transition of M}.$  The set of words  $\rho \in \Sigma^*$  over which M has an accepting run is called the language of M, denoted L(M).

FSMs can be composed parallelly and hierarchically to build Hierarchical Machines(HM) [2] called Statecharts(SC). It is assumed that these FSMs have mutually disjoint set of states.

**Definition 2.5.2** We define a Transition System as a special FSM which has no final state. A Transition System is a triple  $S = (Q, q^I, \rightarrow)$ , where S is a set of states,  $s \in S$  is the initial state,  $\rightarrow \subseteq Q \times L \times Q$  is the set of transitions. A reactive system can be defined as the composition of such transition systems. If S is a reactive system and S produces output O at the moment that input I is provided, the behaviour can be written as

$$S \xrightarrow[I]{O} S'$$

Definition 2.5.3 A HM is defined inductively as

- Base case: A TS  $(Q, q^I, \rightarrow)$  is a HM.

- Concurrency: If  $M_1, M_2 \cdots M_k$  are SCs then  $M_1 \parallel M_2 \parallel \cdots \parallel M_k$  is a HM.

- Hierarchy: If  $\mathcal{M}$  is a finite set of HMs,  $\gamma = (Q, q_I, \rightarrow)$  is a TM with states Q and  $\mu : Q \mapsto \mathcal{M}$  that associates each state  $q \in Q$  with a HM in  $\mathcal{M}$  then the triple  $(\gamma, \mathcal{M}, \mu)$  is a HM. Here  $\gamma$  is defined to be the root of the SC.

A HM of the form  $M_1 \parallel M_2 \parallel M_k$  is called a product expression and each  $M_i$  is called a component of the product expression. Such product forms are called AND-Charts.

**Definition 2.5.4** We define a HM of the form  $(\gamma, \mathcal{M}, E, \mu)$  as a Statechart, where the TS  $\gamma$  is called the top-level of the hierarchical expression, and each HM in  $\mathcal{M}$  is called a component of the Statechart. E is defined as the set of events which are propositions over  $\Sigma$  and their boolean combinations.

The set of events are defined over the alphabet  $\Sigma$  as boolean predicates

- $e \in \Sigma \rightarrow e \in E$ .

- $e \in \Sigma \rightarrow \neg e \in E$

- $e_1 \in \Sigma$  and  $e_2 \in \Sigma \rightarrow e_1 \land e_2 \in E$

- $e_1 \in \Sigma$  and  $e_2 \in \Sigma \rightarrow e_1 \lor e_2 \in E$

The mapping function  $\mu$  defines the type of Statecharts.

- If  $|\mu(s)| = 1$  then s is defined to be a single flat TS.

- If  $|\mu(s)| => 1$  then s is defined to be a parallel composition of TS.

- If  $|\mu(s)| = 0$  then s is defined to be a basic state.

The composition function  $\mu$  on M defines a successor function such that

$$\chi: \bigcup_{M \in \mathcal{M}} Q_M \to \mathbb{P}(\bigcup_{M \in \mathcal{M}} Q_M)$$

defined by

$$\chi(s) = \{s' \mid \exists M \in \mathcal{M} \bullet M \in \mu(s) \land s' \in Q_M\}$$

where  $s' \in \chi(s) \leftrightarrow s'$  is a state of the direct sub-automaton of s. We define a configuration as the set of states in which the system lies at any instant of time.

**Definition 2.5.5** Given a Statechart  $SC = (\gamma, \mathcal{M}, E, \mu)$ . A set  $C \subseteq \bigcup_{M \in \mathcal{M}} Q_M$  is a configuration of SC iff

- There exists one state of the root automaton  $\gamma \in C$

- $s \in C \land M \in \mu(s) \to \exists i \mid s_i \in Q_M \to s_i \in C$

- $s \in C \land (\exists s' \bullet s \in \chi(s') \to s' \in C)$

A transition  $s \stackrel{l}{\rightarrow} s'$  of  $M \in \mathcal{M}$  is enabled if  $s \in C$  and  $(C, E) \models l$ . Let  $Enabled_{C,E}$  be the set of enabled transitions. An automaton  $M \in \mathcal{M}$  is said to be enabled if  $s \stackrel{l}{\rightarrow} s' \in Enabled_{C,E}$ . We define two functions source and target such that  $source(s \stackrel{l}{\rightarrow} s') = s$ and  $target(s \stackrel{l}{\rightarrow} s') = s'$ . If t1 and t2 are two transitions then t1 is at a higher priority if  $source(t1) \prec source(t2)$ , where  $\prec$  is the preceding operator. **Definition 2.5.6** Harel [57] defines the execution of a Statechart as an execution step in (C, E) which consists of synchronously firing all the transitions in a maximal non-conflicting set of transitions. If  $\Upsilon \subseteq Enabled_{C,E}$  be the set of enabled transitions.  $\Upsilon$  will be maximal and non-conflicting iff

- $\forall t \in \Upsilon \not\exists t' \in Enabled_{C,E} \bullet Source(t) = Source(t')$

- $\forall t \in Enabled_{C,E} \bullet t \in \Upsilon \leftrightarrow \not\exists t' \in Enabled_{C,E}$

#### 2.5.1 Synchronous STEP Semantics

If two reactive systems  $S_1$  and  $S_2$  make a step together, they are defined to be concurrent and the global step represented as  $S_1 \parallel S_2 \xrightarrow[I]{O} S_1' \parallel S_2'$  which may be composed of two local steps  $S_1 \xrightarrow[I]{O} S_1'$  and  $S_2 \xrightarrow[I]{O} S_2'$ .

**Definition 2.5.7** Let  $K = (S, s_0, \stackrel{STEP}{\rightarrow})$  be TS where

- $S = Conf(\mu) \times \mathbb{P}(E)$  is the set of states of K, where  $Conf(\mu)$  is the set of all configurations.

- $s_0 \in S$ , where  $s_0 = (C_0, \phi)$  is the initial state of K where  $C_0$  is defined as follows. Let  $\gamma_{root} = (Q, q^I, rightarrow)$  and  $S_0 = \bigcup_{M \in \mathcal{M}} s_{0_M}$  then  $C_0 = (\chi \mid Q_0)^*(s_0)$

- $\overset{STEP}{\rightarrow} \subseteq S \times S$  is the transition relation of K where  $(C, E) \overset{STEP}{\rightarrow} (C', E')$  such that  $C' = (C/\chi^*(Source(\Upsilon))) \cup Target(\Upsilon) \cup (\chi^+(target(\Upsilon)) \cap \bigcup_{M \in \mathcal{M}} s_{0_M})$  and  $E' = E \cup Action(label(\Upsilon))$

This definition of composition models synchronous behaviour. This gives us following advantages

- 1. The reaction time is short as possible and we take it as 0.

- 2. The timing behaviour is abstract enabling us further refinement without bothering about delays since 0 + 0 = 0

The execution semantics of a SC now can be defined in terms of steps of execution of the composite systems. Responsiveness, Modularity and Causality [63] are three very important criteria in judging the semantics.

**Definition 2.5.8 Responsive** A semantics S is responsive if for any two distinct input sets  $I_1$  and  $I_2$  and non-empty output set O with  $O \cap (I_1 \cup I_2) = \phi$  such that

$$S \xrightarrow[I_1]{O} \text{ and } S \xrightarrow[I_2]{O}$$

**Definition 2.5.9** Modularity A semantics is modular if for any two systems  $S_1$  and  $S_2$  the following two statements are equivalent

1.  $S_1 \parallel S_2 \xrightarrow[I_1]{O} S'_1 \parallel S'_2$ 2.  $S_i \xrightarrow[I \cup O_{i-1}]{O_i} S'_i$  for i=1,2

where  $O = O_1 \cup O_2$

**Definition 2.5.10** Causality A semantics is causal if we can add to every step  $S \xrightarrow[I]{O} S'$  a partial order  $\leq$  on  $I \cup O$ , such that

- 1. if  $S \xrightarrow[I]{O} and S \xrightarrow[I]{O} and I, O \neq \phi$ , then there is at least one dependency between I and O i.e  $\exists a \in I, b \in O$  with  $a \leq b$

- 2. if  $S_1 \parallel S_2 \xrightarrow[I_1]{O} S'_1 \parallel S'_2$  with causal order  $\leq$  then there should exist a partitioning into processes  $T_1, T_2 \cdots T_n$  and causal orders  $\leq_1, \cdots \leq_n$  such that  $\leq \upharpoonright (I_i \cup O_i) = \leq_i$  and  $T_1 \parallel \cdots \parallel T_n = S_1 \parallel S_2, n \geq 2$ , and for each  $T_i \xrightarrow[I_i]{O_i} T'_i$ , these steps combine into the steps of  $S_1 \parallel S_2$

It has been proved in [63], that no semantics of reactive systems can be responsive, modular and causal at the same time. In our framework, we assume the following

- Every observable step is divided into a number of micro-steps. Actions and reactions strictly follow the order in micro-steps. The events generated as a reaction to some input can only be sensed in the micro-step following the input.

- Events are generated at the next step but before the reaction of the system is completely stable (no more transitions are possible), no input from environment is possible.