# Analysis and Design of FFT Processor Architecture for OFDM Applications

#### **THESIS**

Submitted in partial fulfilment of the requirements for the degree of DOCTOR OF PHILOSOPHY

by

Ganjikunta Ganesh Kumar ID. No. 2013PHXF0007H

Under the Supervision of **Prof. Subhendu K Sahoo**

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE - PILANI 2018

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE - PILANI

#### **CERTIFICATE**

This is to certify that the thesis entitled, <u>Analysis and Design of FFT Processor Architecture for OFDM Applications</u> and submitted by <u>Ganjikunta Ganesh Kumar</u> ID No. <u>2013PHXF0007H</u> for award of Ph.D. of the Institute embodies original work done by him under my supervision.

Supervisor

Prof. Subhendu K Sahoo

Associate Professor,

BITS-Pilani, Hyderabad Campus

Date:

#### Acknowledgements

I wish to express my sincere gratitude to my supervisor Prof. Subhendu K Sahoo for his continuous help and valuable guidance, without which this work would not have been accomplished. His unwavering support through-out the journey has been a constant source of encouragement. I am grateful to Prof. G. Sundar, Director, Birla Institute of Technology and Science - Pilani, Hyderabad Campus, for providing all the necessary facilities required to carried out my research. I also take this opportunity to thank the previous and current Heads of the Department of Electrical Engineering, Prof. Y. Yoganandam and Prof. Sanket Goel, respectively for the support and help extended to me. I would also like to thank my Doctoral Advisory Committee (DAC): Prof. Prabhakara Rao and Dr. S. K. Chatterjee, for their timely feedback and insightful comments. I heartily thank Prof. Pramod Kumar Meher, School of Computer Engineering, Nanyang Technological University, Singapore, for his support throughout the research work. To all my friends in the department, thank you for your cooperation and camaraderie - especially to Mr. Avinash S Vaidya, Mr. Sai Phaneendra P, Mr. Goutham Makkena, and Mr. Chetan Kumar V for helping me to overcome difficult phases and not letting me give up. Lastly, my warmest acknowledgments to my parents, Mr. Venkata Ramudu and Mrs. Lakshmi Devi, my sister Mrs. Bhargavi and my brother-in-law Mr. P Manohara for their unconditional love, and support throughout my Ph.D.

#### Abstract

The aim of this thesis is to analyze fast Fourier transform (FFT) at algorithmic, architecture, and arithmetic level and the possibilities to reduce complexity and power consumption of the twiddle factor multiplication in FFT for IEEE 802.11a and 802.15.4-g OFDM systems. In algorithmic level, we have analyzed various algorithms in terms of arithmetic complexity (number of real multiplications and real additions), that effect accuracy, area, and power consumption of the architecture. At architecture level, different FFT architectures are analyzed and compared with respect to number of complex multipliers, complex adders and memory. Further, the design choice of FFT algorithm and architecture for OFDM systems is discussed. At arithmetic level, the hardware implementation of the twiddle factor multiplication is presented. Initially, the implementation of twiddle factor multiplication using general complex multiplication is discussed and then, the twiddle factor multiplication architecture based on constant multiplications are investigated.

Based on the FFT analysis, two architectures are proposed: i) fixed length (64-point) FFT for IEEE 802.11a WLAN application and ii) variable-length (16/32/64/128-point) FFT for IEEE 802.15.4 – g WPAN application. For fixed-length FFT, novel pipelined single-path delay feedback (SDF) architectures are proposed for radix- $2^{3}$  and radix- $2^{3}$  algorithms using modified complex constant multipliers. These architectures

result in low hardware complexity and consumes low power compared to earlier FFT architectures.

For variable-length (16/32/64/128-point) FFT, a SDF architecture is proposed based on mixed-radix algorithm to reduce the number of complex multipliers. It employs a configurable complex constant multiplier (CCCM) structure instead of fixed constant multiplier to perform variable-length twiddle factor multiplication. A hardware-sharing mechanism is introduced to reduce the memory space requirements of the proposed FFT computation scheme. Both Field Programmable Gate Array (FPGA) and Application Specific Integrated Circuit (ASIC) targeted synthesis results of the proposed variable-length processor are presented.

# Contents

| Certificate                           | i   |

|---------------------------------------|-----|

| Acknowledgements                      | ii  |

| Abstract                              | iii |

| Contents                              | v   |

| List of Figures                       | Х   |

| List of Tables                        | xiv |

| Abbreviations                         | xvi |

| 1 Introduction                        | 1   |

| 1.1 Discrete Fourier Transform:       | 2   |

| 1.1.1 Computational complexity of DFT | 6   |

*Contents* vi

|          | 1.2 | Fast C | Computation of DFT: A Historical Perspective               | 8  |

|----------|-----|--------|------------------------------------------------------------|----|

|          |     | 1.2.1  | Applications of FFT                                        | 10 |

|          | 1.3 | Motiva | ation                                                      | 11 |

|          | 1.4 | Object | tives of the Thesis                                        | 12 |

|          | 1.5 | Organ  | ization of the Thesis                                      | 13 |

| <b>2</b> | Adv | ancem  | nents in FFT Algorithm                                     | 15 |

|          | 2.1 | Introd | uction                                                     | 15 |

|          | 2.2 | Compl  | lex-valued FFT Algorithms                                  | 16 |

|          |     | 2.2.1  | Radix-2 FFT algorithms                                     | 16 |

|          |     | 2.2.2  | Radix-4 FFT algorithm                                      | 20 |

|          |     | 2.2.3  | Radix- $2^i$ and Higher radix FFT Algorithms               | 22 |

|          |     | 2.2.4  | Split-Radix FFT                                            | 27 |

|          |     | 2.2.5  | Computational Complexity for Complex-Valued FFT Algorithms | 29 |

|          | 2.3 | Real-v | ralued FFT Algorithms                                      | 30 |

|          |     | 2.3.1  | Computation of the RFFT using the CFFT                     | 31 |

|          |     | 2.3.2  | FFT of Real-Valued data                                    | 34 |

|          |     | 2.3.3  | Fast Hartley Transform                                     | 35 |

|          |     | 2.3.4  | Quick Discrete Fourier Transform                           | 37 |

|          |     | 2.3.5  | Computational Complexity for Real-Valued FFT Algorithms    | 38 |

*Contents* vii

|   | 2.4 | Specia  | l cases of the FFT algorithms                     | 39 |

|---|-----|---------|---------------------------------------------------|----|

|   |     | 2.4.1   | FFT Pruning                                       | 39 |

|   |     | 2.4.2   | Fast Fourier Transform of Sparse Input            | 40 |

|   |     | 2.4.3   | Scaled DFTs                                       | 41 |

|   |     | 2.4.4   | Multidimensional FFTs                             | 42 |

|   |     | 2.4.5   | Quantum Fourier Transform                         | 43 |

|   | 2.5 | Conclu  | asion                                             | 45 |

| 3 | FFT | Γ Arch  | itectures and Design choice for OFDM systems      | 47 |

|   | 3.1 | Memo    | ry based Architectures                            | 48 |

|   |     | 3.1.1   | Single Memory                                     | 49 |

|   |     | 3.1.2   | Dual Memory                                       | 49 |

|   |     | 3.1.3   | Array Memory                                      | 50 |

|   |     | 3.1.4   | Cached Memory                                     | 51 |

|   | 3.2 | Pipelii | ned Architectures                                 | 52 |

|   |     | 3.2.1   | Delay Feedback Architectures                      | 53 |

|   |     |         | 3.2.1.1 Single-path Delay Feedback (SDF)          | 53 |

|   |     |         | 3.2.1.2 Multi-path Delay Feedback (MDF)           | 58 |

|   |     | 3.2.2   | Delay Commutator Architectures                    | 59 |

|   |     |         | 3.2.2.1 Multi-path Delay Commutator Architectures | 59 |

*Contents* viii

|   |                |         | 3.2.2.2     | Single-path Delay Commutator Architectures      | 62 |

|---|----------------|---------|-------------|-------------------------------------------------|----|

|   | 3.3            | Design  | n choice fo | or OFDM systems                                 | 63 |

|   | 3.4            | Concl   | usion       |                                                 | 66 |

| 4 | $\mathbf{Twi}$ | iddle F | Factor M    | ultiplication and its Hardware                  | 68 |

|   | 4.1            | Gener   | al Comple   | ex Multiplication                               | 69 |

|   |                | 4.1.1   | Fixed-w     | idth Multiplication                             | 72 |

|   | 4.2            | Const   | ant Multi   | plication                                       | 74 |

|   |                | 4.2.1   | Single C    | Constant Multiplication (SCM)                   | 75 |

|   |                | 4.2.2   | Multiple    | Constant Multiplication (MCM)                   | 78 |

|   | 4.3            | Concl   | usion       |                                                 | 79 |

| 5 | Pip            | eline F | `FT Arch    | nitecture Design for an OFDM-based IEEE 802.11a | 80 |

|   | 5.1            | Design  | n consider  | ation of the FFT for 64-point                   | 81 |

|   | 5.2            | Propo   | sed Modif   | fied FFT Architectures                          | 82 |

|   |                | 5.2.1   | Butterfly   | y unit                                          | 84 |

|   |                | 5.2.2   | Modified    | l CSD Complex Constant Multipliers              | 85 |

|   |                |         | 5.2.2.1     | $CCMW_{64}$ multiplier unit                     | 90 |

|   |                |         | 5.2.2.2     | $CCMW_{16}$ multiplier unit                     | 94 |

|   |                |         | 5.2.2.3     | $CCMW_8$ multiplier unit                        | 95 |

|   | 5.3            | Comp    | arison and  | d Experimental results                          | 96 |

Contents

|               | 5.4   | Conclusion                                                 | 101 |

|---------------|-------|------------------------------------------------------------|-----|

| 6             | Var   | iable-Length FFT Architecture for MR-OFDM                  | 102 |

|               | 6.1   | Introduction                                               | 103 |

|               | 6.2   | Decomposition and Twiddle Factors at each stage of FFT     | 106 |

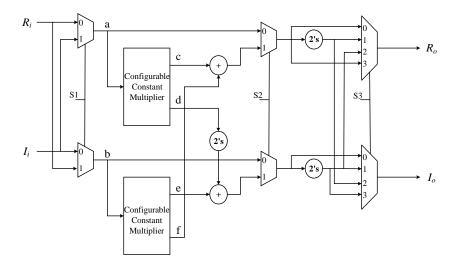

|               | 6.3   | Proposed Architecture                                      | 108 |

|               |       | 6.3.1 Multiplexer switching to perform variable-length FFT | 110 |

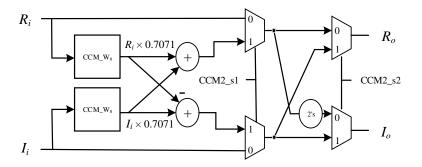

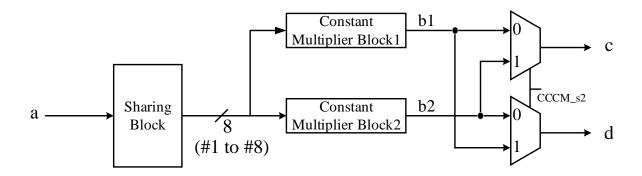

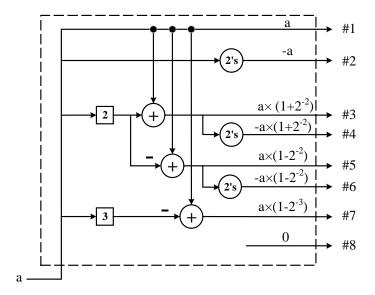

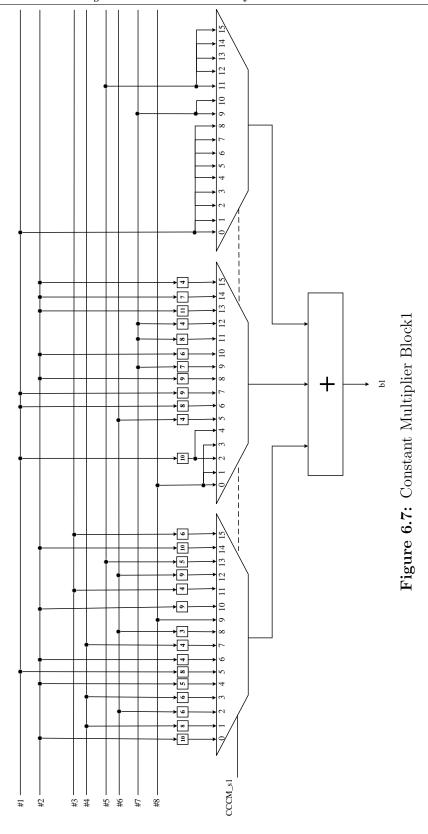

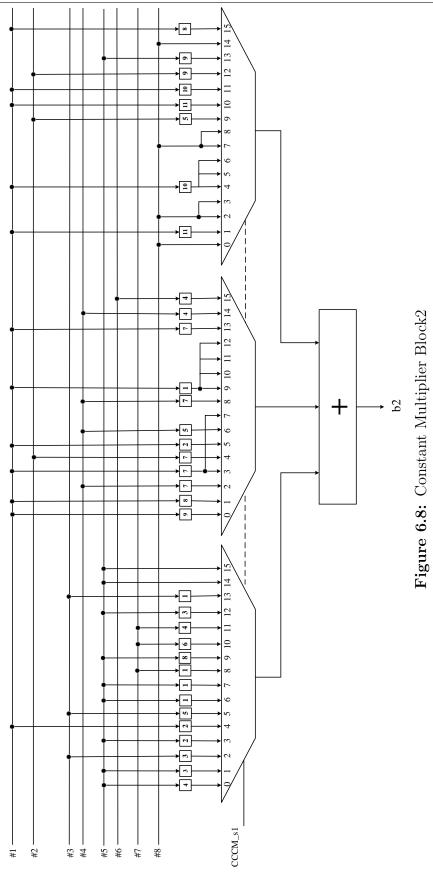

|               |       | 6.3.2 Modified Complex Constant Multipliers                | 111 |

|               |       | 6.3.2.1 Configurable $W_{128}$ Multiplier                  | 114 |

|               | 6.4   | Comparison and Results                                     | 119 |

|               | 6.5   | Conclusion                                                 | 122 |

| 7             | Con   | nclusions and Future Work                                  | 123 |

|               | 7.1   | Future Work                                                | 125 |

|               |       |                                                            |     |

|               |       |                                                            |     |

| $\mathbf{Bi}$ | bliog | graphy                                                     | 126 |

# List of Figures

| 1.1 | A sine wave                                                         | 4  |

|-----|---------------------------------------------------------------------|----|

| 1.2 | Illustration of the DFT for $N=4$ of a sine wave. (a) Finite-length |    |

|     | sequence $x(n)$ (b) DFT magnitude. (c) DFT phase                    | 5  |

| 2.1 | Length-4, DIT Radix-2 FFT                                           | 18 |

| 2.2 | Length-4, DIF Radix-2 FFT                                           | 19 |

| 2.3 | Radix-4 FFT butterfly                                               | 21 |

| 2.4 | Signal flow graph of 16-point radix-2 <sup>2</sup> DIF FFT          | 25 |

| 2.5 | Split-Radix FFT                                                     | 28 |

| 2.6 | Quick Discrete Fourier Transform                                    | 36 |

| 2.7 | FFT pruning                                                         | 40 |

| 3.1 | Single memory architecture                                          | 49 |

| 3.2 | Dual memory architecture                                            | 50 |

| 3.3 | Array memory architecture                                           | 51 |

List of Figures xi

| 3.4  | Cached memory architecture                                     | 52 |

|------|----------------------------------------------------------------|----|

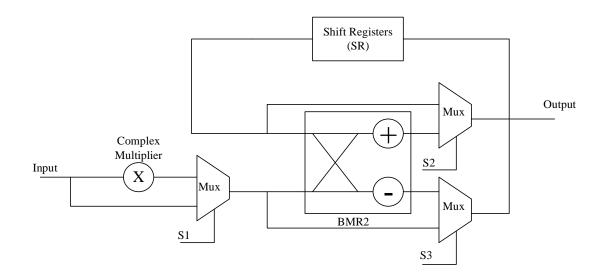

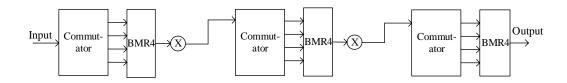

| 3.5  | Basic building blocks of R2SDF architecture                    | 53 |

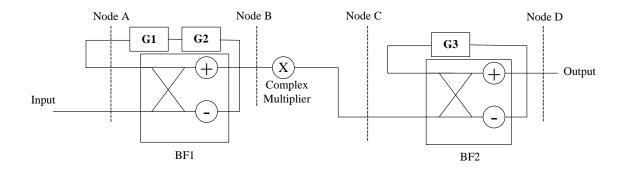

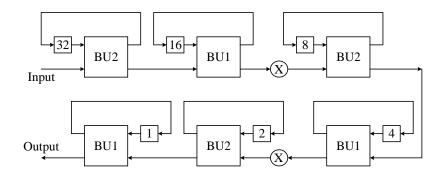

| 3.6  | R2SDF 4-point DIF FFT architecture                             | 54 |

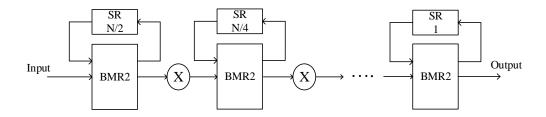

| 3.7  | N-point R2SDF Architecture                                     | 56 |

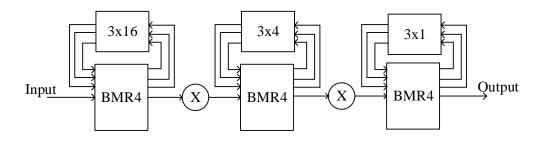

| 3.8  | Length-64, R4SDF Architecture                                  | 57 |

| 3.9  | Length-64, R2 <sup>2</sup> SDF Architecture                    | 57 |

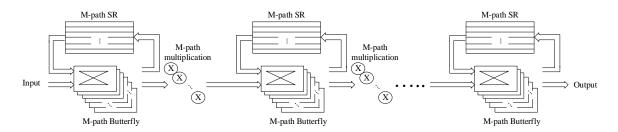

| 3.10 | Multi-Path Delay Feedback Pipelined FFT Architecture           | 58 |

| 3.11 | R2MDC 4-point FFT architecture                                 | 59 |

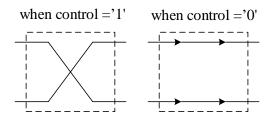

| 3.12 | Operation of the commutator in R2MDC architecture              | 60 |

| 3.13 | Step-by-step process of an 4-point R2MDC FFT architecture      | 61 |

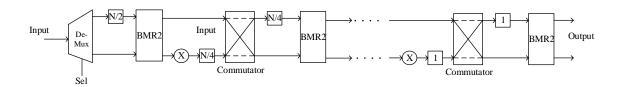

| 3.14 | R2MDC $N$ -point FFT architecture                              | 62 |

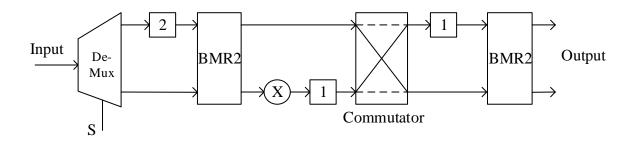

| 3.15 | Length-16, R4MDC Architecture                                  | 62 |

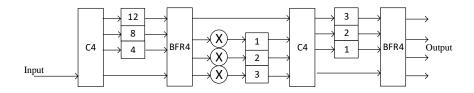

| 3.16 | Length-64, R4SDC Architecture                                  | 63 |

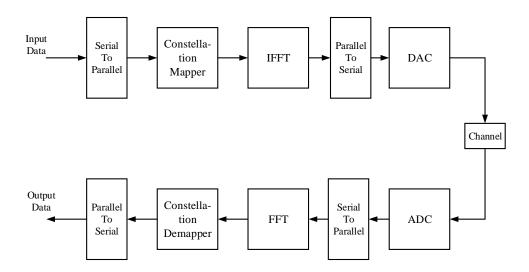

| 3.17 | Block diagram of FFT based OFDM system                         | 64 |

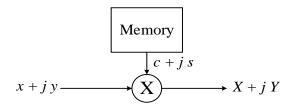

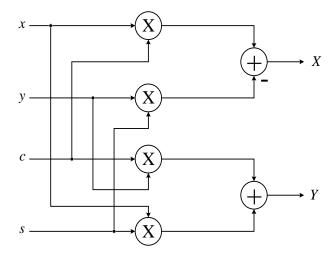

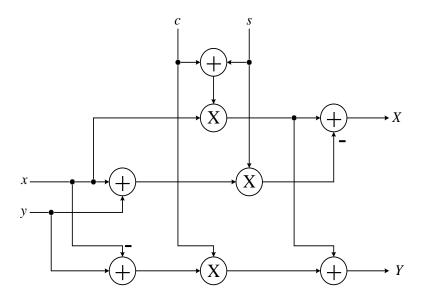

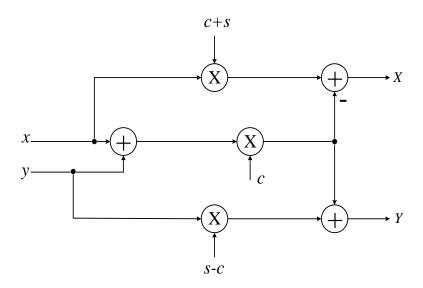

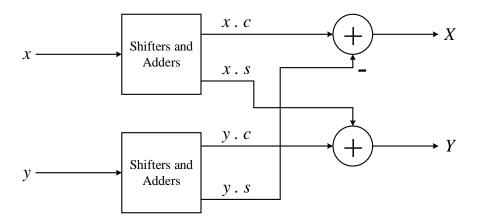

| 4.1  | General complex multiplier                                     | 69 |

| 4.2  | Approach I with four multipliers and two adders                | 70 |

| 4.3  | Approach II with three multipliers and five adders             | 71 |

| 4.4  | Approach III with three multipliers and three adders           | 72 |

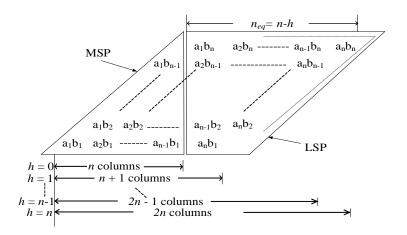

| 4.5  | Partial product array for $n \times n$ unsigned multiplication | 73 |

List of Figures xii

| 4.6 | General constant multiplier                                                                      | 75  |

|-----|--------------------------------------------------------------------------------------------------|-----|

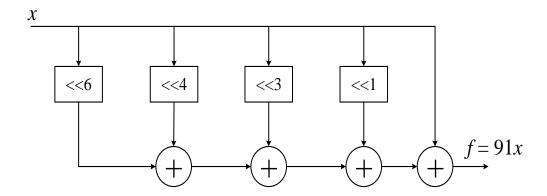

| 4.7 | Constant multiplier using shifters and adders                                                    | 76  |

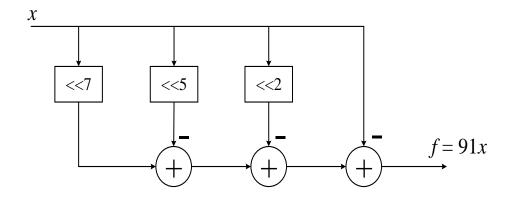

| 4.8 | Optimized constant multiplier                                                                    | 77  |

| 4.9 | Constant multiplier using MCM                                                                    | 78  |

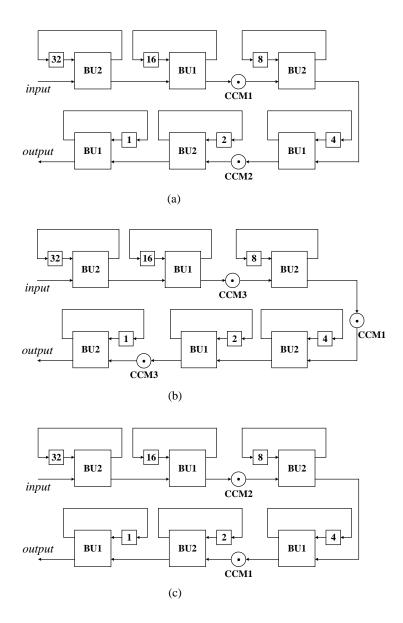

| 5.1 | Radix-2 $^i$ pipelined SDF 64-point FFT : (a) R2 <sup>2</sup> SDF , (b) R2 <sup>3</sup> SDF, and |     |

|     | (c) R2 <sup>4</sup> SDF                                                                          | 83  |

| 5.2 | Butterfly units BU1                                                                              | 84  |

| 5.3 | Butterfly units BU2                                                                              | 84  |

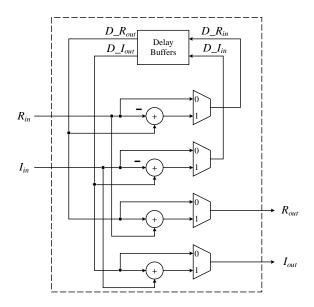

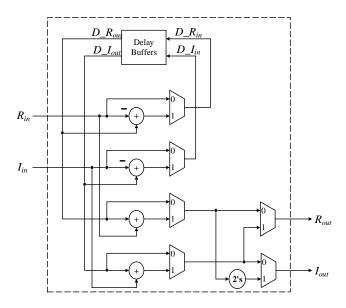

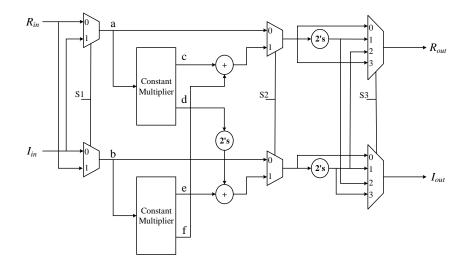

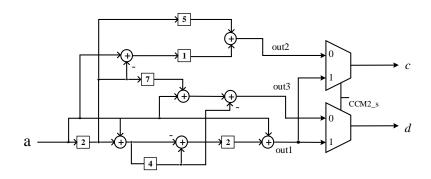

| 5.4 | Proposed modified CSD multiplier for CCM1 and CCM2                                               | 87  |

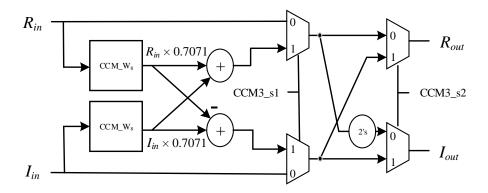

| 5.5 | CSD complex constant multiplier for CCM3                                                         | 88  |

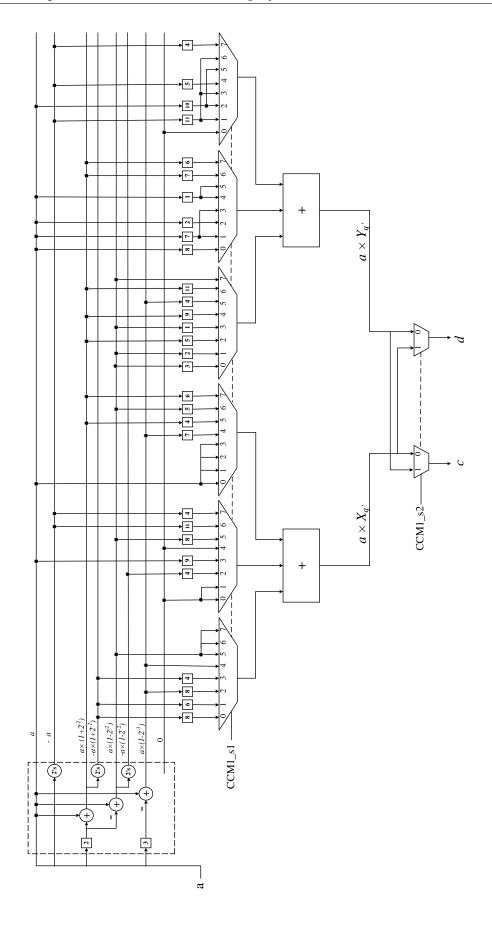

| 5.6 | Block diagram of $CCMW_{64}$ multiplier unit                                                     | 89  |

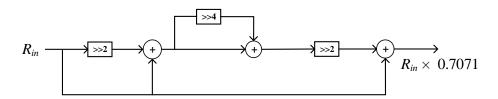

| 5.7 | Block diagram of $CCMW_{16}$ multiplier unit                                                     | 95  |

| 5.8 | Block diagram of $CCMW_8$ multiplier unit                                                        | 95  |

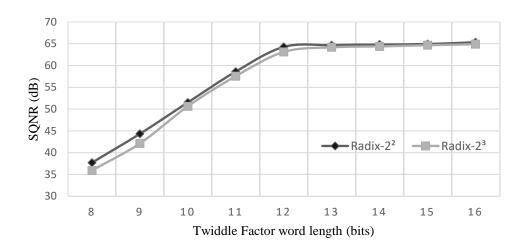

| 5.9 | SQNR versus twiddle factor word length for R22SDF and R23SDF                                     | 99  |

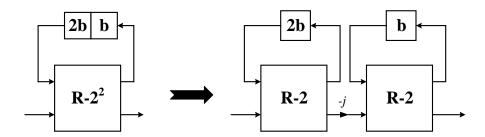

| 6.1 | Radix- $2^2$ butterfly constructed from two Radix-2 butterflies                                  | 107 |

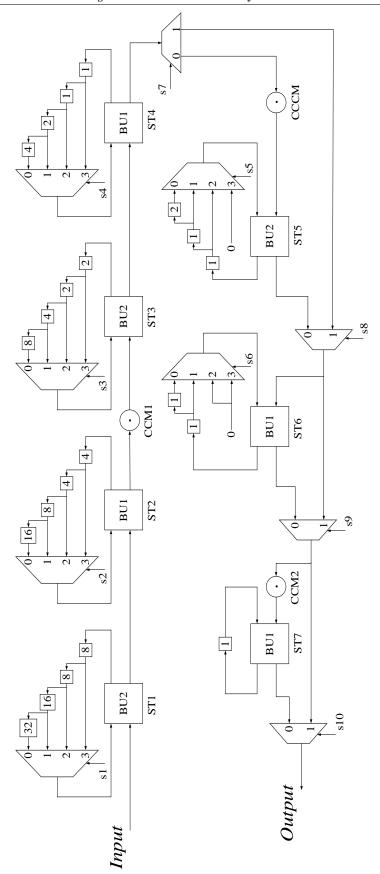

| 6.2 | Proposed $16/32/64/128$ -point SDF pipeline FFT architecture                                     | 109 |

| 6.3 | CSD complex constant multiplier for CCM1 and CCCM                                                | 112 |

| 6.4 | CSD complex constant multiplier for CCM2                                                         | 112 |

| 6.5 | $W_{128}$ configurable constant multiplier block diagram                                         | 114 |

| T           | Figures       | •••   |

|-------------|---------------|-------|

| I not ot    | · L'a gauge a | 37111 |

| 177.51. 111 | PARTITES      | X111  |

| 1 00 C C    | 1 1941 00     | 2111  |

| 6.6 | Sharing block              |

|-----|----------------------------|

| 6.7 | Constant Multiplier Block1 |

| 6.8 | Constant Multiplier Block2 |

# List of Tables

| 2.1 | Twiddle factor at each stage to compute $N$ -point FFT $\ldots \ldots$     | 27 |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Number of real multiplications to compute a length- $\!N$ Complex DFT $$ . | 29 |

| 2.3 | Number of real additions to compute a length- $N$ Complex DFT              | 29 |

| 2.4 | Number of real multiplications to compute the DFT for a real-valued        |    |

|     | input                                                                      | 37 |

| 2.5 | Number of real additions to compute the DFT for a real-valued input .      | 38 |

| 3.1 | Data output order of the R2SDF pipelined architecture for 4-point FFT      | 55 |

| 3.2 | Comparison of the number of complex multipliers, adders, and memory        |    |

|     | units for various pipelined architectures                                  | 65 |

| 5.1 | Base number of twiddle factor at each stage to compute $64$ -point FFT .   | 82 |

| 5.2 | CSD representations of eight sets constant values for composing twiddle    |    |

|     | factors                                                                    | 91 |

| 5.3 | Selection of the Twiddle Factors in CCM1                                   | 92 |

List of Tables xv

| 5.4 | Selection of the Twiddle Factors in CCM2                                       |

|-----|--------------------------------------------------------------------------------|

| 5.5 | Selection of the Twiddle Factors in CCM3                                       |

| 5.6 | Comparison of the proposed $R2^i\mathrm{SDF}$ architectures to other architec- |

|     | tures for the computation of a 64-point FFT                                    |

| 5.7 | Comparison of number of adders for $CCMW_{64}$ multiplier unit 97              |

| 5.8 | Comparison of various 64-point FFT architectures                               |

| 6.1 | MR-OFDM parameters                                                             |

| 6.2 | Decomposition of four different FFT lengths                                    |

| 6.3 | Sequence of the $16/32/64/128$ -point FFT twiddle factor computation           |

|     | for mixed-radix FFT Algorithms                                                 |

| 6.4 | Selection of variable-length FFT                                               |

| 6.5 | CSD representations of 16 sets constant values for composing twiddle           |

|     | factors                                                                        |

| 6.6 | Selection of the Twiddle Factors in CCCM                                       |

| 6.7 | Comparison of the proposed architecture to other architectures for the         |

|     | computation of a 128-point FFT                                                 |

| 6.8 | Comparison of the proposed architecture to other architectures for the         |

|     | computation of a 128-point FFT                                                 |

| 6.9 | Comparison of various 128-point FFT architectures                              |

#### Abbreviations

**DFT** Discrete Fourier Transform

IDFT Inverse Discrete Fourier Transform

FFT Fast Fourier Transform

IFFT Inverse Fast Fourier Transform

OFDM Orthogonal Frequency Division Multiplexing

FPGA Field-Programmable Gate Array

ASIC Application-Specific Integrated Circuit

CORDIC COordinate Rotation DIgital Computer

CFFT Complex-valued Fast Fourier Transform

**DIT** Decimation In Time

DIF Decimation In Frequency

RFFT Real-valued Fast Fourier Transform

SRFFT Split-Radix Fast Fourier Transform

SDFT Scaled Discrete Fourier Transform

SDF Single-path Delay Feedback

CSD Canonical Signed Digit

ASIC Application Specific Integrated Circuit

FPGA Field Programmable Gate Array

**3GPP** 3<sup>rd</sup> Generation Partnership Project

LTE Long Term Evolution

MDCT Modified Discrete Cosine Transform

SFFT Sparse Fast Fourier Transform

QFT Quantum Fourier Transform

PEs Processing Elements

R2SDF Radix-2 Single-path Delay Feedback

R4SDF Radix-4 Single-path Delay Feedback

**BF** Butterfly

R2<sup>2</sup>SDF Radix-2<sup>2</sup> Single-path Delay Feedback

MDF Multi-path Delay Feedback

R2MDC Radix-2 Multipath Delay Commutator

R4MDC Radix-4 Multipath Delay Commutator

SDC Single-path Delay Commutator

R4SDC Radix-4 Single-path Delay Commutator

DAC Digital-to-Analog Converter

ADC Analog-to-Digital Converter

$\mathbf{R}2^{i}\mathbf{SDF}$  Radix- $2^{i}$  Single-path Delay Feedback

SRMDC Split-Radix Multi-path Delay Commutator

LSP Least Significant Part

MSP Most Significant Part

SCM Single Constant Multiplication

MCM Multiple Constant Multiplication

ROM Read- Only Memory

CSD Canonical Signed Digit

CCM Complex Constant Multiplier

CCCM Configurable Complex Constant Multiplier

SQNR Signal-to-Quantization-Noise Ratio

MR-OFDM Multi-Rate and multi-regional Orthogonal

Frequency Division Multiplexing

MR-FSK Multi-Rate and multi-regional Frequency Shift Keying

MR-OQPSK Multi-Rate and multi-regional Offset Quadrature

Phase Shift Keying

DSSS Direct Sequence Spread Spectrum

SUN Smart Metering Utility Networks

AMR Automatic Meter Reading

RF Radio Frequency

LR-WPAN Low Rate Wireless Personal Area Network

WPAN Wireless Personal Area Network

DSP Digital Signal Processing

WLAN Wireless Local Area Network

**nm** Nanometer

ns Nanosecond

$\mu m^2$  Square Micrometer

### Chapter 1

### Introduction

The discrete Fourier transform (DFT) is the most widely used tool in digital signal processing (DSP) systems. It has indispensable role in many applications, such as speech, audio and image processing, signal analysis, communication systems, and many others. It maps time domain sequence to a frequency domain sequence of the same length, while the inverse discrete Fourier transform (IDFT) performs the opposite. The brute-force computation of the DFT of length N requires  $O(N^2)$  multiplications. Due to such high computational requirement, it was not possible to use that for real-time and online DSP applications until 1965, when Cooley and Tukey [1] developed the famous fast Fourier transform (FFT) algorithm. It could be possible to reduce the operation count of DFT from  $O(N^2)$  to  $O(N \log_2 N)$ , for a DFT of length N. During the last 50

years, the innovations in algorithms and architectures have made remarkable progress in the efficiency of computation of the FFT.

This chapter is organized as follows: In Section 1.1, the specifications of DFT and its computational complexity are presented. The basic technique, namely the divide and conquer approach (FFT algorithm) that reduces the computational complexity of DFT is presented in Section 1.2. The motivation of the thesis is discussed in Section 1.3. This chapter further discusses the main objectives and organization of the thesis in Sections 1.4 and 1.5, respectively.

#### 1.1 Discrete Fourier Transform:

The N-point DFT/IDFT are, respectively, calculated as

$$X(k) = \sum_{n=0}^{N-1} x(n)W_N^{nk}, \quad k = 0, 1, 2, ..., N-1,$$

(1.1)

and

$$x(n) = \frac{1}{N} \sum_{k=0}^{N-1} X(k) W_N^{-nk}, \quad n = 0, 1, 2, ..., N-1,$$

(1.2)

where n is the time index and k is the frequency index. The twiddle factor  $W_N^{nk}$  can be represented as:

$$W_N^{nk} = e^{-j2\pi nk/N} = \cos\left(\frac{2\pi nk}{N}\right) - j\,\sin\left(\frac{2\pi nk}{N}\right) \tag{1.3}$$

In equations (1.1) and (1.2), the data sequence x(n) may be complex while the  $k^{th}$  spectral component X(k) is always complex. These two equations differ only in the sign (–) of the exponent of the twiddle factor  $W_N$  and the scale factor 1/N. Therefore, the algorithms for efficient computation of DFT could be applied for the efficient computation of IDFT [2] by simple and straightforward modifications.

#### Significance of the DFT

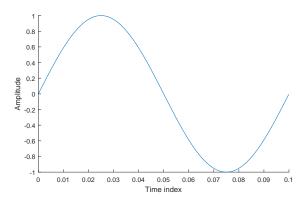

To illustrate the significance of DFT let us consider a 4-point DFT of samples of a sinusoidal signal of 10Hz which is expressed as:

$$x(t) = \sin(2\pi \cdot 10 \cdot t) \tag{1.4}$$

For this sine wave, the fundamental period  $T_0 = 0.1 \ s$  as shown in Fig. 1.1. Let us take the sample rate  $f_s = 40Hz$  i.e. the input is sampled at every  $1/f_s = T = 0.025 \ s$ . Because N = 4, we need 4 input sample values which could be obtained as follows:

$$x(n) = x(nT) = \sin(2\pi \cdot 10 \cdot nT) = \sin\left(\frac{n\pi}{2}\right)$$

Figure 1.1: A sine wave.

at

$$n = 0, x(0) = \sin(0) = 0$$

at  $n = 1, x(1) = \sin(\frac{\pi}{2}) = 1$

at  $n = 2, x(2) = \sin(\pi) = 0$

at  $n = 3, x(3) = \sin(\frac{3\pi}{2}) = -1$

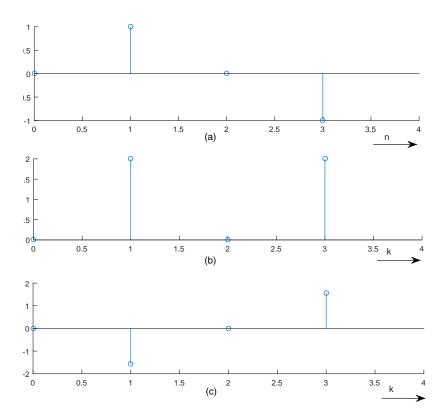

The finite-length sequence of x(n) is shown in Fig. 1.2(a), where x-axis represents the values of n and y-axis represents the amplitude. The twiddle factors for N=4 are defined as:

$$W_4^{nk} = \cos\left(\frac{2\pi nk}{4}\right) - j\sin\left(\frac{2\pi nk}{4}\right) \tag{1.5}$$

where nk = 0 to N - 1 i.e., 0 to 3. From equation (1.5),  $W_4^{nk}$  values are:  $W_4^0 = 1, W_4^1 = -j, W_4^2 = -1, W_4^3 = j$ .

**Figure 1.2:** Illustration of the DFT for N=4 of a sine wave. (a) Finite-length sequence x(n) (b) DFT magnitude. (c) DFT phase.

The general equation for the 4-point DFT could be written as

$$X(k) = \sum_{n=0}^{3} x(n)W_4^{kn}$$

$$= x(0)W_4^{(k)(0)} + x(1)W_4^{(k)(1)} + x(2)W_4^{(k)(2)}$$

$$+ x(3)W_4^{(k)(3)} \quad 0 \le k \le 3$$

(1.6)

The DFT output values are obtained for k = 0, 1, 2, 3 as

$$X(k) = \begin{bmatrix} 0 & -2j & 0 & 2j \end{bmatrix}$$

From the DFT output values, the sinusoidal signal can be plotted in terms of its magnitude and phase as shown in Fig. 1.2(b) and 1.2(c), respectively. The value X(k) is said to provide information about the  $k^{th}$  frequency bin.

The frequency resolution can be obtained as:

$$\triangle f = \frac{1}{T_0} = \frac{1}{NT} = \frac{f_s}{N} \tag{1.7}$$

As the fundamental period of a sinusoidal signal is 0.1 s, so the frequency resolution is 10Hz. From equation (1.7), one can observe that to increase the frequency resolution, the number of points of data N must be increased [3].

#### 1.1.1 Computational complexity of DFT

Computation of each DFT component directly using equation (1.1) requires N complex multiplications and (N-1) complex additions. Therefore, to compute all the N values of DFT requires a total number of  $N^2$  complex multiplications and N(N-1) complex additions.

The DFT of N-point complex-valued input sequence, x(n) then can be expressed as

$$X(k) = X_{R}(k) + jX_{I}(k)$$

$$= \sum_{n=0}^{N-1} [x_{R}(n) + jx_{I}(n)] [W_{RN}^{kn} + jW_{IN}^{kn}]$$

$$= \sum_{n=0}^{N-1} [(x_{R}(n)W_{RN}^{kn} - x_{I}(n)W_{IN}^{kn})]$$

$$+ j [x_{R}(n)W_{IN}^{kn} + x_{I}(n)W_{RN}^{kn}]$$

(1.8)

where k = 0, 1, 2, ....., N - 1. Assuming that each complex multiplication in equation (1.8) is realized by 4 real multiplications and 2 real additions, while each complex addition is realized by 2 real additions, the direct computation of equation (1.8) requires  $4N^2$  and 2N(N-1) number of real multiplications and real additions, respectively [4]. Moreover, the computation of DFT also requires a number of indexing and addressing operations to fetch the input values, intermediate results, and complex coefficients  $W_N^{kn}$  and to store the final results. For large values of N, the arithmetic complexity of DFT is very high. Therefore, different algorithms have been proposed to reduce the arithmetic complexity for fast and efficient computation of DFT.

# 1.2 Fast Computation of DFT: A Historical Perspective

The computational complexity of DFT is substantially reduced by using the following trigonometric symmetry and periodicity of the twiddle factor  $W_N^{kn}$ :

$$W_N^{k+\frac{N}{2}} = -W_N^k(Symmetry\ Property)$$

(1.9)

$$W_N^{k+N} = W_N^k(Periodicity\ Property)$$

(1.10)

These properties were known for a long time even before the inception of digital computation. Heideman et al. [5] have traced the first appearance of the FFT back to Gauss in the year 1805. Gauss developed an algorithm to calculate the DFT which is equivalent to one of the Cooley-Tukey algorithm. However, Gauss never published his algorithm outside his collected works. A prior work of Danielson and Lanczos [6] referred to Runge [7] for their doubling algorithm in X-ray scattering problems. Their algorithm showed how to reduce a DFT in 2N points to two DFTs on N points with only slightly more than N operations. The complexity of these algorithms was much less than  $N^2$  but more than  $N \log_2 N$ .

The early discoveries of the FFT not noticed till the publication of Cooley and Tukey's article in 1965 [1]. This article presented an efficient algorithm based on divide

and conquer approach in order to compute the DFT. Divide and conquer approach was applied to the DFT recursively, such that a DFT of any size  $N = N_1 N_2$  computed in terms of smaller DFTs of sizes  $N_1$  and  $N_2$ . If N can be factored into  $N = N_1 N_2$ , the indices n and k in equation (1.1) for N-point DFT can be rewritten as:

$$n = N_2 n_1 + n_2 \begin{cases} 0 \le n_1 \le N_1 - 1 \\ 0 \le n_2 \le N_2 - 1 \end{cases}$$

$$k = N_1 k_2 + k_1 \begin{cases} 0 \le k_1 \le N_1 - 1 \\ 0 \le k_2 \le N_2 - 1 \end{cases}$$

$$(1.11)$$

The index representation of equation (1.11) can be used in equation (1.1) to write X(k) as:

$$X(k) = \sum_{n_2=0}^{N_2-1} \left( \sum_{n_1=0}^{N_1-1} x(N_2 n_1 + n_2) W_{N_1}^{n_1 k_1} \underbrace{W_N^{n_2 k_1}}_{\text{twiddlefactor}} \right) W_{N_2}^{n_2 k_2}$$

$$\underbrace{V_{N_2-\text{point DFT}}^{N_2-\text{point DFT}}}_{N_2-\text{point DFT}} (1.12)$$

where  $0 \le k_1 \le N_1 - 1$  and  $0 \le k_2 \le N_2 - 1$ .

The calculation of X(k) according to equation (1.12) can be carried out in three steps: (i) compute  $N_1$ -point DFT, (ii) multiply by twiddle factors, and (iii) finally compute  $N_2$ -point DFT. The above three-step procedure can be carried out successively till  $N_1 = 2$ . The computational complexity of the DFT by this recursive divide and conquer approach is reduced from  $O(N^2)$  to  $O(N \log_2 N)$  operations [1]. This was the major turning point for real-time DSP applications of the DFT.

#### 1.2.1 Applications of FFT

The fast Fourier transform finds limitless applications in the general areas of signal/image processing. It plays a key role in many applications of digital signal processing, including frequency and phase estimation [8], and to perform operations such as convolutions or multiplying large integers [9, 10]. Accurate frequency and phase estimation are required in many applications such as speech recognition, speech coding, determining the object position in radar systems, biomedicine, multimedia systems etc.

FFT is used in medical imaging for image filtering, image analysis and image reconstruction [11]. In the Fourier representation of images using FFT, spectral magnitude, and phase tend to play different roles. Correlation between phase-only versions [12, 13] of the two images to be aligned is used for image matching. Some of the important applications based on the FFT-based image matching include face recognition, iris recognition, palm print recognition, finger print matching and waveform matching.

FFTs are also extensively used in multi-carrier transmission systems, specifically for applications in Orthogonal Frequency Division Multiplexing (OFDM) systems, such as Digital Broadcasting [14, 15], Worldwide Interoperability for Microwave Access (WiMAX) [16], IEEE 802.11 standards [17], and Long Term Evolution (LTE) [18].

#### 1.3 Motivation

The FFT algorithm reported by Cooley-Tukey in 1965, named as radix-2 algorithm was shortly followed by its extension to higher radices which include, radix-4 [19], radix-8 [20, 21], and radix-16 [22] algorithms. Higher radix algorithms involve significantly less computational complexity in terms of the number of complex multiplications, but the implementation of these algorithms is not simple. Among numerous further developments, the FFT introduced by Duhamel and Hollmann [23] demonstrated a reduction in the number of multiplications at the cost of input and output mapping. The complexity issue has been studied detail in [4], and showed that the split-radix algorithm requires low arithmetic complexity. However, the implementation of split-radix algorithm is difficult, owing to its irregular structure.

Later in 1996, He and Torkelson [24] proposed a radix- $2^2$  algorithm using index decomposition technique. It has exactly the same number of complex multipliers as radix-4 algorithm, but has a butterfly structure similar to that of radix-2 algorithm. This led to, radix- $2^3$  [25], radix- $2^4$  [26], modified radix- $2^4$  [26], radix- $2^5$  [27] and radix- $2^i$  [28] FFT algorithms being proposed by various researchers using the same index decomposition technique, in order to further reduce the number

of multiplications. The main advantages of the generalized radix- $2^i$  [28] algorithm are high throughput and low latency with less area and less power consumption. This makes radix- $2^i$  algorithms more attractive for different applications in communication systems [28].

Twiddle factor multiplication requires both memory and complex multipliers. The implementation of complex multipliers has a large impact on the accuracy, speed, complexity, and power consumption of the design as well. A complex multiplier can be realized by different approaches such as direct implementation of the complex multiplier [29], and algorithms based on constant multiplication [30, 31]. In all these implementations, there is a trade-off between the complexity and the accuracy of the twiddle factor multiplication. In FFT designs the scenario of twiddle factor multiplication is distinct, and impacts the selection of algorithm and architecture. The main aim of this thesis is to select an appropriate FFT algorithm and architecture and to optimize twiddle factor multiplication in the FFT for IEEE 802.11a and IEEE 802.15.4 – a standard OFDM systems.

#### 1.4 Objectives of the Thesis

The FFT used in OFDM system is the most complex and power hungry block. As this system is used mostly in the battery driven wireless applications, low power consumption is desired. This thesis aims at designing ASIC and/or FPGA FFTs for OFDM systems. The main objectives of this thesis are as follows:

- To choose the best FFT algorithm and an appropriate architecture with less hardware complexity suitable for IEEE 802.11a and IEEE 802.15.4 g standard OFDM systems.

- Modify designs at basic processing elements (adder, multiplier and delay buffers)

to achieve enhanced performance.

- Simulate the proposed FFT architectures to verify the correctness of the functionality.

- Synthesize the FFT architectures to obtain ASIC and/or FPGA implementation and compare its performance with recent implementations in the literature.

#### 1.5 Organization of the Thesis

The thesis is organized as follows.

Chapter 2 introduces the advancements of FFT Algorithms and provides their overview from a mathematical perspective. These algorithms include complex-valued FFTs, real-valued FFTs and special cases of FFTs.

Chapter 3 is a survey of architectural techniques for creating hardware efficient and low-power implementations of the FFT. These architectures include memory-based and pipelined architectures. The important design choices and considerations are also discussed and investigated here.

Chapter 4 discusses various possibilities to implement twiddle factor multiplication and its hardware. It includes general complex multiplication and constant multiplication.

Chapter 5 introduces the design consideration of a 64-point FFT for OFDM based IEEE 802.11a standard system. A novel area-efficient and low power 16-bit word-width 64-point radix-2<sup>2</sup> and radix-2<sup>3</sup> pipelined Single-path Delay Feedback (SDF) FFT architectures are presented based on modified complex constant multiplier. The remainder of this chapter describes the implementation details and comparisons with recent implementations in literature.

Chapter 6 presents a novel 16/32/64/128-point pipelined SDF FFT architecture based on mixed-radix algorithm for IEEE 802.15.4-g standard system. Both FPGA and ASIC targeted synthesis results are presented. The comparison of this structure with other published results is provided at the end.

Chapter 7 concludes with a summary of total contributions of this thesis. It also discuss and made suggestions for future research possibilities using the optimized twiddle factor multiplication.

## Chapter 2

# Advancements in FFT Algorithm

#### 2.1 Introduction

The basic principle of divide and conquer approach leads to a variety of efficient algorithms. As these algorithms improves the performance in terms of computation time, these are known as fast algorithms or fast Fourier transform algorithms. In this chapter, we have classified the FFT algorithms as complex valued FFTs (CFFTs), real-valued FFTs (RFFTs) according to the input values and special cases of FFTs. Finally, this chapter concludes with comparison of FFT algorithms that can be helpful to choose the best algorithm for OFDM applications.

#### 2.2 Complex-valued FFT Algorithms

In this subsection, we discuss the popular FFT algorithm followed by some algorithms that can improve the computational speed and reduce the hardware complexity.

#### 2.2.1 Radix-2 FFT algorithms

The basic FFT algorithms are decimation-in-time (DIT) and the decimation-in-frequency (DIF) radix-2 algorithms. These algorithms are applicable to compute the DFT of integer power of 2 lengths.

#### i) Decimation-in-Time Radix-2 FFT Algorithm

This algorithm decomposes the time domain sequence  $\{x(n)\}$  into successively smaller subsequence. Therefore, it is called as decimation-in-time algorithm [32].

The principle of radix-2 DIT FFT algorithm is illustrated in the following by considering  $N=2^M$ , where M=1,2,3,.... Since N is an even integer, the N-point input data can be split into two (N/2)-point sub-sequences  $\{x_1(n)\}$  and  $\{x_2(n)\}$ , which correspond to the even and the odd-indexed samples of the input  $\{x(n)\}$ , respectively,

that is,

$$x_1(n) = x(2n)$$

$x_2(n) = x(2n+1), n = 0, 1, 2, ..., N/2 - 1$  (2.1)

Now the N-point DFT can be derived from two half-length DFTs by the decimation-in-time process as follows:

$$X(k) = \sum_{n=0}^{N-1} x(n)W_N^{nk}$$

$$= \sum_{n=0}^{\frac{N}{2}-1} x(2n)W_N^{2nk} + \sum_{n=0}^{\frac{N}{2}-1} x(2n+1)W_N^{(2n+1)k}$$

$$= \sum_{n=0}^{\frac{N}{2}-1} x(2n)W_{N/2}^{nk}$$

$$+W_N^k \sum_{n=0}^{\frac{N}{2}-1} x(2n+1)W_{N/2}^{nk}$$

(2.2)

Similarly, the (N/2)-point DFTs can be computed from a pair of (N/4)-point DFTs. The decimation process is continued till it contains only two-point DFTs. For a power of two length sequences, decomposition of N-point DFT into 2-point DFTs could be completed in  $M = \log_2 N$  steps of decimation.

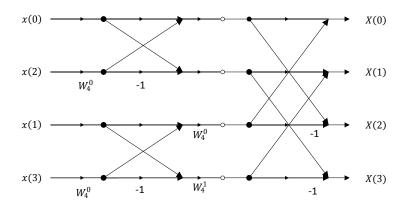

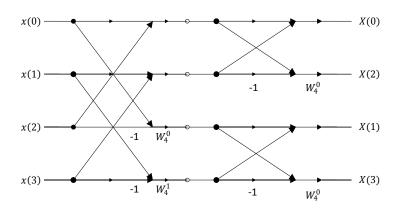

Figure 2.1 shows the decomposition of 4-point radix-2 DIT FFT using the simplified butterflies which involves 2 stages, each with 2 butterflies per stage. The input data to this is in bit-reversed order and the DFT output is in normal order.

Figure 2.1: Length-4, DIT Radix-2 FFT.

#### ii) Decimation-in-Frequency Radix-2 FFT Algorithm

This algorithm is based on computing the DFT by decomposition of the sequence of DFT coefficients X(k)s into smaller subsequences, hence called as decimation-infrequency algorithm [32].

In case of radix-2 DIF FFT, the DFT computation is split into two parts such that the first part involves the first N/2 data points and the second part involves the next N/2 data points, as follows:

$$X(k) = \sum_{n=0}^{\frac{N}{2}-1} x(n)W_N^{nk} + \sum_{n=\frac{N}{2}}^{N-1} x(n)W_N^{nk}$$

(2.3)

Since  $W_N^{nk}=e^{-j2\Pi k/N}$  and  $W_N^{kN/2}=(-1)^k,$  equation (2.3) is simplified as:

$$X(k) = \sum_{n=0}^{\frac{N}{2}-1} \left( x(n) + (-1)^k \cdot x\left(n + \frac{N}{2}\right) \right) \cdot W_N^{nk}$$

(2.4)

Figure 2.2: Length-4, DIF Radix-2 FFT.

The radix-2 DIF algorithm rearranges equation (2.4) into even-indexed and odd-indexed frequency bins as

$$X(2k) = \sum_{n=0}^{\frac{N}{2}-1} \left( x(n) + x\left(n + \frac{N}{2}\right) \right) \cdot W_{N/2}^{nk}$$

(2.5)

$$X(2k+1) = \sum_{n=0}^{\frac{N}{2}-1} \left( \left( x(n) - x\left(n + \frac{N}{2}\right) \cdot W_{N/2}^{nk} \right) \cdot W_{N/2}^{nk} \right)$$

(2.6)

According to equations (2.5) and (2.6), the even-indexed and odd-indexed frequency outputs X(k) can be computed by a pair of N/2-length DFTs. The entire process involves  $M = \log_2 N$  stages of decimation, where each stage involves N/2 butterflies. Figure 2.2 shows the flow graph of radix-2 DIF decomposition of a 4-point DFT computation. In this flow graph the input is in normal order and the DFT output is in bit-reversed order. To compute the 4-point DFT, it requires 4 complex multiplications and 8 complex additions.

The computation of N-point DFT via the DIF or DIT FFT algorithms require  $(N/2) \log_2 N$  and  $N \log_2 N$  number of complex multiplications and complex additions, respectively. For a radix-2 algorithm the operation count can be further reduced by realizing each complex multiplication by 3 real multiplications and 3 real additions (a 3/3 algorithm) [33]. When 3/3 algorithm is used for complex multiplications the arithmetic complexity of radix-2 FFT could be given by:

$$R_M = \frac{3N}{2}\log_2 N - 5N + 8\tag{2.7}$$

$$R_A = \frac{7N}{2}\log_2 N - 5N + 8 \tag{2.8}$$

where  $R_M$  and  $R_A$  are the real multiplications and real additions to compute an Npoint DFT, respectively.

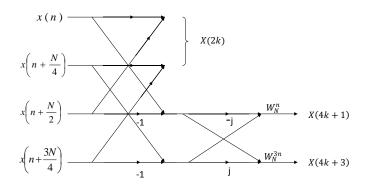

# 2.2.2 Radix-4 FFT algorithm

It can be used when the DFT length N is a power of 4 (i.e.,  $N=4^{M}$ ). Unlike the radix-2 FFT algorithm in the radix-4 algorithm during every step, decimation is carried out by a factor of 4 [19].

In the first step of radix-4 DIT FFT, the input N-point data is split into four subsequences as x(4n), x(4n+1), x(4n+2), and x(4n+3), where n = 0, 1, ..., N/4-1.

Figure 2.3: Radix-4 FFT butterfly.

Then

$$X(k) = \sum_{n=0}^{N-1} x(n)W_N^{nk}$$

$$= \sum_{n=0}^{\frac{N}{4}-1} x(4n)W_{N/4}^{nk} + W_N^k \sum_{n=0}^{\frac{N}{4}-1} x(4n+1)W_{N/4}^{nk}$$

$$+W_N^{2k} \sum_{n=0}^{\frac{N}{4}-1} x(4n+2)W_{N/4}^{nk}$$

$$+W_N^{3k} \sum_{n=0}^{\frac{N}{4}-1} x(4n+3)W_{N/4}^{nk}$$

$$(2.9)$$

As the FFT length of a radix-4 is  $N=4^M$ , it requires  $M=\log_4 N=\frac{\log_2 N}{2}$  stages of decimation where each stage involves N/4 butterflies. The radix-4 FFT butterfly structure is shown in Figure 2.3. The decimation process of each stage is similar to radix-2 algorithm. Since  $W_N^0=1$ , each radix-4 butterfly involves 3 complex multiplications and 8 complex additions [34]. Therefore, the number of complex multiplications

is  $\frac{3N}{4}\log_4 N$ . Comparing with the radix-2 approach, this requires less number of complex multiplications, although it uses the same number of complex additions. The total operation count for N-point radix-4 FFT is [4]:

$$R_M = \frac{9N}{8}\log_2 N - \frac{43N}{12} + \frac{16}{3} \tag{2.10}$$

$$R_A = \frac{25N}{8}\log_2 N - \frac{43N}{12} + \frac{16}{3} \tag{2.11}$$

# 2.2.3 Radix- $2^i$ and Higher radix FFT Algorithms

The twiddle factor multiplicative complexity can be reduced by using higher radices like radix-8 [20] or radix-16 [22]. But, the implementation complexity grows as the radix becomes higher. In 1996, He and Torkelson [24] discussed about radix- $2^2$  and radix- $2^3$  FFT algorithms. These algorithms have the same number of non-trivial multiplications as radix-4 and radix-8 algorithms, respectively. However, these algorithms differ in the twiddle factors at different FFT stages, but maintain the same butterfly structure of radix-2 algorithm. Followed by He and Torkelson [24], several radix- $2^i$  [28] algorithms are developed for higher radices that include radix- $2^4$  [26], modified radix- $2^4$  [26], radix- $2^5$  [27], and modified radix- $2^5$  [27] algorithms. The idea of these radix- $2^i$  algorithms is to get simpler butterfly structure with less multiplicative complexity. The following subsection explains the derivation of the radix- $2^2$  algorithm,

<sup>&</sup>lt;sup>1</sup>Twiddle factor multiplication by 1, -1, j and -j are trivial and other multiplications like  $W_8^1, W_{16}^1$  are non-trivial.

which can be extended for higher radices.

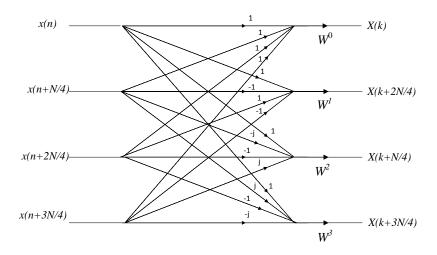

# i) Radix-2<sup>2</sup> Algorithm

In [24], the authors have proposed a radix- $2^2$  algorithm using index decomposition technique. To illustrate the derivation of this algorithm, the time and frequency indices for i = 2 are decomposed as follows:

$$n = \frac{N}{2}n_1 + \frac{N}{4}n_2 + n_3 \left\{ n_1, n_2 = 0, 1, n_3 = 0 \sim \frac{N}{4} - 1 \right\}$$

$$k = k_1 + 2k_2 + 4k_3 \left\{ k_1, k_2 = 0, 1, k_3 = 0 \sim \frac{N}{4} - 1 \right\}$$

(2.12)

Substituting equation (2.12) in (1.1) we can get the following expression:

$$X(k_{1} + 2k_{2} + 4k_{3})$$

$$= \sum_{n_{3}=0}^{\frac{N}{4}-1} \sum_{n_{2}=0}^{1} \sum_{n_{1}=0}^{1} x(\frac{N}{2}n_{1} + \frac{N}{4}n_{2} + n_{3})$$

$$W_{N}^{(\frac{N}{2}n_{1} + \frac{N}{4}n_{2} + n_{3})(k_{1} + 2k_{2} + 4k_{3})}$$

$$= \sum_{n_{3}=0}^{\frac{N}{4}-1} \sum_{n_{2}=0}^{1} \{B_{N/2}^{k_{1}}(\frac{N}{4}n_{2} + n_{3})\}$$

$$W_{N}^{(\frac{N}{4}n_{2} + n_{3})(k_{1} + 2k_{2} + 4k_{3})}$$

$$(2.13)$$

where

$$B_{N/2}^{k_1}(\frac{N}{4}n_2 + n_3) = x(\frac{N}{4}n_2 + n_3) + (-1)^{k_1}x(\frac{N}{4}n_2 + n_3 + \frac{N}{2})$$

(2.14)

The decomposition of common twiddle factor in equation (2.13) is the key difference from the decomposition of the radix-2 algorithm, which can be expressed as

$$W_N^{(\frac{N}{4}n_2+n_3)(k_1+2k_2+4k_3)} = (-j)^{n_2(k_1+2k_2)} W_N^{n_3(k_1+2k_2)} W_N^{n_3k_3}$$

(2.15)

Substituting equation (2.15) in (2.13) the components of N-point DFT could be obtained from four DFTs of length N/4 as follows:

$$X(k_1 + 2k_2 + 4k_3) = \sum_{n_3=0}^{\frac{N}{4}-1} \{B_{N/4}^{k_1 k_2}(n_3) W_N^{n_3(k_1+2k_2)}\} W_{\frac{N}{4}}^{n_3 k_3}$$

(2.16)

where

$$B_{N/4}^{k_1 k_2}(n_3) = B_{N/2}^{k_1}(n_3) + (-1)^{k_2}(-j)^{k_1} B_{N/2}^{k_1}(n_3 + \frac{N}{4})$$

(2.17)

An N-point DFT is now decomposed into four DFTs of length-(N/4) DFTs, according to (2.16). Each DFT of length N/4 can be further decomposed in the same way until length-2 or length-4 DFTs are reached.

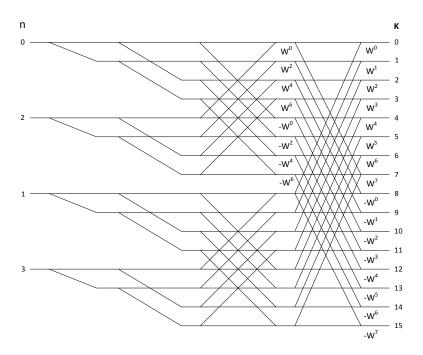

Figure 2.4: Signal flow graph of 16-point radix-2<sup>2</sup> DIF FFT.

Figure 2.4 shows a flow graph of 16-point radix- $2^2$  DIF FFT. It requires the trivial multiplication by  $W_{16}^4 = -j$  in the first and the third stages, whereas it requires non-trivial multiplications in the second stage. This flow graph is different from that of radix-2 algorithm in which non-trivial twiddle factors are needed at the outputs of every stage (except the last one). This algorithm has a great structural advantage compared to other algorithms (radix-2 and radix-4) when they are implemented in pipeline architectures [26].

#### ii) Higher Radix Algorithms

The linear index decomposition scheme of radix- $2^2$  algorithm can be extended for higher radices, e.g, radix- $2^3$ , radix- $2^4$ , modified radix- $2^4$  (Radix- $M.2^4$ ), radix- $2^5$  and modified radix- $2^5$  (Radix- $M.2^5$ ). The N-point FFT computation with radix- $2^i$  algorithm involves  $\log_2 N$  stages. Table 2.1 shows the twiddle factor at each stage to compute the N-point FFT for various radix- $2^i$  algorithms (Number of stages are shown upto 8 in Table 2.1, which can extend to  $\log_2 N$  stages). These algorithms have the same butterfly structure but the twiddle factor multiplication structure is varied with the exponent i. The twiddle factor multiplications are classified into trivial ( $W_4$  which is multiplication by -j), and other multiplications are non-trivial[28].

From Table 2.1, one can observe that radix- $2^3$  [24] algorithm requires trivial multiplication at first stage, and non-trivial multiplications at the second and third stages. This type of sequence is repeated for every three stages in order to obtain radix- $2^3$  algorithm. Radix- $2^4$  includes trivial multiplication at first stage, and non-trivial multiplications in the next three stages. In [26], a modified radix- $2^4$  algorithm have been proposed, which requires less number of multiplications. In the modified algorithm of [26], the twiddle factor of third stage  $W_{16}$  is transferred to the second stage. A modified radix- $2^5$  algorithm is suggested in [27], which is a combination of two decomposition methods of radix- $2^5$  algorithm. In [28], the authors have presented the decomposition

| Stage<br>Algorithm | 1     | 2        | 3        | 4         | 5     | 6          | 7        | 8          |

|--------------------|-------|----------|----------|-----------|-------|------------|----------|------------|

| $Radix-2^2$        | $W_4$ | $W_N$    | $W_4$    | $W_{N/4}$ | $W_4$ | $W_{N/16}$ | $W_4$    | $W_{N/64}$ |

| $Radix-2^3$        | $W_4$ | $W_8$    | $W_N$    | $W_4$     | $W_8$ | $W_{N/8}$  | $W_4$    | $W_8$      |

| $Radix-2^4$        | $W_4$ | $W_8$    | $W_{16}$ | $W_N$     | $W_4$ | $W_8$      | $W_{16}$ | $W_{N/16}$ |

| $Radix-M.2^4$      | $W_4$ | $W_{16}$ | $W_4$    | $W_N$     | $W_4$ | $W_{16}$   | $W_4$    | $W_{N/16}$ |

| $Radix-2^5$        | $W_4$ | $W_8$    | $W_{16}$ | $W_{32}$  | $W_N$ | $W_4$      | $W_8$    | $W_{16}$   |

| $Radix-M.2^5$      | $W_4$ | $W_8$    | $W_{32}$ | $W_4$     | $W_N$ | $W_4$      | $W_{16}$ | $W_4$      |

**Table 2.1:** Twiddle factor at each stage to compute N-point FFT

of radix- $2^i$  algorithm which further reduces the number of multiplications. The radix- $2^i$  algorithms have the advantages of lower multiplicative complexity and structural advantage to be used in pipeline architecture.

# 2.2.4 Split-Radix FFT

The split-radix FFT (SRFFT) algorithm was introduced in [35], but this was clearly described in [23]. The split-radix algorithm decomposes an N-point DFT into one N/2-point DFT and two N/4-point DFTs as:

$$X(k) = \sum_{n=0}^{N-1} x(n)W_N^{nk}$$

$$= \sum_{n=0}^{\frac{N}{2}-1} x(2n)W_{N/2}^{nk} + W_N^k \sum_{n=0}^{\frac{N}{4}-1} x(4n+1)W_{N/4}^{nk}$$

$$+W_N^{3k} \sum_{n=0}^{\frac{N}{4}-1} x(4n+3)W_{N/4}^{nk}$$

(2.18)

Figure 2.5: Split-Radix FFT.

This algorithm makes use of both radix-2 and radix-4 (radix-2/4) behaviour simultaneously on upper and lower half of the signal flow graph as shown in Figure 2.5.

The arithmetic complexity of SRFFT algorithm is given by [23]:

$$R_M = N\log_2 N - 3N + 4 \tag{2.19}$$

$$R_A = 3N\log_2 N - 3N + 4 \tag{2.20}$$

The SRFFT algorithm [23] requires less number of multiplications and additions compared to radix-2 and radix-4 algorithms. Followed by the SRFFT algorithm of [23], many split-radix algorithms [36, 37, 38, 39] were suggested by researchers to further reduce the number of complex multiplications and additions over the radix-2, radix-4 or any higher radix-based algorithms.

**Table 2.2:** Number of real multiplications to compute a length-N Complex DFT

| N    | Radix-2 | Radix- $4/$<br>Radix- $2^2$ | Split Radix |

|------|---------|-----------------------------|-------------|

| 16   | 24      | 20                          | 20          |

| 32   | 88      | -                           | 68          |

| 64   | 264     | 208                         | 196         |

| 128  | 712     | -                           | 516         |

| 256  | 1800    | 1392                        | 1284        |

| 512  | 4360    | -                           | 3076        |

| 1024 | 10248   | 7856                        | 7172        |

**Table 2.3:** Number of real additions to compute a length-N Complex DFT

| N    | Radix-2 | Radix- $4/$<br>Radix- $2^2$ | Split-Radix |

|------|---------|-----------------------------|-------------|

| 16   | 152     | 148                         | 148         |

| 32   | 408     | -                           | 388         |

| 64   | 1032    | 976                         | 964         |

| 128  | 2504    | -                           | 2308        |

| 256  | 5896    | 5488                        | 5380        |

| 512  | 13566   | -                           | 12292       |

| 1024 | 30728   | 28336                       | 27652       |

# 2.2.5 Computational Complexity for Complex-Valued FFT Algorithms

Table 2.2 and Table 2.3 shows the comparison of the number of real multiplications and real additions to compute an N-point DFT. From these tables one can observe that, the split-radix FFT requires less number of arithmetic operations compared to

the other algorithms. However, the flow graph of this algorithm results in an irregular structure due to the mix of FFTs of different lengths in different parts.

# 2.3 Real-valued FFT Algorithms

When the input sequence x(n) is real-valued, the DFT components exhibit conjugate symmetry behavior, i.e.,  $X(k) = X^*(N - k)$ . Therefore, we need to compute only half the number of DFT components in this case. But the FFT algorithms for the computation of complex-valued input cannot be used directly to reduce the computational complexity to half, when we want to compute the DFT of real-valued input. FFT of real-valued data and FFT of complex-valued data are generally referred to as real-valued FFT (RFFT) and complex-valued FFT (CFFT), respectively.

Moreover, efficient realization of RFFT has received great attention due to its several important and emerging applications in the area of bio-medical engineering and health-care, audio and video processing, time-series analysis, and many others [40]. Several algorithms are therefore proposed for the RFFT computation. Real-valued FFTs [20] provide area and speed improvement over the CFFTs. The RFFT algorithms are generally tailored for real-valued data by using the trigonometric symmetries and periodicities [20]. In the following sub-section, initially we discuss different approaches for the computation of FFT of real-valued data.

#### 2.3.1 Computation of the RFFT using the CFFT

The simplest way of using the CFFT algorithm to compute the RFFT is to set the real-valued sequence into the real part of complex-valued input and to set the imaginary part of the input values to zero [3]. This approach does not provide significant saving of computation over the CFFT since the intermediate results become complex-valued just after the first stage, when the complex twiddle factors are multiplied. Therefore, doubling algorithm and packing algorithm are proposed to compute the RFFT [3].

#### i) Doubling Algorithm

In this algorithm a pair of real-valued input sequence is used at a time [27]. The first real-valued data sequence is used as the real part and the second real data sequence as the imaginary part of the complex-valued input sequence of the CFFT. The complex input values thus obtained is expressed as:

$$x(n) = p(n) + j.q(n)$$

(2.21)

where p(n) and q(n) are elements of two real-valued data sequences. An N-point CFFT of complex input  $\{x(n)\}$  is then obtained as:

$$X(K) = P(K) + j \cdot Q(K)$$

(2.22)

Since p(n) and q(n) are real-valued data, the following symmetry holds

$$P^*(N-k) = P(K)$$

$$Q^*(N-k) = Q(K)$$

(2.23)

hence follows the output sequence as:

$$X^*(N-k) = P(K) - j.Q(K)$$

(2.24)

By using equations (2.22) and (2.24), P(k) and Q(k) can be obtained as:

$$P(k) = \frac{1}{2} (X(k) + X^*(N - k))$$

$$Q(k) = \frac{j}{2} (X^*(N - k) - X(k))$$

(2.25)

In order to separate P(k) and Q(k) according to equation (2.25), 2(N-1) extra additions over the normal complex FFT are required. Using the 3/3 algorithm for complex multiplication, the RFFT requires  $\frac{1}{2}MN - \frac{3}{2}N + 2$  multiplications and  $\frac{3}{2}MN - \frac{1}{2}N$  additions [41]. This algorithm requires almost half of the arithmetic complexity of the CFFT algorithm.

#### ii) Packing Algorithm

This is another approach to compute N-point FFT of real-valued input using N/2point CFFT [41]. It uses the odd and even indexed samples of the N-point realvalued input sequence to form the (N/2)-point complex data. This is called packing

algorithm, since it packs the N-point real-valued sequence into (N/2)-point complex

valued sequence. The real-valued data can be represented in the form of a complex

data as:

$$x(n) = x(2n) + j.x(2n+1)$$

(2.26)

where n = 0, 1, 2, ...., N - 1.

Let p(n) = x(2n) and q(n) = x(2n + 1), then the DFT output X(K) can be obtained by using CFFT as in doubling algorithm. Therefore, this also requires 2(N-1) extra additions to separate the outputs of the CFFT as in the case of doubling algorithm. Moreover, it requires an additional stage to compute the outputs of the RFFT. The corresponding RFFT requires  $\frac{1}{2}MN - \frac{5}{4}N$  multiplications and  $\frac{3}{2}MN - \frac{1}{4}N - 4$  additions by using 3/3 algorithm for complex multiplications [41].

#### 2.3.2 FFT of Real-Valued data

The reduction in the arithmetic complexity can be obtained by using specific algorithms such as DIT FFT algorithm for the computation of the RFFT. This can be achieved by applying the conjugate symmetric property, and computing only one half of the intermediate outputs in each stage, since the others can be obtained by conjugating those intermediate values. This results with less arithmetic complexity for the radix-2 DIT FFT algorithm [40]. By assuming a 3/3 algorithm, radix-2 DIT FFT for a real-valued sequence require  $\frac{3}{4}MN - \frac{5}{2}N + 4$  multiplications and  $\frac{7}{4}MN - \frac{7}{2}N + 6$  additions.

The radix-4 and higher radix algorithms [42] for real valued inputs can be obtained in the way similar to that of the radix-2 DIT FFT. As the split-radix algorithm is more efficient in terms of arithmetic complexity than higher radix algorithms. It requires only  $\frac{1}{2}MN - \frac{3}{2}N + 2$  multiplications and  $\frac{3}{2}MN - \frac{5}{2}N + 4$  additions [40]. However, these algorithms are not valid for the DIF decomposition of the FFT because it is not possible to apply the conjugate symmetry at each stage. In [43], an alternative algorithm is proposed to obtain the same savings for the DIF decomposition. In [44], the authors have proposed a modified radix-2 algorithm for the computation of the RFFT which solves the irregularities of the RFFT. This approach is valid for both DIT and DIF decompositions and could be generalized for any number of points, which is power of 2. In [45], the computation of RFFT was based on a modified

radix-2 algorithm which removes the redundant operations from the flow graph. This modified flow graph contains only real data paths instead of complex data paths in a regular flow graph. In [46], a mathematical formulation was presented for removing the redundancies in the radix-2 DIT RFFT. This formulation regularizes the flow graph in order to compute folded RFFT with a simple control unit.

#### 2.3.3 Fast Hartley Transform

The DFT of real-valued data could be computed from the Discrete Hartley Transform (DHT) [47] of the same data. The DHT of a real valued input sequence is defined as:

$$X(k) = \sum_{n=0}^{N-1} x(n) \left[ \cos \left( \frac{2\pi kn}{N} \right) + \sin \left( \frac{2\pi kn}{N} \right) \right]$$

(2.27)

for  $k = 0, 1, 2 \dots N - 1$ .

Unlike the DFT, the DHT takes real-valued input and provides real-valued output. The absence of complex arithmetic makes the DHT faster than the DFT. Algorithms similar to the radix-based FFT can also be applied to DHT computations called as Fast Hartley Transform (FHT) algorithm. Generally, FHT algorithms involve the same multiplications and (N-2) more addition compared to the corresponding FFT

Figure 2.6: Quick Discrete Fourier Transform

algorithm. The split-radix FHT algorithm requires  $\frac{2N}{3}\log_2 N - \frac{19N}{9} + 3 + \frac{(-1)^M}{9}$  multiplications and  $\frac{4N}{3}\log_2 N - \frac{14N}{9} + 3 + (-1)^M \frac{5}{9}$  additions.

An N-point DFT of real-valued data can be computed from the DHT of the same data as follows:

$$Re(DFT(k)) = \frac{DHT(k) + DHT(N - k)}{2}$$

$$Im(DFT(k)) = \frac{DHT(k) - DHT(N - k)}{2}$$

(2.28)

**Table 2.4:** Number of real multiplications to compute the DFT for a real-valued input

| varued input |        |         |          |         |             |      |       |

|--------------|--------|---------|----------|---------|-------------|------|-------|

| N            | CFFT   | CFFT    | CFFT     | Radix-2 | Split-radix | FHT  | Quick |

|              | Direct | Packing | Doubling | RFFT    | RFFT        | 1111 | DFT   |

| 16           | 20     | 12      | 10       | 12      | 10          | 12   | 11    |

| 32           | 68     | 40      | 34       | 44      | 34          | 42   | 37    |

| 64           | 196    | 112     | 98       | 132     | 98          | 124  | 105   |

| 128          | 516    | 288     | 258      | 356     | 258         | 330  | 273   |

| 256          | 1284   | 704     | 642      | 900     | 642         | 828  | 673   |

| 512          | 3076   | 1664    | 1538     | 2180    | 1538        | 1994 | 1601  |

| 1024         | 7172   | 3840    | 3586     | 5124    | 3586        | 4668 | 3713  |

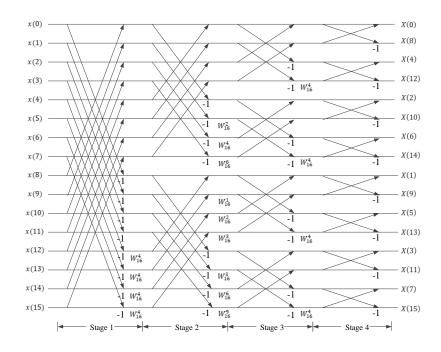

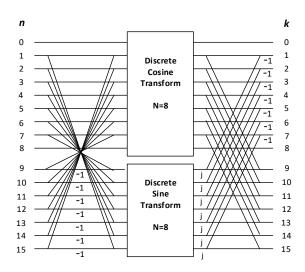

# 2.3.4 Quick Discrete Fourier Transform

This algorithm computes the DFT via Discrete Cosine Transform (DCT) and Discrete Sine Transform (DST). It decomposes the N-point DFT into (N/2 + 1)-point DCT and (N/2 - 1)-point DST. The Quick DFT for 16-point data is shown in Figure 2.6. This computes the DCT and the DST seperately by taking the complex operations at the last stage. The arithmetic operations required by this algorithm to compute the N-point DFT are as follows:

$$R_M = \frac{N}{2}\log_2 N - \frac{11}{8}N + 1 \tag{2.29}$$

$$R_A = \frac{7}{4}N\log_2 N - 3N + 2\tag{2.30}$$

.

**Table 2.5:** Number of real additions to compute the DFT for a real-valued input

| N CFFT | CFFT      | CFFT  | Radix-2  | Split-radix | FHT   | Quick |       |

|--------|-----------|-------|----------|-------------|-------|-------|-------|

| 1 4    | Direct Pa |       | Doubling | RFFT        | RFFT  | 1111  | DFT   |

| 16     | 148       | 88    | 88       | 62          | 60    | 64    | 66    |

| 32     | 388       | 228   | 224      | 170         | 164   | 166   | 186   |

| 64     | 964       | 556   | 544      | 442         | 420   | 416   | 482   |

| 128    | 2308      | 1308  | 1280     | 1082        | 1028  | 998   | 1186  |

| 256    | 5308      | 3004  | 2944     | 2586        | 2436  | 2336  | 2818  |

| 512    | 12292     | 6780  | 6656     | 5978        | 5636  | 5350  | 6530  |

| 1024   | 27652     | 15100 | 14848    | 13658       | 12804 | 12064 | 14580 |

# 2.3.5 Computational Complexity for Real-Valued FFT Algorithms

Although most of the FFT algorithms are developed for complex-valued inputs, by taking the advantages of redundancies and trigonometric symmetries, the computational complexity is reduced in all of these RFFT algorithm. The number of real multiplications and real additions required for the operation of real-valued are shown in Table 2.3 and Table 2.4, respectively. If a CFFT is used directly for real inputs, it requires more arithmetic complexity. The packing and oubling algorithms involve more additions than a Split-radix RFFT algorithm [40] for a real-valued input.

Split-radix FHT requires less number of multiplications and additions than radix-2 RFFT for N greater than 16. However, it requires more number of multiplications and additions than split-radix RFFT. The Quick DFT algorithm requires more real multiplications than the doubling algorithm.

# 2.4 Special cases of the FFT algorithms

The FFT algorithm could be optimized for some special cases, e.g., when only a part of the output is desired or when there are a large number of zeros in the input or when the input is non-power of two or multidimensional inputs. In this subsection, we discuss some special cases of FFT algorithms that are useful for specific applications like, Third Generation Partnership Project (3GPP) Long-Term Evolution (LTE) [18], and modern microscopy [48], and radar signal processing.

# 2.4.1 FFT Pruning

If the data sequence contains  $2^l$  non-zero data points out of  $2^m$  data points, where m > l, then the corresponding FFT can be computed by means of the pruned FFT which accomplishes time saving. A slight modification to radix-2 DIT algorithm allows a time-saving of approximately (m-l)/m where  $2^m$  points are transformed of which only  $2^l$  are non-zero [49].

The FFT pruning for l = 2, m = 3 is shown in Figure 2.7. There are four non-zero data points and three stages. Pruning is applied to first stage, but second and third stages cannot be pruned [49]. When pruning is applicable, we compute only the partial butterflies instead of entire butterflies. In general, if there are  $2^l$  non-zero data points in a set of  $2^m$  data points, then the number of stage(s) where pruning can be applied

Figure 2.7: FFT pruning.

(m-l) stages. FFT pruning is used when there are a large number of zero's that are known in the input. However, it only allows l to be a power-of-two. The asymptotic run-time of the pruned FFT is  $O(N.\log a)$ , where N is the FFT length and a is the number of non-zero inputs. The main drawback of pruning is that the data sequence is to be known in advance, so that one can find the non-zero input values.

# 2.4.2 Fast Fourier Transform of Sparse Input

The computation time of DFT generally corresponds to its size N. However, in most of the applications like spectrum sensing and radar signal processing, only a few selected output of the FFT is used. An algorithm to compute those coefficients of its Fourier

transform is called Sparse FFT (SFFT) [50], whose runtime is sublinear in the signal size N.

In [51], the first sublinear algorithm was presented, which is followed by several other sublinear algorithms [52, 53, 54] were developed for Fourier transform over the complex input. There are several versions of SFFT algorithms described in [50]. A hardware implementation of SFFT algorithm is recently published in [55]. However, it is implemented for a specific signal size. Therefore, in [56], the authors have presented the hardware implementation of a million-point SFFT design, that can provide configurable parameters. Robust Sparse Fourier Transform (RSFT), which is a modification of Sparse Fourier Transform (SFT) is presented in [57] that extends the SFT advantages which are useful for short-range radar signal processing. It is shown that the RSFT is robust in detecting frequencies when exact knowledge of signal sparsity is not available. It has further investigated the trade-off between detection performance and computational complexity [57].

#### 2.4.3 Scaled DFTs

In certain applications like orthogonal frequency division multiplexing demodulation and modern microscopy [58], the input length of DFT is length- $q*2^M$ , where q is a odd number. However, fast algorithms for such sequence lengths generally require complex computational structure and are less efficient than that of power-of-two length DFTs.

Zero-padding technique was often used to get the DFT of such sequence lengths. However, this technique requires more computations. Therefore, a scaled DFT has been proposed in [58], which can be flexibly used for length- $q * 2^M$  DFTs. Several algorithms [39, 58, 59, 60] have been proposed thereafter, in order to further reduce the arithmetic complexity for scaled DFT computation.

#### 2.4.4 Multidimensional FFTs

The multidimensional fast Fourier transforms (FFTs in 2D or more dimensions) are used in many applications such as image processing, applied physics etc. These applications require large amount of computations.

The general form of the multidimensional FFT is as follows:

$$X(u_1, u_2, \dots, u_m) = \sum_{v_1=0}^{N_1-1} \sum_{v_2=0}^{N_2-1} \dots \sum_{v_m=0}^{N_m-1} W_{N_1}^{u_1 v_1} W_{N_2}^{u_2 v_2} \dots W_{N_m}^{u_m v_m} x(v_1, v_2, \dots, v_m)$$

$$(2.31)$$

where  $W_{N_k} = exp(\frac{-2\pi j}{N_k})$ ,  $u_k = 0, 1, ...., u_k - 1$ ;  $u_k$  is the length of the  $k^{th}$  dimension k = 1, 2, ...., m and  $x(v_1, v_2, ...., v_m)$  are the complex input data sequences.

Equation (2.31) is converted into m one-dimensional FFTs in order to simplify the computation as follows:

$$X(u_1, u_2, \dots, u_m) = \sum_{v_1=0}^{N_1-1} W_{N_1}^{u_1 v_1} \sum_{v_2=0}^{N_2-1} W_{N_2}^{u_2 v_2} \dots \sum_{v_m=0}^{N_m-1} W_{N_m}^{u_m v_m} x(v_1, v_2, \dots, v_m)$$

(2.32)

This provides the simplest algorithm where each one-dimensional FFT can be computed by the Cooley-Tukey FFT [1], so this algorithm is known as row-column algorithm [61].

Several algorithms have been proposed for the multidimensional FFTs such as the vector-radix algorithms, the polynomial transform algorithms and the split vector-radix algorithms [62, 63, 64]. These algorithms reduces the complexity over row-column algorithm. In [65], a fast algorithm has been derived based on vector coding for multidimensional integral points. This algorithm has reduced the multiplication complexity and the number of recursive stages without increasing the number of additions. However, the most popular one among these algorithms is the row-column decomposition algorithm, due to its simple structure and easy to program.

# 2.4.5 Quantum Fourier Transform

The Moore's law [66] has been consistent for several decades, but sustaining the pace of scaling has become increasingly difficult in recent years. To meet the performance and power requirements of exa-scale systems, quantum computers may be one of the alternatives which possibly could offer exponential speedup for certain types of calculations.

The Quantum Fourier Transform (QFT) is used in Quantum computers, which is similar to FFT [67]. But the QFT operates on quantum bits instead of operating on vector elements. If  $2^p$  elements are considered for both transforms, these can take  $p2^p$  operations and p(p+1)/2 operations to compute FFT and QFT, respectively. By comparing the quantity of operations, it is evidenced that the QFT is efficient than the FFT. Nowadays, significant attention is given for research to implement the QFT algorithms [68, 69, 70].

Basic quantum computers are developed in many labs across the world. Companies such as Microsoft, IBM and Google are all developed their own prototypes [71]. However, these prototypes are very simple with only a small number of qubits. The Quantum hardware emulation is also critical in developing practical QFT algorithms before large-scale quantum computer becomes viable. Therefore, a comprehensive methodology to perform accurate mapping of quantum algorithm for FPGA emulation purposes have been demonstrated through the emulation of QFT hardware in [68, 69, 70, 72].

#### 2.5 Conclusion

This chapter briefly reviewed three classes of FFT algorithms that comprises of complex valued FFTs, real-valued FFTs and special cases of FFTs. In complex valued FFTs, the radix-2 DIT and DIF algorithms have simple structure that makes easy to implement and is suitable for generic FFT implementation. However, these algorithms require large memory to store data at inner stages, which increases the hardware complexity for implementation. The radix-4 or higher radix algorithms require less multiplications than radix-2 algorithm. However, this algorithm is suitable only when N is a power of 4. This chapter also discussed radix-2<sup>2</sup> and higher-radix algorithms using index decomposition technique. The radix -2<sup>2</sup> algorithm has the same multiplicative complexity as radix-4 algorithm, but retains the butterfly structure of radix-2 algorithm, which is very suitable for ASIC implementation. As compared to radix-based algorithms, the split-radix FFT algorithm require less number of multiplications and additions. However, the FFT implementation is difficult due to its irregular structure.

In real-valued FFTs, the RFFT computations can be obtained by using the CFFT (doubling algorithm and packing algorithm) based on complex conjugate symmetry. In the direct use of CFFT for RFFT computation, the complexity increases as the imaginary part of CFFT is considered by making it as zero. In the other CFFT based techniques (doubling algorithm and packing algorithm), the arithmetic complexity is much less than the direct computation of CFFT. This chapter also discussed specific

algorithms for the computation of RFFT based on radix-2 and split-radix algorithm.

Among these split-radix requires fewer operations than a radix-2 or even for higher radix algorithms.

Further we have discussed the special cases of the FFT algorithms based on some constraints. FFT pruning is considered when the data sequence contain large number of zeros. However, the data sequence has to be known in advance. By using sparse FFT, where fewer than N inputs are required and the data sequence does not known in advance. Scaled DFTs are preferred only for length- $q*2^M$  DFTs. Multidimensional FFTs are required for 2-D or higher dimensional FFTs. A brief description about Quantum Fourier Transform is also discussed which are going to be implement in future. These are the special cases of FFT algorithm that further reduces the hardware complexity of the algorithm. However, these algorithms are considered only for specific applications.

Nowadays, based on literature research, either radix- $2^i$  or combination of radix- $2^i$  algorithms are most suitable for FFT implementation of OFDM system. This thesis is constrained to design FFT for OFDM system. So, more detailed analysis is discussed in the next chapter 3 combined with architecture choice.

# Chapter 3

# FFT Architectures and Design choice for OFDM systems

The key to high performance in FFT hardware is to have the computational elements organized in such a way that they match the structure of the computational algorithm. In chapter 2, FFT algorithms were discussed particularly about the optimization of the number of operations. In real implementations, often the number of operations is not as important as the amount of resources required and the utilization of those.

The FFT architecture generally consists of one or more processing elements (PEs) that includes butterflies and twiddle factor multipliers with memory and data management circuits. Each butterfly comprises of adder and subtractor, which is usually

reused to compute several butterflies of the FFT algorithm. Similarly, complex twiddle factor multipliers can be reused to perform several twiddle factor multiplications.

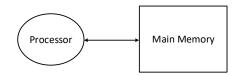

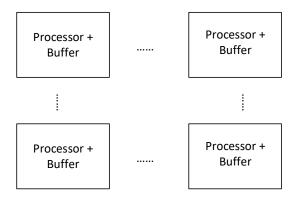

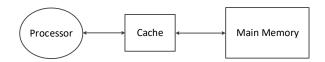

This reuse of the processing element reduces the area of circuit.