# Framework for Translation of C/C++ Applications on Reconfigurable Computing Systems

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY**

by

# **ASHISH MISHRA**

**ID No. 2009PHXF038P**

Under the Supervision of

Dr. Kota Solomon Raju

Dr. Abhijit Rameshwar Asati

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

PILANI - 333031 (RAJASTHAN) INDIA

2016

# Framework for Translation of C/C++ Applications on Reconfigurable Computing Systems

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY**

by

# **ASHISH MISHRA**

**ID No. 2009PHXF038P**

Under the Supervision of

Dr. Kota Solomon Raju

Dr. Abhijit Rameshwar Asati

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

PILANI - 333031 (RAJASTHAN) INDIA

2016

#### **ACKNOWLEDGMENTS**

First and foremost, I would like to thank my supervisor, Dr. Kota Solomon Raju, for giving me a valuable problem definition and laying the basic foundation for my research work. He has inspired me throughout these years and pooled in valuable ideas whenever I was struck. His immense knowledge, insights and indispensible suggestions always inspired me to reach a new level. Without his support and guidance, my thesis work would not have been possible. I am very grateful for his guidance and for being a phenomenal advisor.

Secondly, I would like to express my gratitude to my co-supervisor Dr. Abhijit R. Asati for his valuable discussions in the domain of EDA VLSI design algorithms. His patience to understand the problem crux makes him special. His continued support and mentoring led me to restructure my writing and presentation ability.

I take this opportunity to thank Prof. Souvik Bhattacharyya, Vice-Chancellor BITS, Pilani and Prof A. K. Sarkar, Director, BITS, Pilani (Pilani Campus) for providing me the necessary infrastructure, facilities and constant inspiration. I also acknowledge the kind support from R. N. Saha (Director, Dubai campus), Prof. G. Sundar (Director, Hyderabad Campus), Prof. G. Raghurama (Director, Goa Campus), and Prof. S. K. Verma Dean (Academic Research and Development). I would also like to extend my sincere thanks to my doctoral advisory committee (DAC) members, Prof. S. Gurunarayanan and Prof. Sudeept Mohan for carefully going through my thesis drafts and helping me learn the various skills of academic research. I also thank DRC convener Dr. Abhijeet Asati and other DRC committee members for their time and insightful comments. I am also thankful to Dr. Navneet Gupta (HOD, Department of Electrical and Electronics Engineering), Prof. V. K. Chaubey, Prof. Anu Gupta, Prof. Sundar Balasubramaniam, Dr. Hari Om Bansal, Dr. Hitesh Datt Mathur, Dr. Dheerendra Singh, Dr. Anantha K Chintanpalli and Prof. Surekha Bhanot. A big thanks to the rest of the people that are or have been with BITS-Pilani during my time here so far, you all make this a great place to work at.

I am also fortunate to have the blessings of my Guru Babuji Maharaj and My father Shri. Hari Mohan Mishra, which I gratefully acknowledge. My deepest gratitude goes to my extended family: my sisters Roli di and Jaya di, my brother Anurag da, my brother-in-laws Mr.

Ameetabh Tyagi and Mr. Vinay Kumar Pandey. I have no words to thank my wife, Mrs. Lucky Mishra, who has always stood beside me like a rock whenever I had a difficult time. She has been a constant source of motivation and at times even sacrificed her professional time to help me grow further. My son Adyut never complained about not being able to spend enough time with him. Lastly, I express my thanks to all those who directly or indirectly contributed to the completion of this work.

| Date:  | Signature:          |

|--------|---------------------|

| Place: | Name: Ashish Mishra |

## **ABSTRACT**

Embedded Systems are an integral part of the stupendous technological advances as they meet the automation, monitoring and computational demands of the electronic industry. Most of the times, these systems are transparent to the user and do their defined work eternally such as telecommunication systems. Further advancements in these systems have led to the migration of the applications from manual operation to fully automated behavior; major examples of such domains include automotive industries, artificial intelligence applications, remote seasoning, surveillance etc. The stringent system requirements of such systems have pushed the designers to explore innovative design methodologies that deliver higher performance, occupy lesser area and consume minimum power. Modern embedded systems are expected to perform extensive computations on a streaming data set with various degrees of constraint. The design exploration space for such systems is huge; starting from a complete software (SW) implementation on various platforms (general purpose processor/digital signaling processor (DSP) processor/superscalar processor/very long instruction word (VLIW) processor/multiprocessor systems) and culminating as a complete hardware (HW).

The HW implementation includes application specific integrated circuits (ASIC) or field programmable gate arrays (FPGA) based design flow that delivers better performance as compared to the SW implementation due to a dedicated datapath and is thus used in many critical applications. In exploration of design space, the system specifications may further be optimized by partitioning a design into HW and SW. To exploit the potential of FPGA based design, the research community is also targeting different methodologies such as HW-HW partitioning and usage of partial reconfiguration concept.

FPGAs are HW programmable chips on which any digital function can be synthesized, tested and prototyped. They are an attractive choice for the designer due to less non-recurring cost and less time-to-market as compared to the ASIC. These chips contain configurable resources that are used to implement any application in HW. But as they contain a limited amount of resources on the chip, hence the amount of resources consumed when implementing any digital function on a chip, should not exceed the area constraint.

The concept of system design using partial reconfiguration design poses a number of challenges including optimization of partial reconfiguration method, reducing reconfiguration latency, scheduling of HW, SW and reconfigurable HW. To solve these problems, design space automation is one of the key challenges. A general objective of this thesis is efficient

deployment of embedded applications on reconfigurable computing systems. This thesis work targets one of the design space automation requirement which is to map C/C++/HDL/DFG application code onto general purpose hardware such as FPGA using static and partial reconfiguration approach. The thesis proposes a novel design methodology to automate the mapping of C/C++/HDL/Dataflow graphs application code by converting it into system level blocks. This includes design and development of an algorithm that generates coarse-grain functional blocks from the fine grain instruction level i.e. the proposed algorithm clusters an instruction level specification to high-level abstraction, while optimizing the latency and data communication among the combined functional blocks. To achieve an optimized algorithm for the above purpose, various design flows exist and improving them to suit our proposed algorithm is another important contribution of this thesis work.

To map the application on the system level architecture, (assuming general purpose hardware in FPGA with built-in processor within it), there are traditionally **two methods:** HW-SW codesign (method-1) and intellectual property (IP) core as HW implementation (method-2). Both the methods have been extensively investigated, enhanced and compared throughout the dissertation. The co-design method achieves the required system parameters by implementing the system partly in HW and partly in SW. Though the first method is well established, automation of HW-SW co-design of an application is limited to manual design flow. This work proposes an automated co-design methodology of an application using genetic algorithm. The proposed design flow supports HW as functional sub-blocks, where readymade IP blocks of critical part of the application are used. The proposed design flow uses time profiling and synthesis data to guide a genetic algorithm to generate good solutions.

In the co-design flow, a commercial high level synthesis tool has been used in this work for estimating the amount of resources consumed by the program. In addition, in this research a new approach has been proposed to estimate the amount of resources without synthesizing the program. For this purpose, the SW specification in C/C++ and a compiler has been used to generate control flow graph (CFG) which is a commonly used format for hardware generation. This process of mapping the logic from high level languages (HLL) to HW requires resource estimation at the granularity level of instruction. A resource table depicting the resource consumed by each operator found in the low level virtual machine (LLVM) compiler has been computed by coding in Verilog for Virtex-5 series. Using this library, a resource estimation algorithm based on CFG operator has been proposed and verified. In many cases if the entire specification is migrated to HW in the form of accelerator, it may consume significant

resources. Hence, optimization techniques applied at the HW specification are required to satisfy system design parameters (area-delay product). Various optimization techniques have applied and compared for area and latency trade-offs.

The second method for system design is to partition the specification in HW sub-modules and execute them as intellectual property (IP) core. Another major contribution of this work is proposing and testing the second methodology extensively. A dataflow graph specification has been used for verification and development of algorithms in this methodology.

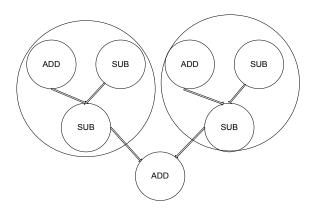

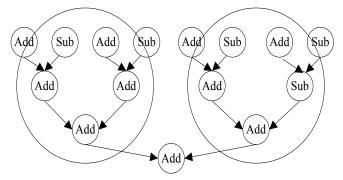

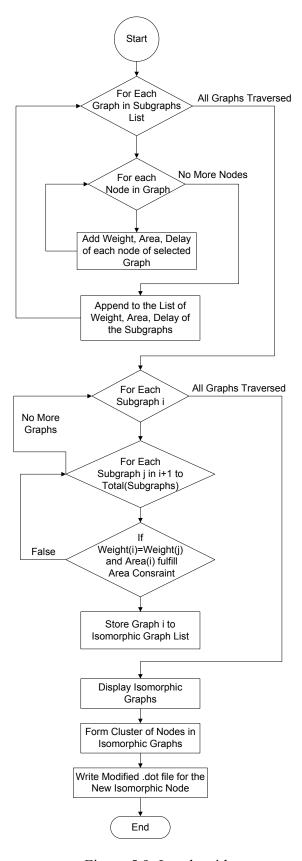

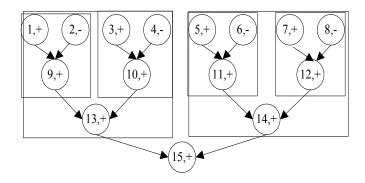

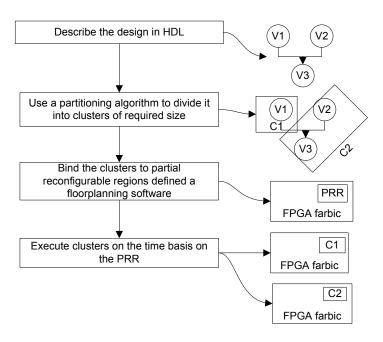

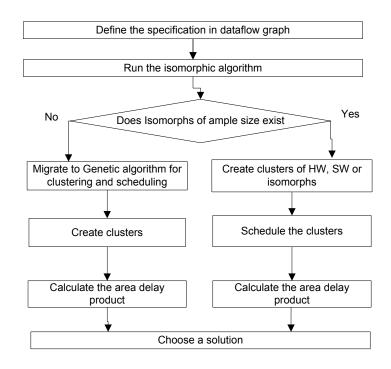

The second method can further be divided into sub-methods: static (sub-method-1) and dynamic (sub-method-2) scheduling of HW blocks on FPGA. In sub-method-1, a partitioning algorithm based on graph isomorphism has been proposed, which takes dataflow graph as the input and returns partitions based on constraints. These clusters are interfaced as static IP cores for reusability. Multiple clusters are possible which are similar in nature and must be interfaced as separate HW blocks in a system-on-chip (SOC) design flow and hence we have named this flow as HW-HW design flow.

In sub-method-2, dynamic scheduling of HW blocks based on partial reconfiguration flow has been investigated. A genetic algorithm based approach for optimizing the partitioning process and generating the best partitions based on defined objective function has been proposed. Using partial reconfiguration design flow the partitions are bound to a specific area on the chip known as partial reconfiguration (PR) region using floor planning software Xilinx PlanAhead. The results highlight the pros and cons of this technique by comparing the time required in SW and PR flow. The flow re-uses the same Silicon area at different execution times so that the application fits into the minimum area possible. This method provides a robust technique for implementing any application on FPGA irrespective of the quantity of resources it consumes. This opens new channels for exploiting PR design in future products where the reusability of HW would be possible. This will allow the development of new algorithms at run time at the user level. The design flow will further boost the automation of development and facility offered by electronic design automation (EDA) tools.

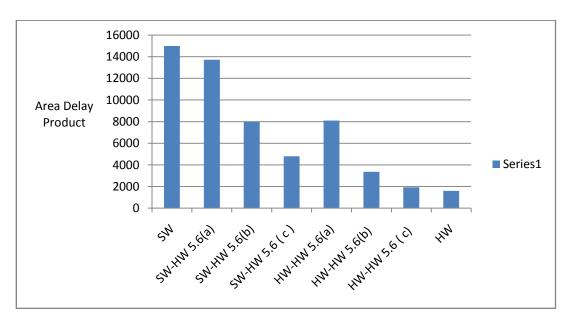

In order to assess both the methodologies, discrete cosine transform which is a computationally intensive algorithm has been used for comparing both the approaches on ML507 board. The results clearly show the design flow of isomorphic clustering is much better than any other flow.

The thesis proposes novel methodologies for system level integration in simulation as well as in experimentation. This research gives us an insight to HW-SW design space exploration of

an application and provides a foundation for future research in this domain. It emphasizes on the anticipated constraints and challenges in system design methodologies by presenting various optimal solutions. The results of this work offer a wide spectrum of design space implementations to the designer with area-delay parameter as the criteria to choose among them.

# TABLE OF CONTENTS

| ACKNOWLEDGEMENT                                        |

|--------------------------------------------------------|

| ABSTRACT                                               |

| TABLE OF CONTENTS.                                     |

| LIST OF ABBREVIATIONS                                  |

| LIST OF UNITS                                          |

| LIST OF FIGURES.                                       |

| LIST OF TABLES.                                        |

| Chapter 1. Introduction                                |

| 1.1. Embedded System Design.                           |

| 1.2. FPGA Based System Design.                         |

| 1.2.1. Introduction to FPGAs.                          |

| 1.2.2. FPGA Architecture.                              |

| 1.2.3. System-On-Chip Design.                          |

| 1.2.4. FPGA Based System-On-Chip Design.               |

| 1.3. Introduction to RCS                               |

| 1.3.1. Dynamic Partial Reconfigurable Systems (DPRS)   |

| 1.3.2. Advantages of Partial Reconfiguration.          |

| 1.4. Motivation for Current Research.                  |

| 1.5. Problem Definition.                               |

| 1.6. Thesis Organization.                              |

| 1.7. Conclusions.                                      |

| References for Chapter 1                               |

| Chapter 2. Literature Survey                           |

| 2.1. Frameworks and Design Methodology                 |

| 2.2. Partitioning and Scheduling.                      |

| 2.3. Resource Estimation and High Level Synthesis.     |

| 2.4. Reconfigurable Computing Systems                  |

| 2.4.1. Reconfiguration Controller.                     |

| 2.4.2. External Reconfiguration                        |

| 2 4 3 Internal Reconfiguration or Self Reconfiguration |

|      | 2.4.4. Partial Reconfigurable System Design in Xilinx                                 |

|------|---------------------------------------------------------------------------------------|

| 2.5. | Challenges of RCS Frameworks and Design Methodology                                   |

|      | 2.5.1. The Complex Design Flow                                                        |

|      | 2.5.2. Restrictions in Design Flow.                                                   |

|      | 2.5.3. The Reconfiguration Overhead.                                                  |

| 2.6. | Conclusion.                                                                           |

| Ref  | erences for Chapter 2                                                                 |

| Cha  | pter 3. Automated Migration of Applications in Hardware Software Co-                  |

| desi | gn Paradigm                                                                           |

| 3.1. | Hardware and Software Systems                                                         |

|      | Automated Approach to HW-SW Co-design                                                 |

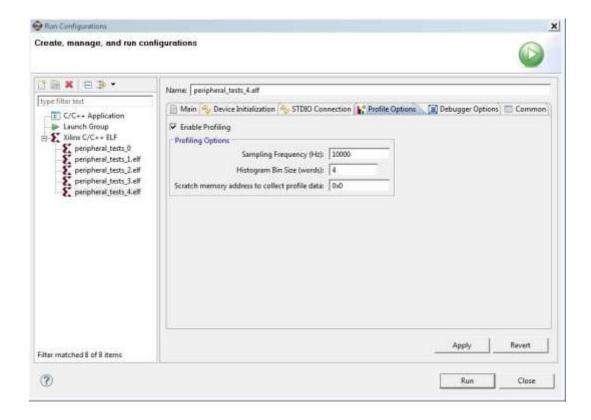

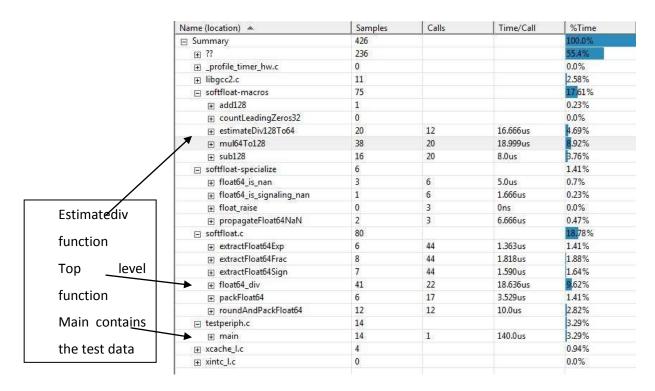

|      | Estimation of SW Resources Using Time profiling                                       |

|      | 3.3.1 Time Profiling on Target                                                        |

| 3.4. | Estimation of HW Resources Using LLVM Compiler                                        |

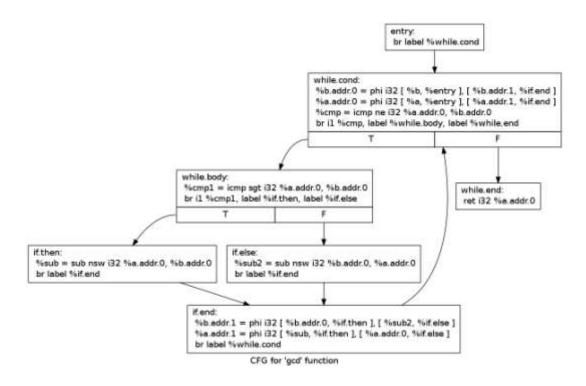

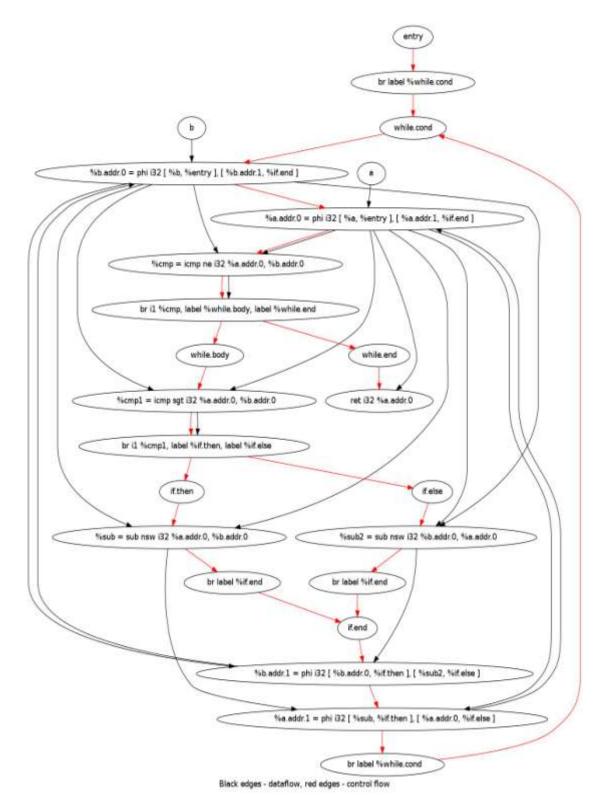

|      | 3.4.1. Generating CFG and DFG from LLVM Compiler                                      |

|      | 3.4.2. Library of Operators in LLVM Compiler                                          |

|      | 3.4.3. Converting C program to HDL                                                    |

|      | 3.4.4. Comparative Results of Theoretical and Synthesized Programs                    |

|      | 3.4.5. Creating Extended Basic Block for Task graph generation from CFG               |

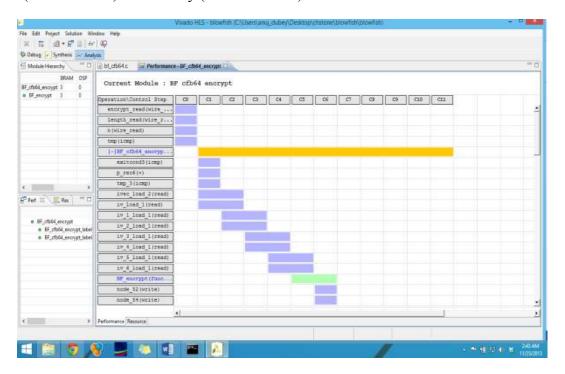

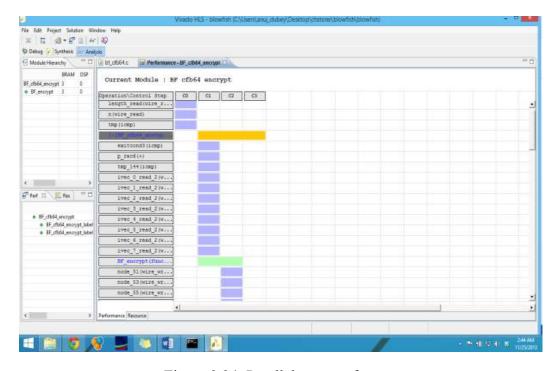

| 3.5. | Resource Estimation using Vivado High Level Synthesis Tool                            |

|      | 3.5.1. Optimizations in Vivado-HLS.                                                   |

| 3.6. | HW IP Design Integration of IP as a part of SOC.                                      |

|      | 3.6.1. Case Study for Hardware, Software IP Core Integration Using Vivado-HLS and EDK |

| 3.7. | Hardware Timer                                                                        |

| 3.8. | Results of Manual Interface of DfDiv Program as IP Core                               |

|      | 3.8.1. Comparison with LegUp.                                                         |

| 3.9. | Conclusions.                                                                          |

| Ref  | erences for Chapter 3                                                                 |

| Cha  | pter 4 Design and Development of Efficient Hardware and Software                      |

| Par  | titioning Algorithm                                                                   |

| 4.1. | Frameworks for Reconfigurable Computing Systems                                       |

| 4.2. | Hardware Software Co-design Partitioning Design Flow.                                 |

| 4.3. | Partitioning Process Using Genetic Algorithm for HW-SW Co-design                      |

|      | 4.3.1 Hardware and Software Partitioning Issues                                       |

| 4.4. Genetic Algorithm for Co-design.                                                  |       |

|----------------------------------------------------------------------------------------|-------|

| 4.4.1. Sample Case Study using GA for Co-design Using Callgraph Mod                    | del   |

| 4.4.2. Experimental Results                                                            |       |

| 4.5. Sample Case Study using GA for Co-design Using Task Graph Model                   |       |

| 4.5.1. Results of Sample Case Study                                                    |       |

| 4.6. Conclusions                                                                       |       |

| References for Chapter 4.                                                              |       |

| Chapter 5 Static and Dynamic Hardware Partitioning for Reconfigu Computing Systems     | rable |

| 5.1. Partitioning and Scheduling of Dataflow Graphs for Reconfigured Computing Systems |       |

| 5.2 Hardware and Software Synthesis of DFGs                                            |       |

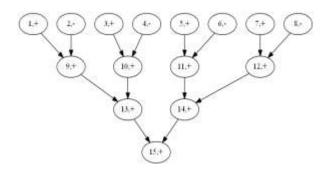

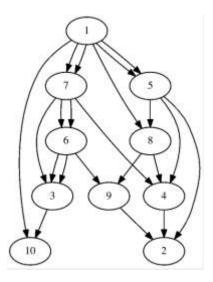

| 5.3. Algorithmic Approach for Creating Isomorphic Graph                                |       |

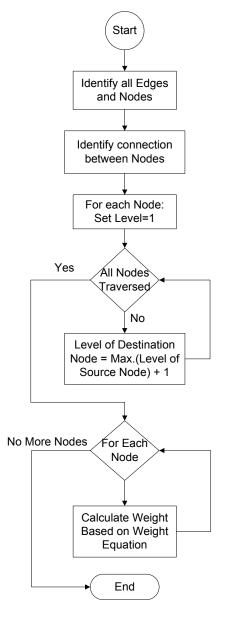

| 5.3.1. Weight algorithm                                                                |       |

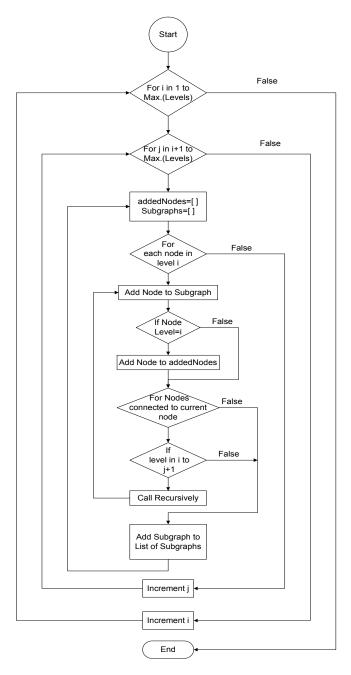

| 5.3.2. Subgraph Algorithm:                                                             |       |

| 5.3.3. Iso Algorithm:                                                                  |       |

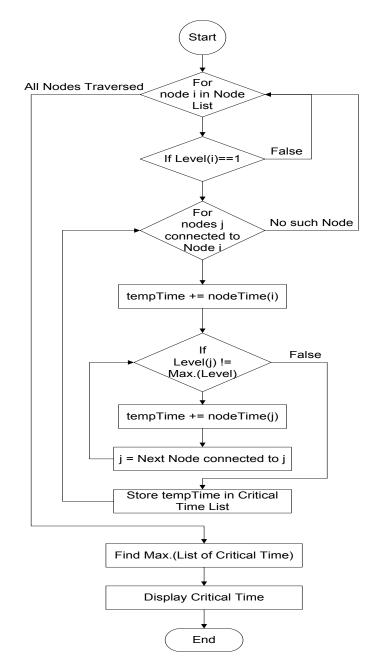

| 5.3.4. Performance Algorithm:                                                          |       |

| 5.4. Scheduler Design                                                                  |       |

| 5.5. Results and Discussion for Isomorphic Design Flow.                                |       |

| 5.6 Partitioning and Scheduling Problem for Partial Reconfiguration                    |       |

| 5.6.1 Coarse Level Graph Creation.                                                     |       |

| 5.7. Genetic Algorithm for RCS                                                         |       |

| 5.8. Wrapper Design and Scheduler Design.                                              |       |

| 5.9. Reconfiguration Time Analysis                                                     |       |

| 5.10. Parameters and Results for Genetic Algorithm                                     |       |

| 5.11. Random Task Graph Generation                                                     |       |

| 5.11.1. Random Graph Generators                                                        |       |

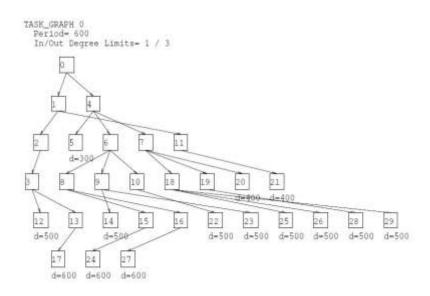

| 5.11.2. Algorithmic Design of MRTG                                                     |       |

| 5.11.2.1 Module 1: assignLevels.                                                       |       |

| 5.11.2.3 Module 2: connectNodes                                                        |       |

| 5.11. 2.4 Module 3: isomorphize                                                        |       |

| 5.11.2.5 Module 4: plotGraph                                                           |       |

| 5.12. Results and Discussion: Comparing ISO and GA Approaches                          |       |

| 5.13. DCT Case Study for HW Isomorphic Design flow Based on Experim Work               |       |

| 5.13.1. Implementations of Discrete Cosine Transform                                   |       |

| 5.13.2 Pipelining Approach and Implementation of DCT based on AA Algorithm. |           |

|-----------------------------------------------------------------------------|-----------|

| 5.13.3. HW SW Co-design of DCT                                              |           |

| 5.13.4. Synthesis and Simulation results.                                   |           |

| 5.13.5. Synthesis and Simulation Results of PPR Design Flow                 |           |

| 5.14. Conclusions                                                           |           |

| References for chapter 5.                                                   |           |

| Chapter 6 Conclusions                                                       |           |

| 6.1. Contributions of the Thesis.                                           |           |

| 6.2. Limitations of the Work Done.                                          |           |

| 6.3. Future Scope.                                                          |           |

| List of Publications                                                        |           |

| Appendix-1                                                                  | . <b></b> |

| Appendix-2                                                                  | . <b></b> |

| Appendix-3                                                                  |           |

| BRIEF BIOGRAPHY OF THE CANDIDATE                                            |           |

| BRIEF BIOGRAPHY OF THE SUPERVISOR                                           |           |

| BRIEF BIOGRAPHY OF THE CO-SUPERVISOR                                        |           |

## **ABBREVIATIONS**

ASIC Application specific integrated circuits

AXI Advanced Microcontroller Bus Architecture

BRAM Random access block memory

CDFG Control dataflow graphs

CFG Control flow graph

CLB Configurable logic block

DAG Directed acyclic graph

DCT Discrete cosine transform

DFG Dataflow graph

DDR Double data rate

DFG Dataflow graphs

DMA Direct memory access

DSP Digital signal processing

EBB Extended basic block

EDA Electronic design automation

FIFO First-in-first-out

FM Fiduccia-Mattheyses

FPGA Field Programmable Gate Arrays

GA Generic algorithm

HAL Hardware abstraction layer

HDL Hardware description language

HLL High level languages

HLS High Level Synthesis

HW Hardware

I/O Input Output

ICAP Internal configuration access port

IP Intellectual Property

IR Intermediate representations

KHz Kilo Hertz

LLVM Low level virtual machine

LUT Look-up-table

MRTG Modular random task graph generator

OS Operating Systems

Pc Crossover probability

PLB processor local bus (PLB)

Pm Mutation probability

PR Partial reconfiguration

PRM Partially reconfigurable modules

PRR Partial reconfigurable region

RCS Reconfigurable computing systems

RTL Register transfer level

SA Simulated annealing

SDK Software Development Kit

SOC System-On-Chip

SRAM Static random access memory

SUIF Stanford universal intermediate format

SW Software

UART Universal asynchronous receiver transceiver

UCF user constraints file

VLSI Very large scale integration

XPS Xilinx Platform Studio XPS Xilinx platform studio

#### LIST OF UNITS

MHz Mega Hertz

ns Nano seconds

μsec Microseconds

KB Kilobyte

MB Megabyte

# LIST OF FIGURES

| Figure No | o. Title                                                                  | Pag<br>No |

|-----------|---------------------------------------------------------------------------|-----------|

| 1.1       | Embedded development cycle                                                | 1         |

| 1.2       | Logic element                                                             | 5         |

| 1.3       | Look-Up-Table                                                             | 5         |

| 1.4       | FPGA architecture.                                                        | 6         |

| 1.5       | Various IP interfacing techniques                                         | 7         |

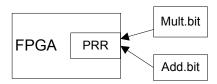

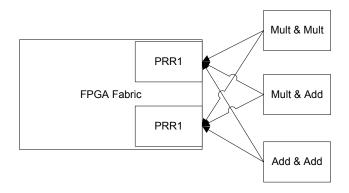

| 1.6       | FPGA based system with one PR region with two PRM mapped                  | 9         |

| 1.7       | Organization of thesis work                                               | 12        |

| 2.1       | Co-simulation of digital camera case study in Xilinx ISIM                 | 17        |

| 2.2       | HW accelerators in Leon3 platform on Altera StratixII                     | 19        |

| 2.3       | ASSET co-design methodology                                               | 19        |

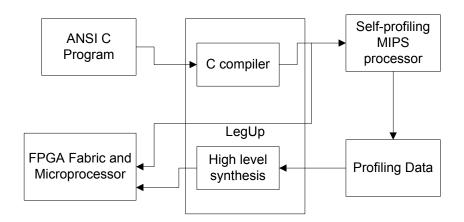

| 2.4       | LegUp Co-design methodology                                               | 20        |

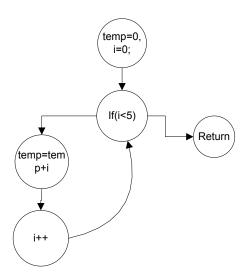

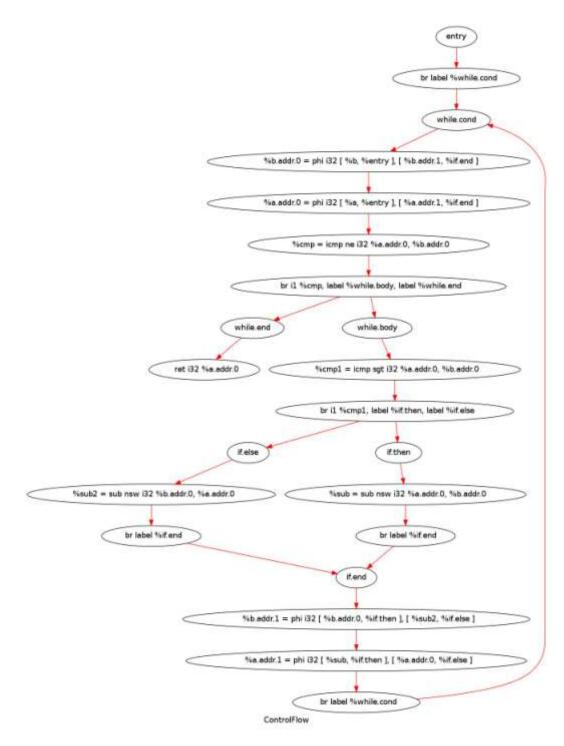

| 2.5       | Control flow graph for the code snippet                                   | 22        |

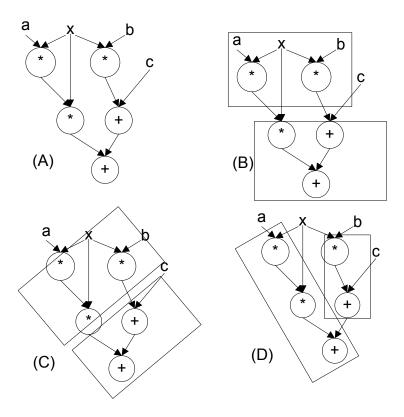

| 2.6       | Partitioning of graph                                                     | 23        |

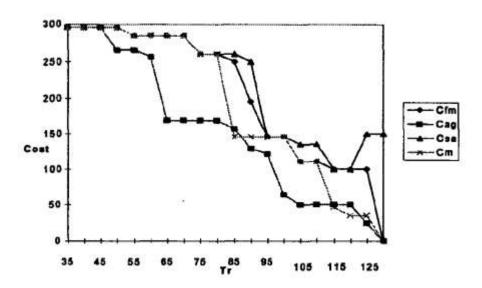

| 2.7       | Comparative results among FM, GA, SA and MFM for cost vs. time constraint | 25        |

| 2.8       | ASAP schedule                                                             | 27        |

| 2.9       | ALAP schedule                                                             | 27        |

| 2.10      | Constraint scheduling.                                                    | 29        |

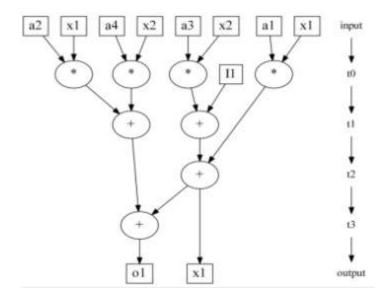

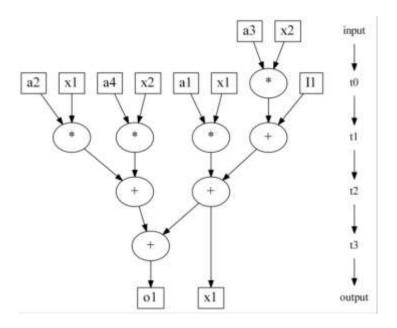

| 2.11      | Express benchmark of Cosine-2 program                                     | 30        |

| 2.12      | Node matching based isomorphic graphs                                     | 30        |

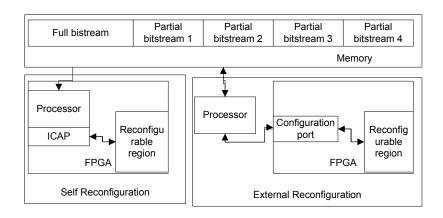

| 2.13      | External vs. internal reconfiguration.                                    | 33        |

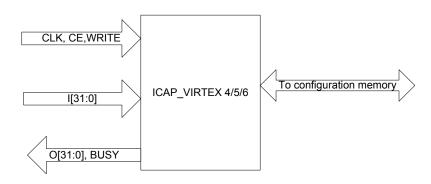

| 2.14      | ICAP controller                                                           | 34        |

| 2.15      | FPGA systems with one reconfigurable region                               | 35        |

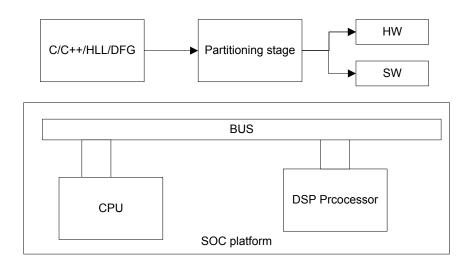

| 3.1       | SOC platform on FPGA with a design in HW and SW                           | 51        |

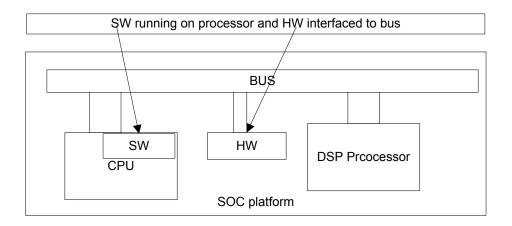

| 3.2       | Design in HW-SW with bus interface.                                       | 52        |

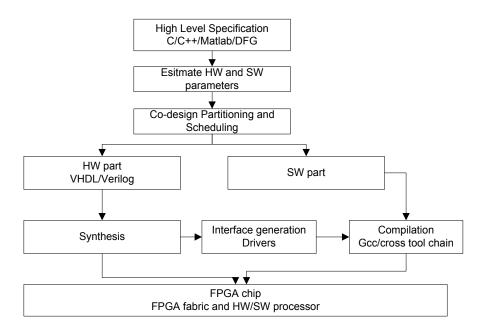

| 3.3       | Co-design tool.                                                           | 53        |

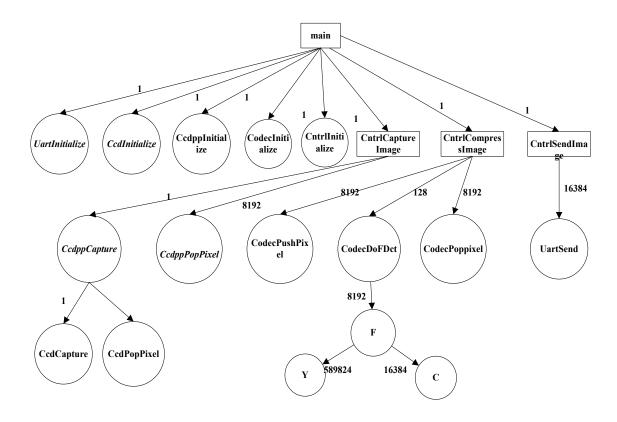

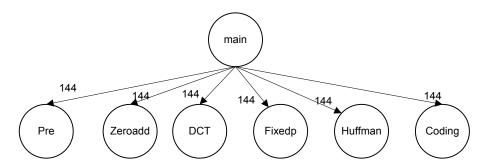

| 3.4       | Callgraph of digital camera case study                                    | 57        |

| 3.5       | Profiling and bin options in SDK                                          | 58        |

| 3.6       | Software profiling results of DFDIV on ML507 board on PowerPC@400MHz.     | 59        |

| 3.7     | Control flow graph of GCD program.                                |

|---------|-------------------------------------------------------------------|

| 3.8     | Instruction level CFG of GCD program                              |

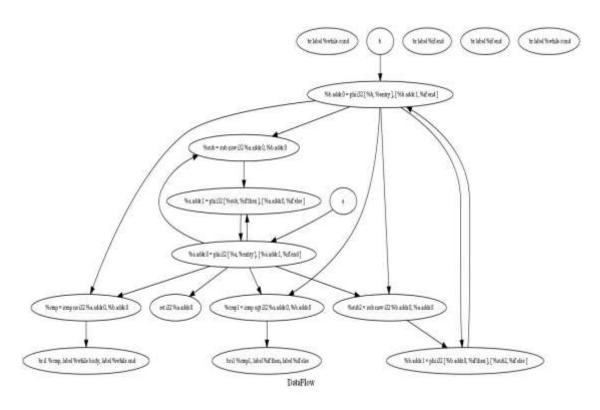

| 3.9     | CFG of GCD program                                                |

| 3.10    | DFG of GCD Program.                                               |

| 3.11    | Fibonacci series C program and its CFG                            |

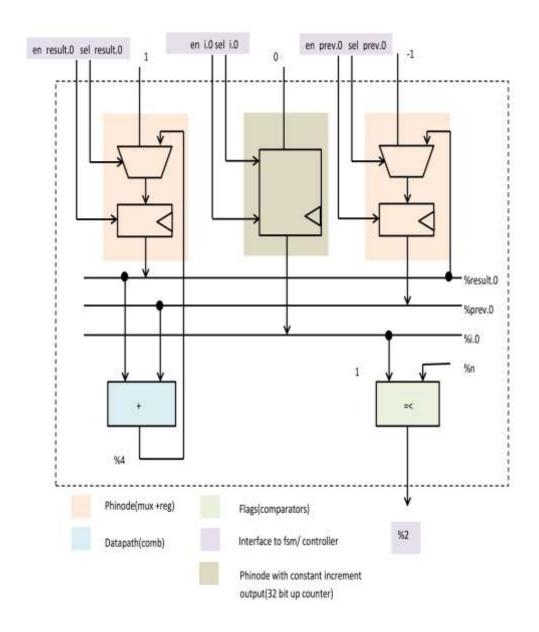

| 3.12    | Datapath for Fibonacci program                                    |

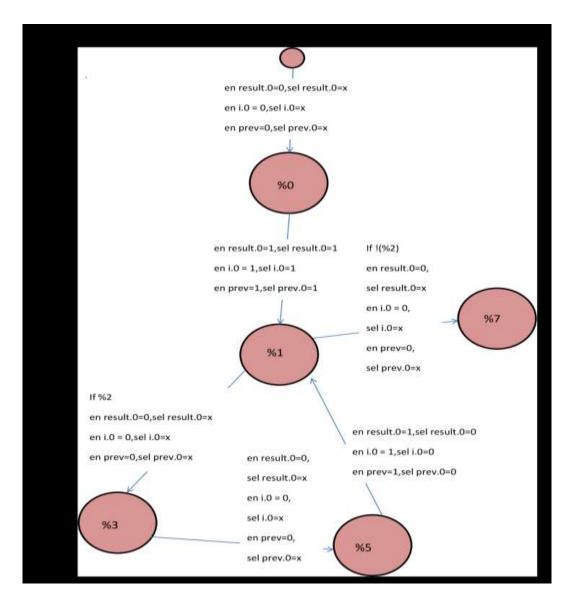

| 3.13    | FSM of Fibonacci program.                                         |

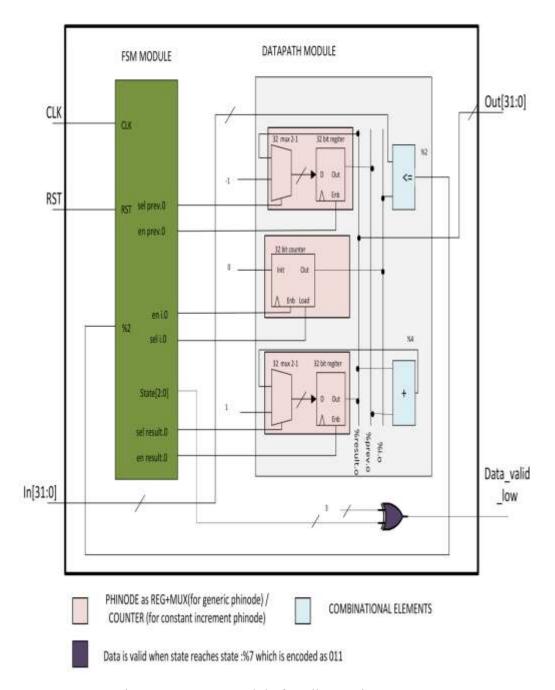

| 3.14    | Top module for Fibonacci program                                  |

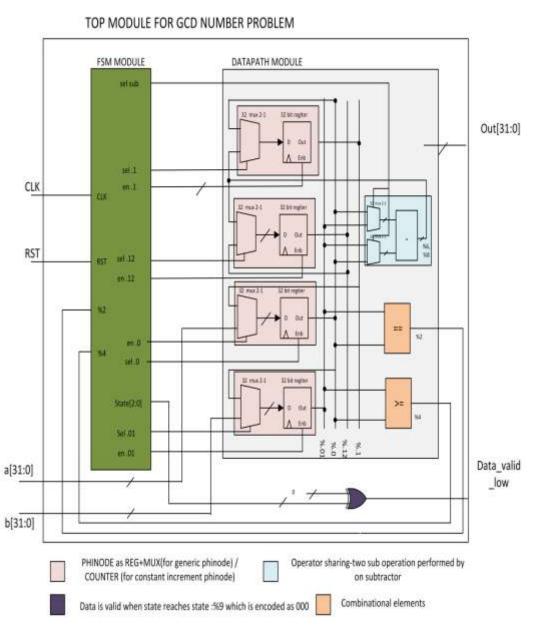

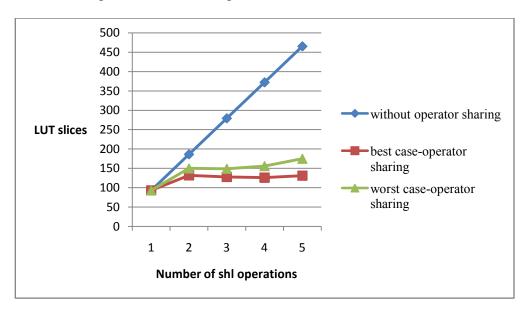

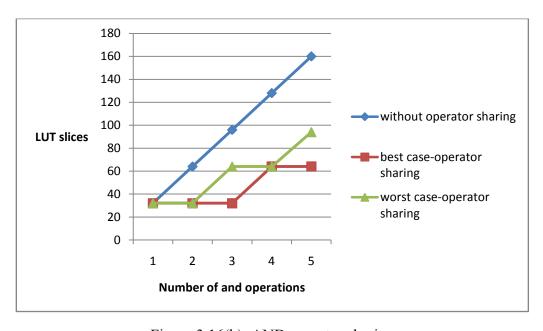

| 3.15    | Sharing operators program for Fibonacci                           |

| 3.16(a) | SHL operator sharing.                                             |

| 3.16(b) | AND operator sharing.                                             |

| 3.16(c) | ADD operator sharing.                                             |

| 3.16(d) | SUB operator sharing.                                             |

| 3.17    | Verification of the GCD program                                   |

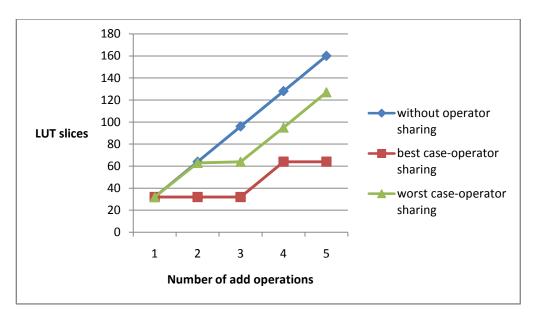

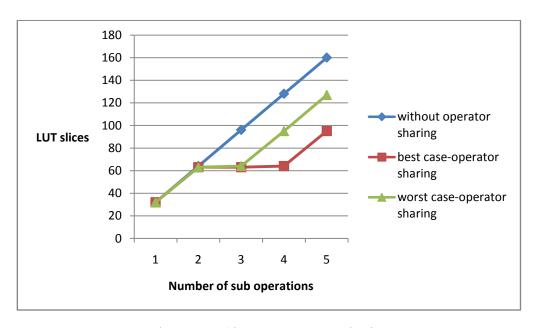

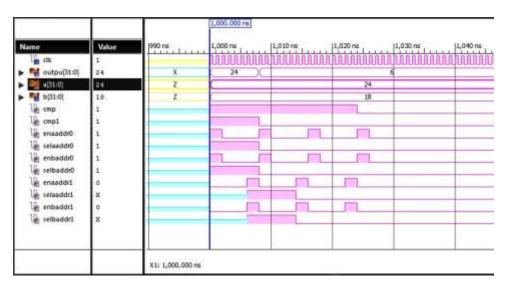

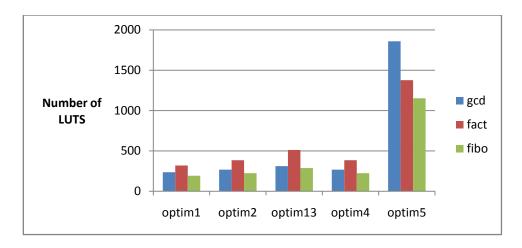

| 3.18    | Comparison of LUT after optimizations on three programs           |

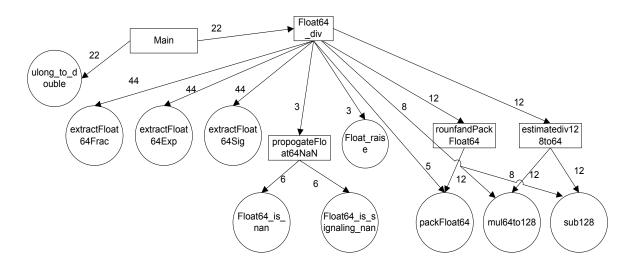

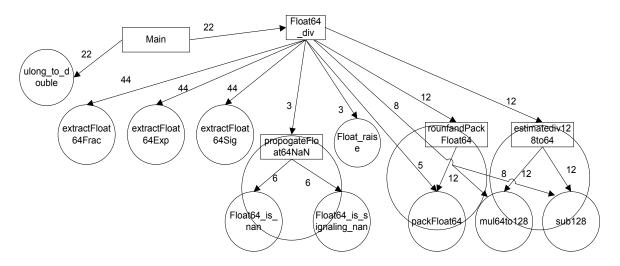

| 3.19    | Callgraph for DfDiv                                               |

| 3.20    | Identification of extended basic block                            |

| 3.21    | CFG for Dijkstra                                                  |

| 3.22    | Extended basic block for the CFG.                                 |

| 3.23    | Sequential access of array                                        |

| 3.24    | Parallel access of array                                          |

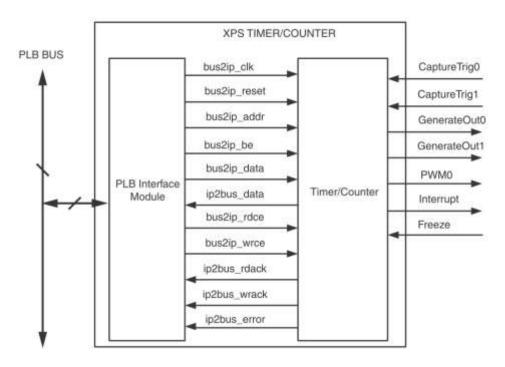

| 3.25    | XPS timer interface with PLB bus                                  |

| 4.1     | HW and SW Co-design flow                                          |

| 4.2 (a) | Sample graph                                                      |

| 4.2 (b) | Parameters for sample graph                                       |

| 4.3 (a) | Sample graph                                                      |

| 4.3 (b) | Adjacency matrix                                                  |

| 4.4     | Callgraph of a random C program                                   |

| 4.5     | A SOC testing architecture                                        |

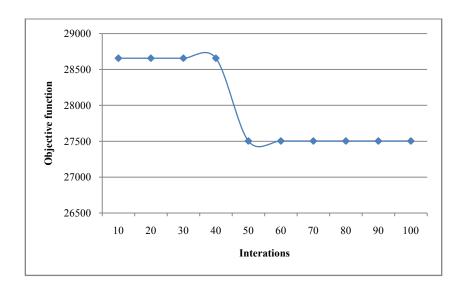

| 4.6     | Fitness value optimized with iterations in GA for implementation. |

| 4.7     | Callgraph for DfDiv                                               |

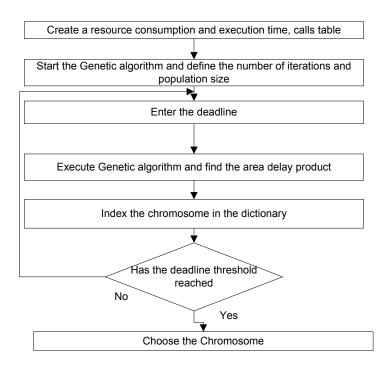

| 4.8     | Flowchart for the algorithm execution.                            |

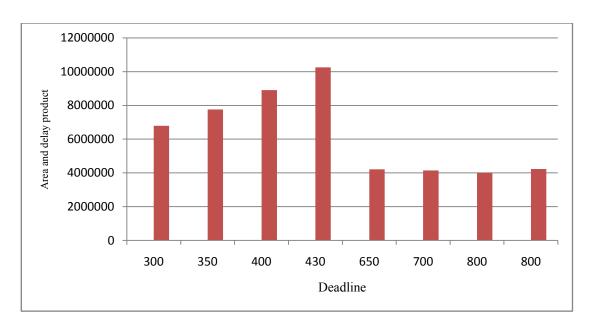

| 4.9     | Deadline vs. Area/delay product for various genes                 |

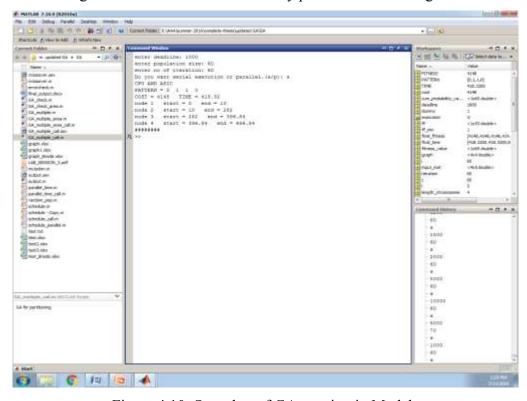

| 4.10    | Snapshot of GA running in Matlab                                  |

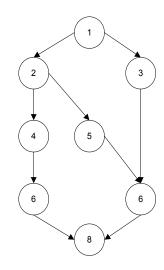

| 4.11    | Sample task graph                                                 |

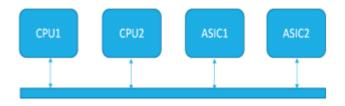

| 4.12 | Multiple CPU and ASIC sample testing architecture                          |

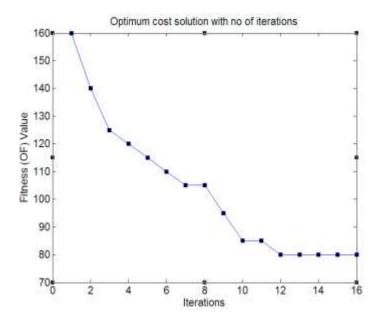

|------|----------------------------------------------------------------------------|

| 4.13 | Fitness value optimized with iterations in GA for CPU2 - ASIC1             |

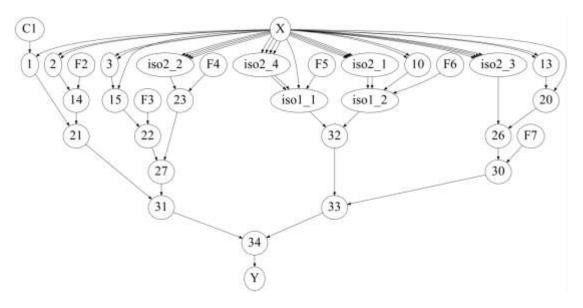

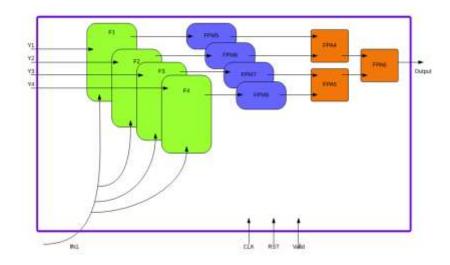

| 5.1  | Framework 2 design flow.                                                   |

| 5.2  | Node model                                                                 |

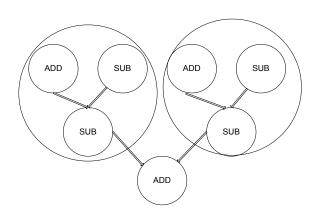

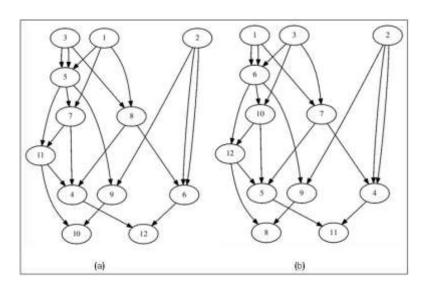

| 5.3  | Node matching based isomorphic graphs                                      |

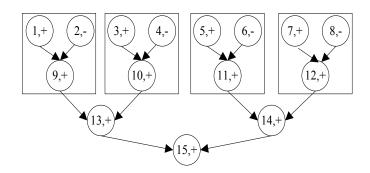

| 5.4  | Creation of isomorphic clusters at different levels                        |

| 5.5  | Comparison of various implementations                                      |

| 5.6  | Sample graph                                                               |

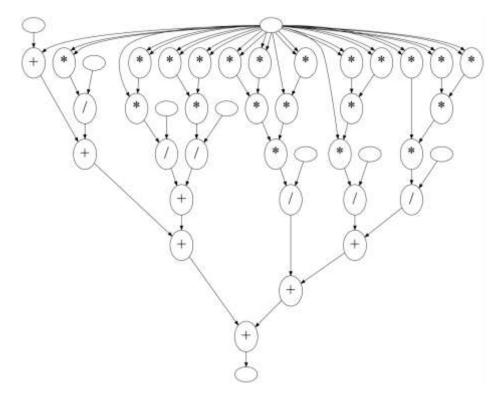

| 5.7  | Weight algorithm                                                           |

| 5.8  | All subgraphs algorithm                                                    |

| 5.9  | Iso algorithm                                                              |

| 5.10 | Performance algorithm                                                      |

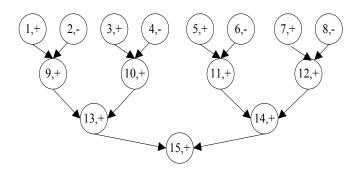

| 5.11 | Sample graph                                                               |

| 5.12 | Various clusters in sample graphs                                          |

| 5.13 | Sample graph with isomorphic clusters                                      |

| 5.14 | Resources consumed by a basic design in ML507 Board                        |

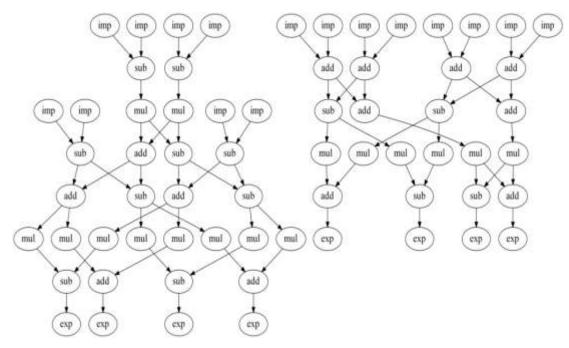

| 5.15 | DFG of Cosine series.                                                      |

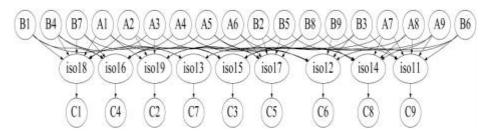

| 5.16 | Cosine Series with Isomorphic Graphs                                       |

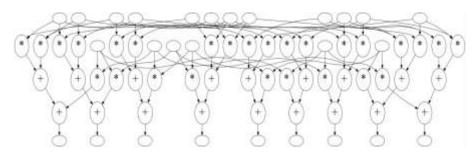

| 5.17 | DFG of Exponent series.                                                    |

| 5.18 | Exponent series with isomorphic graphs                                     |

| 5.19 | Matrix Multiplication for 3x3 elements                                     |

| 5.20 | Matrix Multiplication for nine isomorphic graphs                           |

| 5.21 | Sine Series with five elements.                                            |

| 5.22 | Sine Series with three isomorphic graphs                                   |

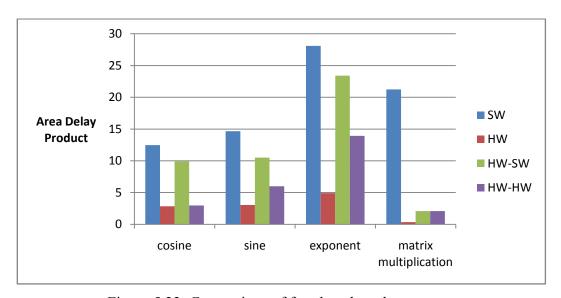

| 5.23 | Comparison of four benchmark programs                                      |

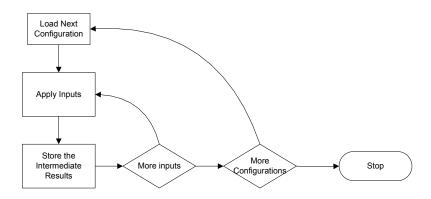

| 5.24 | Partitioned design running on PRR.                                         |

| 5.25 | Two PR regions with three PRM                                              |

| 5.26 | Two PR regions Schedule.                                                   |

| 5.27 | PR schedule                                                                |

| 5.28 | Level based clusters                                                       |

| 5.29 | Scheduler design in SDK                                                    |

| 5.30 | DFG of Cosine1                                                             |

| 5.31 | DFG of Cosine 2.                                                           |

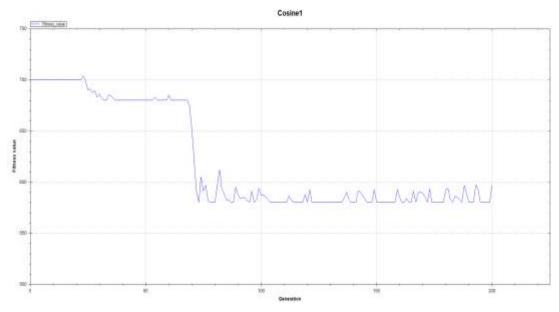

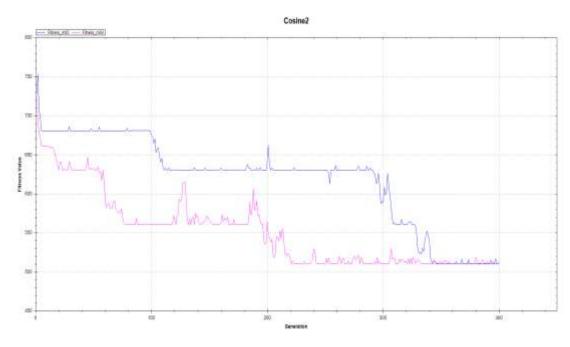

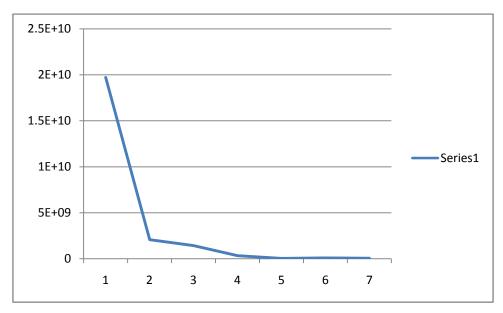

| 5.32 | Fitness vs. generations                                                    |

| 5.33 | Fitness value vs. generation for mutation value as 0.2(Blue) and 0.4(Pink) |

|      |                                                                            |

| 5.34 | A graph generated using TGFF                    | 168 |

|------|-------------------------------------------------|-----|

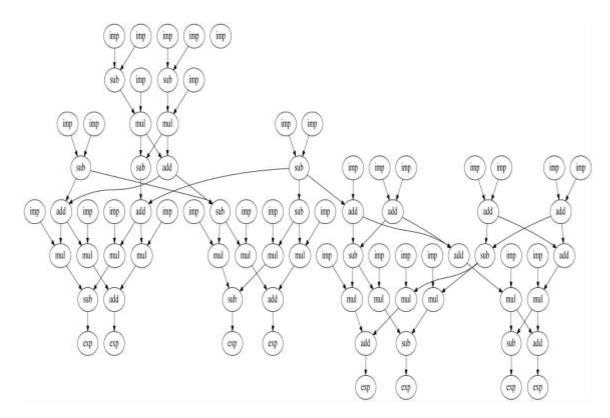

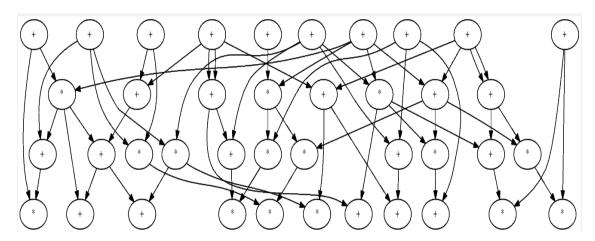

| 5.35 | A rooted graph generated using MRTG             | 173 |

| 5.36 | Two isomorphic graphs generated using MRTG      | 170 |

| 5.37 | Nodes with operators generated using MRTG       | 17  |

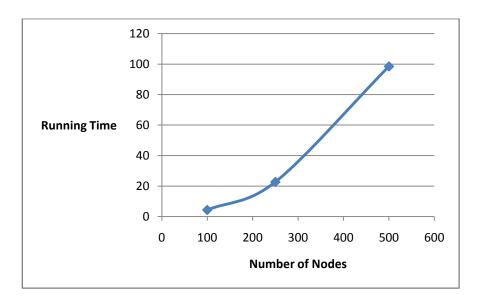

| 5.38 | Number of Nodes vs. time taken.                 | 178 |

| 5.39 | Flowchart for comparing the ISO and GA approach | 180 |

| 5.40 | Pipeline architecture                           | 184 |

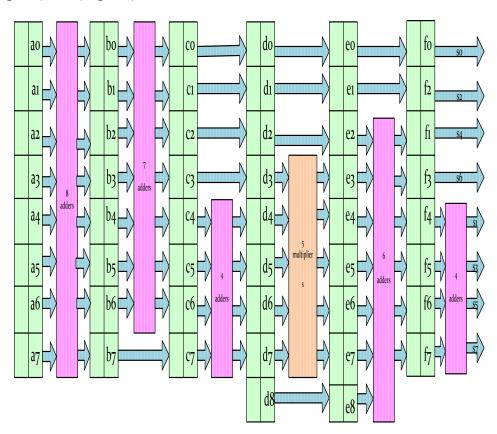

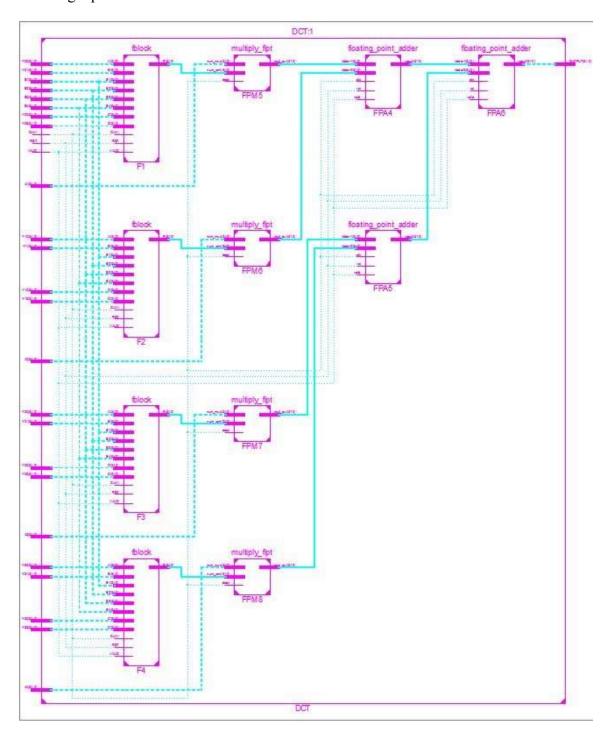

| 5.41 | DCT netlist in Xilinx ISE.                      | 18  |

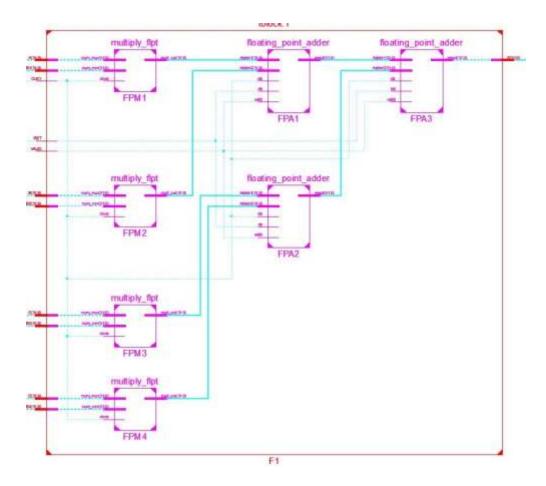

| 5.42 | F block netlist in Xilinx ISE.                  | 18  |

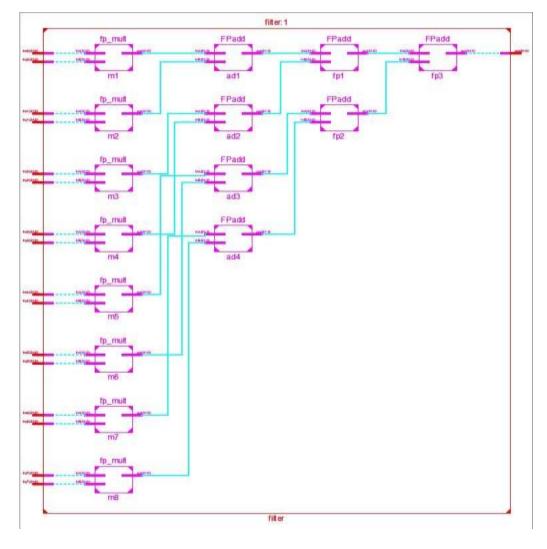

| 5.43 | Netlist diagram for dataflow model              | 18  |

| 5.44 | Redrawn DCT netlist showing isomorphic modules  | 18  |

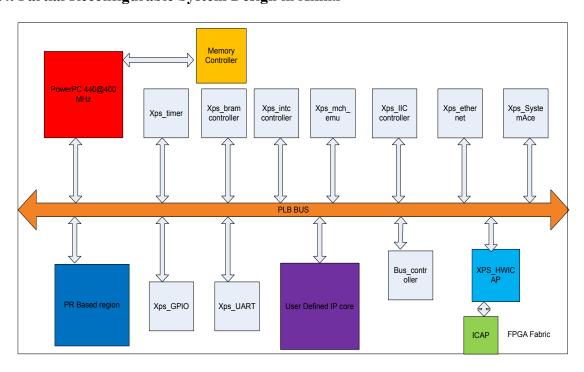

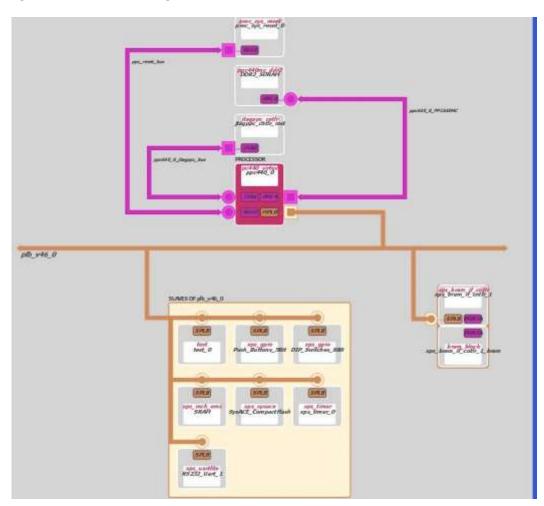

| 5.45 | EDK components used in implementation           | 18  |

| 5.46 | Comparison of area and delay product            | 19  |

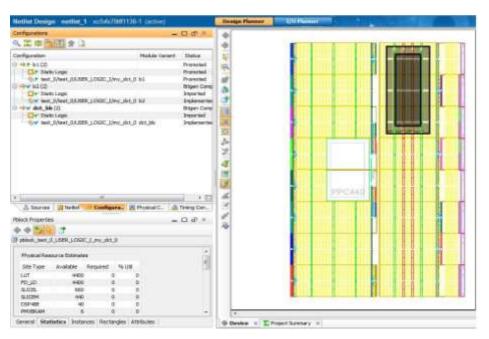

| 5.47 | Floorplan for DCT having one PRR                | 19  |

# LIST OF TABLES

| Table No | Title                                                                                                                                           | Page<br>No. |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 1.1.     | HW and SW comparison                                                                                                                            | 3           |

| 2.1.     | Three parameters for digital camera case study on 8051                                                                                          | 17          |

| 2.2.     | Performance results of LegUp                                                                                                                    | 21          |

| 2.3.     | Configuration bandwidth Using ICAP primitive                                                                                                    | 35          |

| 2.4.     | Comparison of reconfiguration throughput from 2003 to 2009                                                                                      | 37          |

| 2.5.     | Reconfiguration speed measurement of ICAP design for various sizes of partial bitstream.                                                        | 39          |

| 3.1.     | Digital system hardware and software layered architecture                                                                                       | 49          |

| 3.2      | Flat profile                                                                                                                                    | 55          |

| 3.3.     | Callgraph profile                                                                                                                               | 56          |

| 3.4.     | Library of operators                                                                                                                            | 65          |

| 3.5      | LUT/DSP resource estimation for each of the optimizations                                                                                       | 77          |

| 3.6      | Comparison of resources                                                                                                                         | 78          |

| 3.7      | Resource consumption of Dfdiv functions                                                                                                         | 79          |

| 3.8      | Synthesized results of ChStone benchmarks                                                                                                       | 83          |

| 3.9      | Performance comparison of original and optimized adpcm synthesis and Resource usage comparison of original and optimized adpcm synthesis.       | 84          |

| 3.10     | Performance comparison of original and optimized blowfish synthesis and Resource usage comparison of original and optimized blowfish synthesis. | 86          |

| 3.11     | Performance comparison of original and optimized dfmul synthesis and Resource usage comparison of original and optimized dfmul synthesis        | 86          |

| 3.12     | Performance comparison of original and optimized mips synthesis and                                                                             | 86          |

|          | Resource usage comparison of original and optimized mips synthesis                                                                              |             |

| 3.13     | Performance comparison of original and optimized sha synthesis and Resource usage comparison of original and optimized sha synthesis            | 87          |

| 3.14     | Comparison with LegUP compiler synthesis results                                                                                                | 87          |

| 3.15     | ChStone benchmarks timing results on ML506 Board                                                                                                | 94          |

| 3.16     | Performance comparison of DfDiv in LegUp.                                                                                                       | 95          |

| 3.17 | Area delay product comparison of DfDiv in LegUp                     |

|------|---------------------------------------------------------------------|

| 4.1  | SW and HW parameters                                                |

| 4.2  | Partitioning results for different deadlines                        |

| 4.3  | Parameter values used in GA                                         |

| 4.4  | Resource usage from Vivado HLS for DfDiv program                    |

| 4.5  | Parameters for DfDiv                                                |

| 4.6  | Results of DfDiv program                                            |

| 4.7  | Implementation parameters for different tasks                       |

| 4.8  | Optimization results for deadline = 275                             |

| 4.9  | Optimization results for deadline = 200.                            |

| 4.10 | Partitioning results for different deadlines                        |

| 4.11 | Partitioning results for different area                             |

| 5.1  | Description of different implementations                            |

| 5.2  | Comparison of time taken by the DFG in different implementations    |

| 5.3  | Weight of the nodes                                                 |

| 5.4  | Parameters for sample graphs                                        |

| 5.5  | Sample graph results                                                |

| 5.6  | Programs used for testing                                           |

| 5.7  | Library of hardware blocks and their values on Xilinx ML507 board   |

| 5.8  | Comparison of area delay product for Cosine function                |

| 5.9  | Comparison of area delay product for Exponent function              |

| 5.10 | Comparison of area delay product for Matrix function                |

| 5.11 | Comparison of area delay product for Sine function                  |

| 5.12 | Constants used in genetic algorithm                                 |

| 5.13 | Order of complexity of functions in GA                              |

| 5.14 | PR and GA parameters                                                |

| 5.15 | Express benchmark programs used for testing GA                      |

| 5.16 | Number of nodes vs. time taken                                      |

| 5.17 | GA applied to four benchmarks                                       |

| 5.18 | Comparison of Area delay product                                    |

| 5.19 | Computational steps in AAN algorithm                                |

| 5.20 | Matrix as Coefficient                                               |

| 5.21 | Resources consumed by floating point dataflow model of DCT          |

| 5.22 | Area and delay of each node                                         |

| 5.23 | Showing the resources for the AAN and DFG design flow as highlights |

| 5.24 | Comparison of various implementations done | 191 |

|------|--------------------------------------------|-----|

| 5.25 | Comparison of reconfiguration time         | 193 |

# Chapter 1

# Introduction

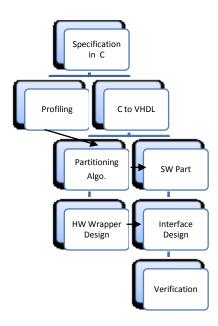

This chapter presents an introduction to embedded system design, FPGA based System-On-Chip design, reconfigurable systems, and partial reconfigurable systems. After presenting the design flow for such systems, the research gaps are identified and the objectives are outlined. The chapter ends with the discussion on the thesis organization in the form of a flow graph.

#### 1.1. Embedded System Design

Electronic systems have become ubiquitous and pervasive because of the possibilities of smart system designs which encompasses computation, communication and sensing. Such systems are built with high speed processing components, complex interfaces such as a camera and wired/non-wired communication. Embedded systems, which are designed to achieve application specific requirements, have further boosted the lifespan of such systems. These systems are designed with miscellanea of components such as Microcontrollers /Microprocessors/System-on-chip (SOC), sensors/actuators, input/output devices, storage elements and accelerators. In designing such systems, the characteristics which are of prime concern are good real-time performance, low monetary cost, low power design and less time-to-market. These systems are programmed with applications written in software (SW) for a chosen hardware (HW), making the design cycle rigid in terms of hardware parameter variations. Fig. 1.1 shows that a conventional design cycle of embedded systems, in which selection of HW and then writing the required SW [1.1] is sequential in nature.

Figure 1.1: Embedded development cycle

The modern embedded systems [1.2, 1.3] which are used to design complex systems such as surveillance, object tracking, machine learning, etc. require more processing demand for intensive computational part of the application. The conventional embedded design flow starts by selecting the processing element, writing the SW for application, cross-compiling and burning the image created. Such a SW implementation for intensive applications offers a high degree of flexibility, but exhibits poor performance due to sequential execution on embedded

platforms like microcontroller. High-performance computing and parallel computing paradigms of computer science aim at achieving the performance by exploiting parallelism as multithreaded application which is bound to run on multi-core systems. Such computing is more applicable to general purpose machines where operating system support, OpenGL like library compilation and costly platforms are the backbone.

Signal processing in SW has been further strengthened by usage of digital signaling processors (DSP) which have a tailored data path for better computation. Traditionally, digital signal processors have been used in many Digital Signal Processing applications [1.4], mainly due to the short development time, lower power consumption, and lower cost. Such processors are still the choice for applications requiring computation. However, over the decade, many algorithms which were implemented in SW were migrated to HW because of the higher performance gain as compared to DSP processors.

The HW implementation, which requires the development in a hardware description language (HDL) and code verification, has the lowest degree of flexibility, but shows the best performance due to the possibility of extraction of parallelism. All those operations which are independent in SW can be executed at the same time in HW, allowing the design of a concurrent structure. Such applications which have been migrated from SW to HW for achieving performance are known as accelerators [1.5, 1.6]. Such accelerators are conventionally designed by two different approaches. The first approach is to design the HW as chip using ASIC methodology. The common examples of such chips are graphics cards, network cards, router, gaming gazettes etc. The performance gain in this process is enormous, but the high non-recurring engineering cost and long development cycle makes it attractive only for voluminous production.

The second design approach is based on designing the system using Field Programmable Gate Arrays (FPGA) which allows the accelerator to be designed, tested and interfaced to the processor at the user level. The FPGAs do not deliver as much performance gain as compared to the ASIC based design flow [1.7], but chip fabrication is bypassed which saves considerable design cycle time and thus are a favored choice [1.8]. The FPGAs chips are designed with configurable cells and can be used to implement any digital function. The user level HW programmability makes these chips an attractive choice for a large class of applications. The FPGA based design offers an embedded development environment platform, which has a processor around which the systems is designed and any HW intellectual property (IP) core can be interfaced to an underlying bus.

This platform allows the design to be implemented in SW, HW, HW-SW (HW-SW co-design) or HW-HW [1.9] thus providing a designer to discover various HW/SW trade-off. The comparison of HW and SW on various parameters such as execution, resources, etc. is shown in Table 1.1. Both HW and SW consume space on the FPGA chipset as configurable cells and memory.

Table 1.1: HW and SW comparison

| Parameter      | HW             | SW            |

|----------------|----------------|---------------|

| Execution      | Concurrent     | Sequential    |

| Development    | Flexible/Rigid | Very Flexible |

| Resources      | Uses spaces    | Uses Memory   |

| Performance    | Fast           | Slow          |

| Time to Market | More           | Less          |

HW-SW co-design [1.10] flow requires the identification of candidate functions suitable for HW implementation and its interface to the remaining part of the application. Whereas, HW-HW design flow requires the design to be partitioned into sub-designs and executed in the predefined areas. The HW partitions can be interfaced and executed statically or dynamically, giving rise to two different approaches. When a part of the chip can only be used by an application at any point of time, we call it static approach. In the case of dynamic, the same area can be used by multiple applications at different point of times. This feature has now become feasible with the advent of partial reconfiguration, which allows a part of the chip to be reconfigured even when the system is running. HW-HW design flow implemented with partial reconfiguration support is thus a new emerging trend and has not been extensively tested on HW [1.7]. The increasing trends towards high performance, reusability and low power design have encouraged the researchers to add new dimensions to system design under various degrees of constraint. The topic of this research work is thus inspired from comparing the SW and HW design flows.

#### 1.2. FPGA Based System Design

#### 1.2.1. Introduction to FPGAs

The programmable chips came into existence due to the advent of general purpose processing [1.7] in which a HW code is burned into a programmable ROM chip referred as basic input output systems (BIOS). Programmable logic devices which include programmable logic array, programmable array logic and generic array logic [1.11] are used for developing glue logic in prototyping designs such as address decoder, error detection and correction, etc. With the

advancement in very large scale integration (VLSI) design flow, the density of logic gates increased, making it possible to bring more complex design into HW, giving rise to the generation of FPGAs.

The FPGAs are programmable VLSI chips that can be used to implement any digital function without changing the on chip HW resources. FPGA chips contain configurable memory cells, which are either anti-fuse or memory based. An anti-fuse based bit cell uses irreversible thin (gate) oxide breakdown mechanism to program a bit and it is one time programmable in nature. The examples of such FPGA are Actel based chips memory based FPGAs use SRAM, FLASH, EEPROM based technology [1.7]. Memory based technology offers reprogrammable dimension of these systems by allowing them to be programmed almost unlimited times. The SRAM based technology holds the configuration in the memory only when the power is up; however, in the case of FLASH based technology the configuration is permanently stored in the memory. The major market players in the FPGA domain are Xilinx [1.12], Altera [1.13], Lattice [1.14], Actel [1.15], with Xilinx capturing 45-50% of the market share and supporting various embedded platforms based on the processor like PowerPC, ARM etc. The remaining discussions in this thesis are with respect to FPGAs manufactured by Xilinx. Xilinx offers a plethora of electronic design automation (EDA) tools for complete systems design such as Xilinx-ISE, Xilinx Platform Studio (XPS) [1.16], Software Development Kit (SDK) [1.17], System Generator [1.18], PlanAhead Software [1.19], Chipscope Debugging tools [1.20] and Vivado-HLS [1.21].

#### 1.2.2. FPGA Architecture

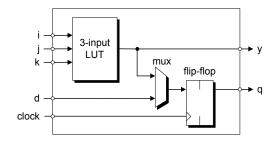

A generic FPGA architecture [1.22] can be classified into three parts: a programmable logic element, a programmable interconnection network and set of inputs/outputs. A logic element contains a combination of SRAM based Look-up-table (LUTs), multiplexers and flip-flops as shown in Fig. 1.2 [1.23, 1.24]. The functionality is implemented by writing the output in the LUT. Suppose we need to implement the function  $f(i, j, k) = \sum (0, 1, 2, 5, 7)$ . The table stored in the LUT will be 0, 1, 1, 0, 0, 1, 0, 1. The logic element can give a combinational or registered logic by using a flip flop. The output y is a combinational logic, while q is a registered output. The d input can be a direct output to y or q.

Figure 1.2: Logic element

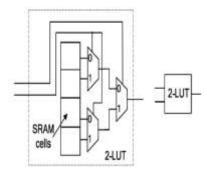

The digital functions in FPGAs are realized using LUTs, which are a series of flip-flops and multiplexers that store the output function. These elements are put together to form a configurable logic block (CLB) that contains a hierarchical structure of LUTs. Fig. 1.3 shows the internal organization of 2-input LUT which has four flip-flops and three two input multiplexers.

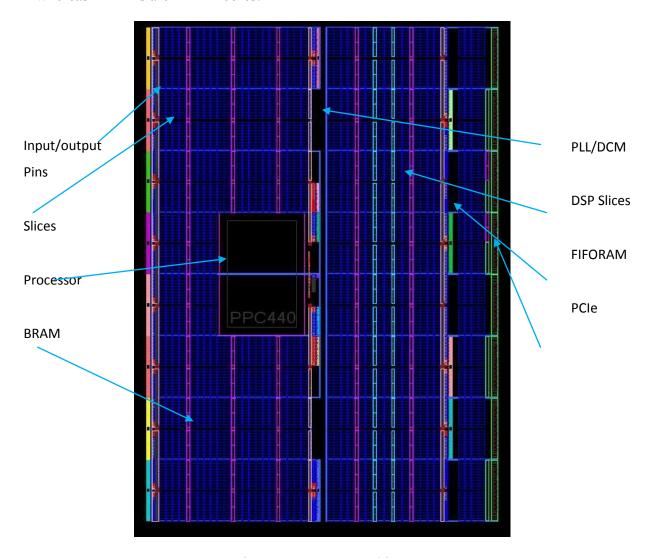

Figure 1.3: Look-Up-Table

The synthesized design in FPGA is mapped onto different logic blocks and connection is made by the interconnection network, which contains an array of switch matrix and wires. The wires are typically organized in wiring and routing channels. The channels provide wires of varying length such as short wire, medium length wire and global wires. Modern FPGAs contain a heterogeneous architecture consisting of fine grain and coarse grain components. The heterogeneous coarse grain components can be soft, firm or hard IP cores [1.25]. The soft-core IP is synthesizable RTL level designs which include embedded soft-core processors, bus controllers, memory controllers etc. that can be configured as per the requirement. Hard IPs are pre-placed components that can be used as black boxes and have an optimized layout. These include embedded hard core processors, hard macros such as ethernet, analog to digital converter, digital to analog converters, RF modules, digital clock manager, phase locked loop, high-speed transceivers etc. Firm IP cores are provided as parameterized RTL description, so that designers can optimize the cores for their specific design needs. Fig. 1.4 shows the organization of the Virtex-5 Xilinx FPGAs depicting LUT slices, processor, Block RAM,

FIFOs, Digital clock manager, etc. PowerPC processor is preplaced and is an example of hard IP whereas BRAMs are firm IP cores.

Figure 1.4: FPGA architecture

#### 1.2.3. System-On-Chip Design

The integrated circuits had become increasingly complex and expensive, which has led to the emergence of new designs and reuse methodologies and it is collectively referred to as SOC. The SOC platforms [1.25] are not only a chip, but a combination of IP cores, software support and integrated platform. These platforms usually include embedded processor, ASIC logics, analog circuitry, embedded memory etc. Their SW includes: operating system, compiler, simulator, firmware, driver, protocol stack, integrated development environment (debugger, linker) and application interface (C/C++, assembly). There are several benefits of integrating a large digital system into a single integrated circuit. These include lower cost per gate, lower power consumption, faster circuit operation, more reliable implementation, smaller physical size, and greater design security. The principal drawbacks of SOC design are associated with the design pressures imposed on today's engineers, such as time-to-market demands,

exponential fabrication cost, increased system complexity and increased verification requirements.

### 1.2.4. FPGA Based System-On-Chip Design

Common architectures and supporting technologies are called platform based design. These platforms offer the designer IP libraries and tools support, bus support, mixed signal blocks, software component (e.g. Driver, OS). Examples of such platforms are Xilinx EDK, Altera SOPC builder, programmable system on chip (PSoC) [1.26] etc. The FPGA based system SOC design offers the designer a HW and SW development platform. Each of these platforms are tightly integrated, allowing the designer to create the HW and develop its SW, hence facilitating rapid system prototyping. An HW definition of an application developed by the designer is usually known as user defined intellectual property (IP), which FPGA based SOC usually supports.

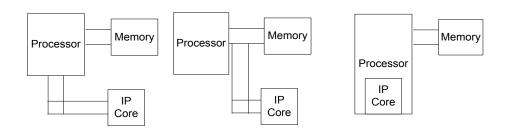

In configurable SOC based design, different techniques are used for interfacing the IP depending on the speed requirement [1.27]. Examples of interfaces are buses, peer-to peer link to the processor and modified processor data-path. Fig.1.5 shows the IP interfaced in three ways: loosely coupled, medium-coupled and tightly coupled. In case of loosely coupled system, IP can be interfaced with a low speed bus. Medium coupled IP are interfaced with high speed bus. It is also possible to change the datapath of the processor and define a new operation as an instruction in tightly coupled systems. Such tightly bound systems come in the class of application specific integrated processor (ASIP) and is a popular way of implementation of accelerators. Designing such ASIP, requires the complete new definition of software toolchains requiring a dedicated team for designing, coding and verification of the application.

- a) Loosely coupled IP

- (b) Medium coupled IP

- (c) Tightly coupled IP

Figure 1.5: Various IP interfacing techniques

Xilinx EDK design flow allows the development of user defined IP and generates its driver for usage in SW development in the SDK. The developed IP is wrapped around the bus wrapper

automatically which can communicate with the processor through slave registers, first-in-first-out (FIFO) memory or local memory. Medium coupling is allowed through the fast simplex link [1.28].

### 1.3. Introduction to Reconfigurable Computing Systems (RCS)

A common alias for FPGA based systems is reconfigurable computing systems. They can be defined as the study of computations involving reconfigurable devices, which includes architecture, algorithms and applications. They involve computation in space and time, using hardware that can adapt at the logic level to solve specific problems. Reconfiguration is the process of changing the behavior of the systems to execute various configurations. With the reprogrammable feature offered by FPGAs, it became possible to change the HW, giving rise to the emergence of the RC systems. This reconfiguration in FPGAs can be temporal or spatial which means the functionality can be changed by reconfiguring structure area with more than one functional block and scheduling in time. The reconfiguration of the device can be done statically or dynamically, allowing the design flow to be adaptable as per the requirement of the applications.

#### 1.3.1. Dynamic Partial Reconfigurable Systems (DPRS)

A static random access memory (SRAM) based FPGA as discussed in section 1.2.2 is a two layer device consisting of configuration memory layer and logic layer. The lower layer is the configuration memory layer in which the configuration data is stored. The upper layer called the logic layer consists of the logic blocks and interconnection that forms the system architecture.

After choosing the required HW along with specific processor (either hardcore or soft core processor) system configuration file is prepared that is used to program the SRAM cells. The loading of configuration can be done either statically or dynamically [1.7] and hence are known as reconfigurable computing systems (RCS). The static approach known as compile time reconfiguration works by inactivating the running systems and loading a new configuration file. In the dynamic case which is also known as run-time reconfiguration, the configuration is loaded while the rest of the system blocks are running. This allows configuring a selected part of the chip by using specialized hardware. Hence, dynamic RCS systems are also referred as partial dynamically reconfigurable systems and are created by defining partial reconfigurable region (PRR) using a floor-planning software such as Xilinx PlanAhead. The concept of partial reconfiguration allows multiple configurations to be swapped in and out of the hardware independently. The applications to be reconfigured at run-

time are known as partially reconfigurable modules and are statically bound to the PR region, allowing them to run only in the defined partially reconfigurable modules region. Fig. 1.6 shows one such PRR region and two partial reconfigurable module (PRM) named as *add* and *mult* bound to this region.

Figure 1.6: FPGA based system with one PR region with two PRM mapped

The PRM modules are compiled and partial bit files for each functional block configuration are moved to the memory available on the respective board such as compact flash, double data rate (DDR) or platform flash providing a database center for partial bit files. At run time, these files are loaded and executed by static scheduler, which calls the configuration in dependency order, stores the intermediate results and executes the complete application. The primary concern here is the total time taken starting from loading to executing the given configuration. Thus the idea of partial reconfiguration enables system flexibility in terms of providing more functionality to be performed in the same area by reducing the area and power requirement of the system. Runtime reconfiguration of programmable devices is the state of the art technology available, but is still not applied in the industrial applications due to lack of sophisticated and automated tools. To exploit the potentiality of RC systems, development of user friendly tools is required.

#### 1.3.2. Advantages of Partial Reconfiguration

The advantages of dynamic partial reconfiguration are as follows:

- i. Partial reconfiguration allows designing a self-adaptive and flexible system, where hardware changes can be rapidly migrated, depending on the applications.

- ii. Partial reconfiguration allows designing an intelligent system that manages reconfiguration in order to save power.

- iii. Partial reconfiguration enables hardware reuse that allows using more silicon than we pay for.

#### 1.4. Motivation for Current Research

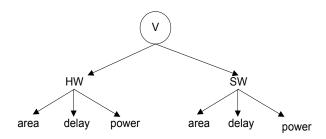

As described in the previous section, FPGAs can be used for both software and hardware design thereby offering a wide spectrum of choice of tradeoffs to the designer. The decision from a pure SW implementation to HW requires certain design parameters comparison based on performance, HW area, power consumption and suitable design flows for FPGAs. Further each layer from SW to HW, spans many optimization techniques, resulting in new dimensions of acceptable functional parameters. This research work has been inspired from such demand and comparative data interrogations from the designers.

The application which requires better performance can be partitioned into HW-SW or HW-HW parts [1.9]. For mapping such a candidate, two solutions are possible: 1) Migrating part of the design to HW and the remaining part to the SW, 2) Dividing the design into HW partitions by implementing and executing them sequentially as well as concurrently. HW-HW partitioning using partial reconfiguration has not been extensively tested on real hardware. Hence the objective of this thesis work is to achieve efficient HW-HW partitioning using static approach and partial reconfiguration flow and bring out the pros and cons of the proposed design flow.

Some of the high level synthesis tools such as Vivado-HLS convert a high level languages (HLL) specification like C/C++/SystemC etc. into HW automatically. But due to this, many of the functions normally consume more HW resources as compared to RTL design. In this scenario, the advantage of automation is nullified as most of the chip area is used. Using partial reconfiguration, more HW reusable functions may be divided into further small design. These functions can be executed temporally using partial reconfiguration concept.

In concise, we identify the following motivational gaps for the current work:

- Though HW-SW co-design flow is established, some of the practical design flows are not

offered by the present tools. These practical flows are achieved by design methodology

that can assist the designer.

- With the advent of high level synthesis tools like Vivado-HLS, the migration of SW to HW is now accelerated. These automated approaches have not been extensively explored for effectiveness in performance.

- The partial reconfiguration flow, has not been used for HW, HW partitioning problem, hence needs to be compared for its pros and cons.

#### 1.5. Problem Definition and Objectives

Many applications fail to achieve the required performance on the processor as pure SW execution. This problem is solved by migrating a certain part of the code to HW. During this migration the decision making task is: which part of the code to migrate. This answer can only be addressed after an initial implementation of the design has been done on the target device, through which execution profile of the application can be accumulated. This makes the life of the design cycle longer and complex. Hence, what we need is the exact design method that can guide the designer prior to implementation. Such methods requires a proposal of an algorithmic approach to generate design place solutions and guide the designer for area/delay trade-offs.

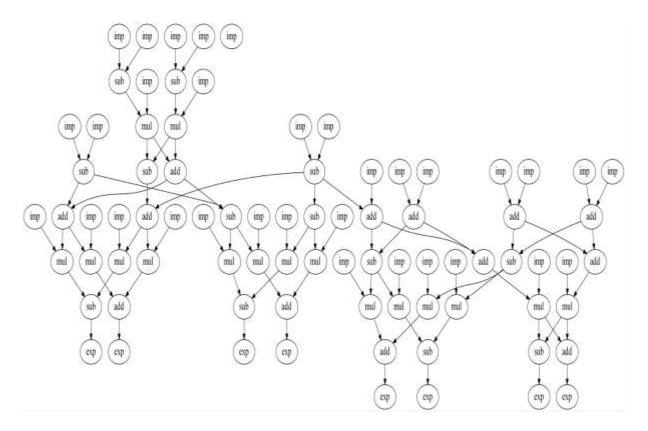

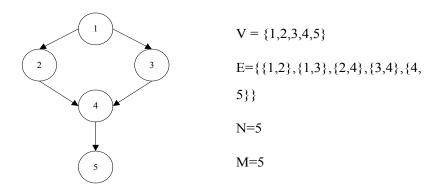

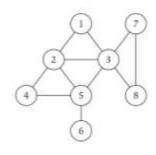

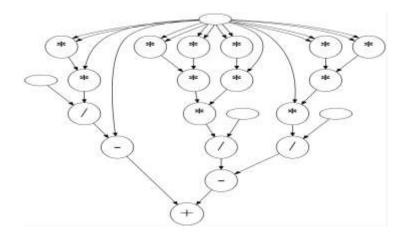

The specification of an application can be done in various ways such as C language, Matlab, finite state machines, dataflow graphs etc. A dataflow model of computation aims at capturing the data flow and its computations among the various operations. The computation part of any design can easily be defined in such a model. They can be used as input specification and can be easily generated, verified and comprehended. Hence these models are a good choice for examining the proposed algorithms in terms of their correctness and effectiveness. These algorithms demand proposal of efficient partitioning and scheduling of operations in correct order. Such algorithms aim at creation of coarse grain clusters that can be mapped as static or dynamic modules. These clusters should be created in such a way that overall the area-delay product improves.

For estimating the area required for a DFG or a C program, we need to generate its control flow graph. Without the HW generation, making this possible will allow the SW programmer to bypass the HW learning and quickly generate functional parameters.

Hence the objective set for this work is defined as:

- 1. Design and implementation of automated system design flow for applications defined in high level language with HW-SW co-design concept to design optimal systems.

- 2. Design and development of an algorithm for estimation of resources consumed by functions described as control flow graphs generated from compiler.

- 3. Given a dataflow and control flow graph specification, design and implement efficient algorithms to convert fine grain graphs to coarse grain graphs. Create such coarse level graph by finding reusable patterns in the specification.

4. Identification of functional blocks for efficient mapping using a partial reconfiguration approach and schedule the application to exploit the strength of a RC system.

## 1.6. Thesis Organization

This thesis is organized into six chapters. Chapter 1 presents the introduction to reconfigurable systems and motivation for the thesis work. Chapter 2 discusses the literature survey of system design methodology, partitioning of DFGs, high level synthesis and partial reconfiguration.

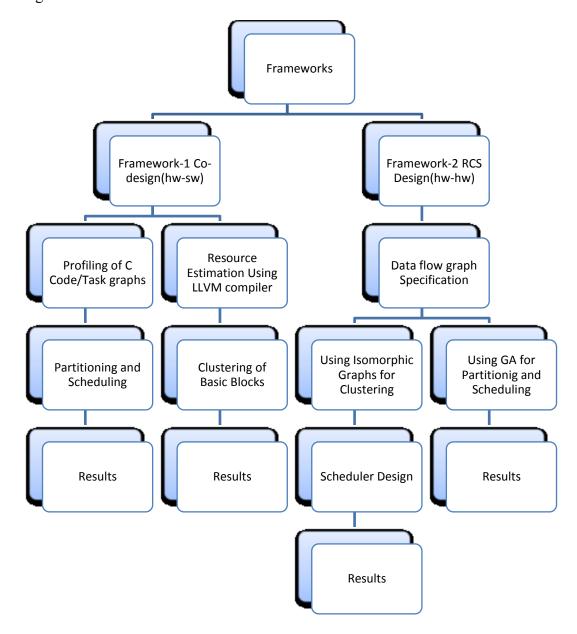

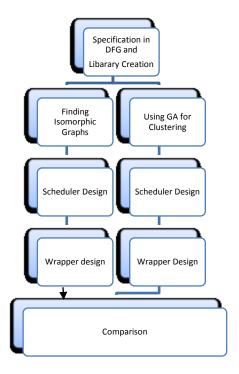

Figure 1.7: Organization of thesis work

Chapter 3 focuses on resource estimation of C/C++ programs and cluster creation. The work further demonstrates how clusters known as extended basic block can be created using an algorithmic approach. A framework for HW-SW co-design using genetic algorithm has been

proposed in chapter 4. Chapter 5 explains the partitioning problem and applies it for creating clusters to HW-HW design flow. Genetic Algorithm (GA) has been used for partitioning and scheduling of RC systems and is extensively covered in this thesis. It also highlights the process of dynamic partial reconfiguration and compares the results of the previous chapters. Chapter 6 gives a summary and draws conclusions on the basis of results obtained. It also presents the future work to be carried out with the existing platform. Fig. 1.7 shows the summary of work done and organization of thesis.

#### 1.7. Conclusion

In this chapter we have discussed the principles of FPGAs, system-on-chip, reconfigurable systems and partial reconfigurable systems. These emerging systems are allowing searching for various HW and SW implementations to maximize the performance while meeting the constraints. This has motivated out research work and inspired us to define the research objectives.

## REFERENCES

- 1.1 Peter Marwedel, Embedded system Design, Springer, Kluwer Academic Publishers, 2003. (chapter-1)

- 1.2 Peter Barry and Patrick Crowley, Modern Embedded System, Springer Publisher, 2012.(chapter-1)

- 1.3 Software Design Methods for Concurrent and Real-Time Systems. Hassan Gomaa, Addison-Wesley, 1993. (chapter-1)

- 1.4 Digital Signal Processors: Architecture, Programming and Applications, B. Venkataramani, M. Bhaskar, Tata McGraw-Hill Education, 2002.(chapter-6)

- 1.5 SOC W. Wolf, A Decade of Hardware/Software Co-Design, in Proc. of the 5th International Symposium on Multimedia Software Engineering (MSE), pp. 38–43, December, 2003.

- 1.6 R. A. Klein, A. Moona, Migrating software to hardware on fpgas, International conference on field programmable technology, pp. 217-224, December, 2004.

- 1.7 Cristophe Bobda, Introduction to Reconfigurable Computing: Architectures, Algorithms and Applications, Springer, 2007. (chapter-2)

- 1.8 Kuon, J. Rose, Measuring the gap between FPGAs and ASICs, IEEE transactions on computer-aided design of integrated circuits and systems, vol. 26, no. 2, February, 2007.

- 1.9 J. Straunstrup, W. Wolf, Hardware/Software Co-design Principles and Practices, Springer, Kluwer Academic Publishers, 1993. (chapter-4)

- 1.10 Patrick R. Schaumont, A practical introduction to hardware/software codesign, Springer international edition, 2011. (chapter-2)

- 1.11 Robert K. Dueck, Digital Design with CPLD Applications and VHDL, Delmar Cengage Learning, 2nd revised edition, July, 2004.

- 1.12 http://www.xilinx.com/,last accessed on 15 July 2016.

- 1.13 https://www.altera.com/, last accessed on 15 July 2016.

- 1.14 http://www.latticesemi.com/, last accessed on 15 July 2016.

- 1.15 http://www.microsemi.com/products/fpga-soc/fpga-and-soc, last accessed on 15 July 2016.

- 1.16 http://www.xilinx.com/products/design-tools/xps.html, last accessed on 15 July 2016.

- 1.17 http://www.xilinx.com/support/documentation/sw\_manuals/xilinx2015\_1/SDK\_Doc/ind ex.html, last accessed on 15 July 2016.

- 1.18 http://www.xilinx.com/products/design-tools/vivado/integration/sysgen.html, last accessed on 15 July 2016.

- 1.19 http://www.xilinx.com/products/design-tools/planahead.html, last accessed on 15 July 2016.

- 1.20 http://www.xilinx.com/itp/xilinx10/isehelp/ise\_c\_process\_analyze\_design\_using\_chipsc ope.htm, last accessed on 15 July 2016.

- 1.21 http://www.xilinx.com/products/design-tools/vivado.html, last accessed on 15 July 2016.

- 1.22 Wayne Wolf, FPGA based System Design, Prentice hall India, 2004. (chapter-3)

- 1.23 http://www.xilinx.com/support/documentation/data\_sheets/3000.pdf, last accessed on 15 July 2016.

- 1.24 Clark N. Taylor, FPGA Implementation Details, 2008. (http://ece320web.groups.et.byu.net/CourseNotes/FPGA.pdf), last accessed on 15 July 2016.

- 1.25 Dimitris Gizopoulos, A. Paschalis, Yervant Zorian, Embedded Processor-Based Self-Test, Springer, Kluwer, 2004. (chapter-4)

- 1.26 http://www.cypress.com/products/32-bit-arm-cortex-m-psoc. , last accessed on 15 July 2016.

- 1.27 System-on-a-Programmable-Chip Development Platforms in the Classroom, users.ece.gatech.edu/~hamblen/papers/SOC top.pdf., last accessed on 15 July 2016.

- 1.28 http://www.xilinx.com/products/intellectual-property/fsl.html.

# Chapter 2

# **Literature Survey**

Reconfigurable systems are versatile platforms which allow the designer to conceive any kind of SW or HW optimizations and methodologies. It allows achieving the desired system performance by different approaches. These systems contain a processor, on which the SW can be executed and HW fabric on which any accelerator can be designed. Techniques like fixed point vs. floating point arithmetic, usage of simple vs. complex algorithm, language selection etc. allow bringing out the tradeoff in SW implementation. Similarly optimization in HW implementation can be achieved by various techniques like pipelining vs. parallelism, static vs. dynamic scheduling etc. The design of HW accelerators on RCS requires that the resources available on the chip are effectively used to deliver the best performance.

To gain an elaborate insight in the research progress made in the field of chosen problem statement and identify the existing gaps we undertook an extensive literature survey. This enabled us to highlight the problems to be focused on, formalize the solutions and explore the strategy to be adopted to achieve the objectives of the proposed work. This chapter is divided into four sections which cover the literature survey for HW-SW frameworks, high level synthesis, partitioning/scheduling, and partial reconfiguration process.

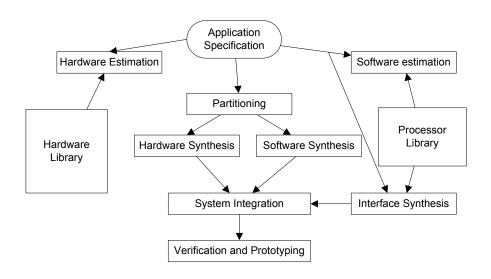

## 2.1. Frameworks and Design Methodology

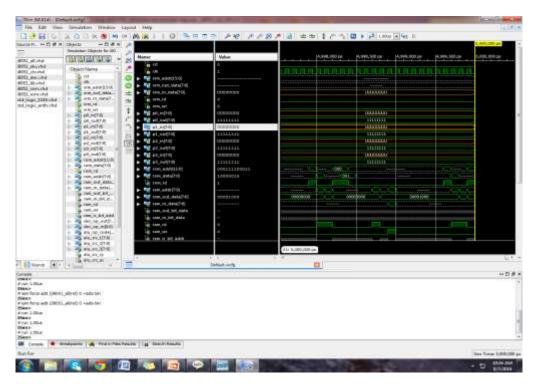

The initial framework for HW-SW partitioning and mapping using manual time estimation and manual synthesis was proposed in [2.1], which demonstrates a complete working example of digital camera using a C specification. This design shows an image compression implementation on a soft core based 8051 complied on FPGAs. A co-simulation testing setup having a cross-compiler and HDL simulator was used for verification. This benchmark was downloaded and simulated in Xilinx ISIM simulator as shown in Fig. 2.1 for verifying the way in which co-simulation is performed. The 8051 VHDL model files and the C code stored in ROM VHDL model is shown in Fig. 2.1. The simulation setup includes the cross compiler and its conversion to a ROM image. The execution in the simulator was possible without a HW implementation allowing the co-simulation to accumulate the performance results.

Figure 2.1: Co-simulation of digital camera case study in Xilinx ISIM

The timing constraint kept for the design was given as 1 second, since holding a camera for a prolonged time is frustrating to the user. Hence to achieve the required performance a codesign methodology was adopted and four implementations were written for achieving the target of 1 second. Implementation 1 is pure SW execution and fails to achieve the required time. In implementation 2, one of the modules is randomly chosen and is migrated to HW. In implementation 3 discrete cosine transform (DCT) is implemented in HW and 4 is an implementation of using fixed point arithmetic in DCT block. The Table 2.1 shows the time comparison, which is coming down from 9.1 seconds to 0.099 seconds.

Table 2.1: Three parameters for Digital Camera Case Study on 8051 [Source: 2.1]

|                      | Implementation 2 | Implementation 3 | Implementation 4 |

|----------------------|------------------|------------------|------------------|

| Performance (second) | 9.1              | 1.5              | 0.099            |

| Power (watt)         | 0.033            | 0.033            | 0.040            |

| Size (gate)          | 98,000           | 90,000           | 128,000          |

| Energy (joule)       | 0.30             | 0.050            | 0.0040           |

The shortcomings of this design flow were manual partitioning, manual estimation of time and manual conversion of C to HDL, making it time consuming and resulting in a longer design cycle. These guidelines can be adopted only by an experienced designer who knows an indepth understanding of the platform.

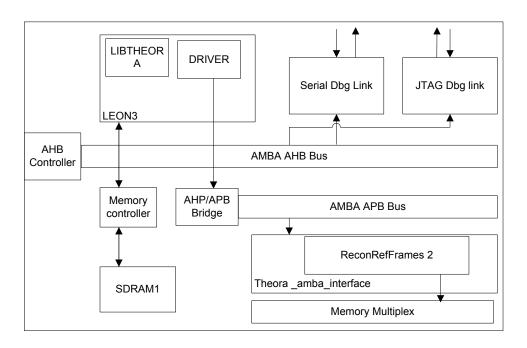

Similar work was done in Google summer of code 2006 [2.2] (a contest organized by Google) on the Leon3 platform, which is from Aeroflex Gaislor company [2.3]. The design flow uses

operating system based design and device driver for migrated IP to HW. This work shows the time profiling on general purpose computer for media application and uses the results for profiling process. The conclusion was that the function reconrefframes waste approximately 60% of CPU-time and should be migrated to HW. The flow does not use algorithmic approach and a C to HDL compiler to compute the resources consumed. Most of the work in this domain lacks the demonstration of time estimation on an embedded target, which can give better estimation results. The structural design is shown in Fig. 2.2 with Theora codec interfaced to APB bus. This work gave an idea of the time profiling on the host and demonstrated the difference in results.

The popularly available tools for co-design are COSYMA, Lycos, Polis, Chinook, Akka, CASTLE/SIR, CodeSign, CoWare and Symphony, The Ode System, COOL, PeaCE [2.4]. Most of these tools are either proposed or not available on-line. The only commercial tool among them is CoWare and its results have not been reported in literature. The common problems encountered in these tools are:

- i. ANSI C language is not a standard input in most of them.

- ii. The design space exploration for a given design requires manual intervention.

- iii. An efficient conversion of SW to HW automatically is missing.