High Performance Binary, Logarithmic, and BCD Multiplier Architectures

#### THESIS

Submitted in partial fulfillment

of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

by

Syed Ershad Ahmed

ID No. 2009PHXF448H

Under the Supervision of

Prof. M. B. Srinivas

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE - PILANI

December, 2017

#### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

### CERTIFICATE

This is to certify that the thesis entitled <u>High Performance Binary</u>, Logarithmic, and BCD <u>Multiplier Architectures</u> and submitted by <u>Syed Ershad Ahmed</u> ID No <u>2009PHXF448H</u> for award of Ph.D. of the Institute embodies original work done by him under my supervision.

Signature of the Supervisor Dr. M. B. SRINIVAS Professor Date:

## Acknowledgements

Accomplishment of this doctoral thesis was not possible without the support of several people directly and indirectly. It gives me great pleasure to express my deep sense of gratitude to Prof. M.B.Srinivas, Professor, Department of Electrical Engineering, BITS-Pilani, Hyderabad Campus for his invaluable guidance, cooperation and keen interest during my research work. I am indeed fortunate to work under his supervision.

I am thankful to Prof. Souvik Bhattacharyya, Vice-Chancellor and Prof. G.Sundar, Director, BITS-Pilani, Hyderabad Campus for providing a research environment to enhance my research interest and commitment.

I wish to enlist my deep sense of gratitude to Prof. Sanket Goel, Head, Electrical Engineering Department, BITS-Pilani, Hyderabad Campus for providing me full support to carry out this research work. I am extremely thankful to all the faculty, PhD scholars and staff of Electrical Engineering Department.

I take this opportunity to thank my doctoral advising committee members, Prof. Prabhakar Rao, and Prof. Subhendu Kumar Sahoo for providing suggestions during the entire thesis and sparing their valuable time in providing useful comments for my draft thesis.

It's my pleasure to thank my parents and wife who stood with me during tough times with all their valuable and encouraging words.

## Abstract

Digital multipliers form an important part of digital arithmetic circuits. Important parameters that characterize these multipliers are their precision and those related to their implementations such as area, critical path delay, and power consumption. While certain applications demand high precision, others would require optimality in terms of die-area, latency of operation and power consumed. Thus the present thesis focuses on developing novel multiplier architectures (binary, logarithmic and BCD) that lead to either improved precision or result in better implementation.

The first contribution of this thesis is the development of a reconfigurable, two-dimensional (2D) bypass multiplier architecture that is based on dynamic bypassing of partial products. The bypass elements incorporated into the multiplier reduce the power consumption by eliminating redundant signal transitions. The reconfigurable architecture offers a good trade-off between area, delay and power dissipation since it uses the same multiplier for performing one *N* or two N/2 multiplications.

As the modern computing systems become increasingly embedded and portable, a growing set of applications in media processing (graphics, audio, video, and image) has evolved. Many of these applications, however, possess an inherent quality of error resilience. For example, it is a known feature of image processing that a range of image resolutions/sharpness is acceptable depending on the nature of the application. Thus arithmetic units (digital multipliers in present case), that are not very precise but return an approximate value, can be utilized in such applications. Such units, it may be anticipated, may result in area savings while also resulting in reduced power consumption. The second contribution of this thesis is the development of a novel approximate binary multiplier architecture that results in improved performance in terms

of area, delay and power compared to existing architectures while the trade-off in accuracy is only marginal.

Further, in recent years, logarithmic number system has been increasingly used as an alternative to the binary number system as it converts multiplication to addition resulting in simplified hardware. While logarithmic number system cannot be compared with that of binary in terms of precision, usage of it in arithmetic operations such as multiplication certainly results in reduced area and power consumption and thus is useful in applications where precise results are not required. The third contribution of this thesis is the development of an efficient logarithmic multiplier architecture that significantly reduces the area and power consumption of the hardware while sacrificing the accuracy only marginally.

Extensive analysis of the hardware requirement of both the multipliers (approximate binary and logarithmic) has been carried out, initially using unit gate modeling, and later on using the synthesis tool. Furthermore, to quantify the advantage of the proposed architectures, both have been used in an image sharpening algorithm (that employs extensive multiplication) and benchmarked against certain standard and well known image processing applications such as Lena, Cameraman and Pirate.

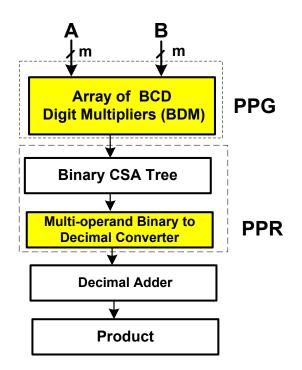

Finally, while binary arithmetic is all pervasive, BCD (decimal) arithmetic is preferred in applications such as financial, scientific and commercial etc. owing to its comparatively high precision. The fourth contribution of this thesis is the development of a generalized design approach and architectural framework for decimal multiplication. In this approach, unlike the existing decimal architectures, the decimal partial product generation is achieved in parallel using fast and area efficient blocks, while the partial product reduction is achieved using hybrid multi-operand binary to decimal converters. A comprehensive analysis of the synthesis results carried out on IEEE-compliant 16-digit decimal multiplier indicates the superiority of the proposed architecture over the existing ones.

## Contents

| Al | bstrac  |                                                 | i  |

|----|---------|-------------------------------------------------|----|

| Co | ontent  | 5                                               | 1  |

| Li | st of l | igures                                          | 6  |

| Li | st of [ | ables                                           | 11 |

| No | omeno   | ature                                           | 13 |

| 1  | Intr    | duction                                         | 16 |

|    | 1.1     | Background                                      | 16 |

|    | 1.2     | Objectives of the Thesis                        | 17 |

|    | 1.3     | Steps involved in carrying out present research | 18 |

|    |         | 1.3.1 High Level Modeling                       | 18 |

|    |         | 1.3.2 Unit Gate Level Modeling                  | 19 |

|    |         | 1.3.3 CAD tools used in the ASIC implementation | 20 |

|    |         | 1.3.3.1 Cadence Simulator                       | 20 |

|    |         | 1.3.3.2 Cadence RTL Compiler                    | 20 |

|    | 1.4     | Organization of the Thesis                      | 20 |

| 2  | Lite    | ature Review                                    | 21 |

|    | 2.1     | Introduction                                    | 21 |

|    | 2.2     | Classification of Multiplier Architectures      | 21 |

|    | 2.3     | Binary Multipliers                              | 21 |

| 2.4 | Braun  | Multiplier  |                                                       | 23 |

|-----|--------|-------------|-------------------------------------------------------|----|

|     | 2.4.1  | Partial Pa  | roduct Generation (PPG)                               | 24 |

|     | 2.4.2  | Partial P   | roduct Reduction (PPR)                                | 24 |

|     |        | 2.4.2.1     | Binary Carry Save (CSA) Adders                        | 25 |

|     | 2.4.3  | Wallace     | Reduction Tree                                        | 28 |

|     | 2.4.4  | Final Ad    | der                                                   | 30 |

|     |        | 2.4.4.1     | Ripple Carry Adder                                    | 30 |

|     |        | 2.4.4.2     | Carry Look-ahead Adder (CLA)                          | 31 |

|     |        | 2.4.4.3     | Carry Look-ahead (CLA) based Parallel Prefix Adder    | 32 |

| 2.5 | Low P  | ower Tech   | niques in Binary Multiplier Design                    | 34 |

|     | 2.5.1  | Dynamic     | Power Dissipation in CMOS based Circuits              | 35 |

|     | 2.5.2  | Power C     | onsumption in Parallel Multipliers                    | 35 |

|     | 2.5.3  | Reconfig    | urable Binary Multiplier                              | 36 |

|     | 2.5.4  | A Review    | w of Bypass Multiplier Architectures                  | 36 |

|     |        | 2.5.4.1     | Row-Bypass Scheme                                     | 36 |

|     |        | 2.5.4.2     | Column-Bypass Scheme                                  | 38 |

|     |        | 2.5.4.3     | Two-Dimensional Bypass Scheme                         | 39 |

| 2.6 | A Rev  | iew of Rec  | cursive Binary Multipliers                            | 40 |

|     | 2.6.1  | Mathema     | atical Analysis of Recursive Multiplier               | 40 |

|     | 2.6.2  | Truncatio   | on Schemes for Binary Multipliers                     | 41 |

|     |        | 2.6.2.1     | Truncation Schemes for Array Multipliers              | 42 |

|     |        | 2.6.2.2     | Truncation Schemes for the Recursive Multiplier       | 42 |

| 2.7 | Multip | liers based | d on Logarithmic Number System                        | 43 |

|     | 2.7.1  | Mathema     | atical Analysis of MA Based Multiplier                | 44 |

|     | 2.7.2  | Hardwar     | e Architectures                                       | 46 |

| 2.8 | Decim  | al Multipl  | ication                                               | 47 |

|     | 2.8.1  | 'Digit-by   | -Digit' Multiplier                                    | 48 |

|     | 2.8.2  | A Review    | w of Partial Product Generation and Reduction Schemes | 49 |

|   |      |          | 2.8.2.1     | Partial Product Generation (Binary Product to BCD conver-  |    |

|---|------|----------|-------------|------------------------------------------------------------|----|

|   |      |          |             | sion)                                                      | 49 |

|   |      |          | 2.8.2.2     | Partial Product Reduction                                  | 51 |

|   | 2.9  | Conclu   | usions      |                                                            | 53 |

| 3 | An l | Efficien | t Reconfig  | urable Binary Multiplier with 2-Dimensional bypassing      | 54 |

|   | 3.1  | Introdu  | uction      |                                                            | 54 |

|   | 3.2  | Propos   | sed Reconf  | igurable Binary Multiplier Architecture                    | 55 |

|   |      | 3.2.1    | Partial Pr  | roduct Arrangement                                         | 56 |

|   |      |          | 3.2.1.1     | Configuration Mode 1 (CM1):                                | 56 |

|   |      |          | 3.2.1.2     | Configuration Mode 0 (CM0) :                               | 57 |

|   |      | 3.2.2    | Partial Pr  | roduct Reduction using 2-Dimensional Bypass Cells          | 57 |

|   |      |          | 3.2.2.1     | Reconfigurable Two-Dimensional Bypass Cell (RTDBC)         | 60 |

|   |      |          | 3.2.2.2     | Reconfigurable Row Bypass Cell (RRBC)                      | 61 |

|   |      | 3.2.3    | Reconfig    | urable Ladner-Fisher Prefix Adder                          | 62 |

|   | 3.3  | Simula   | ation and S | ynthesis                                                   | 64 |

|   | 3.4  | Conclu   | usions      |                                                            | 67 |

| 4 | An l | Improve  | ed Fixed-V  | Vidth Recursive Binary Multiplier                          | 69 |

|   | 4.1  | Introdu  | uction      |                                                            | 69 |

|   | 4.2  | A New    | Approach    | n to Error Correction in Fixed-Width Recursive Multipliers | 70 |

|   |      | 4.2.1    | Error An    | alysis for the proposed correction function                | 73 |

|   |      |          | 4.2.1.1     | Hardware Implementation of the Proposed Fixed-Width Re-    |    |

|   |      |          |             | cursive Multiplier                                         | 74 |

|   | 4.3  | Result   | s           |                                                            | 76 |

|   |      | 4.3.1    | Error An    | alysis                                                     | 76 |

|   |      | 4.3.2    | Area and    | I Delay Comparison of Various Multipliers using Unit Gate  |    |

|   |      |          | Analysis    |                                                            | 78 |

|   |      | 4.3.3    | Hardwar     | e Synthesis Results                                        | 79 |

|   | 4.4  | Benchmarking Various Multiplication Schemes-Application to Image process-  |   |

|---|------|----------------------------------------------------------------------------|---|

|   |      | ing                                                                        | 0 |

|   |      | 4.4.1 Image Sharpening Algorithm                                           | 1 |

|   | 4.5  | Conclusions                                                                | 4 |

| 5 | An l | Iterative Logarithmic Multiplier with Improved Precision 8                 | 6 |

|   | 5.1  | Introduction                                                               | 6 |

|   | 5.2  | Proposed Approach                                                          | 7 |

|   |      | 5.2.1 Mathematical Analysis of the Proposed Scheme                         | 7 |

|   |      | 5.2.2 A New Approach to the Approximation of Logarithmic Multiplier 8      | 8 |

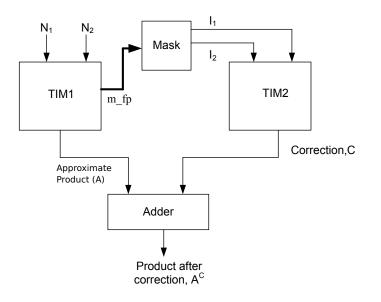

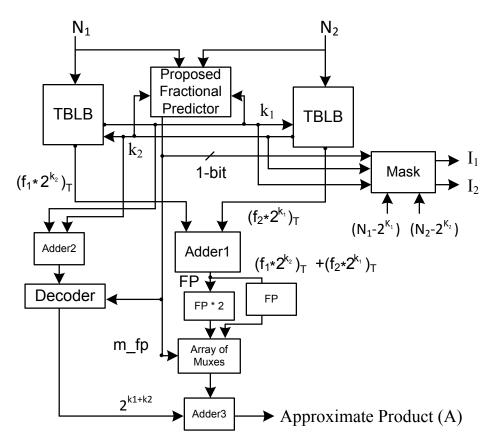

|   |      | 5.2.3 Truncated Iterative Multiplier (TIM) Hardware Implementation 92      | 3 |

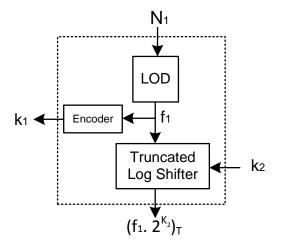

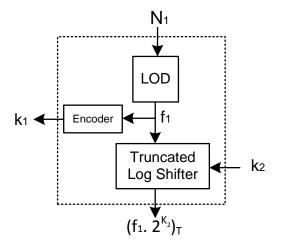

|   |      | 5.2.3.1 Truncated Basic Logarithmic Block (TBLB)                           | 4 |

|   |      | 5.2.3.2 Modified Fractional Predictor (MFP)                                | 4 |

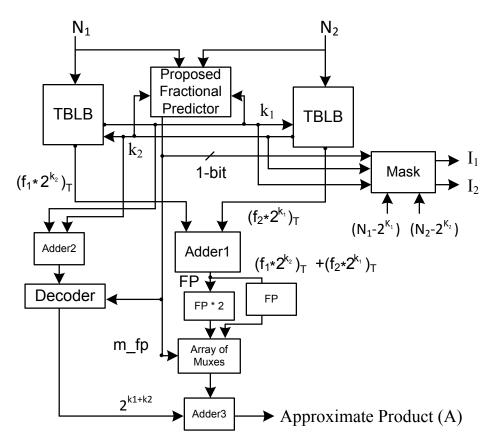

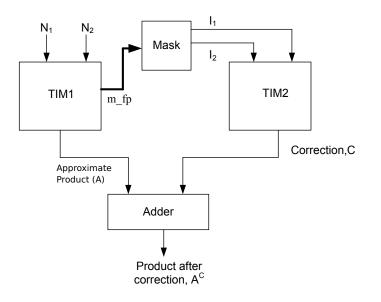

|   |      | 5.2.4 TIM Hardware for two Iterations                                      | 6 |

|   | 5.3  | Error Analysis                                                             | 7 |

|   |      | 5.3.1 Area and Delay Comparison of Various Multipliers using Unit Gate     |   |

|   |      | Level Modeling                                                             | 9 |

|   |      | 5.3.2 Synthesis Results of Various Multipliers                             | 3 |

|   | 5.4  | Benchmarking Various Multiplication Schemes-Application to Image process-  |   |

|   |      | ing                                                                        | 4 |

|   |      | 5.4.1 Image Sharpening Algorithm                                           | 4 |

|   | 5.5  | Conclusions                                                                | 8 |

| 6 | An l | Improved 'Digit-by-Digit' Decimal Multiplier 10                            | 9 |

|   | 6.1  | Introduction                                                               | 9 |

|   | 6.2  | A New Partial Product Generation Scheme in 'Digit-by-Digit' Multiplier 110 | 0 |

|   |      | 6.2.1 High Performance Partial Product Binary to Decimal (PPBD) Con-       |   |

|   |      | verter                                                                     | 0 |

|   |      | 6.2.2 Low Area Partial Product Binary to Decimal Converter (LAPPBD) 112    | 3 |

|   | 6.3  | Partial Product Reduction (PPR) in 'Digit-by-Digit' Multiplier             | 4 |

| Re | eferen            | ces     |            |                                                          | 133        |

|----|-------------------|---------|------------|----------------------------------------------------------|------------|

|    | /.1               | Tuture  | WOIK .     |                                                          | . 132      |

| /  | <b>Con</b><br>7.1 |         |            | ure Work                                                 | <b>131</b> |

| 7  | Con               | alucion | and Fut    | wa Work                                                  | 121        |

|    | 6.5               | Conclu  | usions     |                                                          | . 129      |

|    |                   |         | 6.4.2.3    | Synthesis Results of 16*16 'Digit-by-Digit' Multiplier   | . 127      |

|    |                   |         | 6.4.2.2    | Partial Product Reduction (PPR)                          | . 125      |

|    |                   |         | 6.4.2.1    | Partial Product Generation (PPG)                         | . 124      |

|    |                   | 6.4.2   | Synthesi   | s based Comparison                                       | . 123      |

|    |                   | 6.4.1   | Area and   | Delay Comparison using Unit Gate based Modeling          | . 121      |

|    | 6.4               | Result  | s and Disc | cussion                                                  | . 121      |

|    |                   | 6.3.2   | Algorith   | m for Hybrid Multi-operand Binary to Decimal Converter . | . 118      |

|    |                   | 6.3.1   | Impleme    | entation of 16*16 'Digit-by-Digit' Multiplier            | . 115      |

# List of Figures

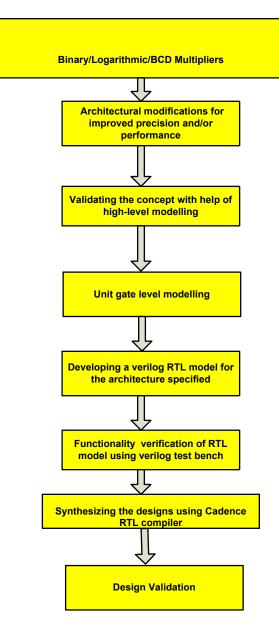

| 1.1  | Research Flow chart                                                             | 19 |

|------|---------------------------------------------------------------------------------|----|

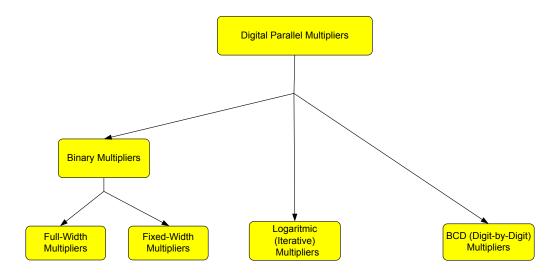

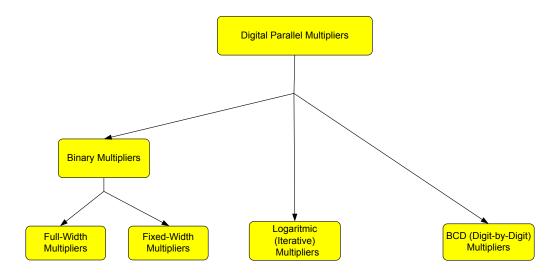

| 2.1  | Classification of digital multiplier architectures based on number system       | 22 |

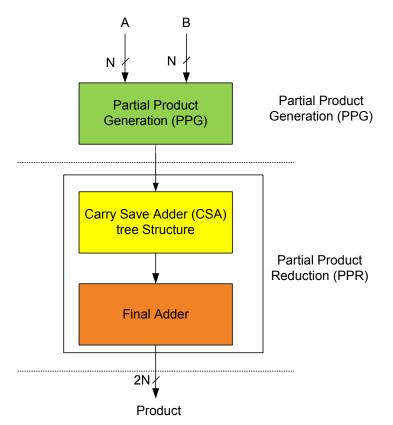

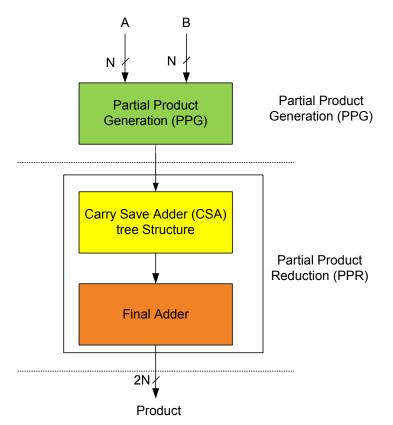

| 2.2  | A general binary multiplication structure                                       | 23 |

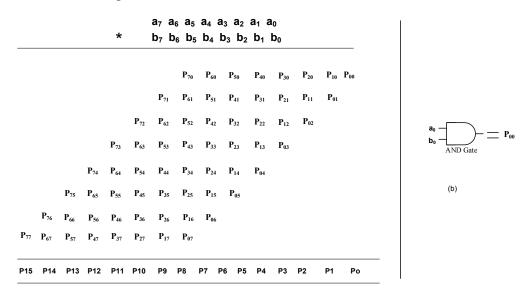

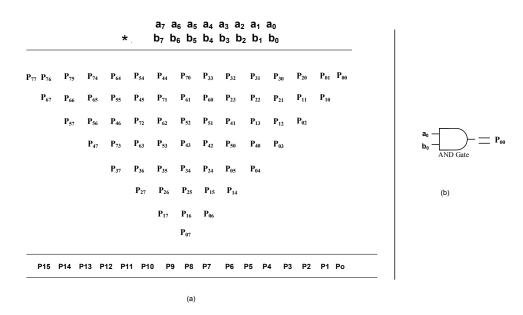

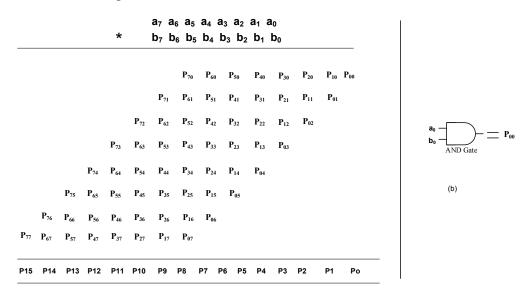

| 2.3  | (a) Partial product matrix representation in a 8*8 Braun multiplier (b) Partial |    |

|      | product computed using an AND gate                                              | 24 |

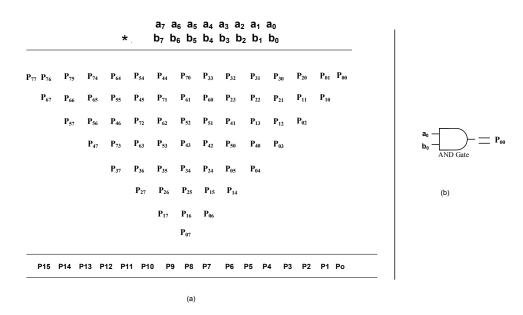

| 2.4  | (a) Alternate representation of partial products in 8*8 Braun array multiplier  |    |

|      | (b) Partial product computed using an AND gate                                  | 25 |

| 2.5  | Carry- free operation using full adders                                         | 26 |

| 2.6  | (a) Logic circuit of half adder (b) Half adder cell notation (c) Computation of |    |

|      | Sum and Carry-out using dot notation in a half adder                            | 26 |

| 2.7  | (a) Logic circuit of full adder (b) Full adder cell notation (c) Computation of |    |

|      | Sum and Carry-out using dot notation in a full adder                            | 27 |

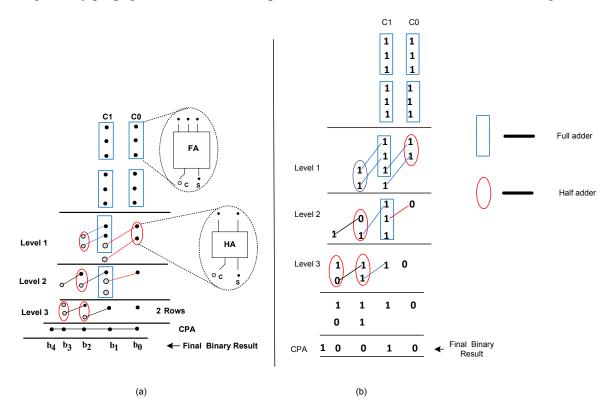

| 2.8  | (a) Partial product reduction using CSA dot notation (b) A numerical example    |    |

|      | related to partial product reduction                                            | 28 |

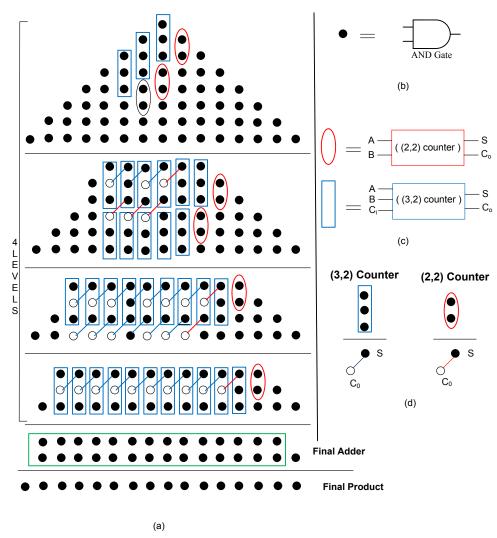

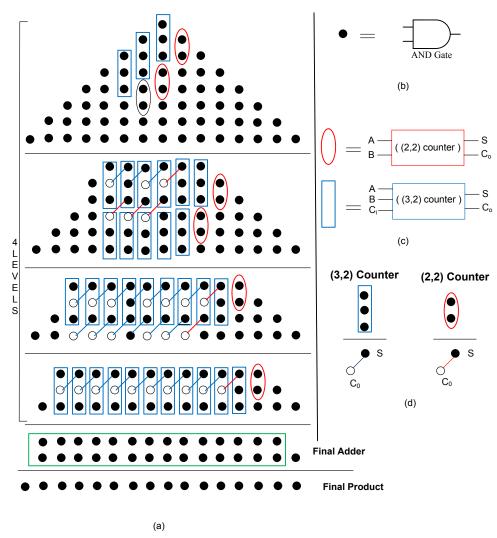

| 2.9  | (a) Wallace tree partial product reduction structure using 3:2 and 2:2 counters |    |

|      | (b) Partial product computed using an AND gate (c) Representation of 3:2 and    |    |

|      | 2:2 counters (d) Computation of Sum and Carry-out using dot notation in a full  |    |

|      | and half adder circuits                                                         | 29 |

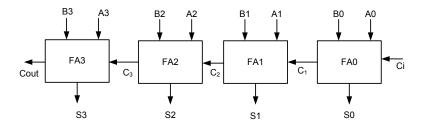

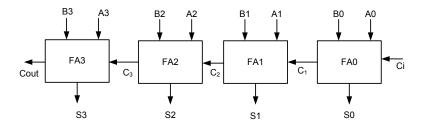

| 2.10 | 4-bit Ripple Carry Adder                                                        | 30 |

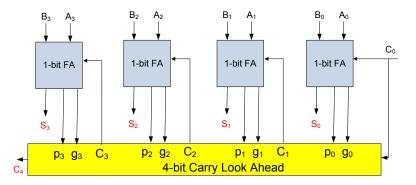

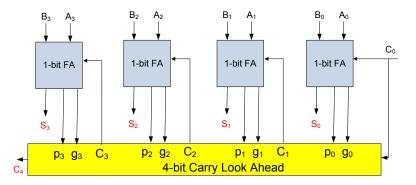

| 2.11 | 4-bit Carry Look-ahead adder                                                    | 32 |

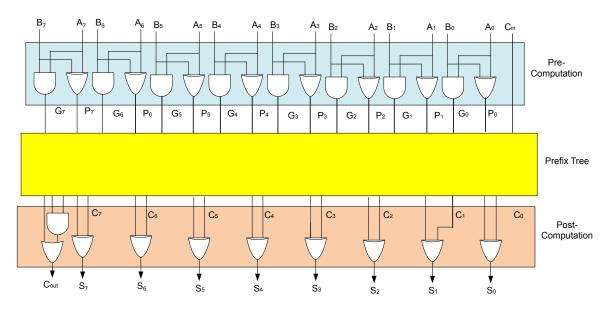

| 2.12 | CLA based 8-bit parallel-prefix structure                                       | 33 |

| 2.13 | CLA based 8-bit Kogge-Stone prefix adder                                        | 34 |

| 2.14 | (a) An example of 4*4 array multiplication (b) Schematic diagram of 4*4 Braun |    |

|------|-------------------------------------------------------------------------------|----|

|      | multiplier                                                                    | 37 |

| 2.15 | Schematic diagram of a 4*4 Braun multiplier using row-bypassing technique .   | 38 |

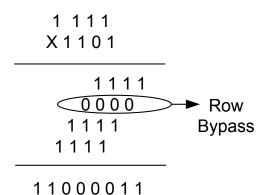

| 2.16 | Numerical example of row-bypass scheme for 4*4 multiplier                     | 38 |

| 2.17 | Schematic diagram of a 4*4 Braun multiplier with column-bypassing scheme .    | 39 |

| 2.18 | Schematic diagram of a 4*4 Braun multiplier with two-dimensional-bypassing    |    |

|      | scheme                                                                        | 40 |

| 2.19 | Schematic diagram of the original recursive multiplication scheme             | 42 |

| 2.20 | Sub-multipliers in a recursive multipliers                                    | 43 |

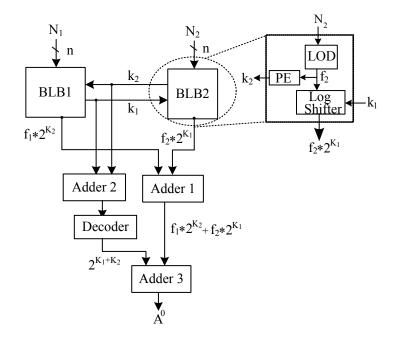

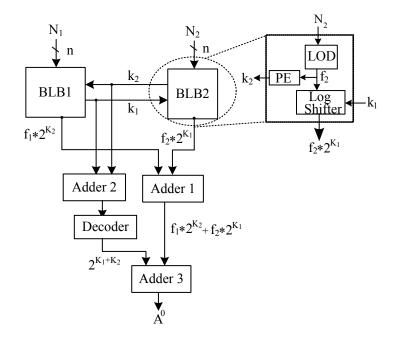

| 2.21 | Functional diagram of Babic Iterative Multiplier (BIM)                        | 46 |

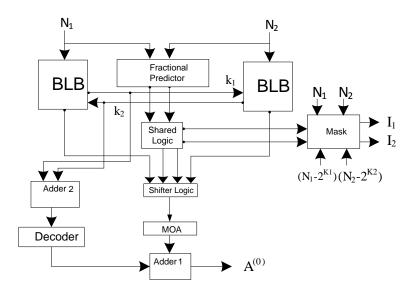

| 2.22 | Functional diagram of truncated error correction (TEC) Scheme                 | 47 |

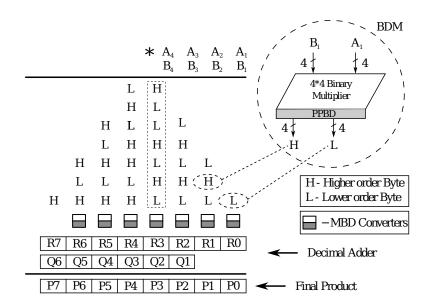

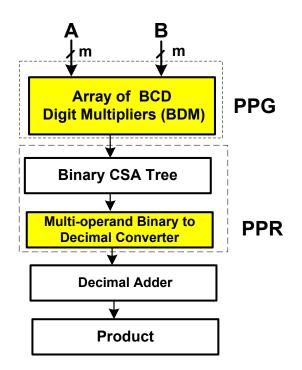

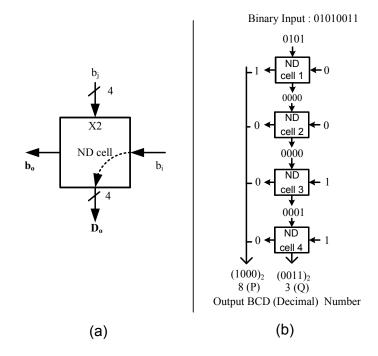

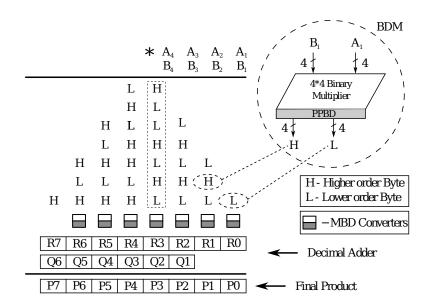

| 2.23 | A top-level architecture of 'digit-by-digit' multiplication                   | 48 |

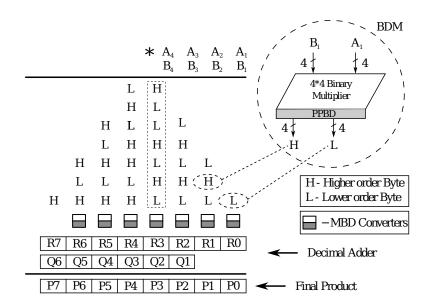

| 2.24 | Example of 4*4 'digit-by-digit' multiplication using BDMs                     | 49 |

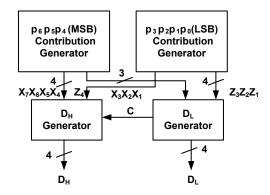

| 2.25 | Block diagram of 'three-four split' binary to BCD converter                   | 50 |

| 2.26 | Block diagram of 'four-three split' binary to BCD converter                   | 51 |

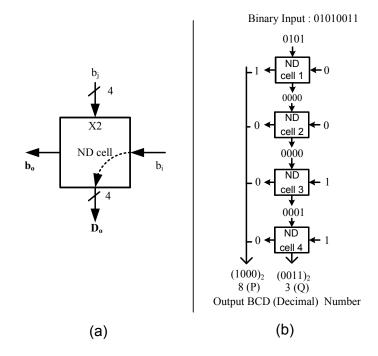

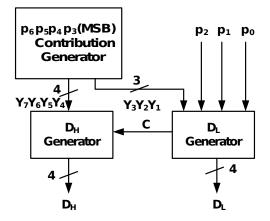

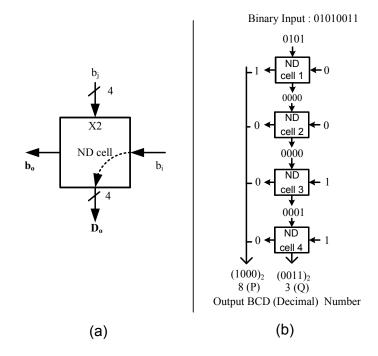

| 2.27 | (a) Compact notation of Nicoud cell (b) Linear array of Nicoud cells to form  |    |

|      | Dadda multi-operand BD converter                                              | 52 |

| 3.1  | Block diagram of proposed reconfigurable binary multiplier                    | 56 |

| 3.2  | Partial product matrix in configuration mode 1                                | 57 |

| 3.3  | Partial product matrix in configuration mode 0                                | 58 |

| 3.4  | (a) Proposed reconfigurable multiplier architecture with bypass computation   |    |

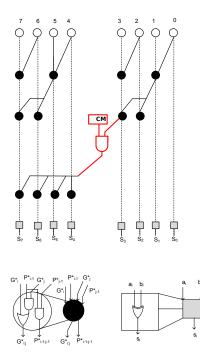

|      | cells (b) Reconfigurable row and column bypass cells with mode bit, CM        | 59 |

| 3.5  | A section of the proposed reconfigurable multiplier                           | 60 |

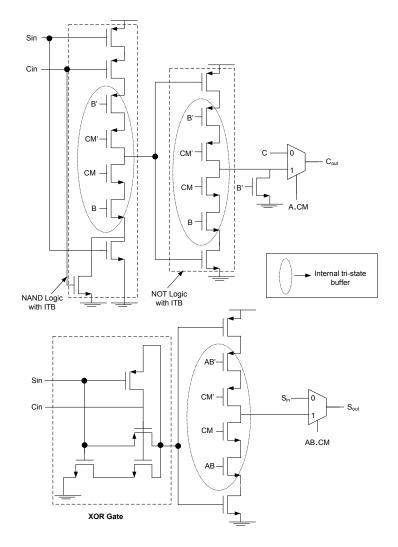

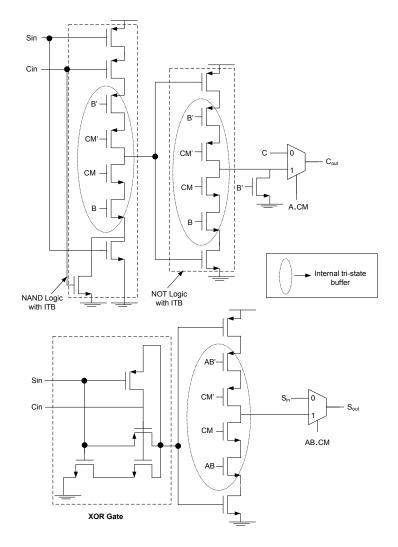

| 3.6  | Logic schematic of RTDBC                                                      | 62 |

| 3.7  | Logic schematic of RRBC                                                       | 63 |

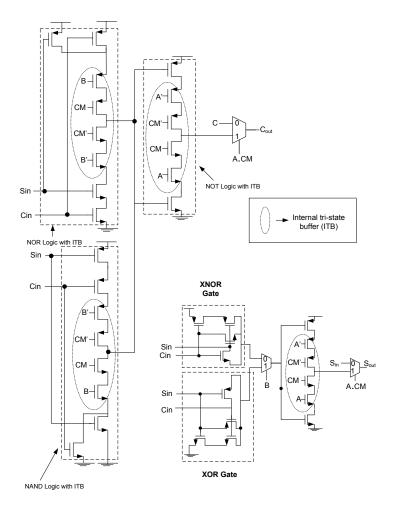

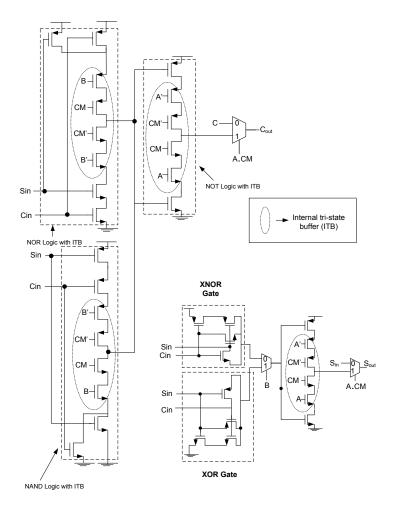

| 3.8  | A reconfigurable 8-bit Ladner-Fisher prefix adder                             | 64 |

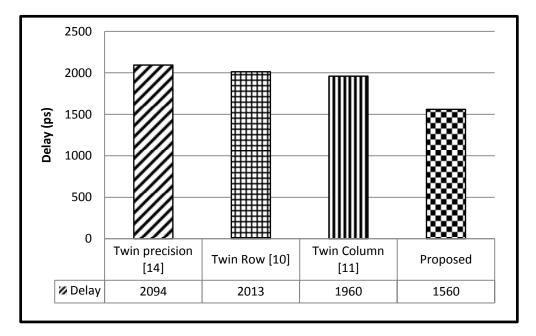

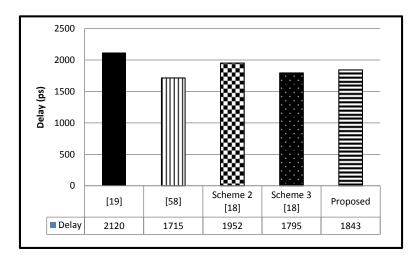

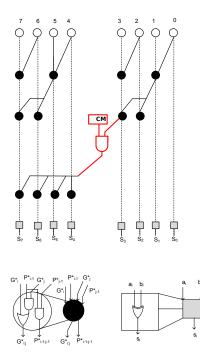

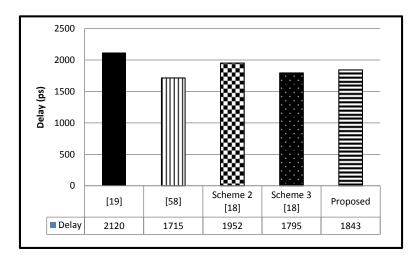

| 3.9  | Latency of various bypass multiplier schemes                                  | 65 |

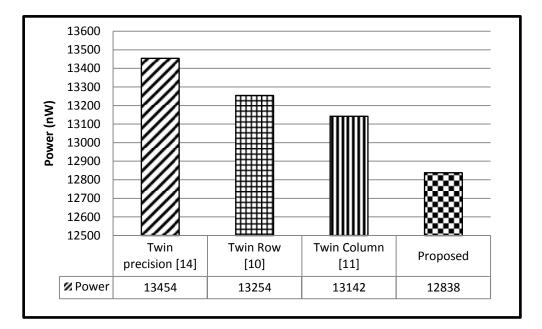

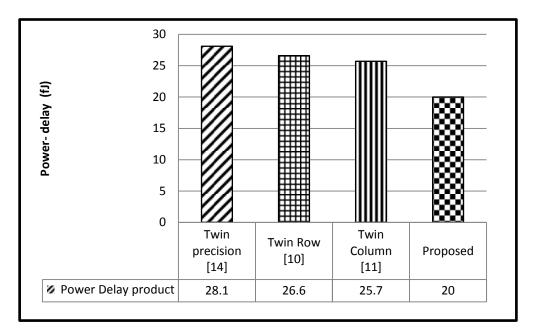

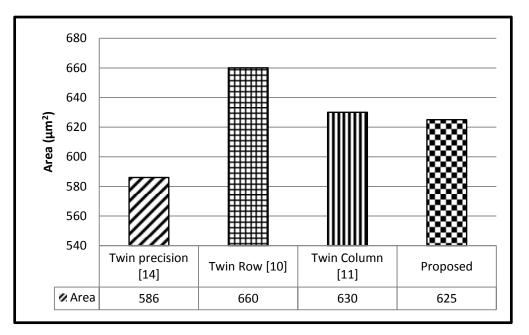

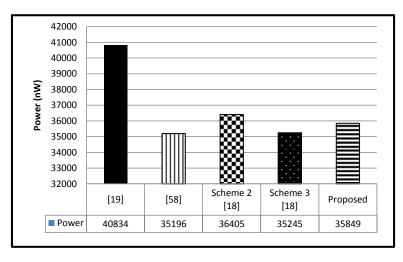

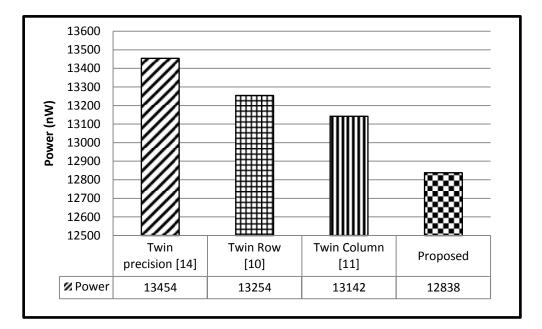

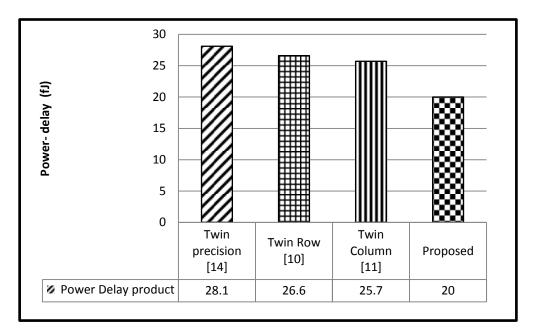

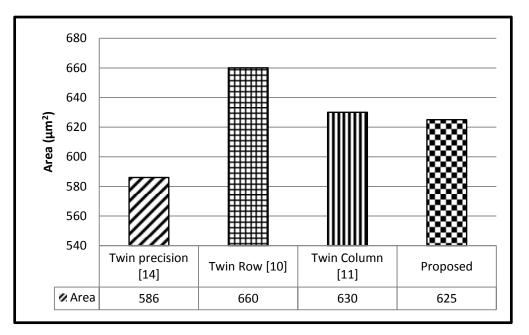

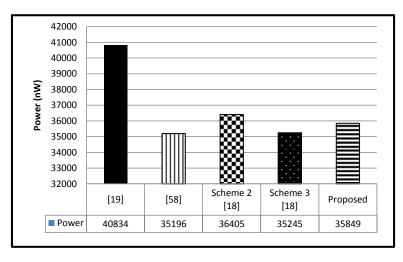

| 3.10 | Comparison of various bypass multiplier schemes in terms of power             | 66 |

| 3.11 | Power-delay product of various bypass multiplier schemes                      | 66 |

| 3.12 | Comparison of various bypass multiplier schemes in terms of area                     | 67 |

|------|--------------------------------------------------------------------------------------|----|

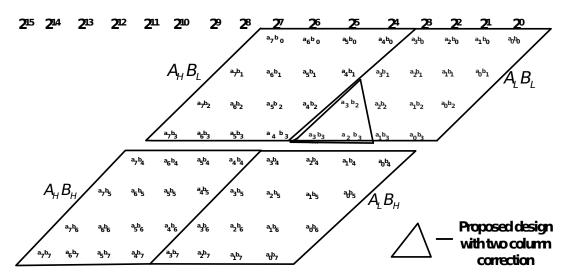

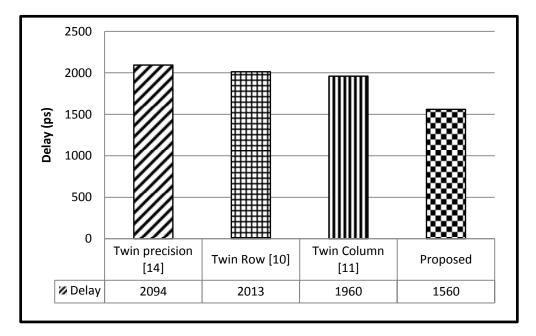

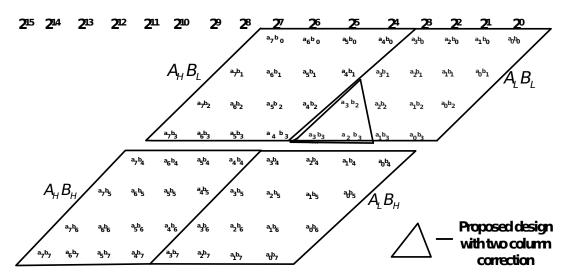

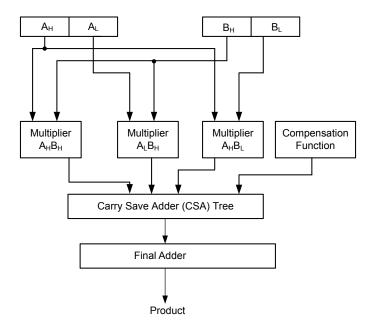

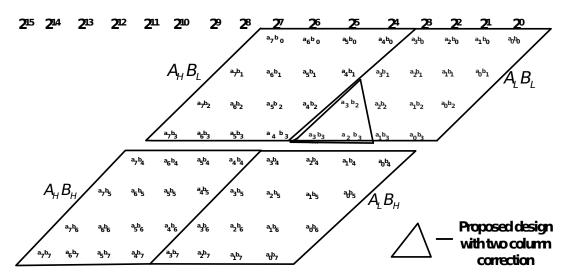

| 4.1  | A 2n*2n recursive multiplication structure illustrating sub-multipliers              | 71 |

| 4.2  | Partial product matrix of a fixed-width recursive multiplier with two most sig-      |    |

|      | nificant columns considered for correction                                           | 72 |

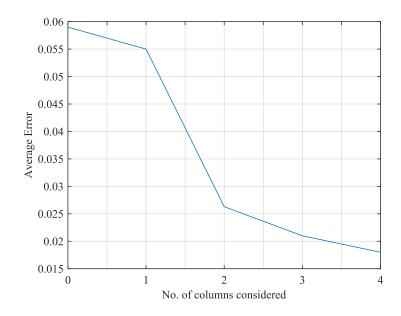

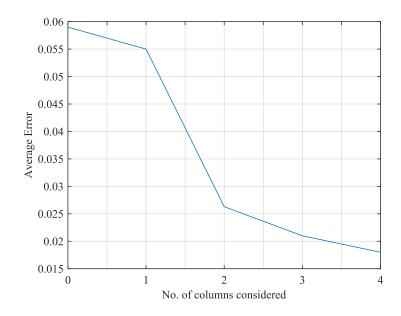

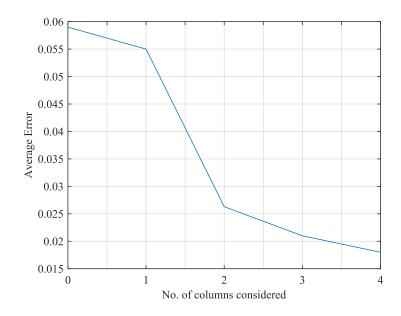

| 4.3  | Average error Vs Number of most significant partial products columns consid-         |    |

|      | ered for correction in a 8 * 8 fixed-width recursive multiplier                      | 73 |

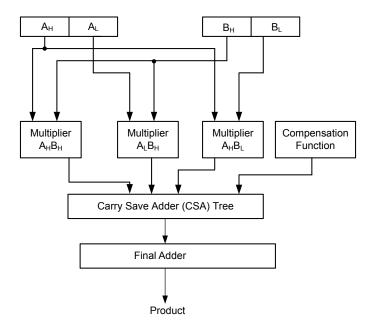

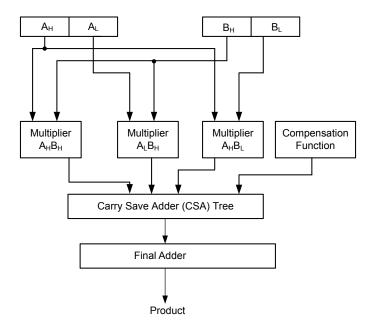

| 4.4  | A new fixed-width recursive multiplier hardware                                      | 74 |

| 4.5  | (a) Partial product reduction structure of a fixed-width recursive multiplier with   |    |

|      | two most significant columns considered for correction (b) Partial product com-      |    |

|      | puted using an AND gate (c) Representation of 3:2 and 2:2 counters (d) Com-          |    |

|      | putation of Sum and Carry-out using dot notation in a full and half adder cir-       |    |

|      | cuits (e) Notation for correction function with two most significant columns         |    |

|      | considered                                                                           | 75 |

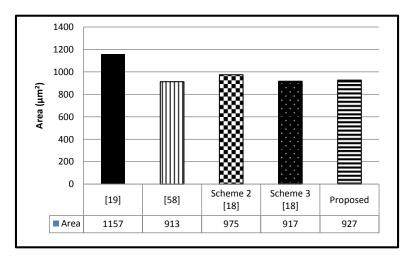

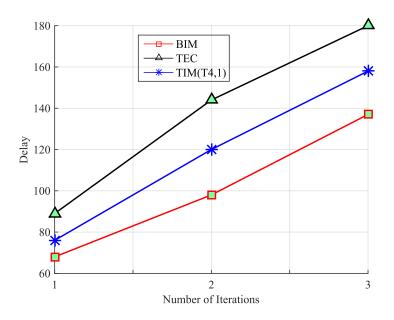

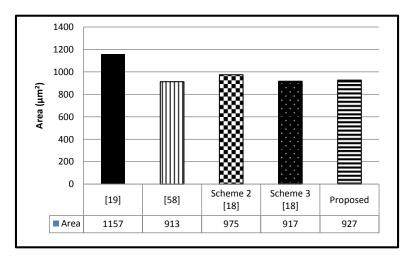

| 4.6  | A Comparison of the proposed fixed-width recursive multiplier with various           |    |

|      | existing multipliers in terms of area                                                | 79 |

| 4.7  | A Comparison of proposed fixed-width recursive multiplier scheme with vari-          |    |

|      | ous existing multipliers in terms of delay                                           | 81 |

| 4.8  | A Comparison of proposed fixed-width recursive multiplier scheme with vari-          |    |

|      | ous existing multipliers in terms of power                                           | 81 |

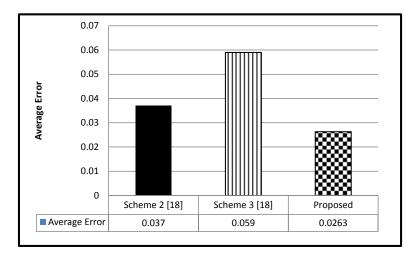

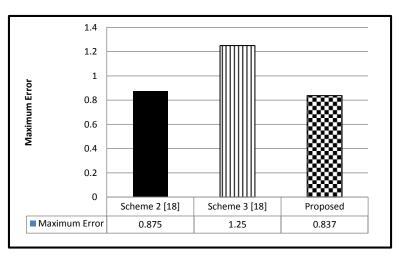

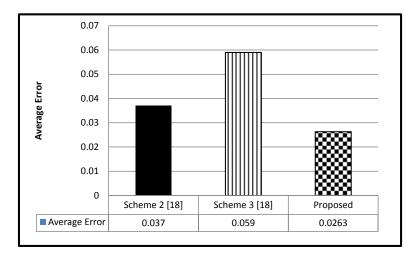

| 4.9  | Average errors of various multipliers                                                | 84 |

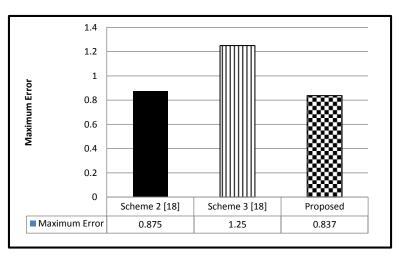

| 4.10 | Maximum errors of various multipliers                                                | 84 |

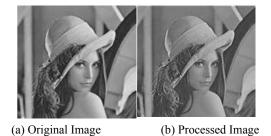

| 4.11 | Cameraman, Lena and pirate Images obtained using exact and the proposed              |    |

|      | multiplier                                                                           | 85 |

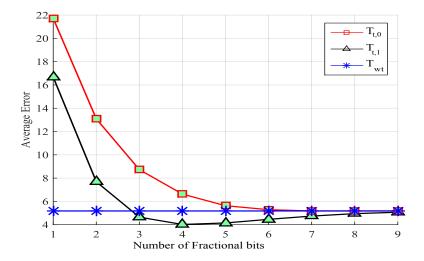

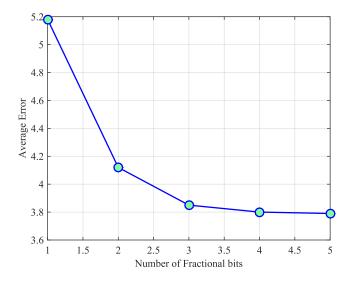

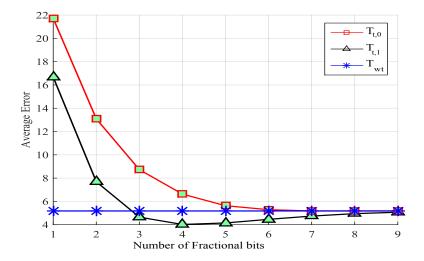

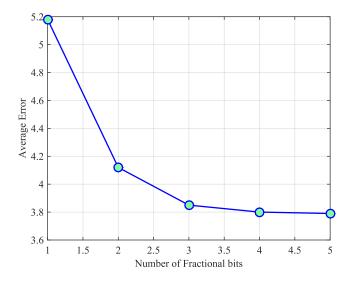

| 5.1  | Average error Vs Number of fractional bits in 8 * 8 multiplication for one iteration | 89 |

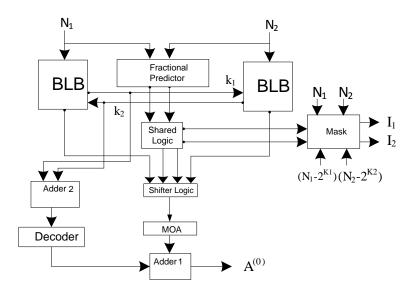

| 5.2  | Block diagram of the proposed truncated iterative multiplier (TIM)                   | 93 |

| 5.3  | Block diagram of the truncated basic logarithmic block (TBLB)                        | 94 |

| 5.4  | Proposed method to detect leading one in fractional portion                          | 95 |

| 5.5  | Variation of average error based on number of fractional bits                        | 96 |

| 5.6  | Truncated iterative multiplier implementation for two iterations 97                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------|

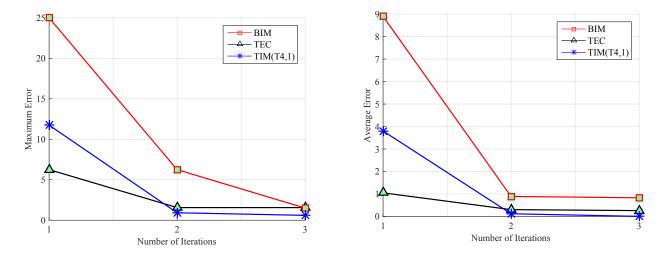

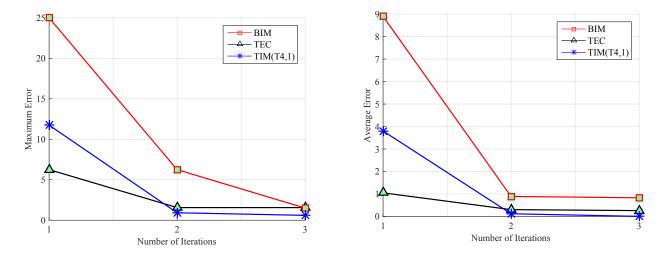

| 5.7  | A comparison of maximum error of existing iterative multiplier designs with                                                        |

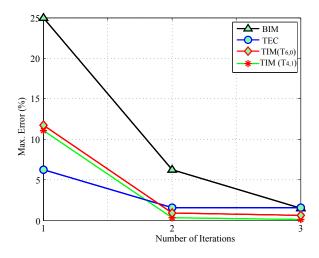

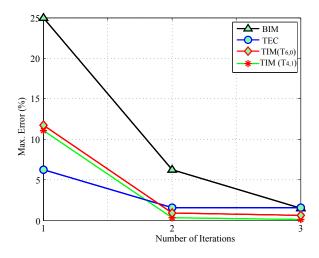

|      | TIM ( $T_{6,0}$ and $T_{4,1}$ ) approach $\ldots \ldots $ 97 |

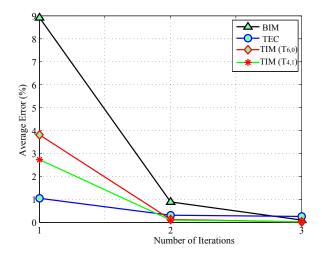

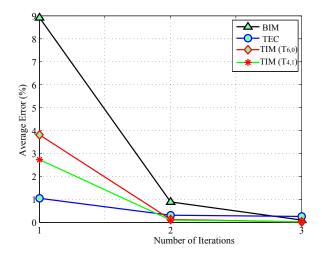

| 5.8  | A comparison of average error of existing iterative multiplier designs with TIM                                                    |

|      | $(T_{6,0} \text{ and } T_{4,1}) \text{ approach } \ldots $ 98                                                                      |

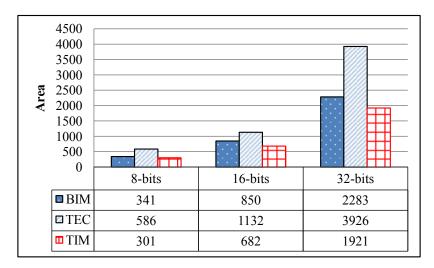

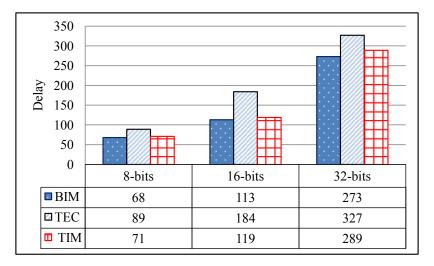

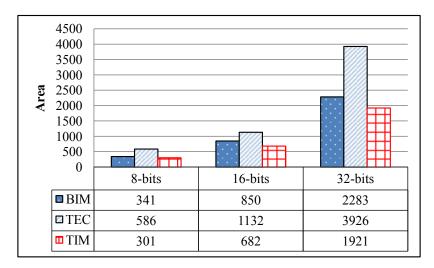

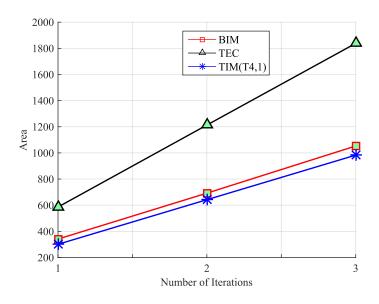

| 5.9  | Area comparison of various multipliers for different bit-widths                                                                    |

| 5.10 | Delay comparison of various multipliers for different bit-widths                                                                   |

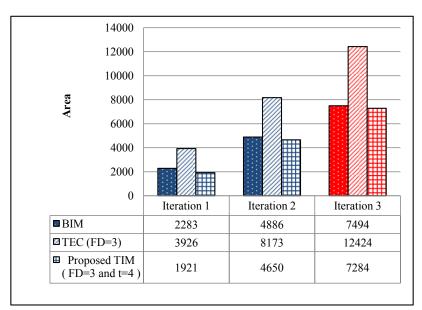

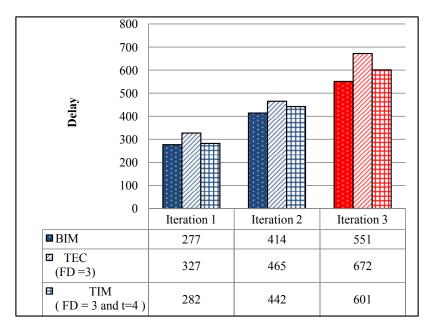

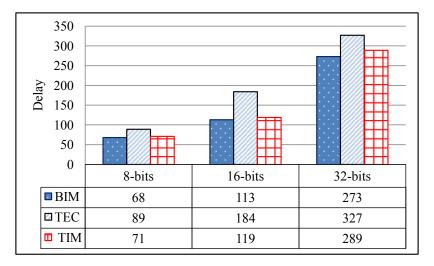

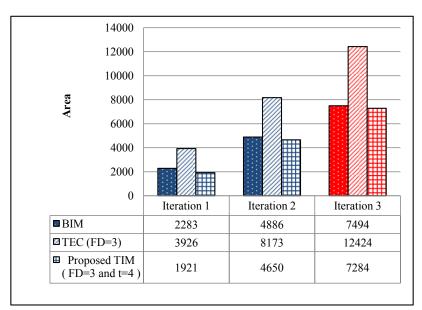

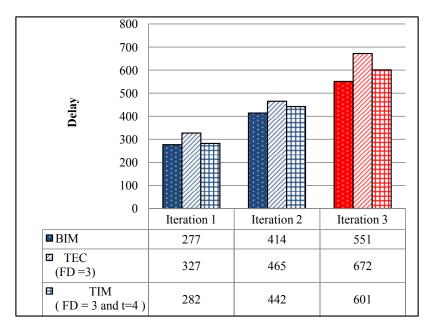

| 5.11 | Area comparison of various multipliers for three iterations                                                                        |

| 5.12 | Delay comparison of various multipliers for three iterations                                                                       |

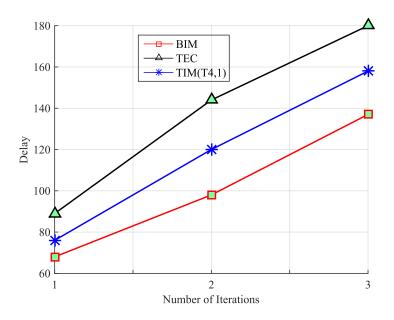

| 5.13 | Maximum and Average errors of various multipliers for three iterations 106                                                         |

| 5.14 | Unit gate area statistics of various multiplier for three iterations                                                               |

| 5.15 | Unit gate delay statistics of various multiplier for three iterations                                                              |

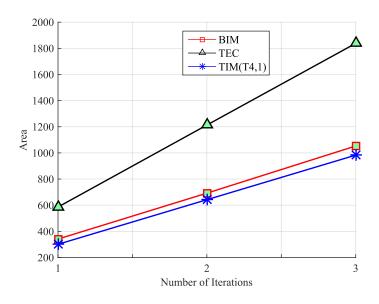

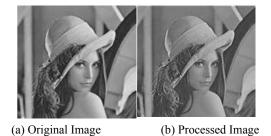

| 5.16 | Lena and Cameraman images obtained using exact and the proposed multiplier 108                                                     |

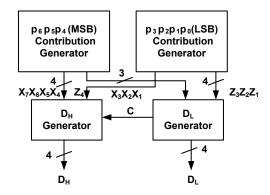

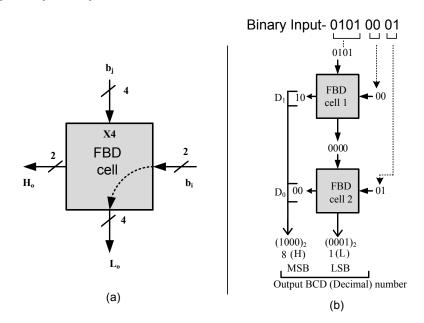

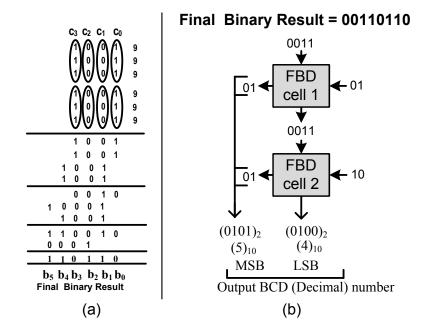

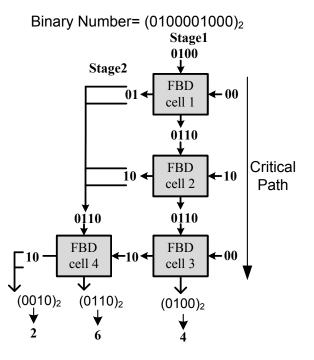

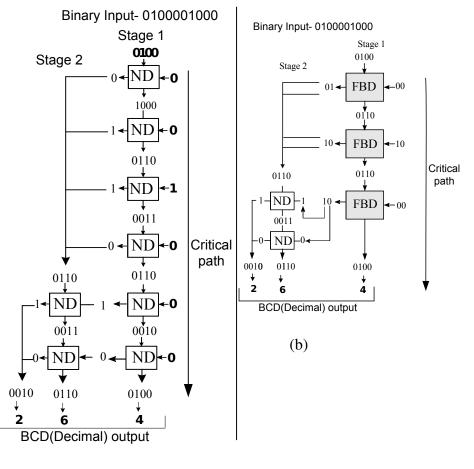

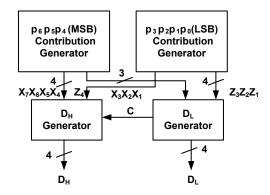

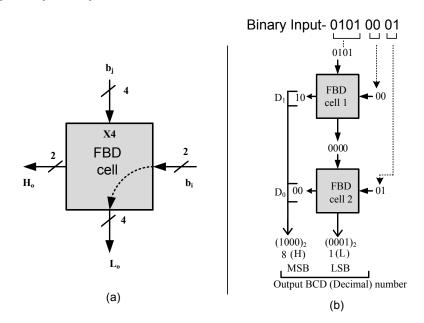

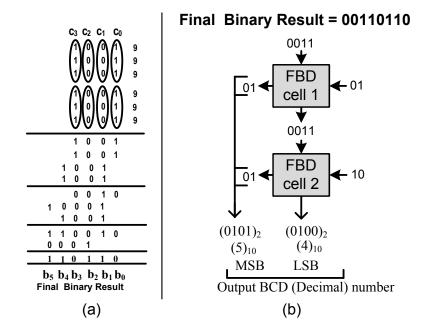

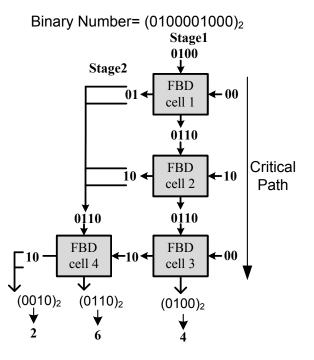

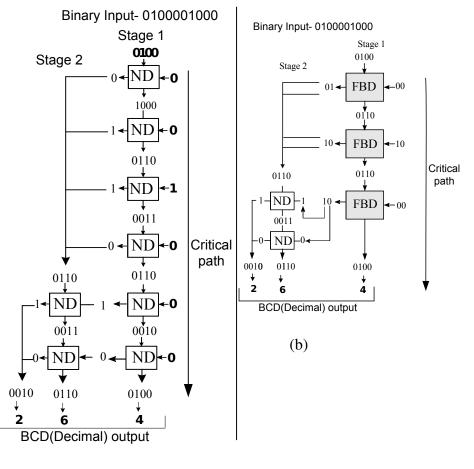

| 6.1  | (a) Compact notation of FBD cell (b) Linear array of FBD cells to form PPBD                                                        |

|      | converter                                                                                                                          |

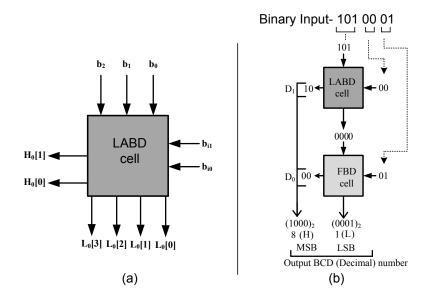

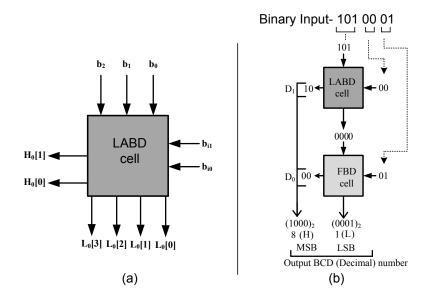

| 6.2  | (a) Compact notation of LABD cell (b) Linear array of LABD and FBD cells                                                           |

|      | to form 'high performance' PPBD (HPPPBD) converter                                                                                 |

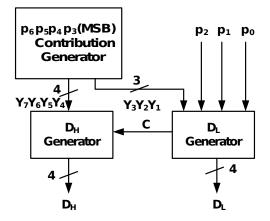

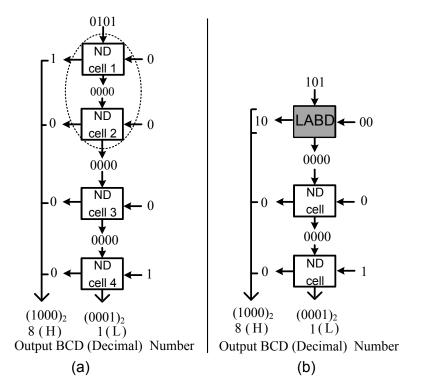

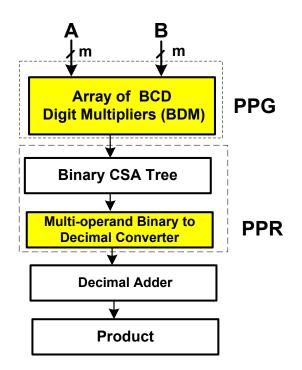

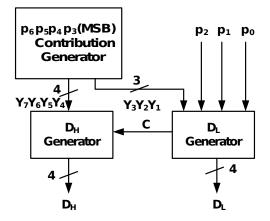

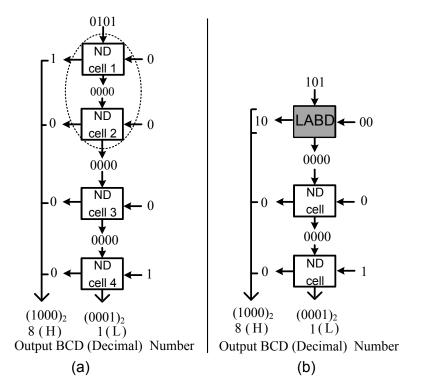

| 6.3  | (a) Iterative array of Nicoud cells to form BDM (b) Linear array of Nicoud and                                                     |

|      | LABD cells to form LAPPBD                                                                                                          |

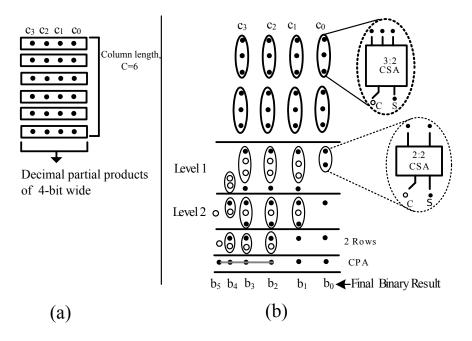

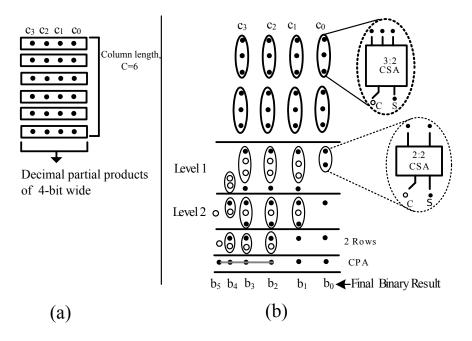

| 6.4  | (a) Decimal partial products of six columns each of 4-bit (b) Example of partial                                                   |

|      | product, denoted using dot, reduction of column size $C=6$                                                                         |

| 6.5  | (a) Numerical example illustrating the reduction of decimal (BCD) partial prod-                                                    |

|      | ucts using CSAs (b) MBD converter formed using linear array of FBD cells to                                                        |

|      | convert binary number to decimal (BCD)                                                                                             |

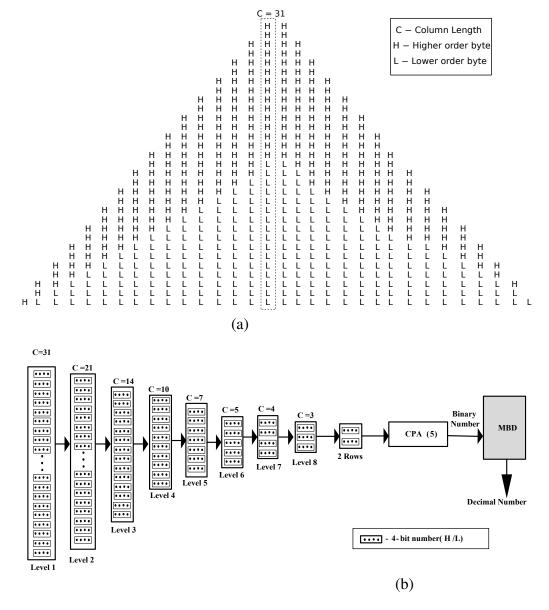

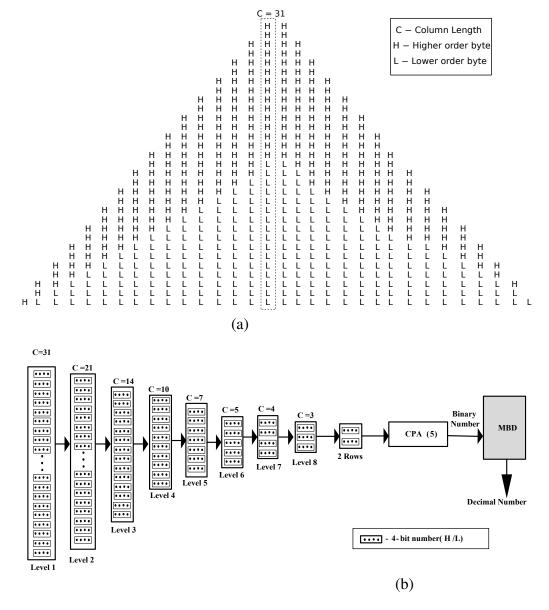

| 6.6  | (a) Partial product matrix in a 16*16 'digit-by-digit' multiplier (b) Partial prod-                                                |

|      | uct reduction of column of largest size C=31 using CSA structure 117                                                               |

| 6.7  | MBD converter for column size, C=31 in 16*16 'digit-by-digit' multiplier 118                                                       |

| 6.8  | MBD converter for column size, C=31 in 16*16 'digit-by-digit' multiplier (a)                                                       |

|      | Using Nicoud cells (b) Hybrid converter using Nicoud and FBD cells 119                                                             |

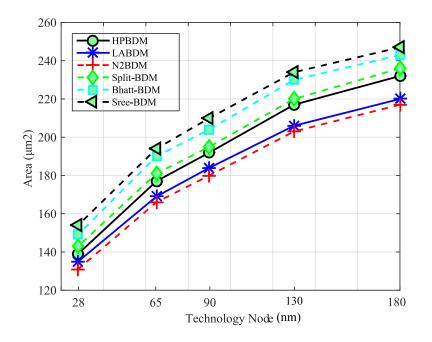

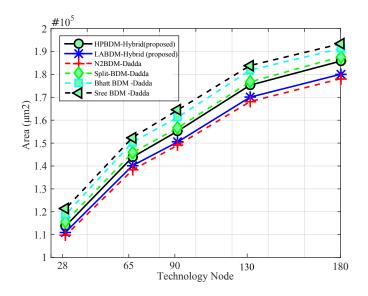

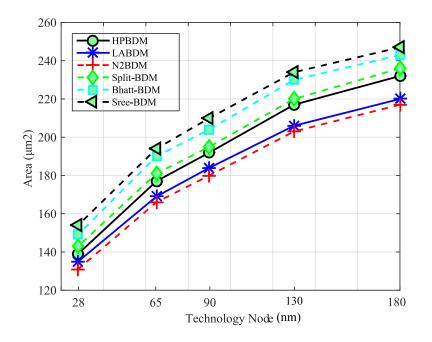

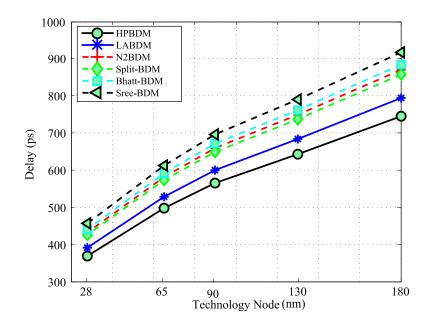

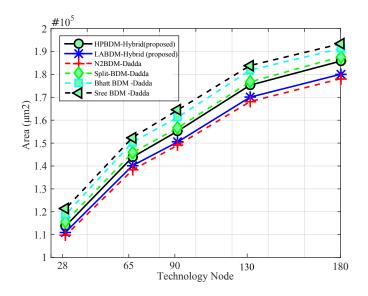

| 6.9  | A Comparison of area consumption by various BDM at different technology         |

|------|---------------------------------------------------------------------------------|

|      | nodes                                                                           |

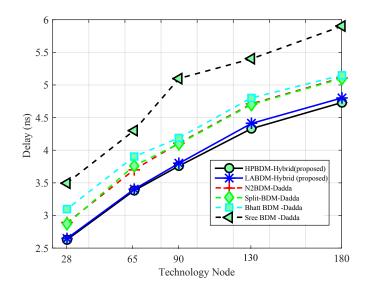

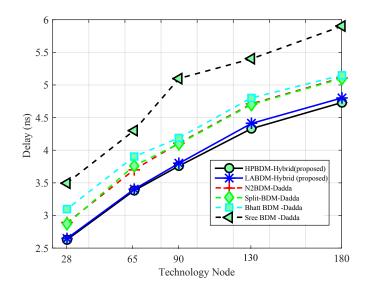

| 6.10 | A Comparison of delay in various BDM at different technology nodes 126          |

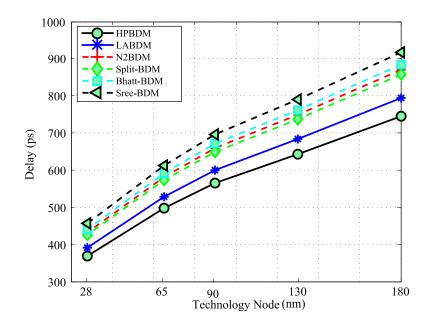

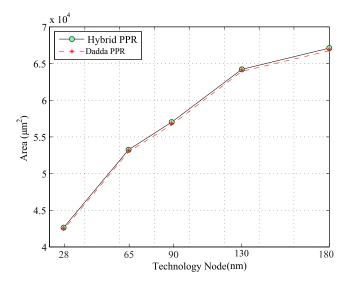

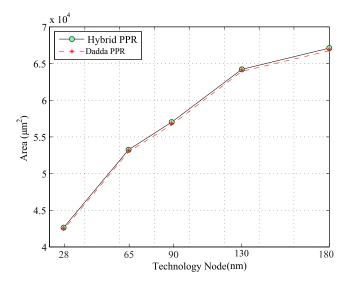

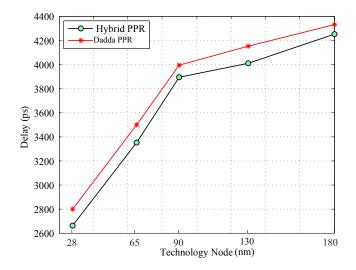

| 6.11 | A Comparison of area consumption at PPR level in 16*16 'digit-by-digit' mul-    |

|      | tiplier at different technology nodes                                           |

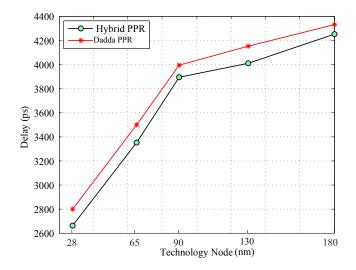

| 6.12 | A Comparison of delay at PPR level in 16*16 'digit-by-digit' multiplier at dif- |

|      | ferent technology nodes                                                         |

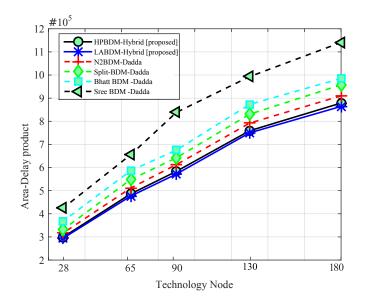

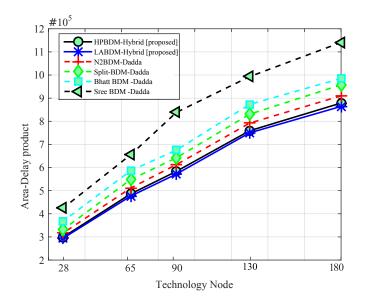

| 6.13 | A Comparison of area consumption by various multiplier at different technol-    |

|      | ogy nodes                                                                       |

| 6.14 | A Comparison of delay of various multiplier at different technology nodes 128   |

| 6.15 | A Comparison of area-delay product of various multiplier at different technol-  |

|      | ogy nodes                                                                       |

## **List of Tables**

| 2.1 | Principle of Binary to BCD conversion                                          | 50  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.1 | Proposed configuration modes of an array multiplier                            | 56  |

| 3.2 | Truth Table of reconfigurable two-dimensional bypass adder cell (RTDBC)        | 61  |

| 3.3 | Truth Table of reconfigurable row-bypass cell (RRBC)                           | 61  |

| 3.4 | Area, delay and power of various multipliers with various bypassing schemes .  | 65  |

| 4.1 | An error comparison of various multiplier architectures                        | 77  |

| 4.2 | Assumptions made for unit gate modeling                                        | 78  |

| 4.3 | Unit gate modeling analysis of various multiplier architectures                | 78  |

| 4.4 | Area, delay and power of various multipliers with correction schemes           | 80  |

| 4.5 | A comparison of values of MSE and PSNR for benchmark images using various      |     |

|     | multiplier schemes                                                             | 83  |

| 5.1 | A comparison of maximum and average error (%) in the proposed TIM $(T_{6,0})$  |     |

|     | and existing schemes for 3 iterations                                          | 99  |

| 5.2 | A comparison of maximum and average error (%) in the proposed TIM $(T_{4,1})$  |     |

|     | for 3 iterations                                                               | 100 |

| 5.3 | Area and Delay metrics of basic design components                              | 100 |

| 5.4 | Area of logarithmic and truncated logarithmic shifter computed using unit gate |     |

|     | analysis                                                                       | 101 |

| 5.5 | Synthesis results of various 32*32 multipliers for one iteration               | 103 |

| 5.6 | A comparison of values of MSE and PSNR for benchmark images using various      |     |

|     | multiplier schemes                                                             | 106 |

| 6.1 | Comparison of area and delay of various BDMs                                |

|-----|-----------------------------------------------------------------------------|

| 6.2 | Performance comparison of different multi-operand converter designs using   |

|     | Dadda and proposed cells for different column size                          |

| 6.3 | Performance comparison of Dadda and Hybrid multi-operand converter in 16*16 |

|     | multiplier                                                                  |

| 6.4 | A Comparison of Dadda and proposed hybrid MBD converters for area and       |

|     | delay performance across various technology nodes                           |

| 6.5 | Area and Delay comparison in 16*16 'Digit-by-Digit' multipliers             |

## Nomenclature

| ASIC   | Application Specific Integrated Circuit                |

|--------|--------------------------------------------------------|

| BCD    | Binary Coded Decimal                                   |

| BD     | Binary to Decimal                                      |

| BDM    | Binary Coded Decimal Digit Multiplier                  |

| BIM    | Babic Iterative Multiplier                             |

| BLB    | Basic Logarithmic Block                                |

| BM     | Binary Multiplier                                      |

| CLA    | Carry Look-ahead Adder                                 |

| CMOS   | Complementary Metal Oxide Semiconductor                |

| CPA    | Carry Propagate Adder                                  |

| CSA    | Carry Save Adder                                       |

| DSP    | Digital Signal Processor                               |

| FA     | Full Adder                                             |

| FBD    | Fast Binary to Decimal                                 |

| FP     | Fractional Predictor                                   |

| HA     | Half Adder                                             |

| HDL    | Hardware Description Language                          |

| HPBDM  | High Performance Binary Coded Decimal Digit Multiplier |

| HPPPBD | High Performance Partial Product Binary to Decimal     |

| ITB    | Internal Tristate Buffer                               |

| IUS    | Incisive Unified Simulator                             |

| KOB    | Karatsuba-Ofman                                        |

- LABDM Low Area Binary Coded Decimal Digit Multiplier

- LAPPBD Low Area Partial Product Binary to Decimal

- LNS Logarithmic Number System

- LS Logarithmic Shifter

- LSB Least Significant Bit

- LSP Least Significant Portion

- LUT Look-up Table

- MA Mitchell Approximation

- MBD Multi-operand Binary to Decimal

- MFA Modified Full Adder

- MFP Modified Fraction Predictor

- MOA Multi-operand Adder

- MRBA Modified Row-Bypass Adder

- MSB Most Significant Bit

- MSE Mean Square Error

- MSP Most Significant Portion

- ND Nicoud Cell

- PE Priority Encoder

- PP Partial Product

- PPBD Partial Product Binary to Decimal

- PPG Partial Product Generation

- PPR Partial Product Reduction

- PSNR Peak Signal to Noise Ratio

- RAM Random Access Memory

- RCA Ripple Carry Adder

- RTDBC Reconfigurable Two Dimensional Bypass Cell

- RTL Register Transfer Level

- TBLBTruncated Basic Logarithmic Block

- TDBA Two Dimensional Bypass Adder

- TEC Truncated Error Correction

- VLSI Very Large Scale Integration

## Chapter 1

## Introduction

### 1.1 Background

One of the most common and frequently executed operations in arithmetic computations is multiplication. Significant amount of work has been carried out to improve the performance of digital multipliers over the years and the same is expected to continue in future. The criteria that are used to quantify their performance include latency, area and power consumed. Thus any improvement made in the design/architecture of multipliers should be reflected in the improvement of these parameters.

In digital static CMOS multipliers, transition activity (due to charging and discharging of the load capacitance) dominates the total energy consumption. Thus, power saving can be achieved by lowering the switching or transition activity per operation. Earlier efforts attempted to reduce the switching activity of the binary multipliers through architectural modifications such as row and/or column bypassing. In these schemes, the redundant signal switching is eliminated by disabling the full adder circuits whose partial product is zero while forwarding the output of the previous adder rows/columns to the next row/columns. However, the extra bypass logic (mostly adder) has only limited effect in reducing the power dissipation while contributing significantly to area overhead. Thus, there is a need to develop alternate bypass multiplication architectures that can address large power consumption in multipliers.

Many of the signal and image processing applications possess an inherent quality of error

resilience and thus do not require absolute accuracy in computation. Further, the final output in these applications is interpreted by human senses which are not perfect. Thus approximation in place of accuracy can be exploited that can lead to a significant improvement in area, power and performance. Based on this idea, several techniques have been proposed that focus on approximate rather than accurate computing. However, most of these techniques provide solutions that are based on trial and error and thus the accuracy achieved tends to be lower. Thus, realizing efficient multiplier units (binary and logarithmic) for approximate computing in a systematic way, which also have high precision would be of considerable interest.

The importance of error-free arithmetic is growing day-by-day and decimal (BCD) arithmetic circuits are making their way into application such as financial, scientific and commercial, etc. Like in binary arithmetic, one of the most vital and common operations in decimal arithmetic, is multiplication. Decimal multiplication can be classified as serial multiplication, parallel ('word-by-digit') and ('digit-by-digit') multiplication. Decimal (BCD) 'digit-by-digit' multipliers are appropriate for pipelined computations and result in improved regularity of the circuits. This regularity, in conjunction with shorter interconnects, results in significant improvement in the multiplier performance. There is however a significant scope to develop more efficient architectures for 'digit-by-digit' multiplication.

### **1.2** Objectives of the Thesis

The objectives of this thesis are as follows:

- To improve the existing binary multiplier architecture to reduce the switching activity resulting in low power consumption.

- To design and implement truncated binary and iterative logarithmic multipliers targeted for error resilient applications

- To develop a BCD multiplier with improved performance for high speed (parallel) multiplication

### **1.3** Steps involved in carrying out present research

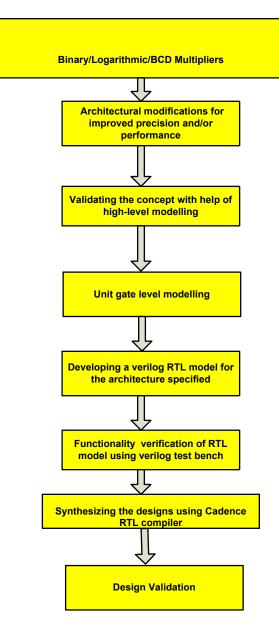

Figure 1.1 illustrates the steps involved in carrying out present work, summarized below:

- Modification of multiplier architectures to improve precision and/or performance for binary, logarithmic and decimal multiplication

- Modeling the architectures (fixed-width binary and logarithmic multiplier) in MATLAB

- Evaluation of the above using synthesis-independent unit gate level (hardware) modeling

- Verification using Verilog test benches and applying random stimuli to cover a wide input range

- Synthesis of binary, logarithmic and decimal multipliers using Cadence RTL compiler to obtain estimates of area, delay, and power

- Analysis of the above multipliers to evaluate and compare their performance with the existing designs

#### **1.3.1** High Level Modeling

The multiplier schemes (fixed-width binary and logarithmic multiplier) have been modeled and verified in MATLAB environment. Metrics related to precision such as maximum error and average error have been computed for different multiplier schemes. The main purpose of carrying out high-level modeling is as follows:

- 1. It is a faster way of realizing optimized architectures/designs

- 2. It offers an easier and faster method to evaluate and compare different architectures/designs

- 3. A high-level model serves as an abstract model of the design to generate input stimulus and verify the result

Figure 1.1: Research Flow chart

#### **1.3.2 Unit Gate Level Modeling**

All the designs (fixed-width binary, logarithmic and decimal (BCD) multipliers) under consideration have been modeled using unit gate approach to obtain a rough estimate of area (A) and delay (D). This model is useful for high-level analysis and does not depend strongly on any one process technology, synthesis tool, or cell library. The assumptions made while performing the unit gate modeling are the following: Each two-input gate (AND, OR, NAND, NOR) is counted as one gate while EX-OR and EX-NOR are counted as two gates for both area and delay. Further, an m-input gate is assumed to be composed of a tree of m-1 input gates while the effects of wiring, buffering and inverting costs (area and delay) are neglected.

#### **1.3.3** CAD tools used in the ASIC implementation

#### 1.3.3.1 Cadence Simulator

Cadence NCSim is an RTL functional simulator that can simulate Verilog models. The functional behavior of the modules (Binary, Logarithmic and BCD multipliers) was verified in NC-Sim using Verilog test benches.

#### 1.3.3.2 Cadence RTL Compiler

Cadence RTL Compiler is a hardware synthesis tool. It maps an RTL hardware description model using a standard cell library into a gate-level net list. The output structural level thus obtained is composed of cells that exist in the standard-cell technology library. The synthesis tool accepts Verilog RTL code as an input and generates area, delay and power reports.

### **1.4** Organization of the Thesis

This thesis is organized as follows. Chapter 2 presents a review of various existing multiplier architectures relevant to this research and their realization in hardware. It also provides a detailed discussion of multipliers based on binary, logarithmic and BCD number systems. Keeping in mind the importance of arithmetic precision, chapters 3 and 6 develop and validate new techniques for improved precision of binary and decimal arithmetic circuits. Since precision is not as important as efficiency of implementation for error resilient applications, chapters 4 and 5 develop novel truncation schemes that lead to efficient implementation of binary and logarithmic multipliers. These schemes have also been compared for performance against the existing ones. Chapter 7 draws conclusions and provides recommendations for future work.

## Chapter 2

## **Literature Review**

### 2.1 Introduction

This chapter reviews a number of widely used multiplier architectures while focusing mainly on those that will be of concern in this thesis. The chapter is organized as follows: Preliminary information on the existing binary multiplier architectures is presented in Section 2.3 - 2.5, and fixed-width (truncated) multipliers are discussed in Section 2.6. An outline of the existing logarithmic multipliers is presented in Section 2.7 while decimal (BCD) multipliers are reviewed in Section 2.8.

## 2.2 Classification of Multiplier Architectures

Digital multipliers based on number system can be classified as (i) Binary multipliers (ii) Logarithmic multipliers and (iii) BCD multipliers. A pictorial representation of the same is given in Fig.2.1 and explained in detail in the following sections.

### 2.3 Binary Multipliers

It is well known that binary multipliers can be classified into two categories, viz., integer fixed-point and floating point. This thesis however focuses on integer fixed-point multiplier architectures only. In fact, floating-point multipliers consist of a fixed-point multiplier for the

Figure 2.1: Classification of digital multiplier architectures based on number system

significant and additional circuitry to deal with the exponents and special values. Thus, techniques developed for efficient binary multiplication presented in this thesis are also applicable for floating-point multiplication.

Literature on binary computer arithmetic includes topics ranging from sequential to parallel multipliers. Today, most of the advanced digital systems include a parallel binary multiplication unit to carry-out mathematical computations. Array and Booth multipliers are a few examples of parallel multiplication in this category. As is well known, array-based multipliers [1] are ideal for very large scale integration (VLSI) and application specific integrated circuits (ASICs) due to their regular layout. On the other hand, Booth multiplier [2], although faster compared to array multipliers, has an irregular layout structure, making it not very suitable for VLSI implementations. Thus, this thesis focuses on design and validation of area and power efficient binary array multipliers. In order to provide more insight in to multiplication process, the general structure of binary multiplier is described initially and implementation of the same is illustrated using Braun array multiplier.

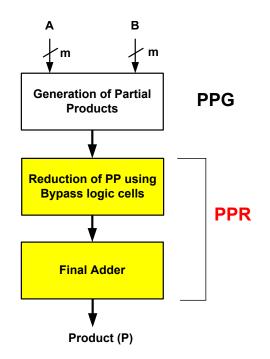

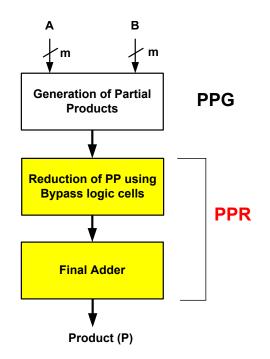

In general, binary multiplication involves three steps: (i) Partial product generation (PPG) (ii) Partial product reduction (PPR) and (iii) Final product computation. A typical binary multiplier accepts two binary inputs *A* and *B*, each of *N*-bit width, as illustrated in Fig.2.2. Multiplication schemes primarily differ in the manner partial products are generated and/or accumulated. The multiplication operation can be accelerated in two ways: generating optimized number of partial products (PPs) in the first (PPG) step or accelerating their accumulation in second (PPR) step. One of the most effective ways of accumulating an array of partial products into two rows is through carry save adder structure. These two rows are eventually reduced using a final adder in the last step. A detailed explanation of PPG and PPR in an array multiplier is provided in subsequent sections.

Figure 2.2: A general binary multiplication structure

## 2.4 Braun Multiplier

The simplest array multiplier proposed was by Braun [3], generally known as carry save multiplier, suited for unsigned operations only. The mathematical model of a N\*N unsigned array multiplication is given below. Assume A and B to be two N-bit unsigned numbers, where A is the multiplicand and B is the multiplier.

$$A = \sum_{i=0}^{n-1} a_i \cdot 2^i \tag{2.1}$$

$$B = \sum_{i=0}^{m-1} b_j . 2^j \tag{2.2}$$

The product (P) can be written as:  $P = A * B = \sum_{i=0}^{n-1} \sum_{j=0}^{m-1} a_i b_j \cdot 2^{i+j}$

#### **2.4.1** Partial Product Generation (PPG)

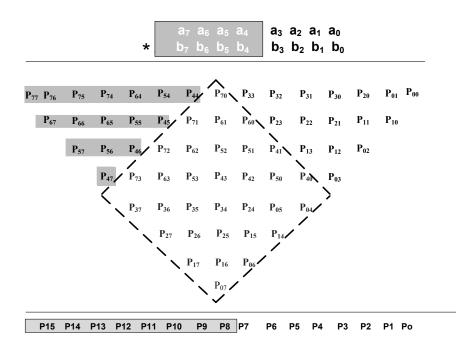

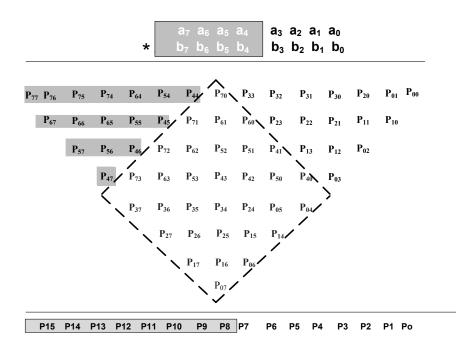

In general, to implement N \* N binary multiplier in hardware,  $N^2$  partial products are required for PPG which are generated using AND gates. As an example, consider hardware implementation of 8\*8 Braun multiplier illustrated in Fig.2.3. A typical multiplication of two 8-bit binary numbers results in a total of 64 PPs. Figure 2.3(a) depicts the arrangement of these partial products in a matrix form. Each of these partial products (PPs) is obtained using an AND gate as illustrated in Fig.2.3(b). Further, an alternate partial product representation of the same multiplier is shown in Figure 2.4.

Figure 2.3: (a) Partial product matrix representation in a 8\*8 Braun multiplier (b) Partial product computed using an AND gate

#### 2.4.2 Partial Product Reduction (PPR)

The PPs generated must be accumulated to form the final product. In multiplication, accumulation of PPs, also referred to as reduction of PPs, consumes most of the time taken for multiplication. The reduction of the PPs is performed using two main methods, namely, ac-

Figure 2.4: (a) Alternate representation of partial products in 8\*8 Braun array multiplier (b) Partial product computed using an AND gate

cumulation by rows and accumulation by columns. The building modules are referred to as adders if the accumulation is by rows and conversely, if the reduction is by columns, they are referred to as counters. A simple technique in the accumulation by rows involves multiple two-operand carry propagate adders (CPAs). However, propagation of the carry using CPAs is time-consuming and thus is slow [4]. An alternate and more efficient approach is to reduce the columns by using carry-free adders, namely, carry save adders (CSAs) as discussed below.

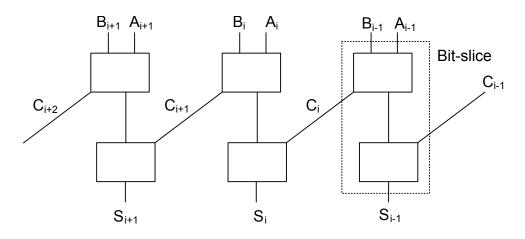

#### 2.4.2.1 Binary Carry Save (CSA) Adders

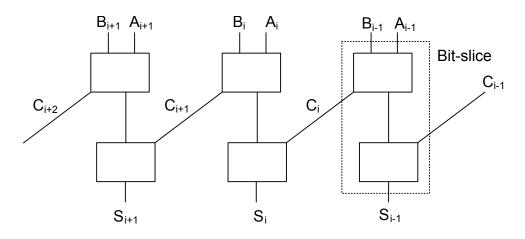

Carry save adders are popular structures used for partial product reduction in multiplication process. The binary partial product reduction structure uses multiple levels of carry save adders (CSAs). As illustrated in Fig.2.5, each bit-slice (group of 3-bits) of a CSA is realized using a full adder. This binary full adder generates a sum-bit and a carry-bit. The carry input is propagated from the previous bit-slice to the next most significant position in the reduction tree. The PP reduction process results in two rows (sum and carry), which are eventually converted to the final sum using a two operand adder (carry propagating adder). In short, binary PPR can be implemented via CSA tree comprising of binary half adders (HAs) and full adders (FAs) as basic elements.

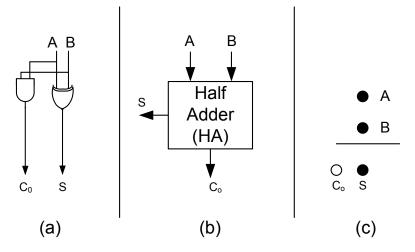

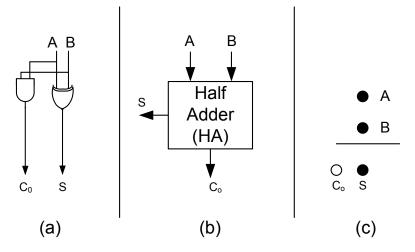

As is well known, a half adder accepts two operand bits (A and B) as inputs and computes

Figure 2.5: Carry- free operation using full adders

sum (S) and output carry bit ( $C_o$ ) as outputs. The carry bit ( $C_o$ ) will eventually serve as input carry-in for the successive half adder. The implementation of a half adder circuit follows the Boolean equations 2.3 and 2.4 and its gate level implementation, cell notation and dot notation are shown respectively in Fig.2.6 (a-c). The notations ' $\oplus$ ', '.' and '+' denote logical XOR, AND and OR gates respectively.

$$S = A \oplus B \tag{2.3}$$

$$C_0 = A.B \tag{2.4}$$

Figure 2.6: (a) Logic circuit of half adder (b) Half adder cell notation (c) Computation of Sum and Carry-out using dot notation in a half adder

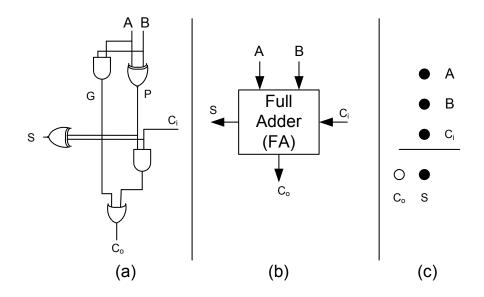

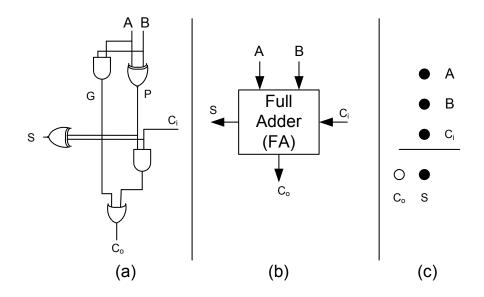

Similarly, a full adder accepts three operands  $(A, B \text{ and } \operatorname{carryin}(C_i))$  as inputs and computes the sum (S) and output carry bit  $(C_o)$  as outputs. The design of a full adder circuit follows the Boolean equations 2.5 and 2.6 while the gate level implementation, cell notation and dot notation are illustrated in Fig.2.7(a-c).

$$S = A \oplus B \oplus C_i \tag{2.5}$$

$$C_0 = (A \oplus B).C_i + AB = AB + BC_i + C_iA \tag{2.6}$$

Figure 2.7: (a) Logic circuit of full adder (b) Full adder cell notation (c) Computation of Sum and Carry-out using dot notation in a full adder

A row of full-adders, represented in Fig.2.5, can be viewed as a mechanism to reduce three operands to two operands. For a CSA, each FA referred to as 3:2 counter has three dots in one column as inputs. The resulting sum output will result in a dot with the same magnitude as the inputs while carry output will result in a dot in the column to its left (one order of magnitude higher) as shown in Fig.2.7(c).

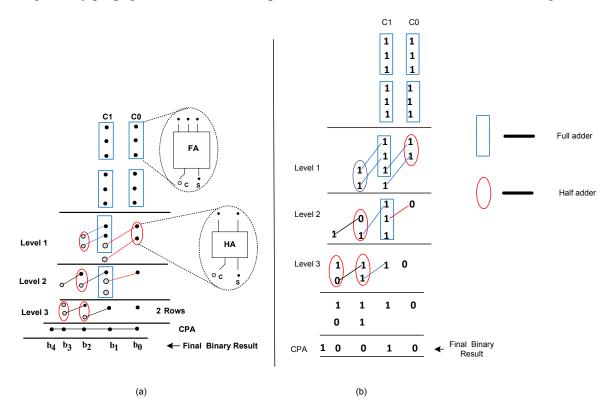

For illustration purpose, reduction of two partial product columns (c0 and c1) is shown in Fig.2.8(a) and the same is later extended to 8\*8 multiplication as shown in Fig.2.9. Each column, consisting of six partial products (each denoted by solid dot( $\bullet$ )), is reduced in parallel to sum (S) and carry (C). The sum is denoted by solid dot( $\bullet$ ) with the same magnitude as the inputs while the carry, denoted with hollow dot ( $\circ$ ), has higher positional weight compared to input. The six partial products are reduced ( in three levels) to two rows using a tree of 3:2 and 2:2 full and half adders. These two rows of PP are eventually reduced to a binary number by

using a carry propagation adder (CPA) represented with a horizontal line shown in Fig.2.8 (a).

Figure 2.8: (a) Partial product reduction using CSA dot notation (b) A numerical example related to partial product reduction

The numerical example illustrated in Fig.2.8(b) describes the addition of two columns (c0 and c1), each consisting of six bits, where each partial product in the column is assumed to be '1'. These columns are reduced to two rows in four levels using a tree of full and half adders. These two rows of PPs are reduced to final binary result by using a carry propagation adder (CPA).

A variety of algorithms for accumulating the partial products using CSAs has been proposed [1]. The advantage of using CSAs is that they do not contribute to hardware complexity and one of the first algorithms proposed was by Wallace [5].

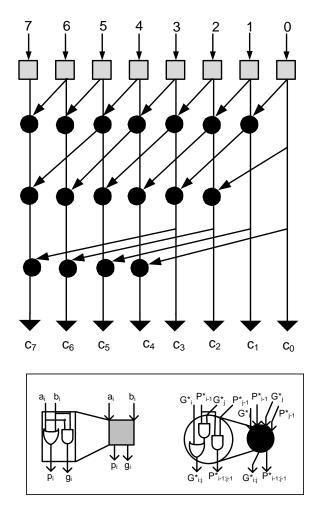

#### 2.4.3 Wallace Reduction Tree

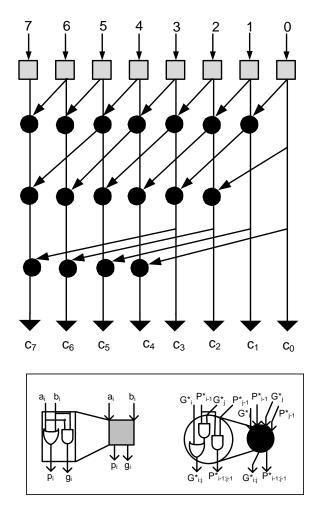

Wallace developed a method for reducing the columns in parallel. Figure 2.9 illustrates a Wallace-like reduction tree organization for an  $8 \times 8$ -bit unsigned multiplier, presented in Section 2.4.1. As discussed earlier, a sum output (*S*) from a full or half-adder at one stage places a

dot in the same column at the next stage. A carry output  $(C_o)$  from a full or half-adder at one stage places a dot one order of magnitude higher i.e., in the column to its left, in the next stage. As shown in Fig.2.9(d), three dots joined by a solid diagonal line indicates that these PPs are outputs of a (3,2) counter, while two dots joined by diagonal line indicates that these PPs are outputs of a (2,2) counter. Consequently, the PP matrix is accumulated to a height of two in four levels using a carry save adder (CSA) tree structure formed using full adder and half adder as shown in Fig.2.9(a). A total of four reduction levels with matrix heights of 6, 4, 3 and 2 is required to accumulate the PP matrix into two rows using Wallace technique. These two rows are reduced to a final sum using a carry propagate adder (CPA) or any fast adder mentioned below.

Figure 2.9: (a) Wallace tree partial product reduction structure using 3:2 and 2:2 counters (b) Partial product computed using an AND gate (c) Representation of 3:2 and 2:2 counters (d) Computation of Sum and Carry-out using dot notation in a full and half adder circuits

#### 2.4.4 Final Adder

The last step in the partial product reduction process is the conversion of the redundant sum obtained from Wallace reduction tree into non-redundant representation. This step is performed using a non-redundant adder. There exist many topologies to implement the final adder namely, ripple carry, carry look-ahead, and parallel prefix (or prefix tree) [6] among many. Based on priorities (area and delay) appropriate adder topology can be selected from the available literature. For instance, a ripple carry adder has area and a delay that is proportional to the adder's length while prefix based adders have almost logarithmic delay but with area overhead. Thus, appropriate adder design can be chosen depending on the requirement.

#### 2.4.4.1 Ripple Carry Adder

The basic building blocks of a ripple-carry adder (RCA) are full adders. Consider two n-bit numbers, *A* and *B*, described by equations 2.1 and 2.2. A total of n full adders are used, one for each column. The full adder in column *i* adds the operand bits  $A_i$  and  $B_i$  plus the carry-in  $(C_i)$ , where  $i = 0, 1 \dots N - 1$ . The carry-out of previous stage full adder is passed down to the carry-in of the full adder in the next most significant column. The  $S_i$  outputs of the *n* full adders form the sum. Figure 2.10 illustrates a 4-bit ripple carry adder.

Figure 2.10: 4-bit Ripple Carry Adder

Although, ripple carry adder is simple and easy to implement, it suffers from large delay. This is because the full adder in the next stage has to wait for carry bit from the previous stage full adder (FA). By inspecting the FA shown in Fig.2.10 it can be observed that each full adder contributes to a two gate delay in the process of rippling the carry [6]. In general, critical path length of the final carry propagation adder can be deduced as follows:

CPA length = 2N - 2

#### 2.4.4.2 Carry Look-ahead Adder (CLA)

The carry propagation delay in a ripple carry adder increases linearly with an increase in the number of input bits. Efforts to reduce this delay has resulted in novel adder architectures and Carry Look-ahead (CLA) is one such adder which improves the speed by computing the carry signals in advance that depends on the input operands.

Based on the combination of inputs  $A_i$  and  $B_i$ , the signals, generate  $(G_i)$  and propagate $(P_i)$ , determine the possibility of carry generation. Generate term determines if a carry-out would be '1' independent of carry-in while propagate term determines whether carry moves to the next higher significant position. The standard carry look-ahead adder equations  $(G_i \text{ and } P_i)$  that dictate if the carry will be generated or propagated can be given as,

$$G_i = A_i \cdot B_i \tag{2.7}$$

$$P_i = A_i \oplus B_i \tag{2.8}$$

Clearly, carry generation depends on the values of  $A_i$  and  $B_i$ . For instance, when  $A_i = B_i$ ='1', a carry of '1' is produced at the *i*<sup>th</sup> position, while a carry of '0' is generated when  $A_i = B_i$ ='0'. Conversely, carry propagation happens when  $A_i \neq B_i$ . Hence, when  $A_i \neq B_i$  and carry-in ( $C_{in}$ ) is '1', then  $C_{in}$  is said to propagate to the next position.

Accordingly, the sum and carry recurrence for the  $i^{th}$  stage is as follows:

$$S_i = P_i \oplus C_i \tag{2.9}$$

$$C_{i+1} = G_i + P_i \cdot C_i \tag{2.10}$$

Similarly, the carries in a 4-bit CLA are generated in parallel according to the following equations:

$$C_1 = g_0 + p_0 c_0 \tag{2.11}$$

$$C_2 = g_1 + p_1 g_0 + p_1 p_0 c_0 \tag{2.12}$$

$$C_3 = g_2 + p_2 g_1 + p_2 p_1 g_0 + p_2 p_1 p_0 c_0 (2.13)$$

$$C_4 = g_3 + p_3g_2 + p_3p_2g_1 + p_3p_2p_1g_0 + p_3p_2p_1p_0c_0$$

(2.14)

The logic circuit of a 4-bit CLA is illustrated in Fig.2.11.

Figure 2.11: 4-bit Carry Look-ahead adder

One obvious disadvantage in CLA adder is that the carry block gets complicated for large values of N. To mitigate this, a new class of adder networks has been designed that transfers the carry through the look-ahead stage in about  $log_2(N)$  stages. These networks are known as tree networks and the adder circuits that utilize these networks are called prefix-adders or tree-adders [7].

#### 2.4.4.3 Carry Look-ahead (CLA) based Parallel Prefix Adder

There are numerous ways to design the parallel prefix tree adders that offer trade-offs among parameters like the number of logic stages, the maximum fan-out of each logic gate and the wiring complexity between the stages [6] etc. Based on these parameters a wide variety of prefix tree architectures, namely, Sklansky, Brent-Kung, Kogge-Stone, Ladner-Fischer, Han-Carlson and Knowles [6] have been developed.

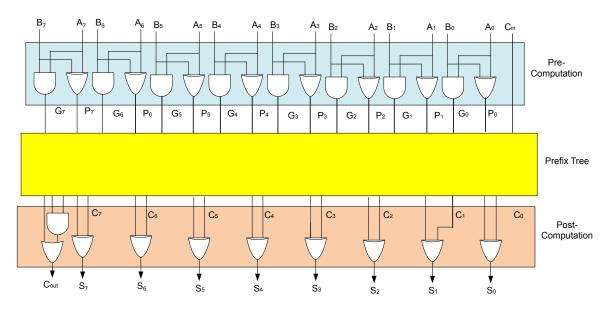

In general, as illustrated in Fig.2.12, there are three stages in any prefix adder that can be termed as (i) pre-computation stage (ii) prefix network stage and (iii) post-computation stage [6,8,9]. The pre-computation stage determines the generate and propagate bits as per the equations 2.7 and 2.8.

Figure 2.12: CLA based 8-bit parallel-prefix structure

The prefix network stage computes the final carries from the individual generate and propagate bits of pre-computation stage. Using associative principle, carry computation is transformed to prefix problem using the operator 'o' which associates pairs of generate and propagate as mentioned below:

$$(g,p) \circ (g',p') = (g+p.g',p.p')$$

(2.15)

where g and g' denote the generate terms and p and p' represent the propagate terms. Using the operator ' $\circ$ ' consecutive generate and propagate pairs can be grouped to generate carry as follows:

$$C_i = (g_i, p_i) \circ (g_{i-1}, p_{i-1}) \circ \dots (g_1, p_1)(g_0, p_0)$$

(2.16)

The post computation stage determines the final sum from carries generated in the prefix network stage.

The graph model of prefix carry computation is obtained by representing the operator ' $\circ$  ' as node •, while the signal pairs (g, p) are denoted as edges of a graph. Different prefix structures differ only in prefix network stage.

To illustrate a prefix structure, an 8-bit Kogge-Stone [8] prefix tree is illustrated in Fig.2.13. The dark color (•) node in the graph represents the logic module while the white color (•) node denotes a feed through node with no logic (realized with a buffer in real hardware).

Figure 2.13: CLA based 8-bit Kogge-Stone prefix adder

# 2.5 Low Power Techniques in Binary Multiplier Design

Multipliers are logic circuits that are computationally heavy. Typically, a large number of logic gates with high transition activity are devoted to perform the multiplication operation. The logic transitions cause the logic gates to charge/discharge the load capacitance leading to dynamic power dissipation. This section provides a brief introduction to various sources of power dissipation in CMOS based designs. It is followed by preliminary information on existing reconfigurable multipliers and bypass techniques to minimize the dynamic power dissipation.

#### 2.5.1 Dynamic Power Dissipation in CMOS based Circuits

The main source of power dissipation in CMOS based circuits is the dynamic power dissipation caused by switching activity of the logic circuits. Dynamic power dissipation is given by,

$$P_{av} = C_L V_{DD}^2 f_p \alpha \tag{2.17}$$

Where:

$C_L$  = charged load capacitance

$V_{DD}$  = supply voltage

$f_p$  = clock frequency

$\alpha$  = switching activity factor.

The dynamic power dissipated is thus proportional to the number of transitions occurring in a logic gate. Various power reduction methods to minimize the redundant switching( $\alpha$ ) have been proposed in the literature as described later.

#### 2.5.2 **Power Consumption in Parallel Multipliers**

In general, multipliers can be implemented as sequential or combinational circuits. However, in the current work, the focus is on parallel multipliers which are purely combinational circuits. Parallel multipliers are fairly complex circuits with a large transistor count and frequent switching of these transistors to carry out logic computations leads to large dynamic power dissipation. As elaborated in Section 3.2, parallel multipliers have the following computation steps: partial product generation, partial product reduction and vector merge addition. The partial product accumulation step, which predominantly comprises of adder units, dictates the overall computation delay, area and power consumption. An obvious technique to minimize power dissipation is to disable the unwanted computations in an adder. A number of methods to bypass the adders has been proposed and discussed in the literature [10–12].

#### 2.5.3 **Reconfigurable Binary Multiplier**

In a binary multiplier, the die area and power consumption are largely dependent upon the word-size. Assuming that an application needs N-bit precision, then using a data path element of more than the required precision would result in wasted area and power. To overcome this problem, a twin-precision multiplier has been proposed in [13]. An attempt has been made to minimize the impact on delay and power of the N-bit multiplier by making as few modifications as possible to the conventional multiplier. This twin-precision scheme decomposes the N\*N partial-product matrix into two N/2 \* N/2 independent multiplications by configuring the appropriate partial products [14]. When it operates on N/2-bit operands however, large parts of the multiplier do not contribute to the final result although they may be active. Thus, the multiplier dissipates considerable dynamic power due to the switching activity involved in computing unwanted partial products. This problem is sought to be addressed in this work by using bypass computation cells that disable unnecessary computations.

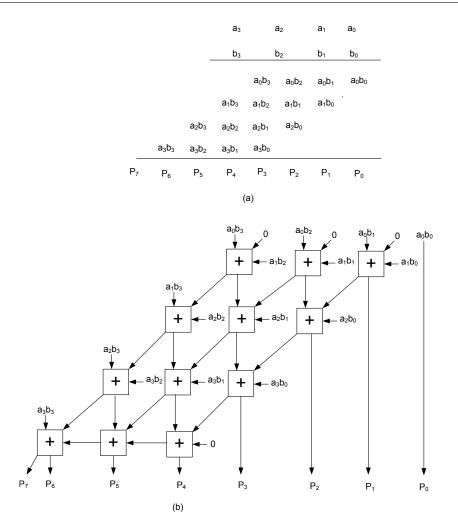

#### 2.5.4 A Review of Bypass Multiplier Architectures

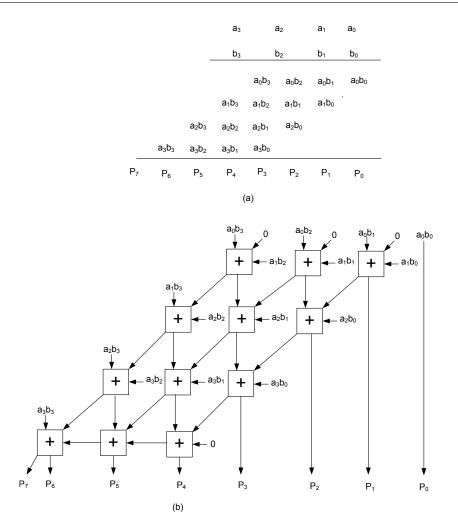

Figure.2.14(a) illustrates the example of multiplication of two unsigned 4-bit numbers, where  $A = a_3a_2a_1a_0$  is the multiplier and  $B = b_3b_2b_1b_0$  is the multiplicand. In a conventional Braun array multiplier for example, the partial products are generated in parallel with the AND gates and added using a 1-bit full adder as illustrated in Fig.2.14(b).

The adder circuits shown in Fig.2.14(b) tend to perform computation of the partial products even if their value is '0' and this results in undesired signal transitions. These transitions can be avoided by disabling the respective adder cells which results in saving of power.

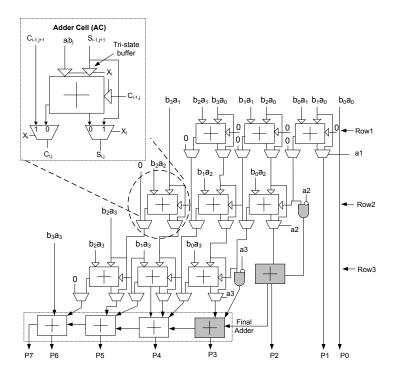

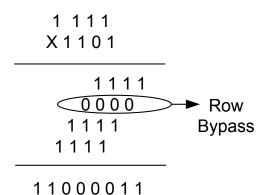

#### 2.5.4.1 Row-Bypass Scheme

Various techniques have been proposed from time to time to reduce the switching activity in array multipliers, of which bypass architectures are an offshoot. A simple approach to reduce the power consumption is to avoid unnecessary computations. Ohban [10] proposed a row-bypass scheme wherein some rows in the multiplier array are skipped to reduce the redundant switching activity. Figure 2.15 illustrates an implementation of a 4\*4 Braun multiplier using

Figure 2.14: (a) An example of 4\*4 array multiplication (b) Schematic diagram of 4\*4 Braun multiplier

row-bypassing technique.

This scheme includes adder cells (denoted by AC and highlighted in Fig.2.15) to bypass the inputs to output whenever the row (horizontal) partial product is zero. The tri-state buffers augmented at the inputs of the adder cell disable unnecessary transitions by shutting down the full adder. The MUXes at the outputs of the adder cells automatically pass the carry-input and the sum of the previous addition to the next computational unit when the corresponding partial product is zero. A notable drawback in this scheme however is the additional logic circuitry required as highlighted in grey color in Fig.2.15.

A numerical example illustrating the multiplication of two 4-bit numbers using row-bypass scheme is shown in Fig.2.16. Since the partial products in the second row are zeroes, the corresponding computational units are turned off to save power. The partial products in the

Figure 2.15: Schematic diagram of a 4\*4 Braun multiplier using row-bypassing technique

first row are bypassed and added with partial products in the next level (third row). In a similar manner, the remaining partial products are reduced to form the final product.

Figure 2.16: Numerical example of row-bypass scheme for 4\*4 multiplier

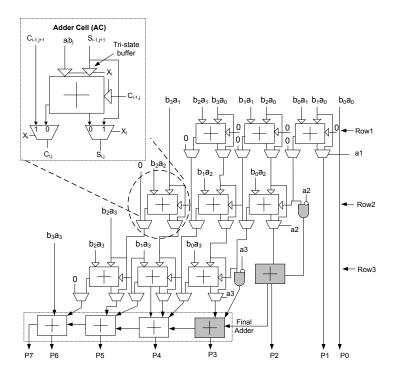

#### 2.5.4.2 Column-Bypass Scheme

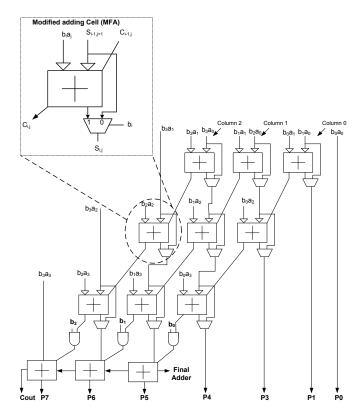

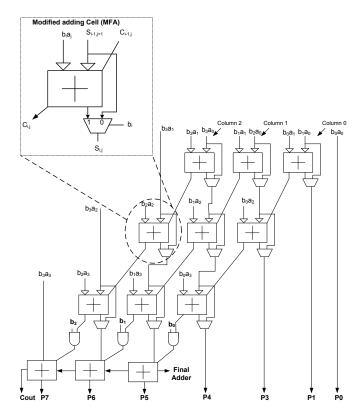

Wen [11] proposed a column-bypass scheme which avoids the adder operations in some columns instead of rows. In this approach, some columns in the partial product matrix can be skipped whenever their outputs are known. Consequently, the switching activity and therefore power dissipation are reduced. This technique has two important advantages: (i) It removes the extra compensating circuitry (ii) the modified full adder (MFA) unit is less complex than that used in

the row-bypassing multiplier.

A typical 4\*4 column-bypassing multiplier is illustrated in Fig.2.17 where the modified adder (MFA) cell is highlighted. The MFA cell skips the full adder whenever the partial product in the corresponding column is zero. This multiplier has less hardware complexity compared to the row-bypassing scheme also because it does not need to consider bypassing of the carry bit.

Figure 2.17: Schematic diagram of a 4\*4 Braun multiplier with column-bypassing scheme

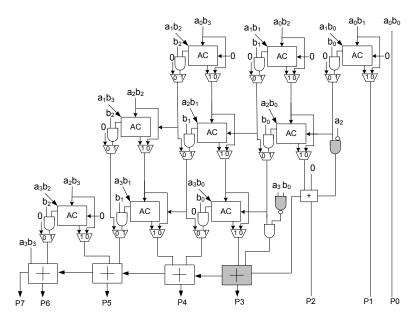

#### 2.5.4.3 Two-Dimensional Bypass Scheme

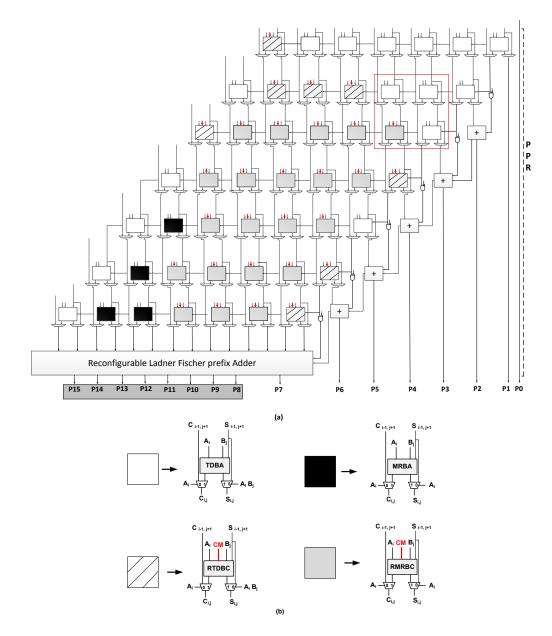

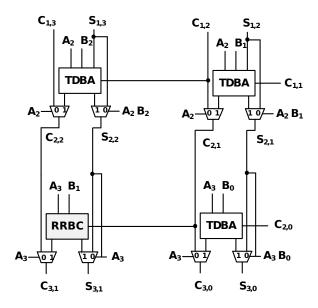

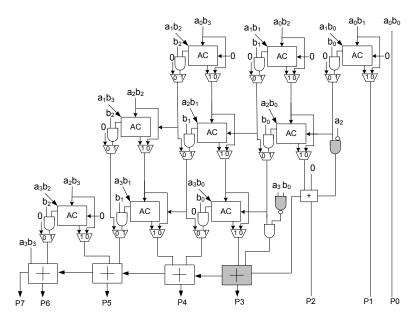

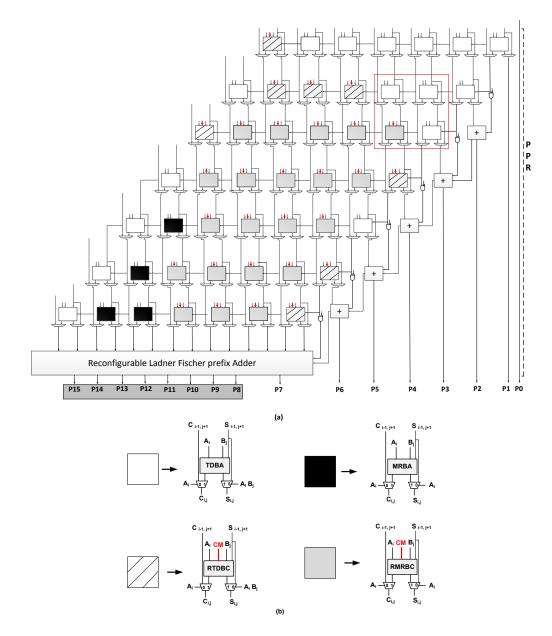

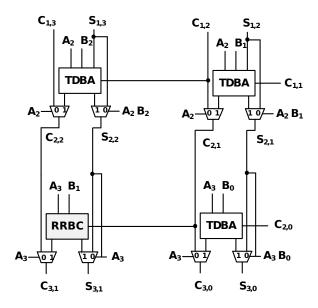

In a 2-dimensional bypassing multiplier, the computing logic cells skip the corresponding row and column depending on nullity of the partial products [12, 15]. Figure 2.18 shows the structure of the 4\*4 Braun multiplier with 2-dimensional bypassing scheme [12].

To overcome the conflict that occurs when both row-bypassing and column-bypassing appear simultaneously, bypass adder cells (AC) incorporate additional logic. These bypass cells have the capability to bypass when either row and/or column element is zero, however with large circuit overhead. In view of this additional complexity, power saving tend to get re-

Figure 2.18: Schematic diagram of a 4\*4 Braun multiplier with two-dimensional-bypassing scheme

duced. To overcome this, Hong [15] introduced two kinds of adder cells, namely, modified row-bypassing adder (MRBA) and two-dimensional bypassing adder (TDBA). The MRBA cells have row-bypassing capability while the TDBA cells are deactivated when either row or column partial product becomes zero.

# 2.6 A Review of Recursive Binary Multipliers

This section presents the mathematical modeling of the recursive binary multiplier. This is followed by various truncation schemes that have been used in the existing multiplier architectures.

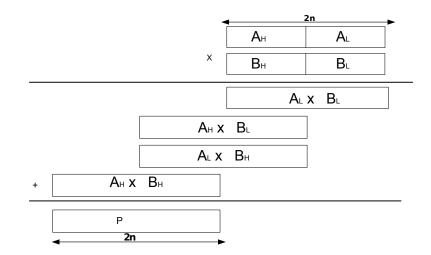

#### 2.6.1 Mathematical Analysis of Recursive Multiplier

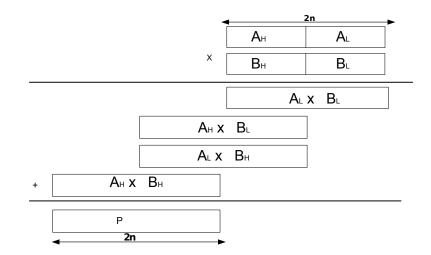

Recursive multipliers based on Karatsuba-Ofman Algorithm (KOA) [16] are found to have a hierarchical architecture consisting of several sub-multipliers making them ideal for fixedwidth multiplication.

Assume *A* and *B* to be two 2n-bit unsigned numbers, where *A* is the multiplicand and *B* is the multiplier. *A* and *B* can be written as:

$$A = \sum_{i=0}^{2n-1} a_i . 2^i \tag{2.18}$$

$$B = \sum_{j=0}^{2n-1} b_j . 2^j \tag{2.19}$$

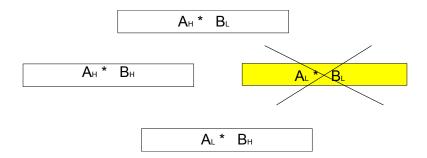

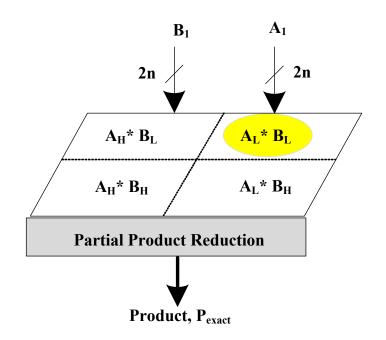

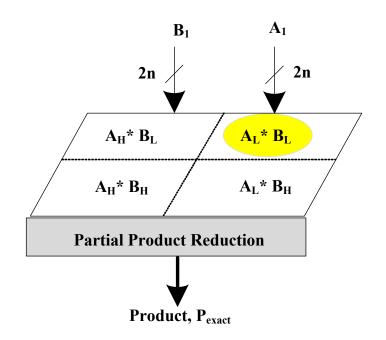

The recursive multiplication is performed by partitioning each of the operands into two equal portions of *n*-bit width. Based on this, the multiplicand (*A*) is split into  $A_H$  and  $A_L$ , while multiplier (*B*) is divided into  $B_H$  and  $B_L$  respectively as mentioned in equations 2.20 and 2.21 given below:

$$A = A_H * 2^n + A_L \tag{2.20}$$

$$B = B_H * 2^n + B_L \tag{2.21}$$

The subscript H denotes the most significant portion while L denotes the lower significant portion of the corresponding binary numbers.

The product (P) is written as follows:

$$P = A * B = (A_H * B_H) * 2^{2n} + (A_L * B_H + A_H * B_L) * 2^n + A_L * B_L$$

(2.22)

Thus, multiplication can be performed using four n \* n binary sub-multipliers, namely,  $A_H * B_H$ ,  $A_H * B_L$ ,  $A_L * B_H$ , and  $A_L * B_L$ , in parallel as shown in Fig.2.19. The partial products of all the individual sub-multipliers are reduced to product (*P*) of 2*n*-bit width using a reduction structure.

#### 2.6.2 Truncation Schemes for Binary Multipliers

Several techniques [17–20] have been proposed in the past to achieve fixed-width multiplication. Among these, truncation techniques developed for recursive multipliers have been proven to be efficient as opposed to the array multipliers in terms of die area and power dissipation [17].

Figure 2.19: Schematic diagram of the original recursive multiplication scheme

#### 2.6.2.1 Truncation Schemes for Array Multipliers

In truncation schemes for array multipliers, the least significant bits of the partial product matrix are removed and a correction function, which is either constant or data-dependent, is added to compensate for the error [21–24].

Authors in [21, 23] present a constant correction technique where compensation function is based on the average value of the partial product bits which are not formed. This technique results in simple hardware which in turn leads to higher power savings. However, the error bounds obtained are high. To overcome this, a data-dependent correction technique proposed in [22, 25] adds a correction value based on the partial products corresponding to least significant column that are not formed. This technique, also referred to as variable correction, achieves a lower error bound compared to the constant correction schemes, though at the cost of the hardware complexity.

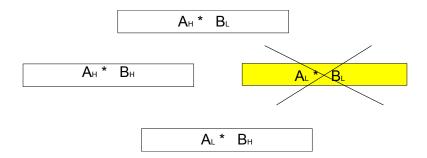

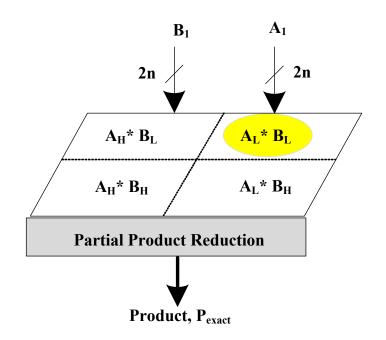

#### 2.6.2.2 Truncation Schemes for the Recursive Multiplier

Most of the truncation techniques targeted at array multipliers focus on modifying the multiplier structure. However, truncation schemes applied to recursive multipliers simply get rid of a least sub-multiplier ( $A_LB_L$ ) as shown in Fig.2.20 and replace it with a correction function which is data dependent.

Three correction schemes can be found in the literature. In scheme 1 [18],  $A_H * B_L$  or  $A_L * B_H$  sub-multiplier replaces  $A_L * B_L$  while in scheme 2, the average value of  $A_H * B_L$  and

Figure 2.20: Sub-multipliers in a recursive multipliers

$A_L * B_H$  is used. In scheme 3, the most significant partial product bit of  $A_L * B_L$ , namely,  $a_{n-1} * b_{n-1}$  forms the correction function. All these schemes are based on trial and error and the precision achieved is also fixed. In this work, a tunable correction function is proposed using a systematic approach and it's performance is compared with the existing ones.

# 2.7 Multipliers based on Logarithmic Number System

Most of the logarithmic multiplier schemes can be classified as iterative [26,27] or non-iterative [28–32]. Non-iterative multipliers have limited precision due to the usage of techniques such as piecewise linear approximation [33], memory look-up [34] or a combination of both [35] making them limited to only a few applications. On the other hand, iterative multipliers tend to improve the precision of the result with each successive iteration.

Mitchell [36] introduced the first iterative multiplier that was simple and flexible to meet the requirements of a wide range of applications. This multiplier however suffered from large relative error in the final result. Further, Mitchell approach cannot initiate next iteration until the completion of the present one. Babic [26] modified the Mitchell design by introducing greater pipeline-level parallelism with an objective to reduce the latency. However, his approach lead to reduced precision in each iteration due to the neglect of carry. Babic iterative multiplier (BIM) design was further improved by truncated error correction (TEC) method [27] which has an additional capability for speculative carry, thereby improving the precision. This however comes at the cost of area overhead.

To overcome these shortcomings, the present work combines carry speculation with an improved fractional predictor leading to a better precision when compared to the existing work. The fractional predictor logic and its efficient precomputation contribute to the improved overall precision due to a fewer number of iterations required compared to the existing techniques. Further, precision of the multiplier improves as the number of iterations increases. Also, savings in hardware are achieved using the truncation scheme proposed in this work. The proposed and the existing logarithmic multipliers have been applied on an image sharpening algorithm and compared in the context of certain well-known image processing benchmarks such as Lena and Cameraman for performance.

#### 2.7.1 Mathematical Analysis of MA Based Multiplier

This section presents the mathematical approach common for MA based multipliers [26,27,36] described below:

According to Mitchell, the binary representation of two n-bit input numbers  $N_1$  and  $N_2$  is given as :

$$\begin{cases} N_1 = 2^{k_1}(1+x_1) \\ N_2 = 2^{k_2}(1+x_2) \end{cases}$$

(2.23)

The characteristics of  $N_1$  and  $N_2$  are  $k_1$  and  $k_2$  respectively, representing the most significant operand bits with the value of '1'. Further,  $x_1$  and  $x_2$  denote fractional portions whose values lie in the range [0,1].

The base-2 logarithm of the product,  $N_1$  and  $N_2$  is written as

$$log_2(N_1 * N_2) = k_1 + k_2 + log_2(1 + x_1) + log_2(1 + x_2)$$

(2.24)

To compute the antilogarithm of equation (2.24), Mitchell proposed the following analytical expressions based on carry information from the fractional portion

$$N_1 * N_2 = 2^{k_1 + k_2} (1 + x_1 + x_2) + 2^{k_1 + k_2} (x_1 * x_2),$$

$$x_1 + x_2 < 1$$

(2.25)

and

$$N_1 * N_2 = 2^{k_1 + k_2 + 1} (x_1 + x_2) + 2^{k_1 + k_2} (x'_1 * x'_2),$$

$$x_1 + x_2 \ge 1$$

(2.26)