### Performance-aware Energy Management for Next Generation Processor and Cloud Computing Systems

Thesis

Submitted in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY**

by

Diyanesh Babu C. V. ID No. 2013PHXF0507H

Under the supervision of

Prof. M.B. Srinivas &

Under the Co-supervision of

#### Prof. Subhendu Kumar Sahoo

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI 2024

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI

## CERTIFICATE

This is to certify that the thesis entitled, **"Performance Aware Energy Management for Next Generation Processor and Cloud Computing Systems"** and submitted by **DIYANESH BABU C. V.** ID No. **2013PHXF0507H** in partial fulfillment of the requirements of Ph.D. of the Institute embodies original work done by him under my supervision.

MBMin

Signature of the Supervisor: Name in capital letters: M. B. SRINIVAS Designation: PROFESSOR

Date: May 10, 2024

Subhender kumar Sahoo

Signature of the Co-supervisor: Name in capital letters: SUBHENDU KUMAR SAHOO Designation: PROFESSOR

Date: May 10, 2024

"The difference between impossible and possible lies in a person's determination."

Swami Vivekananda

"The mind that opens up to a new idea never returns to its original size."

Albert Einstein

"Innovation distinguishes between a leader and a follower."

Steve Jobs

## Acknowledgements

First and foremost, I would like to express sincere gratitude to my supervisor, Prof. Dr. M.B. Srinivas for his help and valuable guidance, without which this work would not have been accomplished. Whenever I have required support or have hit a barrier in my research, his doors have always been open for advice. His unwavering support throughout the journey has been a constant source of encouragement. I would also like to thank my Co-supervisor, Prof. Dr. Subhendu Kumar Sahoo, Doctoral Advisory Committee (DAC), Prof. Dr. Subhendu Kumar Sahoo and Prof. Dr. Tathagata Ray, for their timely feedback and insightful comments. I also take this opportunity to thank Head of the Department of Electrical Engineering, Associate Prof. Dr. Alivelu Manga Parimi for the support and help extended to me.

I would like to express sincere thanks to co-authors Dr. Karthick Rajamani from IBM Cloud Infrastructure Operations group and Dr. Venkata Kalyan Tavva from IIT Ropar for their perseverance to work with me from the start and spending personal time. Life outside the campus is an important ingredient of PhD life and in this respect, I express my gratitude to my friend, colleague and PhD mate, Saravanan Sethuraman for his great support right from day one and during tough times.

Finally, my family has been my pillar of strength during these years. My deepest gratitude goes out to my father, mother, wife, my daughter and son, who have stood by me through thick and thin. I would like to express special thanks to my lovely wife Aswini, for her care, love and continued support has made this journey memorable.

## Abstract

Cloud computing has become an indispensable component of modern computing infrastructure, offering flexible and scalable services to users. However, the rapid growth of cloud computing has also led to concerns regarding energy consumption and carbon dioxide (CO2) emissions. The energy consumption of cloud data centers has a significant impact on CO2 emissions, as majority of electricity generation still relies on fossil fuels. According to a report by the International Energy Agency, data centers consumed around 200 TWh of electricity in 2018, accounting for around 1% of global electricity consumption [39]. The report also notes that data center energy consumption is expected to double by 2030 if no action is taken to improve energy efficiency. According to a study by A. Vakilinia and R. Buyya, cloud data centers are responsible for a significant portion of global CO2 emissions, with emissions expected to reach 3.2 gigatons by 2025 [40]. These trends highlight the need for energy-efficient cloud data center design and operation to mitigate the impact on the environment. In this thesis, we consider methodologies to address CPU and memory energy management challenges in cloud computing environments.

In first part of the thesis related to processor energy management, we present a highly accurate performance estimation methodology that accounts for architecture slack in workloads. Our work leverages the advanced instrumentation available in POWER8 processor that monitors core pipeline activity in relation to off-core memory accesses to build metrics for architecture slack characterization for workloads. Using these metrics, we construct a workload classifier that classifies workloads as core-bound and memory-bound and propose a performance prediction model for change in processor frequency for each class of workload - cPerf and mPerf, respectively. We evaluate these models with SPECCPU and PARSEC benchmark suites on a POWER8 based OpenPOWER system. We observe that the predicted performance with our models have high accuracy (97%) for both CPU and memory intensive benchmarks. We validate that the classifier is suitable to accurately classify phase of workloads during execution intervals. We propose an algorithm that uses classifier for phase classification and prediction models for performance estimation at runtime. We leverage this algorithm and evaluate the execution time impacts of CPU and memory classified benchmarks. Overall, our methods based on architecture slack as key metric can be adopted by newer DVFS algorithms for phase classification and performance estimation at runtime, with a very high accuracy.

Memory subsystems in cloud computing are also a significant contributor to energy consumption. A key research gap is the need for more efficient use of DRAM. DRAM is a key component of cloud computing systems, but it also consumes a significant amount of energy.

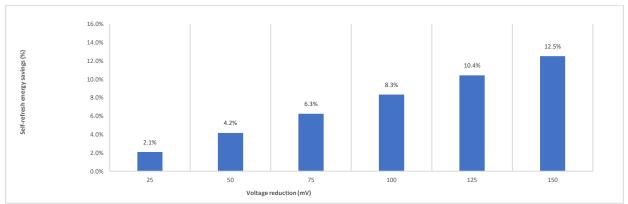

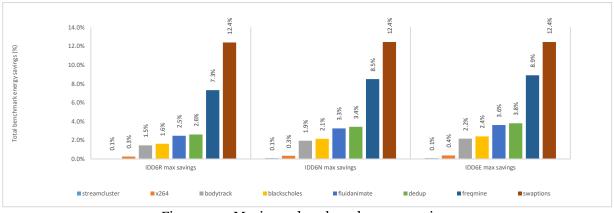

In second part of the thesis related to memory energy management, we propose a new power mode as Voltage Reduced Self-Refresh (VRSR), which is basically reduced DRAM voltage operation in self-refresh. Our simulation results show that there is a maximum of ~12.4% and an average of ~4% workload energy savings, with less than 0.7% performance loss across all benchmarks, for an aggressive voltage reduction of 150 mV. We perform a detailed study of reducing self-refresh energy by reducing the supply voltage. PARSEC benchmarks in Gem5 full-system mode are used to quantify the merit of self-refresh energy savings at reduced voltages for normal, reduced, and extended temperature ranges. The latency impacts of basic operations involved in self-refresh operation are evaluated using the 16 nm SPICE model. Possible limitations in extending the work to real hardware are also discussed. As a potential opportunity to motivate for future implementation, DRAM architectural changes, additional low power states and entry/exit flow to exercise reduced voltage operation in self-refresh mode are proposed.

## **Table of Contents**

### Table of Contents

| Table of  | Contents                                                                |

|-----------|-------------------------------------------------------------------------|

| List of T | ables11                                                                 |

| List of F | igures12                                                                |

| Abbrevia  | ations14                                                                |

| Introduo  | ction16                                                                 |

| 1.1       | Processor Energy Management17                                           |

| 1.2       | Memory Energy Management20                                              |

| 1.3       | Background 24                                                           |

| 1.4       | Motivation 28                                                           |

| 1.5       | Organization of the Thesis31                                            |

| Literatu  | re Survey                                                               |

|           | Workload Classification, Phase Classification and Performance<br>mation |

| 2.2       | Reducing DRAM Refresh Power Consumption                                 |

| Experim   | ental Setup                                                             |

| 3.1       | Experimental Setup for Architecture Slack Exploitation                  |

| 3.2       | Experimental Setup for Study of Self-Refresh Energy Savings             |

|                  | ck Exploitation for Phase Classification and Performance<br>41          |

|------------------|-------------------------------------------------------------------------|

| 4.1 Worklo       | ad Classification of Benchmarks41                                       |

| 4.2 Perform      | nance Estimation Models 47                                              |

| 4.3 Phase (      | Classification at Runtime49                                             |

| 4.4 Perform      | nance Evaluation of Benchmarks 50                                       |

| 4.5 Results      | and Discussion 53                                                       |

| 0                | l Self Refresh (VRSR) for Optimized Energy Savings in DRAM<br>          |

| 5.1 Impact       | of Reduced Voltage and Temperature on Self-refresh                      |

| 5.2 Latency      | v Evaluation with SPICE Model68                                         |

| 5.3 Propos       | ed architectural changes for practical implementation                   |

|                  | tative evaluation of performance overhead due to voltage reduced 73     |

| 5.1Results and   | Discussion                                                              |

| Conclusion and F | uture Work80                                                            |

|                  | cture Slack Exploitation for Phase Classification and Performance<br>80 |

|                  | Reduced Self Refresh (VRSR) for Optimized Energy Savings in DRAM<br>    |

| Bibliography     |                                                                         |

| List of Publicat | tions                                                                   |

| Brief Biograph   | y of the Candidate                                                      |

| Brief Biography of the Supervisor    |    |  |

|--------------------------------------|----|--|

|                                      |    |  |

| Brief Biography of the Co-Supervisor | 98 |  |

## **List of Tables**

| Table 1.1: Power saving features in self-refresh mode                                     |

|-------------------------------------------------------------------------------------------|

| Table 3.1: Simulation setup    39                                                         |

| Table 3.2: Power and timing parameters based on DDR4-2400 8 Gbit device [42]         39   |

| Table 3.3: DRAM energy components                                                         |

| Table 4.1: Events tracked for Performance Management                                      |

| Table 4.2: Parameters mipsr(normalized), Wb(normalized) values                            |

| Table 4.3: Benchmarks – Performance impact study                                          |

| Table 5.1: Resistances and capacitances in DRAM [41]    68                                |

| Table 5.2: Summary of resistance and capacitor changes                                    |

| Table 5.3: Summary of 45 nm and 16 nm transistor dimensions    69                         |

| Table 5.4: Latency values obtained from 16 nm SPICE model simulation    70                |

| Table 5.5: Mode register setting to select self-refresh mode                              |

| Table 5.6: Refresh cycle time for reduced voltages    74                                  |

| Table 5.7: Refresh cycle time and exit latency for reduced voltages                       |

| Table 5.8: Execution time increase of benchmarks at reduced voltage (1.050 V) compared to |

| nominal voltage (1.2 V)77                                                                 |

| Table 5.9: Maximum self-refresh energy savings (mJ) at 150 mV voltage reduction           |

# **List of Figures**

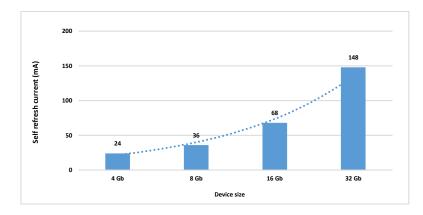

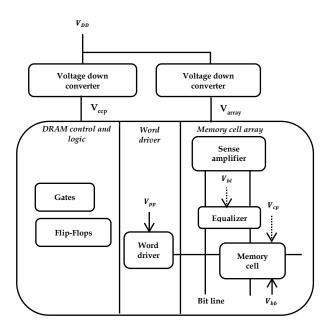

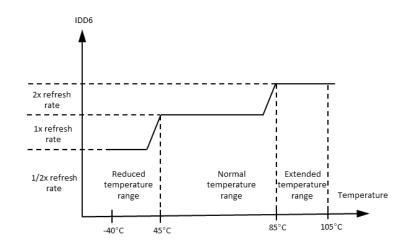

| Figure 1.1: Self-refresh current (IDD6) increase trend in DDR4x devices                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

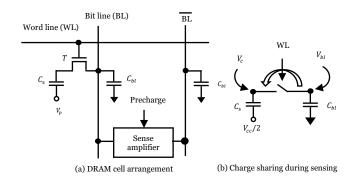

| Figure 1.2: DRAM cell and charge access scheme                                                                                                                     |

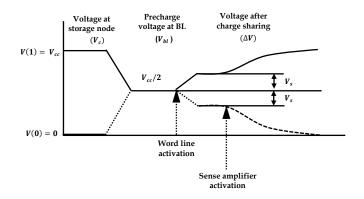

| Figure 1.3: Storage node, bit line and charge sharing voltages                                                                                                     |

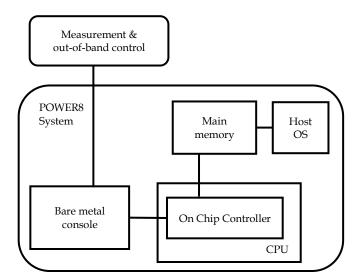

| Figure 3.1: Measurement setup                                                                                                                                      |

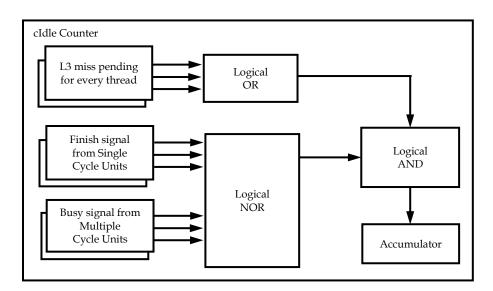

| Figure 4.1: Hardware implementation of <i>cIdle</i> counter                                                                                                        |

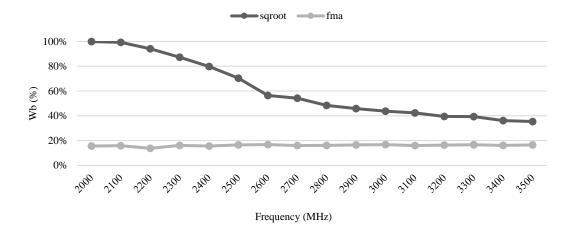

| Figure 4.2: Wb (MIPS to stalls ratio) for custom core-bound benchmarks                                                                                             |

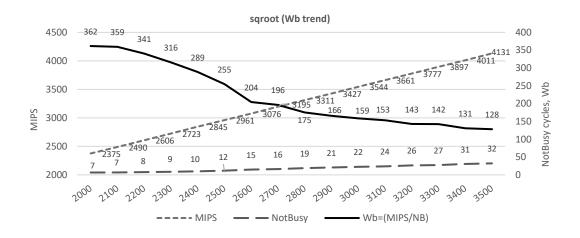

| Figure 4.3: Detailed Wb trend for sqroot core-bound benchmark                                                                                                      |

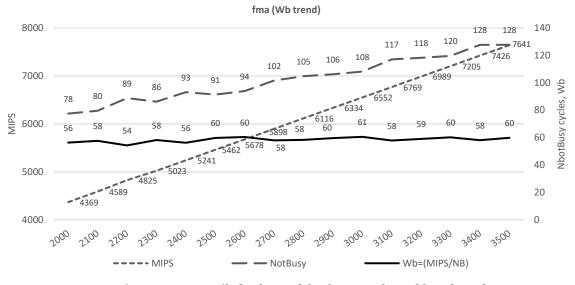

| Figure 4.4: Detailed Wb trend for fma core-bound benchmark                                                                                                         |

| Figure 4.5: Wb (MIPS to stalls ratio) for custom memory-bound benchmarks                                                                                           |

| Figure 4.6: Compute and memory regression models for mipsr estimate at 3.5 GHz target                                                                              |

| frequency                                                                                                                                                          |

| Figure 4.7: Compute and memory regression models for mipsr estimate at 2 GHz target frequency                                                                      |

|                                                                                                                                                                    |

| Figure 4.8: Performance prediction scheme51                                                                                                                        |

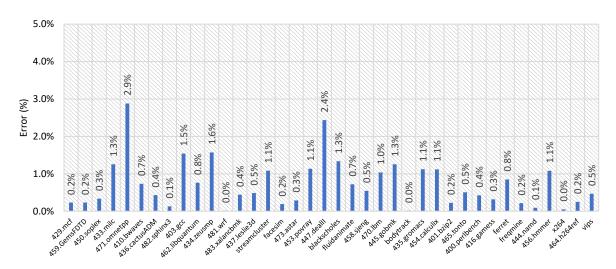

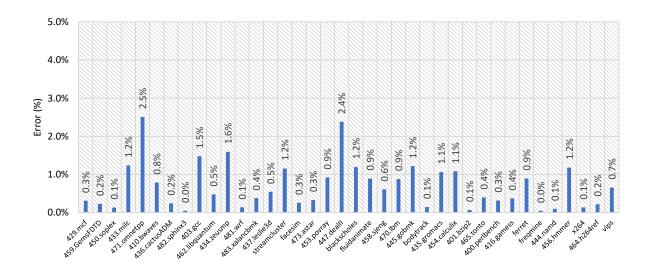

| Figure 4.9: MIPS predicted (using models) vs measured error at 3.5 GHz                                                                                             |

| Figure 4.10: MIPS predicted (using models) vs measured error at 2 GHz 55                                                                                           |

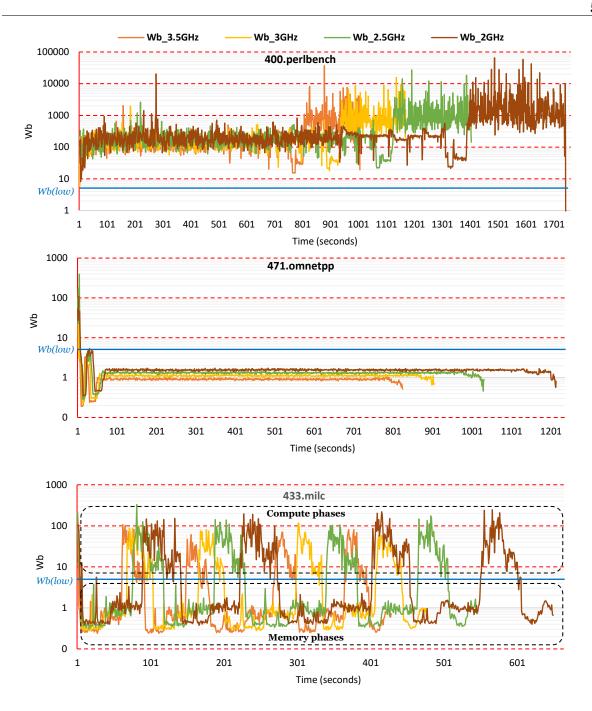

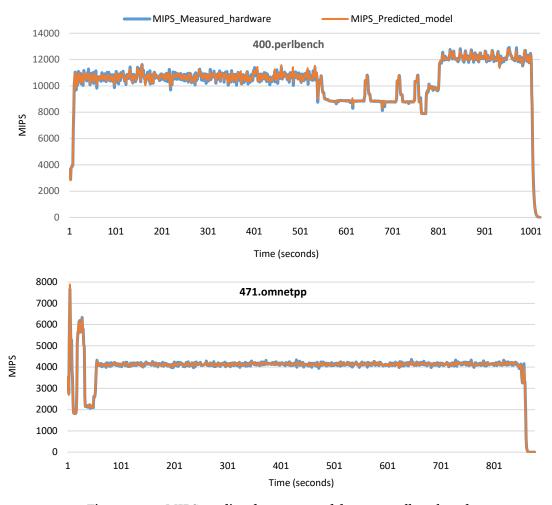

| Figure 4.11: Runtime phase characteristics of 400.perlbench, 471.omnetpp and 433.milc                                                                              |

| benchmarks                                                                                                                                                         |

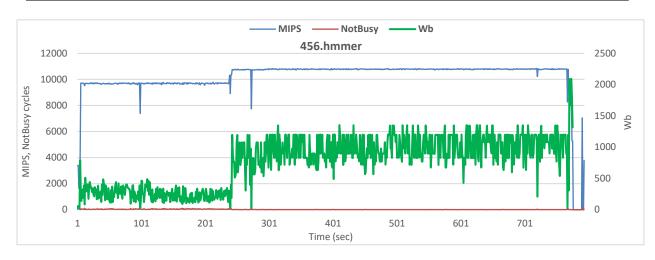

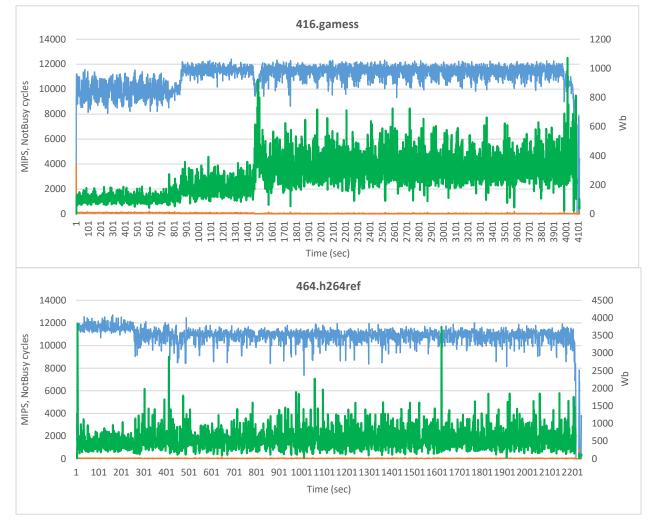

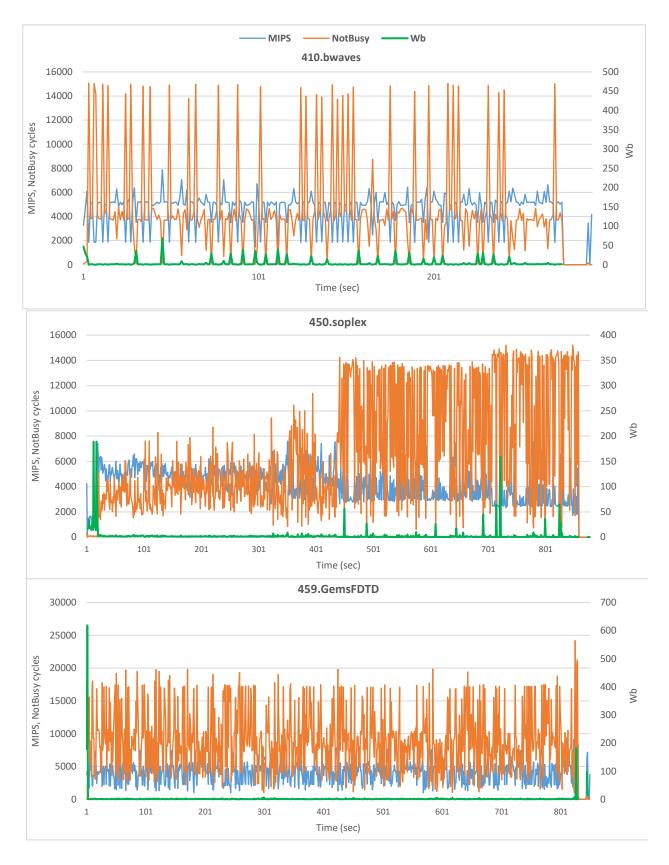

| Figure 4.12: MIPS, NotBusy & Wb characteristics of core-benchmarks (456.hmmer, 464.h264ref                                                                         |

| and 416.gamess) 59                                                                                                                                                 |

| Figure 4.13: MIPS, NotBusy & Wb characteristics of memory-benchmarks (410.bwaves, 450.soplex                                                                       |

| and 459.GemsFDTD)60                                                                                                                                                |

|                                                                                                                                                                    |

| Figure 4.14: MIPS predicted vs measured for 400.perlbench and 471.omnetpp benchmarks61                                                                             |

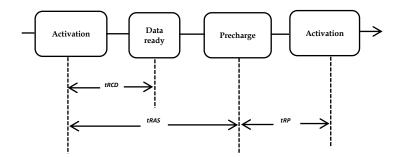

| Figure 4.14: MIPS predicted vs measured for 400.perlbench and 471.omnetpp benchmarks61<br>Figure 5.1: Timing parameters associated with refresh operation of a row |

|                                                                                                                                                                    |

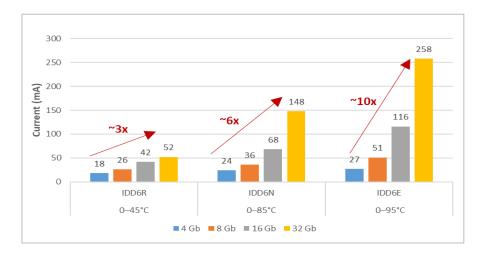

| Figure 5.4: Self-refresh power trend in DDR4 devices at different capacities [42], [8-10]65 |

|---------------------------------------------------------------------------------------------|

| Figure 5.5: Comparison of energy breakdown between active and power-down modes              |

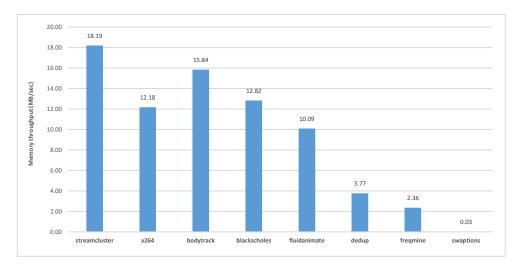

| Figure 5.6: Memory throughput comparison                                                    |

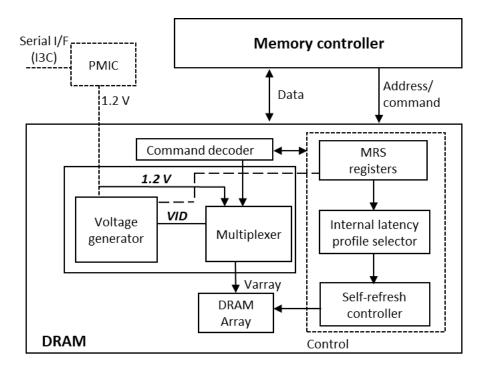

| Figure 5.7: Proposed DRAM architecture changes for reduced DRAM voltage operation in self-  |

| refresh mode71                                                                              |

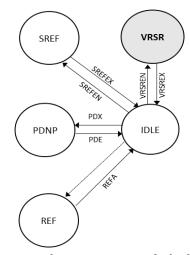

| Figure 5.8: State diagram of DRAM commands for low-Power modes, according to JEDEC          |

| (proposed modes are highlighted in grey)72                                                  |

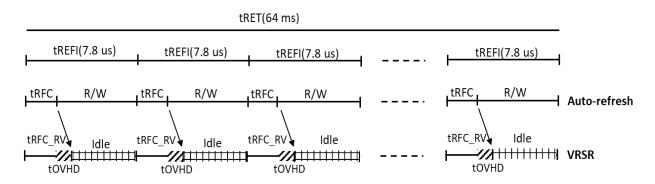

| Figure 5.9: Refresh cycle time (tRFC_VR) in VRSR scheme73                                   |

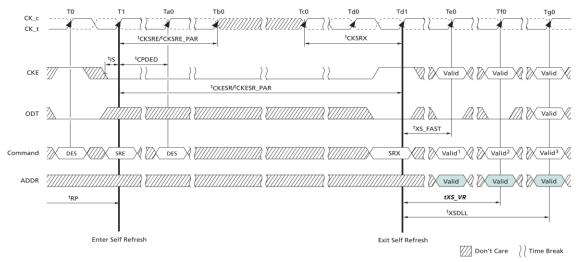

| Figure 5.10: Exit timing latency of VRSR (tXS_VR) with reference to self-refresh [42]74     |

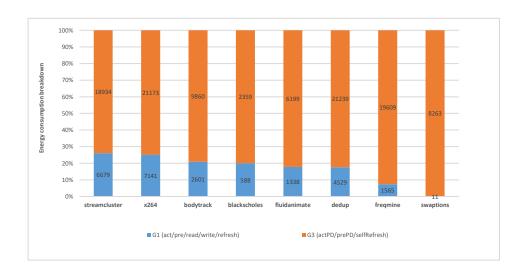

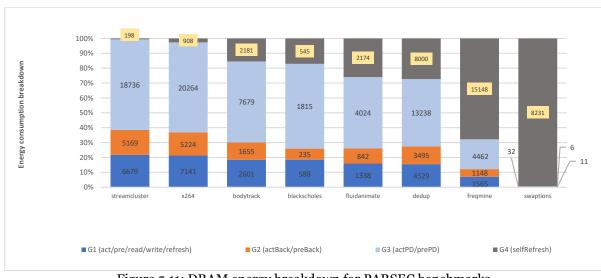

| Figure 5.11: DRAM energy breakdown for PARSEC benchmarks                                    |

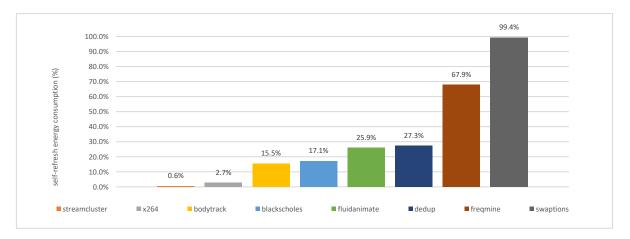

| Figure 5.12: Self-refresh energy (%) contribution to total energy76                         |

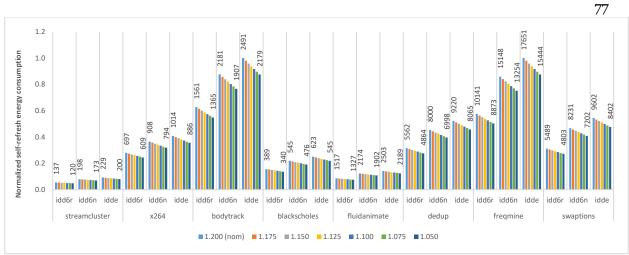

| Figure 5.13: Self-refresh energy at reduced voltages and different temperature ranges77     |

| Figure 5.14: Self-refresh energy savings with voltage reduction77                           |

| Figure 5.15: Maximum benchmark energy savings77                                             |

## Abbreviations

AVATAR - A Variable-Retention-Time (VRT) Aware Refresh for DRAM Systems **BL** - Bit Line CLARA - Circular Linked-List Auto and Self Refresh Architecture **CPU** – Central Processing Unit DDR3L - Double Data Rate 3 Low Voltage DDR4 - Double Data Rate 4 **DIMM -** Dual In line Memory Module **DPD** - Data Pattern Dependencies **DPD** - Deep Power-Down **DRAM** - Dynamic Random-Access Memory **DSR** - Deep Self-Refresh **DVFS** - Dynamic Voltage and Frequency Scaling eDRAM - Embedded Dynamic Random Access Memory **JEDEC** - Joint Electron Device Engineering Council LPASR - Low Power Auto Self Refresh LPDDR - Low Power Double Data Rate LSR - Long latency Self-Refresh MIPS - Millions of Instructions Per Second MRPI - Memory Reads Per Instruction MRS - Mode Register Set **PDNA** - Active Power-Down **PDNP** - Precharge Power-Down **PMU** - Performance Monitoring Unit PTM - Predictive Technology Model **RAIDR** - Retention-Aware Intelligent DRAM Refresh **RAPID** - Retention-aware intelligent DRAM refresh **RDIMM** - Registered Dual In-Line Memory Module SRAM - Static Random-Access Memory **SREF** - Self-Refresh **TCSR** - Temperature Compensated Self Refresh **tRAS** – Active to Precharge Delay tRFC - Refresh cycle time VID - Voltage ID **VRT** - Variable Retention Time WL - Word Line

Dedicate this to my parents, wife, daughter, and son

### **Chapter 1**

## Introduction

In this chapter, we provide a brief introduction about processor and memory energy management in the context of cloud computing domain. We discuss their significance in reducing energy consumption and optimizing performance of systems.

Processor energy management is a critical aspect of cloud computing. In a cloud computing environment, multiple virtual machines run on a single physical server, and managing the energy consumption of each processor is crucial to maintain the overall system's efficiency.

Processor energy management techniques can be classified into two categories: dynamic voltage and frequency scaling (DVFS) and workload consolidation. DVFS adjusts the voltage and frequency of the processor to match the workload's requirements, while workload consolidation consolidates multiple workloads onto a single processor. DVFS can significantly reduce energy consumption by lowering the processor's voltage and frequency when the workload is low and increasing them when the workload is high. However, it can also affect the system's performance if the processor's frequency is reduced too much. Workload consolidation, on the other hand, can reduce energy consumption by consolidating multiple workloads onto a single processor, but it can also increase the system's response time.

First part of work focus on how architecture slack of workloads can be exploited for accurate performance management using DVFS technique.

Memory energy management is a critical aspect of cloud computing systems, as memory

accounts for a significant portion of a system's energy consumption. Dynamic random-access memory (DRAM) is the primary type of memory used in modern cloud computing systems, and DRAM self-refresh will be effective to maintain data integrity when the DRAM memory cells were not accessed. However, DRAM self-refresh also consumes a significant amount of energy and managing its energy consumption is crucial for reducing overall system energy consumption.

There are several primary techniques are commonly used to reduce DRAM self-refresh energy consumption in cloud computing systems, including:

Power Gating: Power gating is a technique that shuts off power to unused portions of the DRAM chip. This technique can significantly reduce DRAM self-refresh energy consumption by reducing power consumption in idle memory areas.

Temperature-aware Self-refresh: Temperature-aware self-refresh is a technique that adjusts the self-refresh rate of the DRAM based on the memory temperature. This technique can reduce DRAM self-refresh energy consumption by reducing the number of self-refresh operations needed at lower temperatures.

Adaptive Self-refresh: Adaptive self-refresh is a technique that adjusts the self-refresh rate of the DRAM based on the memory's usage patterns. This technique can reduce DRAM selfrefresh energy consumption by reducing the number of unnecessary self-refresh operations.

Data Compression: Data compression is a technique that reduces the amount of data stored in memory by compressing it. This technique can reduce DRAM self-refresh energy consumption by reducing the amount of data that needs to be refreshed.

Second part of work focus on achieving self-refresh energy savings at reduced DRAM voltages.

#### **1.1 Processor Energy Management**

In recent years, power and thermal issues have become primary design constraints for highperformance system designs. Restrictions arise from increased transistor densities and clock speeds, hindering the potential performance improvements and escalating expenses in development, acquisition, and operations. Consequently, there is a growing emphasis on effectively managing energy consumption and heat dissipation in high-performance

computer systems [9,20,28].

Energy and thermal management are important for many reasons. First, to avoid employing performance crippling conservative designs to ensure that power and thermal caps are never exceeded, high-end systems employ active power and thermal management. Increasingly the cost of providing the power and cooling infrastructure for a datacenter or supercomputer approaches or exceeds the cost of the machines themselves. In many locations, electric utilities are unwilling to provide the additional power needed to add new machines to datacenters. Organizations also face external pressures to become "greener". In the United States, both the Environmental Protection Agency and Department of Energy are issuing guidelines for energy-efficient systems and data centers [35,36]. An increasing number of customers insists that computers be energy-efficient [38], while still expecting performance improvements.

As the goal is to balance high performance with energy efficiency, power management becomes a strategic approach that involves leveraging opportunities to operate system components at lower power states without compromising performance. "Slack" refers to any characteristic that enables a system to operate a certain portion of itself at a lower power state while still meeting predefined performance objectives.

There are three forms of slack present in server computing environments: workload slack, user-demand slack, and architecture slack.

- Workload slack occurs when the workload is waiting on I/O or CPU does not have instructions to execute. It can be readily measured by monitoring the number of cycles in a given interval that the core is not yielded by the workload or operating system.

- **User-demand slack** occurs when systems can be run at less than full speed, but still achieve user performance requirements. It needs to be explicitly communicated

to the system (low-power mode, favor energy savings etc).

• Architecture slack arises when a workload's performance is bounded at least partially by a resource other than the processor clock frequency, e.g., by limited memory bandwidth. In this work, we focus on architecture slack present in server computing environments.

In a high-performance server system, it is common to find multiple processors that facilitate the simultaneous execution of multiple workloads. In both commercial and technical computing environments, one key objective is to maximize processor usage to speed up the execution of workloads for effective utilization of hardware resources. Another equally important key objective is to minimize energy usage, while maintaining high performance of workloads under execution.

Typically, a server class processor has many cores, and each core can support multiple hardware threads (multi-threading) for concurrent execution of workloads. Each process running on a hardware thread can have following different performance characteristics related to its current operating frequency: compute, memory, or moderate bound. For compute-bound processes, performance tracks linearly with processor core frequency and therefore limited by CPU speed. In the case of memory-bound processes, performance is unaffected by the frequency of the processor core. Instead, it is constrained by factors such as memory bandwidth and latency, which are not directly related to the speed of the CPU.

When a process runs on a hardware thread, it can execute core-bound or memory-intensive operations within a specific timeframe, referred to as a "phase." Core-bound operations can be completed within the core itself, without needing external resources. On the other hand, non-core-bound operations rely on external resources for completion. Typically, core-bound operations involve high-latency instructions that have a higher chance of causing processor pipeline delays. For example, retrieving data from on-chip L2 and L3 caches can have moderately long latencies of 8-60 cycles, while accessing DRAM can result in even longer latencies (e.g., 200+ cycles). To enhance performance during such scenarios, instruction-level parallelism (ILP) allows overlapping execution of multiple instructions using the same

circuitry. However, there are cases where an instruction in the pipeline depends on the completion of a previous instruction, creating dependencies. Due to this, the core must wait until producer instruction is completed and this leads to idle cycles or stalls. There can be many such idle scenarios in modern pipelines that support simultaneous multi-threading (SMT). SMT refers to the capability of a single physical processor core to execute instructions from multiple hardware thread contexts concurrently. This allows the processor core to read and execute instructions in parallel, enabling scheduling of multiple applications simultaneously on the same core. In one situation, if a core is waiting for the outcome of memory access requests from outside the core and is not executing any operations from other threads, it is considered idle. In another scenario, if a core is waiting for the result of memory access requests from outside the core and not completing any execution threads during a cycle, the processor core is deemed idle and non-operational. When a core is both idle and waiting for off-core memory access, it indicates that there is available capacity or slack within the computer system. The presence of slack results in idle cycles, and if the processor is already operating at its maximum frequency, these cycles are essentially lost. These unused cycles are known as the "architectural slack" of the processor. To optimize performance, frequency reductions can be applied during these cycles without impacting overall performance.

#### **1.2** Memory Energy Management

Data centers rank among the largest consumers of electrical power, accounting for around 200 terawatt-hours (TWh) of electricity consumption, which is nearly 1% of the global electricity demand. This substantial energy usage contributes to approximately 0.3% of global CO2 emissions [85]. Be it on-premise or in the cloud, demand for servers has been skyrocketing due to ever growing computing needs and big data explosion. However, around 30 percent of servers are either underutilized or completely idle, as per previous research performed by the uptime institute [86].

Currently, the CPU stands as the most power-intensive element within a server, while memory holds the position as the server's second most significant consumer of power [87]. In a server, main memory capacity and bandwidth requirements continue to grow, year over year. Modern data intensive applications from emerging areas like cloud computing, artificial intelligence, machine learning, augmented reality, geonomics and accelerated computing have clearly necessitated high capacity and low latency memory for superior performance. Due to its distinct benefits of low latency, high density, and well-established fabrication process, DRAM technology remains the favored option for main memory. DRAM energy usage makes up approximately 46% of the total energy consumption in a system [57, 88]. Specifically, in a multicore processor executing a collection of parallel applications with high memory demands, the DRAM core alone consumes roughly 20% of the overall system energy [50].

A DRAM cell consists of an access transistor and a capacitor, where the capacitor serves as a storage unit for data in the form of electrical charge. However, it is important to note that the capacitor gradually loses charge over time due to leakage. Refresh is an essential operation to ensure data retention in DRAM memories. However, it adversely impacts power dissipation and performance. With growing DRAM chip density, refresh power consumption has become significant portion of the total device energy [41].

Industry standard DRAM devices support auto-refresh and self-refresh modes to perform the refresh operation, during active and idle scenarios respectively. Memory controller must issue refresh commands periodically interleaved with the core's read & write data to the DRAM device and it is referred to as auto-refresh.

Once the read and write queues of the controller remain empty for a specific duration, it instructs the DRAM to transition into a low power mode. Self-refresh is an energy-saving mode that can be achieved without compromising the integrity of the data, making it the most power-efficient state. In this mode, the DRAM device performs refresh operation using an inbuilt timer, whereas DLL, clocks and IO pins are all turned off to save the background power. This mode can be exercised to achieve good energy savings during moderate or long idle phases of workloads. increasingly significant. A review of literature reveals that in DDR4x devices (as depicted in Figure 1.1), when memory size doubles, such as from 4 Gb to 8 Gb, 8 Gb to 16 Gb, and 16 Gb to 32 Gb, there is a corresponding increase in self-refresh current (IDD6) of 50%, 89%, and 118% respectively [42], [48-50].

Figure 1.1: Self-refresh current (IDD6) increase trend in DDR4x devices

Extensive research has been conducted to minimize power consumption during refresh operations. Chang et al. [43] conducted a thorough investigation focusing on DDR3L DRAMs. Their study primarily involved characterizing the behavior of the DRAM chip when operated at reduced voltages below the nominal value. They examined the impact of low DRAM supply voltages of 1.2 V and 1.15 V, compared to the nominal value of 1.35 V, across various retention times (64 ms, 128 ms, 256 ms, 512 ms, 1024 ms, 1536 ms, and 2048 ms) on DDR3L DIMMs at temperatures of 20°C and 70°C. The study revealed that no weak cells were observed when the supply voltage was reduced up to a retention time of 512 ms, which is eight times the standard refresh interval of 64 ms. Consequently, the researchers concluded that at these temperatures, a reduction in supply voltage does not necessitate any modifications to the standard refresh interval. Furthermore, their work demonstrated that bit errors resulting from reduced voltage operation could be mitigated by increasing the latency of row activation (tRAS), restoration (tRCD), and precharge (tRP) operations.

Pardeik et al. have proposed to minimize the refresh power consumption by increasing the refresh rate and reducing the DRAM supply voltage during long idle scenarios [44]. Their work involved power evaluation of 16 GB & 32 GB DDR4 RDIMM modules at different refresh rates 2x, 4x, 8x and multiple voltages 1.25 V, 1.2 V, 1.15 V, 1.1 V, 1.05 V, 1 V. Their

characterization results revealed a key finding that, on both 16 GB and 32 GB DIMMs, the voltage reduction of 200 mV, 1.25 V nominal to 1.05 V yielded significant power savings, despite of increased refresh rates. They observed 30%, 28%, 26%, 24% power savings for different refresh rates 7.8(1x), 3.9(2x), 1.94(3x), 0.96(4x) respectively, without any data integrity errors.

Byoungchan et al. [60] conducted a study where they observed that DRAM cells in the selfrefresh mode operate in two distinct modes: static (idle) and dynamic (refreshing), and the transition between these modes follows a predictable pattern. They proposed a novel approach to optimize the leakage current of DRAM cells by aligning the word-line and body voltage levels with the cell's state. Their objective was to enhance the power efficiency of DRAM, leading to the introduction of two new self-refresh modes: Enhanced Self-Refresh (ESR) and Long Latency Self-Refresh (LSR). Through simulations, they demonstrated that the retention time of DRAM cells improved by 2.42 times in the ESR mode and 3.58 times in the LSR mode. Leveraging the extended retention time, their approach involved applying a reduced refresh rate while maintaining improved leakage current. The ESR mode could directly replace the original self-refresh mode without requiring modifications to the memory controller. It employed a selective word-line bias technique, which necessitated two transistors per sub-array to independently control the voltage level of individual sub-arrays. On the other hand, the LSR mode represented a new power-saving mode with even higher efficiency than the ESR mode. However, due to its distinct exit latency compared to selfrefresh, it required adjustments to the memory controller. In addition to selective word-line bias, the LSR mode employed selective body biasing to achieve further power savings.

Existing literature [43, 44] motivates us to investigate energy savings in self-refresh mode at lower DRAM voltages. We observe that the basic idea in [43] explores energy saving opportunities with auto-refresh during memory mainline read & write operation, while our work is orthogonal that focus on self-refresh mode exercised during long idle times. In contrast to [44], we further extend our studies to lower voltage operation at reduced and increased self-refresh rates associated with wider temperature ranges, as supported by DDR standards. For lowering DRAM voltage during self-refresh, we consider the implementation of varying array voltage (Varray) in step sizes without modifying standard refresh rates, which is orthogonal to work [60] that uses selective body bios and selective word-line bios controls to attain the increased retention time thereby to lower the refresh rates for energy savings. Reducing voltage during self-refresh needs additional latency cycles of tRAS and tRP parameters for error free operation [43]. We quantify the performance impact seen by workloads with such increased latency cycles.

In our research, we investigate the necessary modifications to both the DRAM and controller to implement the proposed energy-saving feature. We provide a comprehensive description of the interaction flow between the controller and DRAM, focusing on the newly suggested architectural changes. To maximize the effectiveness of our approach, it can be combined with the findings of previous studies, such as [43] and [60]. As a result, we introduce a new low power mode for DRAM called "voltage reduced self-refresh operation (VRSR)."

#### 1.3 Background

## **1.3.1** Processor – Architecture slack exploitation for performance management

While previous research [5,10,18,32,33] extensively explores the utilization of slack and its applications, we have identified a gap in leveraging architecture slack for performance management. Fields et al. [10] introduce the concept of slack and its exploitation in the design of a processor with heterogeneous pipeline implementations. Our work complements theirs by developing methods for highly accurate performance prediction. Liang et al. [18] propose a cache-miss based prediction model for energy and performance degradation, while Spiliopoulos et al. [32] present a slack time-based model. However, these approaches do not consider architecture slack. In contrast, Hari et al. [5] propose a method to exploit timing slack in embedded applications. Their approach relies on the execution of an application that avoids the processor's static critical paths, enabling energy savings by scaling down the processor's voltage while maintaining the same frequency until the longest active paths meet

the timing constraints. However, this approach requires profiling applications prior to execution, resulting in significant overhead. Similarly, Sharanyan et al. [33] propose a multicore CPU scheduler that combines traffic sources, latency tolerance, and computational resource requirements. They utilize "CPU stall cycles on cache misses" as a key metric to colocate threads on the same socket or physical core for improved parallel efficiency. Our work aims to bridge the gap by focusing on exploiting architectural slack for performance management, providing a novel approach that complements existing research in this area.

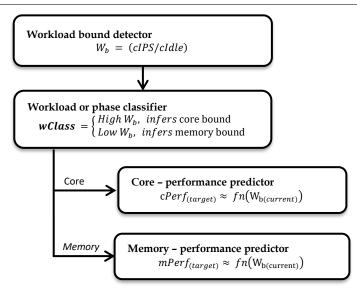

We refer "workload classification" as detecting whether the workload is compute-bound or memory-bound. In our current work, we propose a fixed interval-based online "phase classification" scheme that uses microarchitecture-dependent metrics (instruction throughput and not-busy cycles) obtained from hardware counters. "Performance estimation" is a measure of frequency-performance relationship at target frequency with respect to its current frequency-performance setting, for a given workload under execution.

#### 1.3.2 Memory – Voltage Reduced Self-Refresh operation

JEDEC (Joint Electron Device Engineering Council) supports many features to optimize selfrefresh power (Table 1.1). Low-Power Auto Self Refresh (LPASR) and Temperature Compensated Self Refresh (TCSR) are features that adjusts refresh rate depending on the ambient temperature in DDR4x and mobile LPDDRx devices respectively. The Partial Array Self Refresh (PASR) feature allows the controller to choose the specific portion of memory arrays that need to be refreshed during self-refresh in LPDDRx. By combining the TCSR and PASR features, even more significant power savings can be achieved [41].

| Counter                    | Description                                         | Technique                                                                                |

|----------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------|

| DDR4x                      | Low-Power Auto Self<br>Refresh (LPASR) [42]         | Refresh rate is adjusted based on temperature                                            |

| Low Power DDRx<br>(LPDDRx) | Temperature Compensated<br>Self Refresh (TCSR) [47] | Refresh rate is adjusted<br>based on temperature                                         |

| LPDDRx                     | Partial Array Self Refresh<br>(PASR) [47]           | Refresh operation is limited<br>to portion of the memory's<br>array where data is stored |

The JEDEC standard defines the Deep Power-Down (DPD) mode as the most extreme powersaving state, where the entire memory array in the device is shut down. In DPD mode, all internal voltage generators are halted, resulting in the loss of all data stored in the memory. This mode proves beneficial in mobile applications where continuous data retention in DRAM is not necessary for most of the time. Additionally, a technique called Deep Self-Refresh (DSR) exists, which combines the power-saving advantages of Partial Array Self Refresh (PASR) and DPD [51]. While PASR keeps the internal voltage generators of the DRAM in a low-power mode, DSR allows the unused banks of memory cells to enter the DPD state. It is important to note that although DPD offers even lower energy consumption in self-refresh mode compared to PASR, it is not included in the JEDEC standard. In our work, we focus on reducing DRAM energy consumption by lowering the DRAM supply voltage in the normal self-refresh mode, without the need for additional power-saving modes like DPD or DSR. Our work reported has the following key take aways:

(a) A survey of current techniques to optimize power in self-refresh mode is initially presented. The main cause for power consumption in self-refresh is also described. Further, voltage is proposed as a potential knob to minimize the power consumption. Some of the recent work [43, 44] on comprehensive study & characterization of DRAM data retention ability at lower voltages, wide temperature ranges and refresh rates are presented and discussed. The self-refresh energy scaling trends in modern devices [42] with respect to wider temperature ranges and currently supported adaptive refresh rate techniques are studied in detail. Two key aspects are considered in our study of self-refresh energy savings at lower voltages and different refresh rates. They are (a) Increasing DRAM row activation (tRAS) and precharge (tRP) latencies at reduced voltages to ensure data retention (b) Latency increase in tRAS and tRP parameters are quantified using open-source model, after adapting it for 16nm DDR4 technology and these new latency values are used in simulation for energy and performance study.

(b) To assess the energy-saving effects of self-refresh at reduced voltages, we employ a set of eight PARSEC benchmarks for evaluation purposes. The simulation and measurement setup to quantify the DRAM energy consumption are described in detail. Based on full-system simulations, a detailed study of self-refresh energy savings for a set of 6 reduced voltage points, from 25 mV through 150 mV with a step size of 25 mV, at normal (1x standard refresh), extended (2x refresh) and reduced (0.5x refresh) temperature ranges are performed. (c) Increase of row refresh cycle time (tRFC) due to prolonged tRAS and tRP latencies at reduced voltage levels is discussed. This increased latency presents an overhead in exit latency of VRSR scheme and its impact on workload performance is analyzed.

(d) Subsequently, simulation results are presented and discussed to evaluate the potential energy savings across six reduced voltage points and the corresponding performance impact due to exit latency overhead. These discussions encompass all eight PARSEC benchmarks, providing insights into the effects of an aggressive voltage reduction of 150 mV.

(e) Some of the challenges and limitations in expanding our work to get detailed hardware measurements are discussed. DRAM architectural changes and additional power modes to exercise reduced voltage operation in self-refresh mode are proposed. Based on this proposal, the key open areas are presented to motivate researchers for future exploration with a goal to realize a full-scale solution.

#### 1.4 Motivation

#### 1.4.1 Processor – Performance Aware Energy Management

Dynamic Voltage and Frequency Scaling (DVFS) is a widely recognized and commonly utilized technique that enhances the energy efficiency of computing systems by dynamically adjusting the voltage and frequency based on the current utilization of processor cores. The primary objective of DVFS methodology is to develop a scheduling scheme for the usage of processor clock frequency-voltage settings over time, aiming to minimize processor power consumption while minimizing any performance degradation. To achieve this, a DVFS scheduling algorithm must determine the appropriate timing for adjusting the current frequency-voltage setting (scaling point) and identify the optimal new frequency-voltage setting (scaling factor).

In traditional approaches, metrics such as instruction retired and cache miss have been utilized for performance management [16, 21, 27]. Many existing DVFS algorithms rely on metrics like instructions retired or executed, assuming that an application's performance scales proportionally with the processor clock frequency. According to this assumption, halving the processor clock frequency would halve the computing system's performance. However, in reality, the execution time might only double in worst-case scenarios when the processor clock frequency is halved. Consequently, a DVFS scheduling algorithm based on this model might prioritize scheduling tasks at a faster processor clock frequency, potentially completing them well ahead of their deadlines (leading to a "race to halt" situation). Conversely, a slower processor clock frequency could be scheduled, meeting the performance deadline while consuming less power. Nevertheless, making decisions about "scaling factor" requires accurate runtime prediction of the operational relationship between frequency and performance. While cache miss is another common metric used to measure memory boundedness, it alone cannot guide frequency scaling decisions while accounting for the impact on performance. Hence, there is a clear need for a metric in DVFS that can evaluate the actual performance impact of frequency changes based on the runtime conditions.

To address this requirement, we conduct an evaluation of the instrumentation features available in various processor families to identify the performance monitoring unit (PMU) events that can effectively track the relationship between frequency and performance during runtime. Through our analysis, we have discovered that the POWER8 core [30] possesses a specific counter capable of monitoring the pipelined activity during off-core memory accesses, serving as a reliable indicator of architecture slack. In our work, we develop methods to exploit architecture slack-based counter in the POWER8 core, as this being the first core that offers such a capability. However, next generation POWER9 core also has this counter [3]. Therefore, for any related or future exploration, same methods and approaches can be extended to POWER9 and any other pipelined architectures (Intel, AMD processors) that offer such a capability for measurement of the architecture slack.

#### 1.4.2 Memory – Performance Aware Energy Management

Figure 1.2a shows a DRAM cell arrangement and each cell, has a storage capacitor Cs which stores electrical charge. Data in a memory cell is stored as either the presence or absence of charge. To access the data, a transistor, represented as T, is used. The word line (WL) connects to the transistor's gate and is responsible for accessing the data. On the other hand, the bit line (BL) transfers data to or from the storage capacitor (Cs) and is connected to the transistor's drain. One plate of Cs is linked to the transistor's source, while the other electrode is biased at the cell plate voltage, denoted as Vp. The bit line is typically connected to multiple cells organized in a column, while the word line is connected to multiple cells arranged in a row. However, bit lines have relatively large parasitic capacitance Cbl since they connect all of the transistors in a column.

Figure 1.2: DRAM cell and charge access scheme

As illustrated in Figure 1.2b, when the word line is driven high, the charge redistribution occurs, and this creates a small difference between bit line voltages. A sense amplifier as shown in Figure 1.8a, which is associated with each bit line pair is used to detect the small voltage differences that occur during charge sharing. These bit lines must be pre charged with Vcc/2 before any read operation.

Figure 1.3: Storage node, bit line and charge sharing voltages

As illustrated in Figure 1.3, voltage at storage node (VC) can be either 1 or 0. During word line activation (access operation), when a DRAM cell is connected to bit line (BL), it loses majority of its charge from Vcc to (Vcc/2 + Vs) when storing '1' or it is charged up from 0 to (Vcc/2 - Vs) when storing '0', where Vs is given by equation (1.1). This is due to Cs charge sharing with large bit line capacitor Cbl. This generates a small "readout"  $\Delta V$  which drives the input of the amplifier latch to one of the stable points 1 or 0, depending on the sign of  $\Delta V$  (sense operation). Both access and sense operations are combinedly referred as row activation.

$$V_{S} = (V_{cc}/2) / (1 + \frac{c_{bl}}{c_{s}})$$

(1.1)

As the word line remains active, write back (restore operation) occurs, Cs is recharged back to Vcc level from (Vcc/2 + Vs), when storing '1'. Similarly, (BL)<sup>-</sup>will also charge up from (Vcc/2 - Vs) to Vcc and Cs will be discharged from (Vcc/2 - Vs) to 0, when storing '0'. As a result, refresh power is mostly accounted for cells storing "1" due to recharging of cells from (Vcc/2 + Vs) to Vcc back and charging (BL)<sup>-</sup>capacitance Cbl from (Vcc/2 - Vs) to Vcc level. For stored data '1' and '0', refresh power consumed P1 and P2, can be given as per equations (1.2) and (1.3) respectively.

$$P1 = 0.5 * (C_S) * \left(\frac{V_{cc}}{2} - V_S\right)^2 * f$$

(1.2)

$$P2 = 0.5 * (C_{bl}) * \left(\frac{V_{cc}}{2} + V_S\right)^2 * f$$

(1.3)

where f = refresh rate and total refresh power, P = P1 + P2. Equations (1.2) & (1.3) clearly show that voltage is a potential knob to exercise power reduction during refresh. Self-refresh power also increases proportionately with respect to the number of cells to be refreshed. Therefore, in higher density devices, it contributes to a significant fraction of the total energy consumption.

#### **1.5** Organization of the Thesis

This thesis is organized as follows.

Chapter 1 gave a brief introduction about the importance of processor and memory energy management to reduce energy consumption:

- Specific to processor sub-system, given the dynamic workload nature in cloud computing environments, how workload architecture slack can be exploited to develop accurate models for performance management.

- Specific to memory sub-system, given the increasing DRAM energy consumption, the motivation towards reducing energy consumption by reducing voltage during self-refresh mode.

Chapter 2 summarizes literature survey on the following topics:

- Architecture slack exploitation for workload classification, phase classification and performance estimation.

- Studies to reduce DRAM refresh power consumption.

Chapter 3 covers the following:

- Experimental setup comprising hardware platform, SPECCPU 2006 and PARSEC benchmarks, tools to measure architecture slack and performance parameters of workloads for architecture slack exploitation

- Experimental setup including GEM5 full system simulator and PARSEC benchmarks for measuring DRAM energy consumption at reduced voltages

Chapter 4 covers the following:

• Methodology and evaluation of using architecture slack for workload classification of benchmarks, development of compute and memory regression models, phase classification at runtime, performance evaluation of benchmarks using a custom algorithm

Chapter 5 covers the following:

• Methodology of latency evaluation of timing parameters at reduced voltage DRAM operation using SPICE model, controller & DRAM architectural changes for practical implementation, Quantitative evaluation of performance overhead due to voltage reduced self-refresh

Chapter 6 presents the conclusions and the future work.

### **Chapter 2**

## **Literature Survey**

#### 2.1 Workload Classification, Phase Classification and Performance Estimation

The exploration of architecture slack in server computing environments is a burgeoning field with significant implications for performance management and optimization. Our work is positioned at the forefront of this research, aiming to develop methods that leverage architecture slack for workload classification, phase classification, and performance estimation. This endeavor is underscored by the introduction of a novel metric that measures architecture slack through core instruction throughput and not-busy cycles. The utility of this metric is demonstrated through its application in CPU and memory microbenchmarks, SPECCPU 2006, and PARSEC benchmarks on a POWER8 server processor.

Prior work in the realm of workload classification has predominantly focused on distinguishing between compute-bound and memory-bound workloads. Basireddy et al. [2] utilized the Memory Reads Per Instruction (MRPI) metric on a heterogeneous multi-core platform to classify workloads and optimize energy consumption through voltage-frequency settings. Similarly, Robert et al. [27] employed hardware performance counters to gauge CPU load influenced by main memory accesses, guiding frequency scaling decisions. Chung-Hsing et al. [12] introduced a Dynamic Voltage Scaling (DVS) algorithm, " $\beta$ -Adaptation," which adjusts core frequency based on the MIPS rate, highlighting the importance of instruction metrics over CPU cycles for workload requirement determination. These studies [2,12,27] underscore the significance of hardware metrics in workload classification but do not address architecture slack directly.

Phase classification [14,15,29,37] and its applications have been well studied in many prior works [6,25,34]. In the domain of phase classification, extensive research has been conducted

to identify program phases and optimize performance. Srinivasan et al. [34] introduced an online program phase classification scheme utilizing a bottleneck type vector (BTV) to enhance performance per watt. Chesta et al. [6] proposed a phase detection approach using execution vectors (EVs) derived from hardware counters. Rodrigues et al. [25] demonstrated the efficacy of combining online phase classification with dynamic core morphing in asymmetric multicore processors. These studies [6,25,34] highlight the potential of microarchitecture-dependent metrics in phase classification but do not specifically explore the role of architecture slack.

Performance estimation, a critical aspect of performance management, has been well studied [1,7,17,24]. Shoaib et al. [1] developed a performance prediction model, DEP+BURST, for multithreaded managed applications, significantly reducing performance estimation error. Rajamani et al. [24] and Contreras and Martonosi [7] utilized hardware counters for power management, while Sang-Jeong et al. [17] employed regression analysis based on CPI and memory accesses for runtime performance projection. These studies [1,7,17,24] emphasize the importance of hardware counters in performance prediction but do not leverage architecture slack for this purpose.

Our work distinguishes itself by focusing on architecture slack as a novel metric for workload classification, phase classification, and performance estimation. By leveraging instruction throughput and not-busy cycles, we aim to provide a more nuanced understanding of server computing environments. This approach not only builds upon the foundational work of prior studies [2,12,27,34,6,25,1,7,17,24] but also introduces a new dimension to performance management strategies. Through the characterization of our metric and the development of performance estimation models, we contribute to the ongoing discourse on optimizing server performance, marking a significant advancement in the field.

#### 2.2 Reducing DRAM Refresh Power Consumption

The quest to reduce DRAM refresh power consumption has been a focal point of numerous studies, each contributing unique insights and methodologies to address this challenge. The journey begins with the work of Byoungchan et al. [60], who introduced Enhanced Selfefficiency.

Refresh (ESR) and Long Latency Self-Refresh (LSR) modes. These modes innovatively applied selective voltage levels to DRAM cell transistors based on their activity state, optimizing leakage current and significantly improving power efficiency. The ESR mode, requiring minimal modifications, and the LSR mode, which achieved greater power reduction at the cost of increased latency, laid the groundwork for subsequent research in DRAM power

Building on these foundational concepts, RAIDR [61] exploited the variability in DRAM retention times [64] by grouping rows into bins with specific refresh rates, thereby enhancing system performance and reducing memory energy consumption. In a different study [62], a profiling mechanism is used to detect retention failures when the memory module enters self-refresh mode. This approach, however, faced challenges due to Variable Retention Time (VRT) failures, a problem that Qureshi et al. [65] aimed to address with AVATAR. AVATAR's dynamic adjustment of refresh periods sought to mitigate bit errors caused by VRT, though it could not guarantee the detection of all failing cells due to data pattern dependence. This limitation prompted the development of REAPER [66], which employed testing with multiple data patterns to identify failing cells more effectively.

Das et al. [67] proposed a mechanism that only fully refreshes DRAM cells when necessary, using low-latency partial refresh operations to maintain data integrity. This approach, validated through real workload memory traces, demonstrated a significant reduction in refresh performance overhead, marking a step forward in efficient DRAM management.

Further innovations came from Liu et al. [68] with the Flikker technique, which differentiated between critical and non-critical data for refresh rate adjustments, and the DIMMer approach [69], which powered off unused memory capacity to save energy. RAPID [70] and CLARA [71] introduced software and hardware solutions, respectively, to optimize refresh operations based on retention time variations, highlighting the complexity of addressing DRAM refresh power consumption.

Jung et al. [72] explored power-down mode policies in 3D-DRAMs, demonstrating significant energy savings through adaptive refresh periods based on temperature data. This

study underscored the potential of temperature-aware refresh strategies in reducing DRAM power consumption.

The literature reveals a consistent theme: the challenge of profiling DRAM cells for retention times due to VRT and Data Pattern Dependencies (DPD), as highlighted by Liu et al. [63]. These phenomena, which cause cells to exhibit unpredictable retention states, complicate the development of efficient refresh strategies.

In response to these challenges, recent work [73-78] has introduced algorithmic changes, new DRAM refresh commands, and device-level refresh mechanisms. These innovations aim to improve performance and energy consumption by dynamically adjusting refresh operations to the retention characteristics of DRAM cells. For instance, the proposal to replace the NMOS transistor in 3T eDRAM with a relay [77] and the introduction of a retention-aware refresh technique called elaborate-refresh [78] represent significant advancements in DRAM technology.

In summary, the body of literature on reducing DRAM refresh power consumption highlights a progression from initial strategies focusing on selective voltage application and grouping based on retention times to more sophisticated hardware and software approaches that address the challenges posed by VRT and DPD. These studies collectively underscore the critical need for efficient DRAM refresh mechanisms that can adapt to the varying retention characteristics of cells, thereby reducing power consumption without compromising system performance or data reliability. This evolving landscape of DRAM refresh strategies forms the basis of the current problem statement, which seeks to develop more effective refresh techniques that dynamically adjust to retention time variability and dependencies.

# Chapter 3 Experimental Setup

#### 3.1 Experimental Setup for Architecture Slack Exploitation

We have used Amester tool [22,26] to collect run time traces of a workload under measurement, on a 1-socket POWER8 hardware platform. Figure 3.1 depicts the measurement setup. POWER8 platform used for this work comprises an 8-core processor and has 128 GB of main memory. A measurement system runs Amester (Automated Measurement of Systems for Energy and Temperature Reporting) tool and connects to host system for data collection. Amester is an out-of-band tool which can collect parameters of interest, without impacting the workload performance that runs on host system.

Figure 3.1: Measurement setup

POWER8 processor has a piece of hardware & associated firmware called the On-Chip Controller (OCC) [13]. The OCC (On-Chip Controller) is a separate processor integrated on the chip alongside the main POWER processor cores. It has its own dedicated 512K SRAM and can access main memory. The OCC firmware operates in a continuous loop with a duration of 250 microseconds, constantly gathering system data. It can collect detailed information on temperature, performance, power, and utilization, and has the ability to control processor frequency and memory bandwidth. We have leveraged the OCC's measurement capabilities to collect performance and not-busy stall traces for workload analysis, and its frequency control capability to adjust frequencies using a max-min performance threshold algorithm.

To determine the workload boundedness and leverage the Wb to mipsr correlation, we employed SPEC CPU2006 [31] and PARSEC [23] benchmarks in our study. The POWER8 architecture comprises 12 cores, and each core has the capability to handle eight hardware threads concurrently (SMT8).

Our experimental setting was a single core configured in SMT8 mode. Our goal was to study architecture slack with diverse set of both serial and parallel benchmarks. We identified SPECCPU 2006 as one workload set, as it offered a diverse set of serial benchmarks. We found PARSEC as another workload set for multi-threaded workloads, as their programs have been parallelized to take advantage of multiprocessor computers with shared memory. Together, these benchmarks exhibit a variety of performance sensitivities to changes in CPU frequency, which was an essential aspect for our investigation. We acknowledge that SPECCPU underwent revisions in 2017, introducing enhanced features, improved applications, multi-threading options for select applications, and an optional power consumption measurement metric [19]. However, since our study and results are not significantly impacted by these features, we opted to continue using SPECCPU 2006.

#### 3.2 Experimental Setup for Study of Self-Refresh Energy Savings

We utilized a full system model based on GEM5 [52] to simulate a dual-core X86 ISA processor model, as presented in Table 3.1. The simulated DDR4 subsystem is connected to the controller via a single DDR4-2400 64-bit channel. This subsystem comprises 16 DRAMs, with 8 per rank, and each DRAM has an 8-bit interface (×8). Timings and key current values are based on the Micron DDR4-2400 8 Gbit datasheet (Micron MT40A2G4) as presented in

Table 3.2. To calculate the energy components, we employed the timings and key current values based on the Micron DDR4-2400 8 Gbit datasheet (Micron MT40A2G4) [42], which were utilized by the DRAMPower tool [53, 54] integrated within gem5. During simulation, the commands and timestamps are provided to DRAMPower at runtime. The DRAM subsystem consists of 16 banks, and the buffer that holds incoming requests for all banks is divided into separate read and write queues. The controller reorders the requests, and its scheduling policy follows the principle of First Ready - First Come First Served (FR-FCFS). The page policy employed is open adaptive, meaning that a specific bank's page is closed if there are no row hits (but row misses occur), and it remains open if there are no requests directed to that bank.

| Processor            | X86 ISA, Dual Core, 4GHz, TimingSimpleCPU                                                              |

|----------------------|--------------------------------------------------------------------------------------------------------|

| L1 I-Cache           | 32KB private, 4-way, 64B line, 2 cycle access time                                                     |

| L1 D-Cache           | 32KB private, 4-way, 64B line, 2 cycle access time                                                     |

| L2 D-Cache           | 128KB shared, 8-way, 64B line, 20 cycle access time                                                    |

| Memory<br>controller | FR-FCFS, open-adaptive, address mapping RoRaBaCoCh, 128B write buffer, 64B read buffer, 64B cache line |

|                      | DDR4 1Gbx8 device, 16 banks, 1 Channel, 2 Ranks per channel, 1200 MHz, BL8, Page size 1 KB             |

| PARSEC               | blackscholes, bodytrack, dedup, fluidanimate, frequine, streamcluster, swaptions, x264                 |

| Table 3.: | 1: Simu | ilation | setup |

|-----------|---------|---------|-------|

|-----------|---------|---------|-------|

| Current | Values |

|---------|--------|

|         | (mA)   |

| IDDo    | 48     |

| IDD1    | 60     |

| IDD4R   | 135    |

| IDD4W   | 123    |

| IDD5R   | 53     |

| IDD3N   | 43     |

| IDD2N   | 34     |

| IDD3P   | 37     |

| IDD2P   | 25     |

| IDD6N   | 30     |

| IDD6E   | 35     |

| IDD6R   | 20     |

| Timing  | Values     |

|---------|------------|

|         | (ns)       |

| tCK     | 0.833      |

| tRAS    | 32         |

| tRCD    | 14.16      |

| tREFI   | 7800       |

| tRP     | 14.16      |

|         |            |

| Voltage | Values (V) |

| UDD     | 1.0        |

| vonuge | vulues (v) |

|--------|------------|

| VDD    | 1.2        |

| VPP    | 2.5        |

|        |            |

Table 3.2: Power and timing parameters based on DDR4-2400 8 Gbit device [42]

Our intent is to study self-refresh energy savings with realistic workloads. The PARSEC benchmarks [23] are selected for this purpose, that generate parse traffic to memory with long idle times, thereby exercises the memory device to be in self-refresh mode for most of the times. We utilized the staggered power-down strategy implemented in DRAMPower [54]. This approach enables the memory controller to transition from active power-down mode to

precharge power-down mode and subsequently enter self-refresh mode in a staggered manner, reducing the energy consumption of the DRAM. The staggered power-down strategy, developed by Jung et al. [55], aims to achieve additional energy savings by eliminating unnecessary self-refresh entries [56].

In our study, all the active, idle & power-down energy components of the DRAM device are measured. All energy components are categorized into 4 groups, as shown in Table 3.3. G4 is the self-refresh energy, which is of primary interest for us to investigate energy savings with respect to reduced DRAM array voltage at normal (0- 85°C), extended (0- 95°C) and reduced (0- 45°C) temperatures in LPASR mode. Array voltage is reduced up to 150 mV at 25 mV granularity from 1.20 V nominal (i.e. 1.175 V, 1.150 V, 1.125 V, 1.100 V, 1.075 V, 1.050 V) and quantify self-refresh energy savings at three temperature ranges (IDD6N/IDD6E/IDD6N).

| Group |              | DRAM energy breakdown                        |

|-------|--------------|----------------------------------------------|

| G1    | act/pre      | IDDo: One bank ACTIVATE-to-PRECHARGE current |

|       | _            | IDD1: One bank ACTIVATE-to-READ-to-          |

|       |              | PRECHARGE current                            |

|       | Read         | IDD4R: Burst read current                    |

|       | Write        | IDD4W: Burst write current                   |

|       | refresh      | IDD5R: Distributed refresh current (1X REF)  |

| G2    | actBack      | IDD3N: Active standby current                |

|       | preBack      | IDD2N: Precharge standby current             |

| G3    | actPowerDown | IDD3P: Active power-down current             |

|       | prePowerDown | IDD2P: Precharge power-down current          |

| G4    | selfRefresh  | IDD6N: Self refresh current                  |

Table 3.3: DRAM energy components

### **Chapter 4**

## Architecture Slack Exploitation for Phase Classification and Performance Estimation

#### 4.1 Workload Classification of Benchmarks

Exploiting slack, when the processor core is busy executing programs, requires a very close activity monitoring of execution units. Our goal is to exploit such slack cycles, combined with other metrics for workload classification and performance estimation.

| Counter                                   | Description                                                         |

|-------------------------------------------|---------------------------------------------------------------------|

| Instruction<br>throughput ( <i>cIPS</i> ) | Completed instructions per second throughput of a core              |

| Stall cycles (cIdle)                      | Execution pipeline stall cycles (Not Busy) with outstanding L3 miss |

Table 4.1: Events tracked for Performance Management

Table 4.1 lists the counters available in POWER8 that are accessed by our implementations. While the Instruction throughput counters are widely available across different processor families, the *cIdle* counter is a novel counter introduced in POWER8 especially for facilitating the tracking of idleness in the core when waiting on data from memory. *cIPS* measures the rate of completed 'millions of instructions per second (MIPS)' i.e., instruction throughput in a core pipeline that is a direct measure of the performance. *cIdle* measures 'not busy' cycles of a core, when execution units are not busy, while there is at least one L3 cache miss pending, which is a direct measure of the execution pipeline stall cycles.

Figure 4.1: Hardware implementation of *cIdle* counter

The POWER8 core pipeline has both single-cycle and multiple-cycle execution units. Figure 4.1 illustrates the hardware implementation of the cIdle counter [11]. This counter increases during each execution cycle when at least one thread is waiting for off-core memory access and no threads are actively working, indicating that at least one processor core is not in use. The cIdle counter performs a logical AND operation between the finish signals of single-cycle units, the delayed busy signals of multi-cycle units, and the logical OR operation of L3 miss signals from all threads. The output signal is activated when all pipelines are not busy, meaning there are no finishes from single-cycle units or no delayed busy signals from multi-cycle units. Accumulating this metric over millions of cycles reveals insights into pipeline activity trends during periods of off-core memory access.

We identify that the instruction throughput (MIPS) and not-busy cycles (stalls) as providing measures, which are complementary in nature to understand the fast or slow execution behavior of pipeline. With this intuition, we propose to combine these metrics to characterize the architecture slack and leverage for workload classification, phase classification and performance estimation.

Workload classification can infer how the performance of a workload is bounded to frequency changes. We propose a compounded metric Wb (workload bound) for this classification purpose, which basically is "MIPS to Stalls" ratio, as shown in Equation 4.1. It is measured in millions of instructions per second to million cycles of idle stalls. Wb metric is sensitive to frequency changes, as measures of both instruction throughput and stall cycles are impacted directly by frequency. It is a measure of architecture slack of workloads.

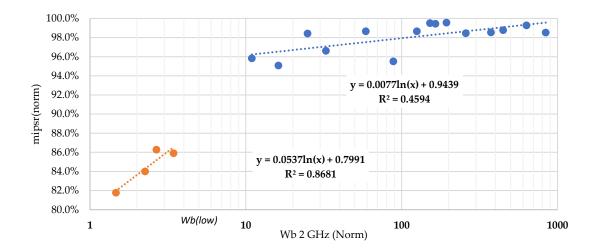

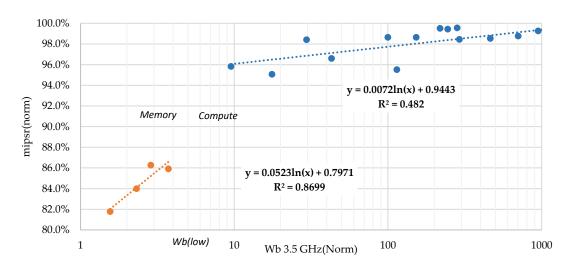

Performance estimation by a DVFS algorithm require accurate prediction of operational relationship between frequency and performance at current and target frequency points (frequency sensitivity), at run-time. It is essentially a measure of "architecture slack" present in the workloads to indicate how many wasted cycles can be eliminated, by lowering the frequency with minimal impact on performance. mipsr (ratio of MIPS between target and current frequency) is a direct measure of frequency sensitivity accounting for architecture slack, between two frequency points. However, measuring mipsr at runtime, has the following drawbacks (a) DVFS algorithms need performance measurement at current and target frequency to determine the sensitivity. This necessitates DVFS controller to slew frequency from current frequency to target frequency point and (b) It must be calibrated periodically to account for phase changes that occurs during runtime. Both (a) and (b) are huge overhead for a performance control algorithm. One important motivation of our work is to evaluate how Wb can be leveraged as proxy to mipsr, by exploiting the relationship between these parameters. This is mainly to address the above-mentioned drawbacks. The intuition behind this approach is that both parameters provide similar measure of frequency sensitivity accounted for architecture slack of workloads.

$$W_b = \left(\frac{cIPS}{cIdle}\right) mips/mcyc \tag{4.1}$$

Equation 4.1 is based on the following simple intuition. For a compute intensive workload, instruction throughput measured by *cIPS* will be high and not-busy cycles measured by *cIdle* will be low. Such trend will be exactly opposite for a memory-bound workload. Therefore, higher bound Wb(high) indicates, more performance impact (more throughput and less stalls) which is tightly bounded to frequency change implying a core-bound workload. Lower bound Wb(low) indicates, less performance impact (less throughput and more stalls) which is loosely bounded to frequency change, implying a memory-bound workload. We have validated "Wb" behavior for a 1.5 GHz broader frequency range, from 2 to 3.5 GHz, at 100

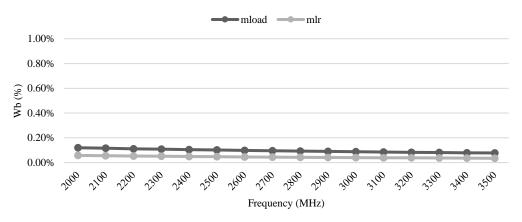

MHz granularity using four custom micro benchmarks: sqroot, fma, mcopy and mlr. sqroot & fma are CPU intensive benchmarks, whereas mcopy & mlr are memory intensive benchmarks.

Figure 4.2: Wb (MIPS to stalls ratio) for custom core-bound benchmarks

Figure 4.3: Detailed Wb trend for sqroot core-bound benchmark

Figure 4.4: Detailed Wb trend for fma core-bound benchmark

Figure 4.5: Wb (MIPS to stalls ratio) for custom memory-bound benchmarks

The behavior of Wb for these four benchmarks, from 2 GHz to 3.5 GHz, is shown in Figures 4.2 & 4.5. Wb-values shown have been normalized to the peak value which is the value for sqroot at 3.5 GHz. Figures 4.3 and 4.4 illustrate the detailed Wb trend along with MIPS and Not busy cycles, across the 2 to 3.5 GHz full frequency range for sqroot & fma respectively. It is observed that both MIPS & Not busy cycles are impacted at each measurement point of 100 MHz granularity step size, resulted in overall trend of Wb metric at each frequency point. This shows that measure of these two metrics (MIPS, not-busy cycles) is impacted directly by frequency and hence Wb inherently accounts for the same.

In sqroot and fma benchmarks, Wb(high) consistently exceeds 10% across all frequencies, indicating a significantly higher instruction throughput than stalls. On the other hand, in mload and mlr benchmarks, Wb(low) remains below 0.2%, suggesting a considerably higher

occurrence of stalls compared to instruction throughput. This substantial disparity in the normalized Wb metric value demonstrates its effectiveness in distinguishing between corebound and memory-bound workloads.