### Superior Analog, Digital, and Ternary Circuit Designs Using Advanced Nano-electronic Gate Overlap Tunnel FET Devices for Ultra-Low Power Applications

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY**

by

Simhadri Hariprasad ID No. 2017PHXF0015H

Under the supervision of:

#### Prof. Surya Shankar Dan

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI2023

#### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

## Certificate

This is to certify that the thesis titled, "Superior Analog, Digital, and Ternary Circuit Designs Using Advanced Nano-electronic Gate Overlap Tunnel FET Devices for Ultra-Low Power Applications" and submitted by <u>Simhadri Hariprasad</u> ID No. <u>2017PHXF0015H</u> in partial fulfillment of the requirements of **DOCTOR OF PHILOSOPHY** embodies the work done by him under my supervision.

Supervisor **Prof. Surya Shankar Dan** Associate Professor, BITS-Pilani Hyderabad Campus Date:

## **Declaration of Authorship**

I, **Simhadri Hariprasad**, declare that this Thesis titled, "Superior Analog, Digital, and Ternary Circuit Designs Using Advanced Nano-electronic Gate Overlap Tunnel FET Devices for Ultra-Low Power Applications" and the work presented in it are my own. I confirm that:

- This work was done wholly or mainly while in candidature for a research degree at this University.

- Where any part of this thesis has previously been submitted for a degree or any other qualification at this University or any other institution, this has been clearly stated.

- Where I have consulted the published work of others, this is always clearly attributed.

- Where I have quoted from the work of others, the source is always given. With the exception of such quotations, this thesis is entirely my own work.

- I have acknowledged all primary sources of help.

- Where the thesis is based on work done by myself jointly with others, I have made clear exactly what was done by others and what I have contributed myself.

Signed:

Date:

## Acknowledgments

First and foremost, I would like to express my sincere gratitude to my supervisor Prof. Surya Shankar Dan for his constant support, patience and valuable guidance throughout my work.

I would also wish to express my gratitude to HoD Prof. Subhendu K Sahoo, the ex-HoD, Prof.Alivelu M.Parimi and Prof.Sanket Goel, DRC convener Prof. Prabhakar Rao and DAC members, Dr.Syed Ershad Ahmed and Dr.Parikshit Sahatiya, for their valuable suggestions and constructive comments.

I am thankful to my senior colleagues, Dr.Sanjay Vidhyadharan and Dr.Ramakant Yadav, for their constant support and for helping develop the device simulation framework.

I would also like to thank my fellow research scholars of the Department of Electrical and Electronics Engineering at BITS-Pilani, Hyderabad Campus, who have supported me through their suggestions.

Furthermost, I would like to thank all members of the Department of Electrical Engineering at BITS-Pilani, Hyderabad Campus, that have supported me with their suggestions and discussions.

I am incredibly grateful to my parents for their love, prayers, care, and sacrifices in educating and preparing me for my future. Also, I express my thanks to my sister, brother, sister-in-law, and brother-in-law for their support and valuable prayers.

Finally, thanks go to all the people who have supported me to complete the research work directly or indirectly.

### Abstract

Energy efficiency limit has become the main obstacle for power-constrained applications using the conventional silicon complementary metal-oxide-semiconductor (CMOS) technology. In particular, the supply voltage scaling has slowed down in the past few technology generations due to the 60 mV/decade fundamental limit for on-off switching in MOSFETs, which prevents the reduction of the energy per operation in today's circuits and systems. To mitigate this challenge, Tunnel FETs or TFETs are envisioned as a viable alternative to achieve the steep on-off switching (SS<60 mV/dec) at low supply voltages and fabrication process, which is compatible with CMOS technology. Gate-controlled BtB tunneling phenomena enable the switching in TFETs at the source channel p-n junction.Tunnel FETs, which are gated PIN diodes whose on current  $I_{on}$  arises from band-to-band tunneling, are desirable for ultra-low power applications due to their low off current  $I_{off}$  and reduced inverse Sub-threshold Slope SS. Furthermore, a fundamental disadvantage of TFETs is that their ON-state current is significantly lower than that of MOSFETs.

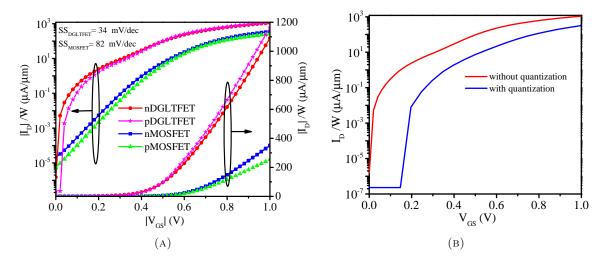

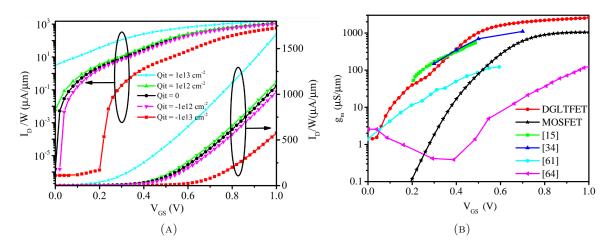

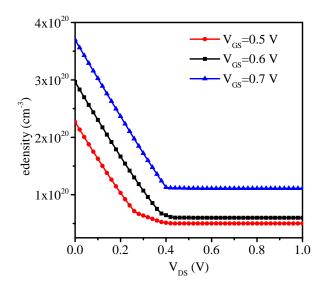

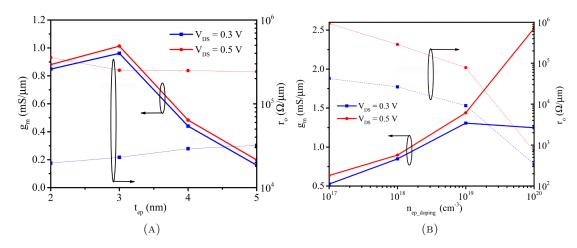

This thesis proposes different types of TFETs for digital, analog, and ternary logic applications. The first DGLTFET device has been optimized such that device characteristics are superior to equally sized 45 nm MOSFETs for analog applications. TFETs show excellent current saturation characteristics and negligible channel length modulation effect, which is detrimental in MOSFETs, especially at lower technology nodes. As a result, output resistance  $r_o$  in the saturation region is a high order of  $10^6$  Ohms. In the proposed TFETs, vertical BtB tunneling has been used compared to point tunneling in conventional TFETs given a more BtB generation rate, which improves  $I_{on}$  as well as  $g_m$ . DGLTFET has thrice the on currents  $I_{on}$ , at least one order lower off currents  $I_{off}$ , twice the transconductance  $g_m$ , at least two orders higher output resistance  $r_o$ , and at least two orders higher overall intrinsic gain  $g_m r_o$  than the equivalent metal oxide- semiconductor field-effect transistor (MOSFET) having the same width at the same technology node. Device optimization has been carried out by studying the impact of various device parameters and dimensions on performance. In this work, we have optimized the DGLTFET device by changing critical parameters like the epi-layer thickness  $t_{ep}$  and its doping concentration  $n_{ep}$ , which seriously influence the line-tunneling behavior. Optimizing the critical parameters for enhanced line-tunneling leads to improved analog performance parameters like  $g_m$ ,  $r_o$ , and, finally, superior analog circuits.

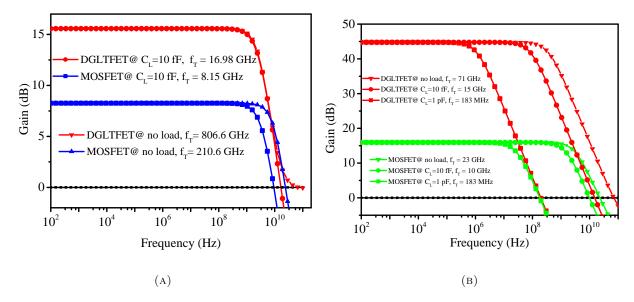

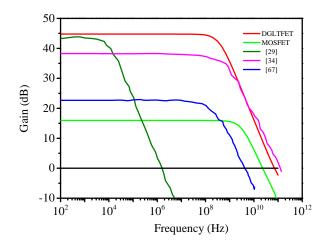

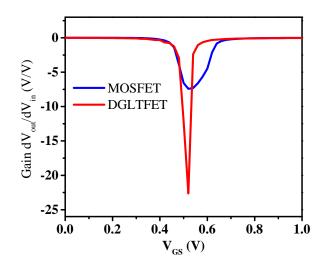

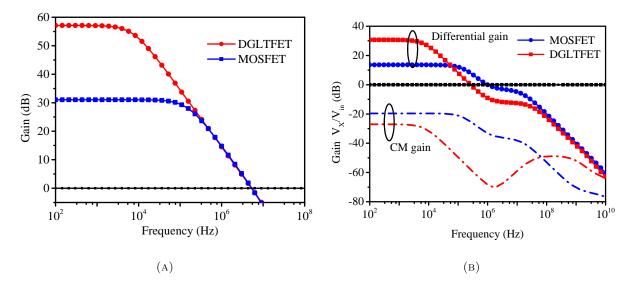

We have compared the performance of the proposed devices with the TFETs reported earlier in the literature and the standard 45 nm MOSFETs. TFET characteristics were simulated using synopsys® TCAD tools, while circuit performance was benchmarked with the standard 45 nm CMOS library using cadence® EDA tools. The performance of the DGLTFET was benchmarked with the equivalent MOSFET in fundamental analog VLSI circuits, namely, Common Source CS amplifier (resistive and cascade loads), current mirror (single-stage and cascode configurations), and a two-stage op-amp. The AC gain of cascode CS amplifier based DGLTFET devices is observed to be 30 dB higher gain compared with MOSFETs. DGLTFET CS amplifier has a gain-BW product or unity-gain BW  $f_T$  of 15 GHz, while the MOSFET CS amplifier with the same bias current is 10 GHz. The DGLTFET current mirror has at least three orders of magnitude higher output resistance  $R_{out}$  than the corresponding MOSFET current mirror. Similarly, the common-mode rejection ratio (CMRR) of the DGLTFET op-amp is 57 dB compared to the CMRR of 33.5 dB of the equivalent design in the standard 45-nm complementary metal-oxide semiconductor(CMOS) technology.

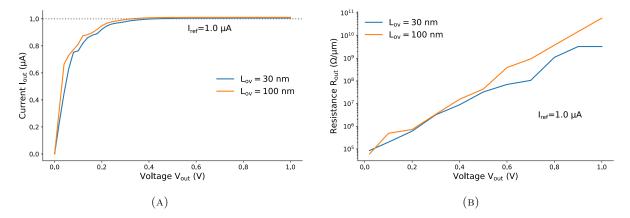

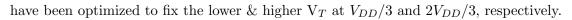

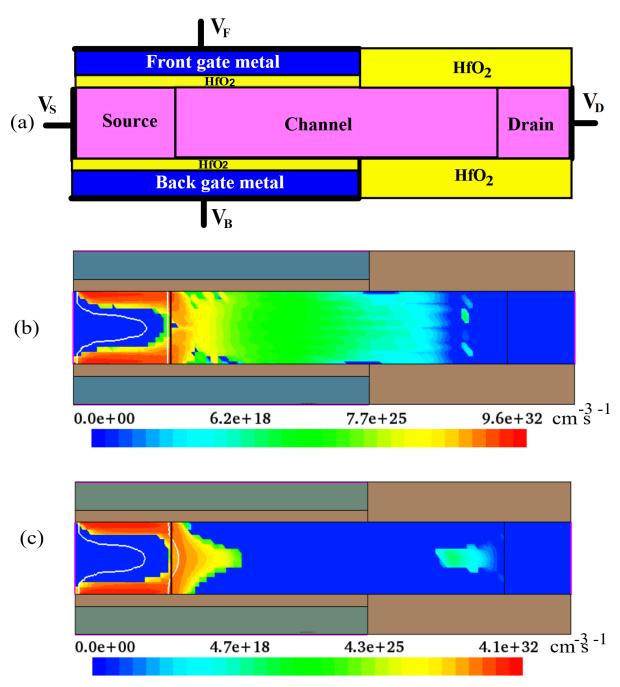

Vertically grown TFETs are preferred as they allow the integration of more TFETs on a single chip, increasing device density. This thesis work presents a Vertical Line-Tunneling FET (VLTFET) optimized for superior performance in analog applications. The saturation mechanism, DC, and small-signal behaviors are physically explained with the help of energy band diagrams, electron density, and tunneling width parameters. VLTFET has higher output resistance  $r_o$  owing to the independence of the drain bias on the band-to-band (BtB) generation. Increasing the source-gate overlap length  $L_{ov}$  from 0.1  $\mu$ m to 0.5  $\mu$ m triples the transconductance  $g_m$ , maintaining  $r_o$  constant, resulting in thrice the intrinsic gain  $A_{vo}$ . In analog circuits using conventional MOSFETs,  $g_m$  increases and  $r_o$  decreases with increasing width W. On the other hand, in analog circuits using VLTFETs,  $A_{vo}$  can be enhanced by increasing  $L_{ov}$  which increases  $g_m$  without affecting  $r_o$ . Unity-gain BW  $f_T$  (or the GBW product) is dominated by the relative change in the overall gate capacitance  $C_{GG}$  and  $g_m$  due to change in  $L_{ov}$ , since both  $g_m$  and  $C_{GG}$ are proportional to  $L_{ov}$ . However, in analog circuits with realistic capacitive loads,  $f_T$  rapidly increases with  $L_{ov}$ . VLTFET-based cascode CS amplifiers provide a 10 dB increment in its gain as  $L_{ov}$  is increased from 30 nm to 100 nm. Similarly, a VLTFET-based cascode current mirror shows a theoretical output resistance  $R_{out}$  in the order of  $10^{11} \Omega$ , behaving as an ideal current mirror/source.

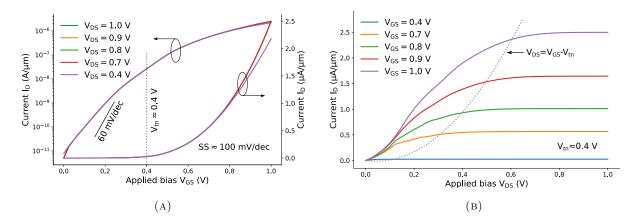

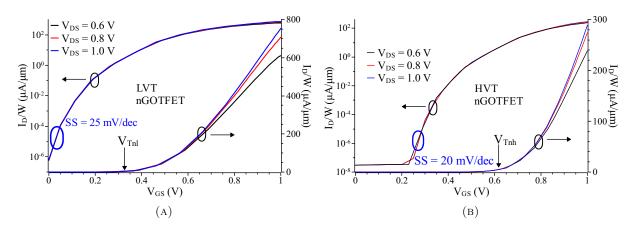

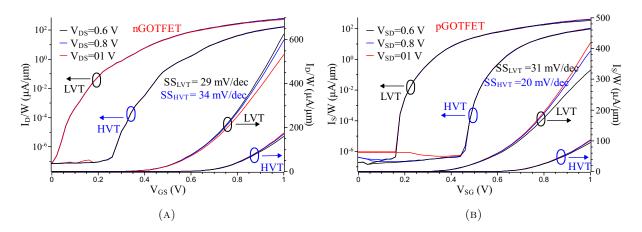

In this thesis, we have proposed GOTFETs for prospective digital applications . Its on-state currents  $I_{on}$  at least twice  $(I_{on,GOT} \geq 2I_{on,MOS})$  with off-state currents  $I_{off}$  remaining at least an order of magnitude lower  $(I_{off,GOT} \leq 0.1I_{off,MOS})$ , than the corresponding equally-sized MOSFETs at the same 45 nm technology node. The proposed GOTFET designs are targeted for higher  $I_{on}$  leading to high-speed operation and lower  $I_{off}$  to minimize static leakage in ultra-low-power digital applications. This work further modified the GOTFETs for low and high threshold transistors (LVT & HVT) for ternary logic applications. These devices are designed in such a way that the low and high threshold voltages  $(V_{tn} & V_{th})$  are  $V_{DD}/3$  and  $2V_{DD}/3$  respectively, with the ranges {0 to  $V_{DD}/3$ }, { $V_{DD}/3$  to  $2V_{DD}/3$ } & { $2V_{DD}/3$  to  $V_{DD}$ } representing the three logic states 0, 1 & 2 respectively. Proposed LVT & HVT TFETs have on currents  $(I_{on})$  roughly twice and off currents  $(I_{off})$  at least an order of magnitude lower than the corresponding MOSFETs. Dual threshold GOTFETs proposed in this work use single devices by altering their terminal connections.

Along with analog circuits, this thesis shows the performance of GOTFETs-based digital circuits. Proposed GOTFETs outperform similar CMOS designs in both aspects of the speed of operation and power consumption. This work proposes the GOTFET-based basic building blocks of digital circuits like an improved double tail comparator, ultra-low-power dynamic adder, an ultra-low voltage Schmitt trigger, and ultra-low-power ternary flash ADC circuits. The proposed circuit-level modifications in this Complementary GOTFET (CGOT) circuits have not only resulted in significantly lower static power due to TFET technology but also helped achieve faster circuit operation (lower delays) than the corresponding CMOS circuits. The overall Power Delay Product (PDP) in the proposed improved GOTFET-based circuits is only 1-5% of the PDP of the corresponding conventional CMOS-based circuits.

## Contents

| Certifi                                   | cate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Declar                                    | ation of Authorship ii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Acknow                                    | wledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Conter                                    | vii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| List of                                   | Tables x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| List of                                   | Figures xii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Abbre                                     | viations xvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Image: coduction1Motivation and Related Work1Objectives, Research Gaps, and Scope of this Work3Operating Principle of the Tunnel Field Effect Transistor4Contributions5Thesis Outline6                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                           | Ible-Gate Line-Tunneling FET (DGLTFET) Devices for Superior Analog<br>formance8Introduction8Proposed DGLTFET device structure and its characteristics102.2.1 DGLTFET device structure102.2.2 Calibration of the simulation deck with experiments102.2.3 Physical explanation for DGLTFET's superior performance122.2.4 DGLTFET fabrication process142.2.5 Results and discussions on the nDGLTFET142.2.6 Results and discussions on the pDGLTFET19Comparison of the DGLTFET with the other TFETs reported earlier19Comparison of the analog performance of DGLTFET with other TFETS reported19Conclusions20Publications Based on This Chapter21 |

| 3 | Ana      | alog Circuits using DGLTFET devices                                                   | <b>22</b> |

|---|----------|---------------------------------------------------------------------------------------|-----------|

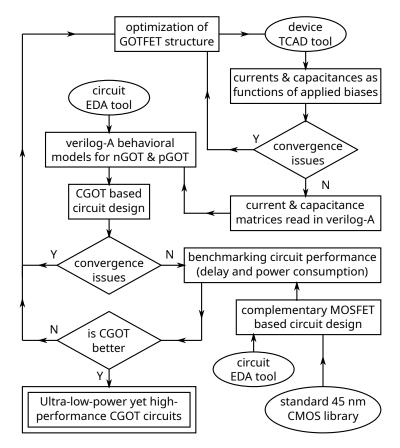

|   | 3.1      | Co-simulation Methodology and Benchmarking Criteria                                   | 22        |

|   | 3.2      | Common source (CS) amplifier in resistive load and cascode configurations             | 24        |

|   | 3.3      | Small-signal analysis of the CS amplifier                                             | 27        |

|   | 3.4      | DGLTFET based single stage and cascode current mirrors                                | 28        |

|   | 3.5      | Two-stage operational amplifier (op-amp)                                              | 30        |

|   | 3.6      | Conclusions                                                                           | 32        |

|   | 3.7      | Publications Based on This Chapter                                                    | 33        |

| 4 | Sup      | perior Analog Performance due to Source-Gate Overlap in Vertical Line-                |           |

|   | Tun      | neling FETs and Their Circuits                                                        | 34        |

|   | 4.1      | Introduction                                                                          | 34        |

|   | 4.2      | VLTFET Device Structure and its Characteristics                                       | 34        |

|   |          | 4.2.1 VLTFET Device Structure                                                         | 34        |

|   |          | 4.2.2 Physics-Based Modeling Approach                                                 | 35        |

|   |          | 4.2.3 Calibration of the Simulation Deck With Experiments                             | 37        |

|   |          | 4.2.4 VLTFET fabrication process                                                      | 38        |

|   | 4.3      | Physical Explanation of VLTFET Behavior                                               | 38        |

|   | 4.4      | Impact of Gate-Overlap $L_{ov}$ on Analog Circuits                                    | 45        |

|   | 4.5      | Conclusions                                                                           | 46        |

|   | 4.6      | Publications Based on This Chapter                                                    | 47        |

| 5 | Nov      | vel GOTFET Devices for Digital and Ternary Logic Applications                         | 48        |

|   | 5.1      | Introduction                                                                          | 48        |

|   | 5.2      | Proposed GOTFET Devices for Digital Applications                                      | 51        |

|   |          | 5.2.1 Structure of the Proposed GOTFET                                                | 51        |

|   | 5.3      | Suppression of Ambipolar Behavior of GOTFET without Compromising $I_{on}$ , $I_{off}$ |           |

|   | <u> </u> | , and SS                                                                              | 52        |

|   | 5.4      | Proposed LVT & HVT GOTFET Devices for Ternary logic Applications                      | 55        |

|   |          | 5.4.1 Proposed LVT & HVT GOTFETs Structure and Parameter Optimization                 |           |

|   | 5.5      |                                                                                       | 58        |

|   |          | 1                                                                                     | 62        |

|   | 5.6      | Conclusions                                                                           | 63        |

|   | 5.7      | Publications Based on This Chapter                                                    | 64        |

| 6 | Ult      |                                                                                       | 66        |

|   | 6.1      |                                                                                       | 66        |

|   | 6.2      | GOTFET Based Improved Double-Tail Dynamic Comparator                                  | 72        |

|   | 6.3      | GOTFET Based Dynamic Full Adder (DFA)                                                 | 74        |

|   |          | 6.3.1 Benchmarking CGOT DFA Against CMOS Dynamic Full Adder                           | 76        |

|   | 6.4      | GOTFET Based Regenerative-Latch Schmitt Trigger                                       | 78        |

|   | 6.5      | GOTFET Based Innovative Ternary Flash ADC                                             | 81        |

|   |          | 6.5.1 Validation of the Proposed ADC Design                                           | 85        |

|   |          | 6.5.2 Performance Benchmarking of the Proposed GOTFET Against CMOS                    |           |

|   |          | Ternary Flash ADC                                                                     | 86        |

|   | 6.6      | An Advanced Adiabatic Logic Using GOTFET Devices                                      | 89        |

|   |          | 6.6.1 Principle of Adiabatic Energy Recovery Cycle                                    | 90        |

|   |          | 6.6.2 CMOS Symmetric Pass Gate Adiabatic Logic (SPGAL)                                | 90        |

| 8 | Sur | nmary  |           |          |          |         |       |       |     |       |      |      |      |    |     |     |   |       | 101 |

|---|-----|--------|-----------|----------|----------|---------|-------|-------|-----|-------|------|------|------|----|-----|-----|---|-------|-----|

|   | 7.2 | Future | e Work .  |          |          |         |       |       |     |       |      |      |      |    | •   | ••• | • | <br>• | 99  |

|   |     |        | usion     |          |          |         |       |       |     |       |      |      |      |    |     |     |   |       |     |

| 7 |     |        | n and Fu  |          |          |         |       |       |     |       |      |      |      |    |     |     |   |       | 98  |

|   | 6.7 | Public | ations Ba | sed on ' | This Cl  | hapter  |       |       |     |       |      | • •  | • •  |    | •   | ••• | • | <br>• | 97  |

|   |     |        | Conclusi  |          |          |         |       |       |     |       |      |      |      |    |     |     |   |       |     |

|   |     |        | 6.6.4.2   | GOTA     | L Inve   | rter/B  | uffer |       |     |       |      |      |      |    |     |     | • | <br>• | 93  |

|   |     |        | 6.6.4.1   | Advan    | tages of | f CGC   | OT Ov | ver C | CMO | S for | c Ad | liab | atic | Lo | gic |     | • | <br>• | 92  |

|   |     | 6.6.4  | GOTFE'    | T Adial  | batic Lo | ogic (C | GOTA  | L).   |     |       |      |      |      |    |     |     | • | <br>• | 92  |

|   |     | 6.6.3  | Limitatio | ons of C | CMOS S   | SPGA    | L Buf | fer . |     |       |      |      |      |    |     |     | • |       | 91  |

#### Bibliography

104

## List of Tables

| $2.1 \\ 2.2$ | Parameters of the generic DGLTFET devices                                                                                                       | 11       |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|              | ported earlier. *Denotes unreported data in the publication                                                                                     | 20       |

| 2.3          | Comparison of the DGLTFET's analog performance with the other TFETs reported earlier. *Denotes unreported data in the publication               | 20       |

| 3.1          | Comparison of the DGLTFET cascode CS amplifier with similar other works published earlier.                                                      | 24       |

| 3.2          | Comparison of the DGLTFET with the equivalent MOSFET for the resistive-load<br>and cascode CS amplifiers.                                       | 26       |

| 3.3          | Comparison of the DGLTFET with the equivalent MOSFET for the single-stage<br>and cascode current mirrors.                                       | 29       |

| 3.4          | Transistor sizes used in the two-stage op-amp design at the 45 nm technology node.                                                              | 31       |

| 3.5          | Comparison of two-stage op-amp designed with DGLTFET and the equivalent MOSFET for an $f_T=5$ MHz.                                              | 31       |

| 3.6          | Comparison of the DGLTFET-based two-stage op-amp with similar other works<br>on TFETs published earlier.                                        | 31       |

| 4.1          | Parameters of the nVLTFET and pVLTFET devices                                                                                                   | 36       |

| 4.2          | Summary of the dependence of MOSFET and VLTFET analog performance on device parameters.                                                         | 44       |

| 5.1          | Parameters of the nGOTFET & pGOTFET devices                                                                                                     | 51       |

| 5.2          | Parameters of the Optimized LVT & HVT nGOTFET                                                                                                   | 56       |

| $5.3 \\ 5.4$ | Parameters of the Optimized LVT & HVT pGOTFET                                                                                                   | 56       |

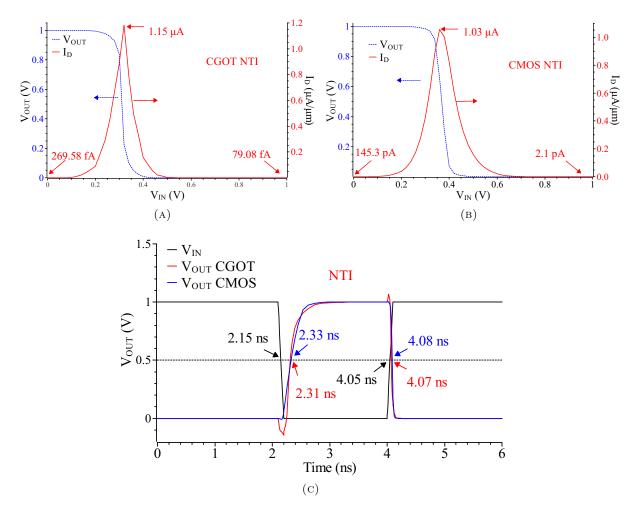

|              | NTI cell.                                                                                                                                       | 58       |

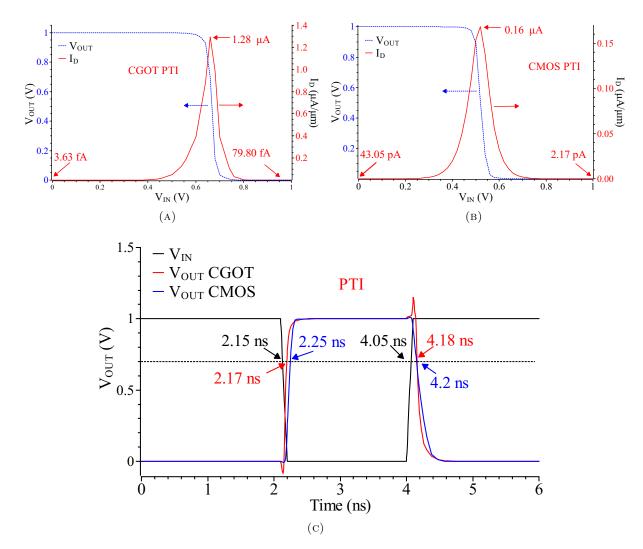

| 5.5          | Comparison of delay and static power consumption of GOTFET and CMOS-based<br>PTI cell.                                                          | 60       |

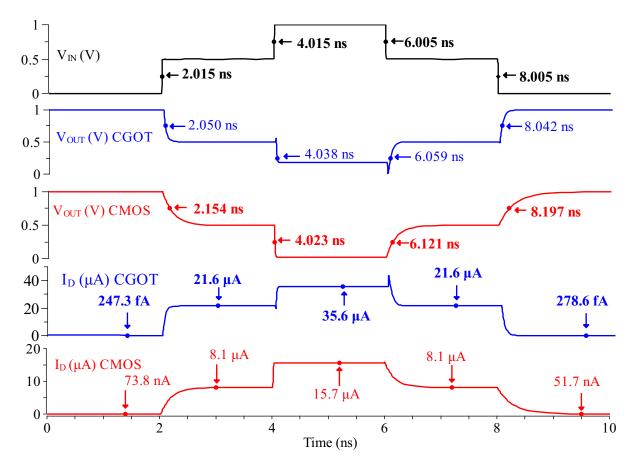

| 5.6          | Comparison of delay and static power consumption of GOTFET and CMOS based STI cell.                                                             | 61       |

| 5.7          | Parameters of dual-threshold nGOTFET and pGOTFET                                                                                                | 63       |

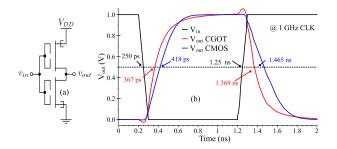

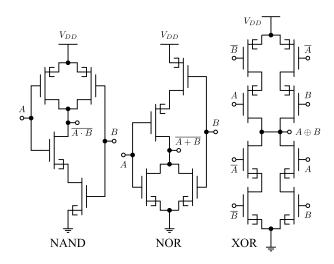

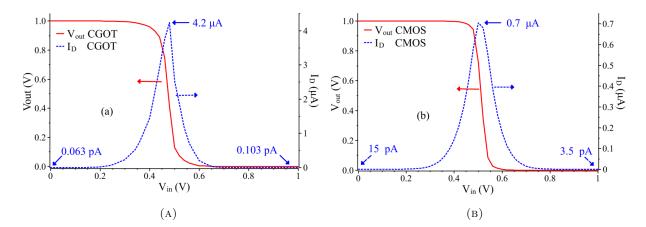

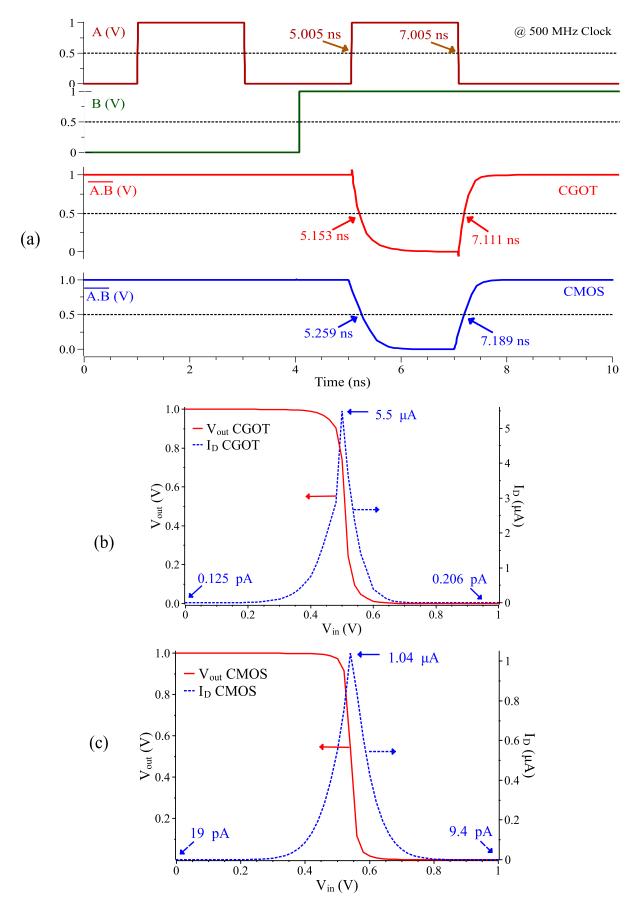

| 6.1          | Benchmarking the performance parameters of inverter NAND, NOR & XOR gates implemented with CGOT and CMOS technologies at 10 fF load capacitance | 71       |

| 6.2          | Significant improvement in propagation delay and static power consumption of                                                                    | 74       |

| 6.3          | CMOS and CGOT conventional double-tail dynamic comparator design Truth table of a Full Adder (FA)                                               | 74<br>75 |

| 6.4          | Comparison of delay and static power parameters of CGOT and CMOS based<br>Dynamic FA (DFA) for a capacitive load equivalent to the fanout of 4. | 79       |

|              | Dynamic In (DIA) for a capacitive load equivalent to the fatiout of 4                                                                           | 19       |

| 6.5 | Improvement in delay and power consumption of CGOT w.r.to CMOS Schmitt |    |

|-----|------------------------------------------------------------------------|----|

|     | trigger for a capacitive load of 20 fF                                 | 81 |

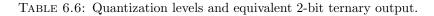

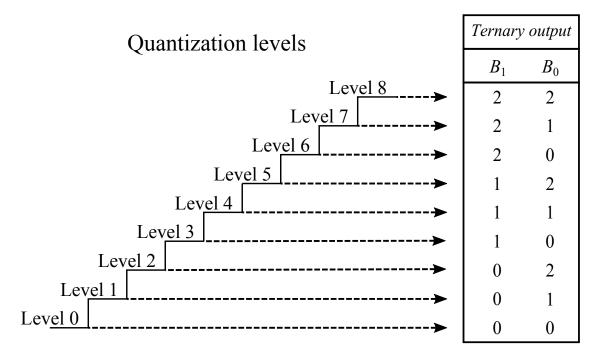

| 6.6 | Quantization levels and equivalent 2-bit ternary output.               | 82 |

| 6.7 | Truth table for the combinational block design.                        | 86 |

| 6.8 | Performance of proposed CGOT ternary ADC compared with CMOS ternary    |    |

|     | ADC at 10 fF capacitive load                                           | 88 |

## List of Figures

| 1.1        | Energy band diagram of an nTFET [5]                                                                                                                                                                 | 5  |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

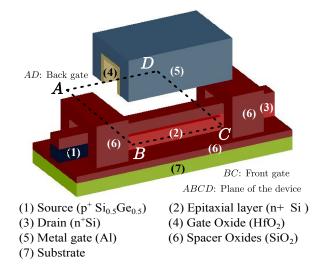

| 2.1        | (a) Schematic cross-sectional view of the proposed DGLTFET device. (1) $p^+$<br>Si <sub>0.5</sub> Ge <sub>0.5</sub> source (2) $p^-$ Si channel (3) $n^+$ Si drain (4) $n^+$ Si epitaxial layer (5) | 0  |

| 2.2        | HfO <sub>2</sub> gate oxide (6) Al metal gate (7) SiO <sub>2</sub> spacer oxide                                                                                                                     | 9  |

| 2.2        | respectively.                                                                                                                                                                                       | 9  |

| 2.3        | $I_D-V_{DS}$ characteristics of nDGLTFET & nMOSFET for different values of $V_{GS}$ and (b) $I_S-V_{SD}$ characteristics of pDGLTFET & pMOSFET for different values                                 |    |

| <b>a</b> 4 | of $V_{SG}$ .                                                                                                                                                                                       | 11 |

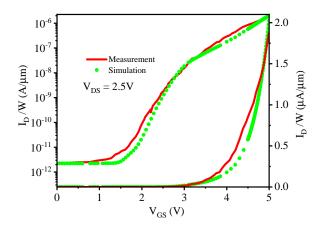

| 2.4        | Calibration of the simulation deck with the $I_D$ - $V_{GS}$ characteristics measured from<br>a prefabricated device at $V_{DS}=2.5$ V[55]                                                          | 12 |

| 2.5        | Section-wise view of the DGLTFET for visualizing the fabrication process. The horizontal plane <i>ABCD</i> represents the device cross-section illustrated in                                       | 13 |

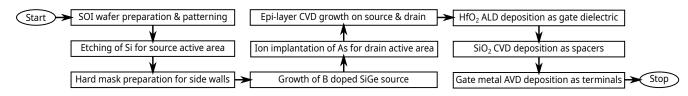

| 2.6        | Process flowchart for the DGLTFET structure. Abbreviations used are SOI:<br>Silicon On Insulator, CVD: Chemical Vapor Deposition, ALD: Atomic Layer                                                 |    |

| ~ -        | Deposition, AVD: Atomic Vapor Deposition.                                                                                                                                                           | 14 |

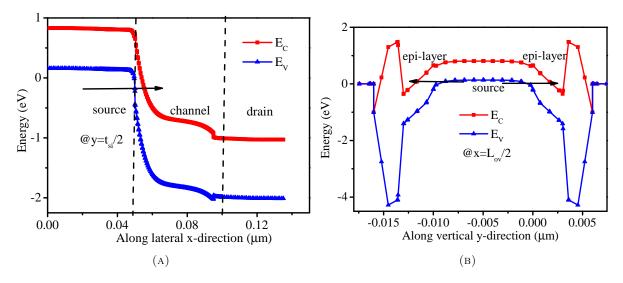

| 2.7        | Energy bands aiding BtB generation along the (A) lateral & (B) vertical directions                                                                                                                  | 14 |

| 2.8        | in the nDGLTFET for $V_{GS}=V_{DS}=1$ V                                                                                                                                                             | 14 |

| 2.9        | Confinement (FIQC) effects on the $I_D$ - $V_{GS}$ characteristics of DGLTFET (a) Effect of trap charge density on the $I_D$ - $V_{GS}$ characteristics of DGLTFET. (b)                             | 15 |

|            | Transconductance $g_m$ of the DGLTFET, compared with equivalent MOSFET and<br>other TFETs reported earlier                                                                                          | 15 |

| 2.10       | Variation of the electron density with increasing $V_{DS}$ within the epi-layer under                                                                                                               |    |

|            | the gate overlap.                                                                                                                                                                                   | 16 |

| 2.11       | Variation in transconductance $g_m$ and output resistance $r_o$ with (a) the epi-layer thickness $t_{ep}$ and (b) epi-layer doping $n_{ep}$ in the nDGLTFET.                                        | 16 |

| 2.12       | Comparison of the (A) $C_{GS}$ - $ V_{GS} $ (B) $C_{GD}$ - $ V_{GS} $ characteristics of nDGLTFET,                                                                                                  |    |

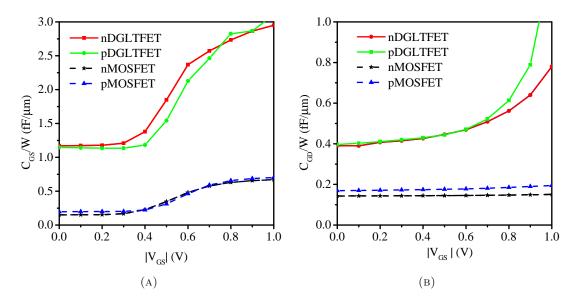

| 0.10       | pDGLTFET, nMOSFET & pMOSFET at $ V_{DS} =1$ V                                                                                                                                                       | 17 |

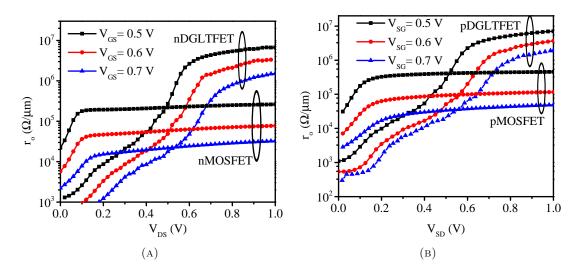

| 2.13       | The output resistance $r_o$ as a function of (A) $V_{DS}$ in nDGLTFET & nMOSFET<br>for different $V_{GS}$ , as well as (B) $V_{SD}$ in pDGLTFET & pMOSFET for different                             |    |

|            | $V_{SG}$                                                                                                                                                                                            | 17 |

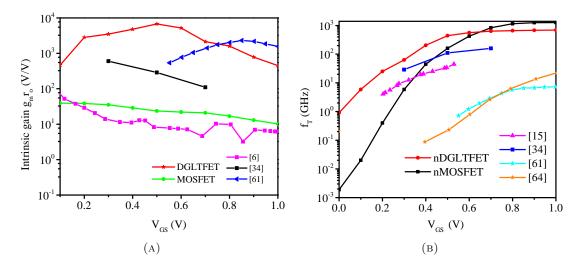

| 2.14       | Comparison of (a) the intrinsic gain $g_m r_o$ and (b) the unity-gain frequency $f_T$ of DGLTFET, the equivalent MOSFET at the same technology node and other                                       |    |

|            | TFETs at $V_{DS}=1$ V.                                                                                                                                                                              | 18 |

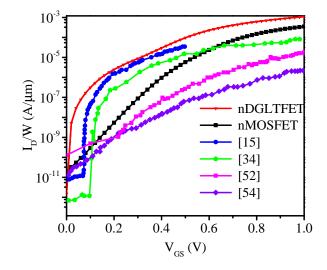

| 2.15         | Comparison of the DGLTFET $I_D$ - $V_{GS}$ characteristics with other TFETs reported earlier.                                                                                             | 21              |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| $3.1 \\ 3.2$ | Flowchart explaining the co-simulation methodology used in this work (a) Circuit schematics and the (b) equivalent circuits of the CS amplifier in                                        | 23              |

| 3.3          | resistive-load and cascode configurations                                                                                                                                                 | 24              |

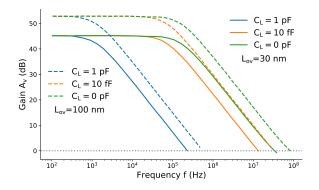

| 3.4          | (B) cascode configuration under $C_L = 0$ , 10 fF, 1 pF                                                                                                                                   | 25              |

| 3.5          | reported TFETs in terms of the AC analyses                                                                                                                                                | 25<br>26        |

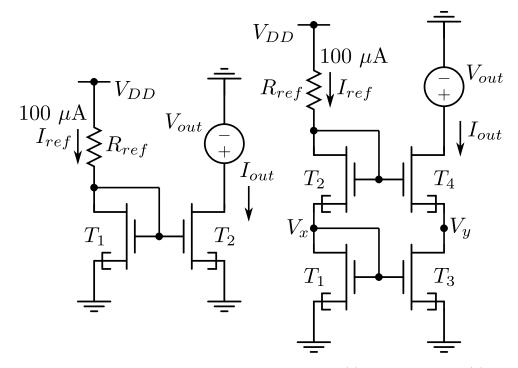

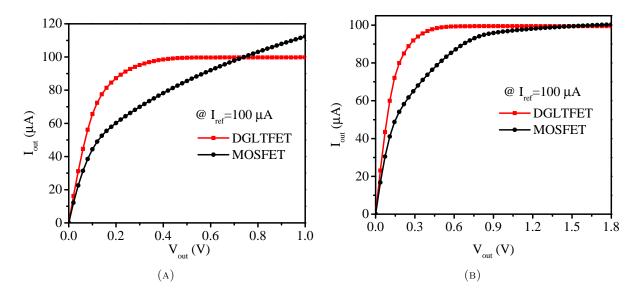

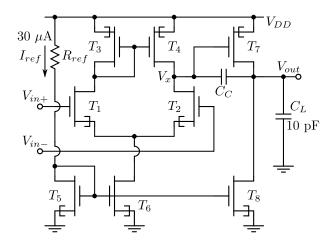

| 3.6          | V. Circuit schematics of the current mirrors in (a) single-stage and (b) cascode configurations.                                                                                          | 26<br>28        |

| 3.7          | $I_{out}$ vs. $V_{out}$ in (A) the single-stage current mirror. (B) the cascode current mirror.                                                                                           | $\frac{20}{29}$ |

| 3.8          | Output resistance $R_{out}$ of (A) single stage and (B) cascode current mirror                                                                                                            | $\frac{-0}{30}$ |

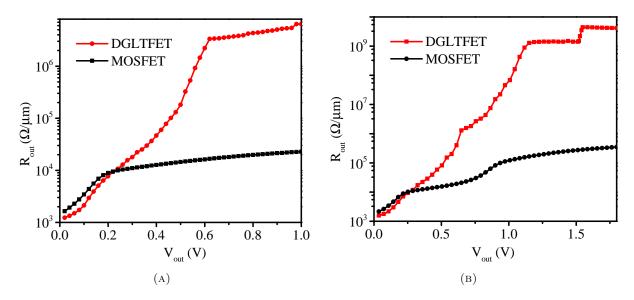

| 3.9          | Schematic of a two-stage complementary DGLTFET op-amp                                                                                                                                     | 30              |

| 3.10         | (a) The overall gains $A_v$ of the two-stage op-amp for an $f_T=5$ MHz. (b) The differential $A_d$ and common mode (CM) gains $A_{cm}$ of the op-amp differential                         |                 |

|              | stage for the overall $f_T = 5$ MHz.                                                                                                                                                      | 32              |

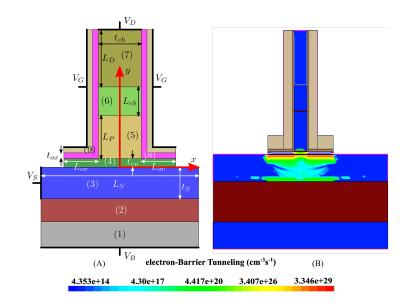

| 4.1          | (a) Schematic cross-sectional view (1) Si substrate (2) SOI (3) $p^+$ SiGe Source (4) $n^+$ Si epitaxial layer (5) i-SiGe Pocket (6) i-Si channel (7) $n^+$ Si drain (8) HfO <sub>2</sub> |                 |

|              | gate oxide (9) TiN metal gate. (b) Electron BtB tunneling rate of nVLTFET device.                                                                                                         | 35              |

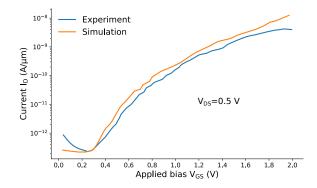

| 4.2          | Calibration of simulation models with the prefabricated device at $V_{DS}=0.5$ V [103]                                                                                                    | 38              |

| 4.3          | (a) $I_D$ - $V_{GS}$ characteristics of nVLTFET for different $V_{DS}$ and (b) $I_D$ - $V_{DS}$ characteristics of nVLTFET for different $V_{GS}$ .                                       | 39              |

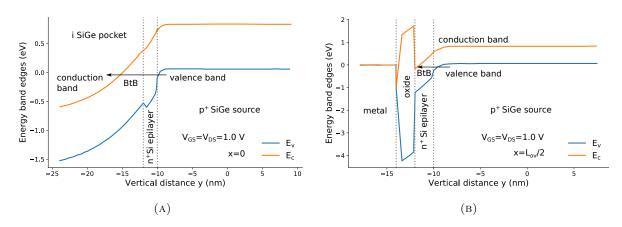

| 4.4          | BtB tunneling profile along the (a) Source & Pocket (@x=0) and (b) Source & Epi-layer (@x= $L_{ov}/2$ ) in the n-type VLTFET for $V_{GS}=V_{DS}=1$ V                                      | 39              |

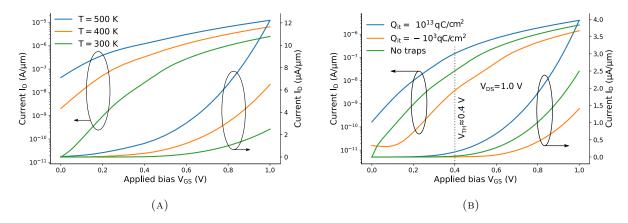

| 4.5          | (a) Influence of temperature on the VLTFET characteristics. (b) Effect of interface trap charges on $I_D$ - $V_{GS}$ characteristics.                                                     | 40              |

| 4.6          | Effect of (a) eDensity (b) Surface potential at the epi-layer region for different values of $V_{DS}$                                                                                     | 41              |

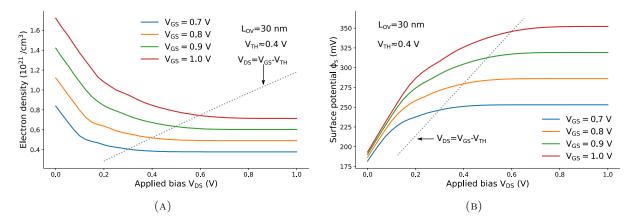

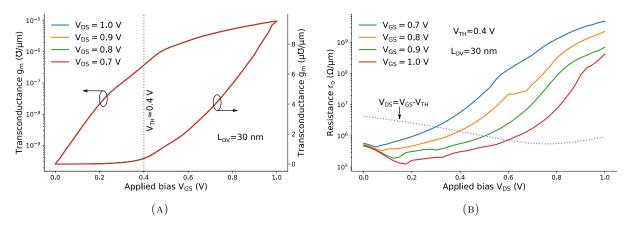

| 4.7          | Variation in (A) transconductance $g_m$ and (B) output resistance $r_o$ in the VLTFET.                                                                                                    | 41              |

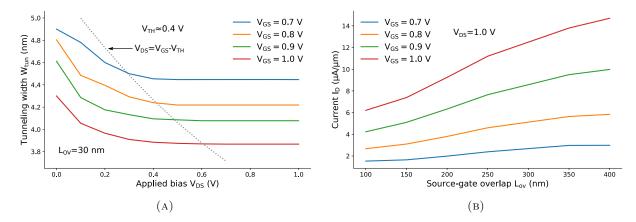

| 4.8          | (a) Variation of tunneling width $W_{tun}$ with $V_{DS}$ for different $V_{GS}$ values. (b) $I_D$ variation with $L_{ov}$ for different $V_{GS}$ values at $V_{DS}=1$ V                   | 42              |

| 4.9          | Variation with $L_{ov}$ for uniferent $V_{GS}$ values at $V_{DS} = 1$ V.<br>Variation in (a) transconductance $g_m$ and (b) output resistance $r_o$ with $L_{ov}$ for                     | 44              |

| 1.0          | different $V_{GS}$ values at $V_{DS}=1$ V                                                                                                                                                 | 42              |

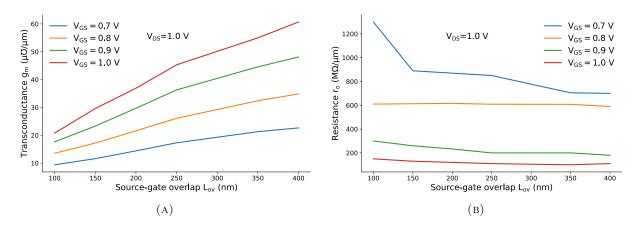

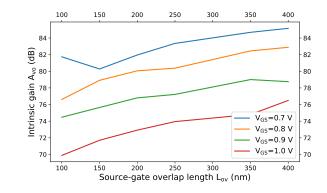

| 4.10         | Intrinsic Gain with $L_{ov}$ for different $V_{GS}$ values at $V_{DS}=1$ V                                                                                                                | 43              |

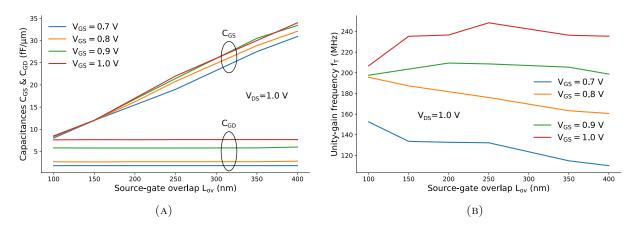

| 4.11         | Variation of (a) Gate Capacitance (b) $f_T$ with $L_{ov}$ for different $V_{GS}$ values at $V_{DS}=1$ V.                                                                                  | 43              |

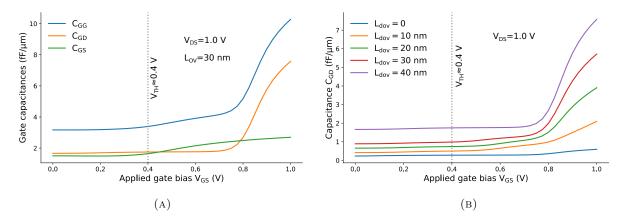

| 4.12         | V <sub>DS</sub> =1 V.<br>Variation of (a) gate capacitances with $V_{GS}$ at $V_{DS}=1$ V and (b) $C_{GD}$ with $V_{GS}$                                                                  | 40              |

|              | for different $L_{dov}$ values at $V_{DS}=1$ V                                                                                                                                            | 44              |

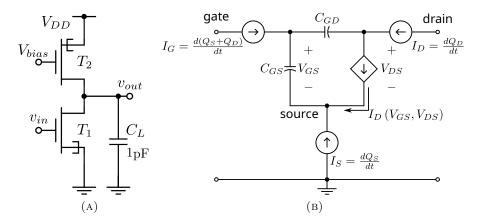

| 4.13         | (a) Schematic and (b) equivalent circuit of the CS amplifier in cascode configura-<br>tions. The dc biases $V_{DD}=1$ V, $V_{bias}=V_{DD}/2$ .                                            | 44              |

| 4.14         | (a) $I_S$ - $V_{SG}$ characteristics of pVLTFET for different $V_{SD}$ and (b) $I_S$ - $V_{SD}$ characteristics                                                                           | -1-1            |

|              | teristics of pVLTFET for different $V_{SG}$ .                                                                                                                                             | 45              |

| 4.15         | AC analyses of the CS amplifier with cascode configuration under $C_L$ =no load,<br>10 fF, 1 pF                                                                                           | 46              |

| 4.16 | Variation of (a) $I_{out}$ and (b) $R_{out}$ with increasing $V_{out}$ of cascode current mirror with $L_{ov}=30$ nm, under a reference current $I_{ref}=1$ $\mu$ A                                                                                                                                                                                                                                                                                                                                  | 46 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

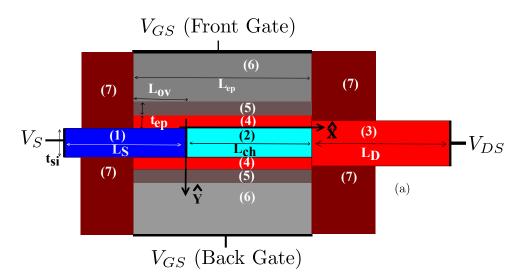

| 5.1  | (a) Schematic of the proposed GOTFET device. (b) Electron & (c) Hole BtB generation in nGOTFET & pGOTFET respectively.                                                                                                                                                                                                                                                                                                                                                                               | 50 |

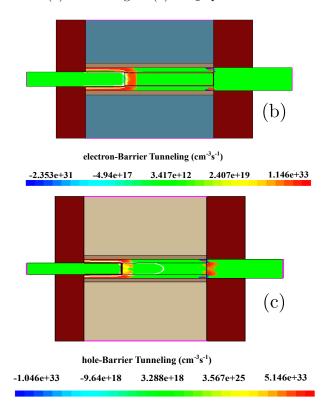

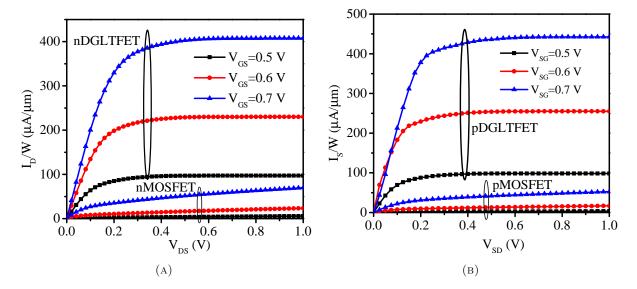

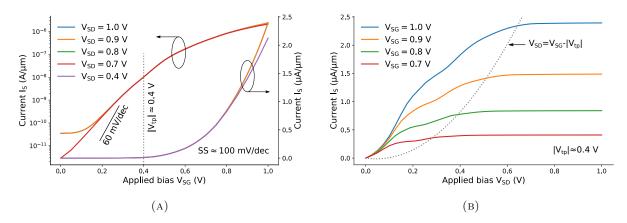

| 5.2  | (a) $I_D$ - $V_{GS}$ characteristics of nGOTFET & nMOSFET for different values of $V_{DS}$ .<br>(b) $I_S$ - $V_{SG}$ characteristics of pGOTFET & pMOSFET for different values of $V_{SD}$ .                                                                                                                                                                                                                                                                                                         | 52 |

| 5.3  | (a) Schematic of the proposed nGOTFET and (b) its corresponding electron BtB generation.                                                                                                                                                                                                                                                                                                                                                                                                             | 53 |

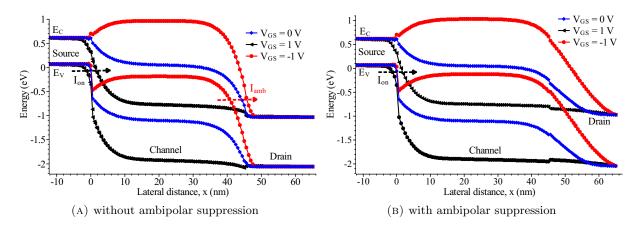

| 5.4  | Energy band diagram of the proposed nGOTFET (a) without gate overlap on the drain side with $N_D = N_S = 10^{20} / \text{cm}^3$ and (b) with gate overlap on the drain side with $N_D = 10^{19} / \text{cm}^3 \& N_S = 10^{20} / \text{cm}^3$ for $V_{GS} = 0$ V, $V_{GS} = 1$ V, $V_{GS} = -1$ V and $V_{DS} = 1$ V.                                                                                                                                                                                | 54 |

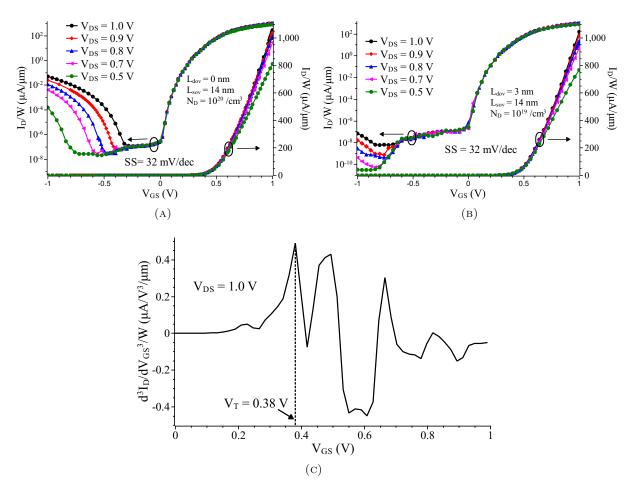

| 5.5  | (a) $I_D$ - $V_{GS}$ characteristics of proposed nGOTFET for different values of $V_{DS}$ with $N_D = N_S = 10^{20}$ /cm <sup>3</sup> , without gate-drain overlap (b) $I_D$ - $V_{GS}$ characteristics of proposed nGOTFET for different values of $V_{DS}$ with $N_D = 10^{19}$ /cm <sup>3</sup> & $N_S = 10^{20}$ /cm <sup>3</sup> , with gate-drain overlap. (c) Threshold voltage $V_T$ extracted from the characteristics of proposed nGOTFET using the 3 <sup>rd</sup> derivative method [74] | 55 |

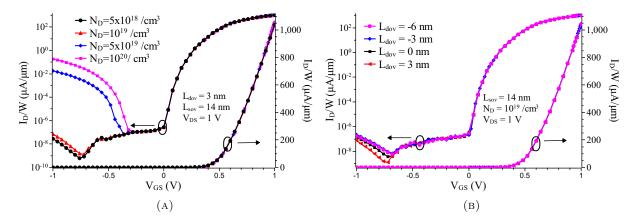

| 5.6  | (a) $I_D$ - $V_{GS}$ characteristics of the proposed nGOTFET showing the influence<br>of drain doping $N_D$ on the ambipolar conduction (b) $I_D$ - $V_{GS}$ characteristics of<br>the proposed nGOTFET showing the influence of gate-drain overlap $L_{dov}$ on<br>ambipolar conduction                                                                                                                                                                                                             | 56 |

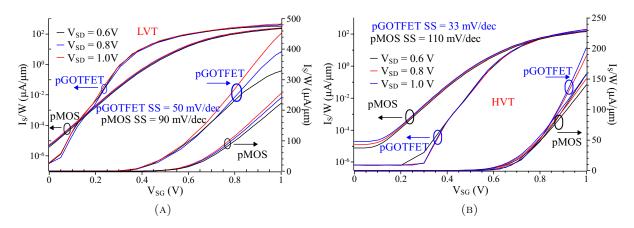

| 5.7  | $I_D$ - $V_{GS}$ characteristics of (A) LVT (B) HVT nGOTFETs for different values of $V_{DS}$ .                                                                                                                                                                                                                                                                                                                                                                                                      | 57 |

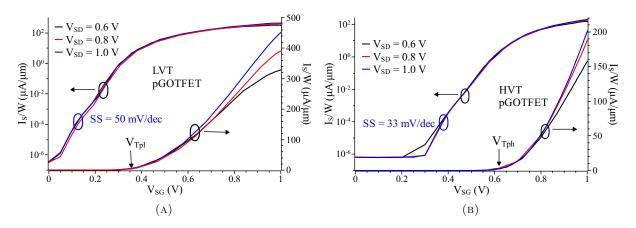

| 5.8  | $I_S$ - $V_{SG}$ characteristics of (A) LVT (B) HVT pGOTFETs for different values of                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | $V_{SD}$ . $V_{Tpl}$ & $V_{Tph}$ denote the Low & High threshold voltages of the LVT & HVT pGOTFETs respectively                                                                                                                                                                                                                                                                                                                                                                                     | 57 |

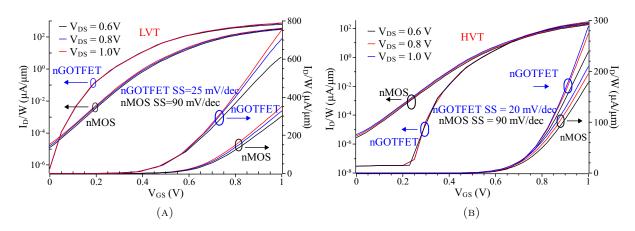

| 5.9  | $I_D$ - $V_{GS}$ characteristics of (A) LVT (B) HVT nGOTFET & nMOSFET for different values of $V_{DS}$ .                                                                                                                                                                                                                                                                                                                                                                                             | 58 |

| 5.10 | $I_S$ - $V_{SG}$ characteristics of (A) LVT (B) HVT pGOTFET & pMOSFET for different values of $V_{SD}$                                                                                                                                                                                                                                                                                                                                                                                               | 58 |

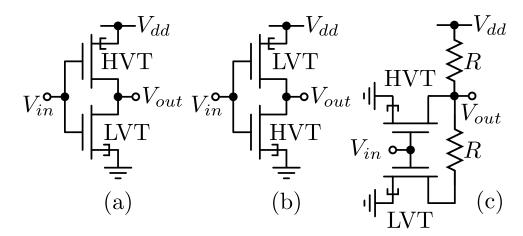

| 5.11 | Schematics of the LVT & HVT CGOT (a) NTI, (b) PTI & (c) STI cells with 100 $k\Omega \leq R \leq 100 \text{ M}\Omega$ [121].                                                                                                                                                                                                                                                                                                                                                                          | 59 |

| 5.12 | Static power consumption of (a) CGOT and (b) CMOS NTI cells. (c) Comparison of the delay characteristics of CGOT vs. CMOS NTI cell.                                                                                                                                                                                                                                                                                                                                                                  | 60 |

| 5.13 | Static power consumption of (a) CGOT and (b) CMOS PTI cells. (c) Comparison of the delay characteristics of CGOT vs. CMOS PTI cell.                                                                                                                                                                                                                                                                                                                                                                  | 61 |

| 5 14 | Comparison of the delay & power characteristics of CGOT vs. CMOS STI cells.                                                                                                                                                                                                                                                                                                                                                                                                                          | 62 |

|      | (A) $I_D$ - $V_{GS}$ characteristics of dual-threshold nGOTFETs for different values of                                                                                                                                                                                                                                                                                                                                                                                                              | 0- |

|      | $V_{DS}$ . (B) $I_S$ - $V_{SG}$ characteristics of dual-threshold pGOTFETs for different values of $V_{SD}$ .                                                                                                                                                                                                                                                                                                                                                                                        | 63 |

| 6.1  | (a) Schematic of CGOT inverter (b) Delay comparison CGOT vs. CMOS inverter.                                                                                                                                                                                                                                                                                                                                                                                                                          | 66 |

| 6.3  | Schematic of CGOT digital circuits : 2 input (a) NAND (b) NOR (c) XNOR gates.                                                                                                                                                                                                                                                                                                                                                                                                                        | 67 |

| 6.2  | Comparison of static currents (a) CGOT vs. (b) CMOS inverter                                                                                                                                                                                                                                                                                                                                                                                                                                         | 67 |

| 6.4  | (a) Delay comparison CGOT vs. CMOS NAND gates. Comparison of static currents (b) CGOT vs. (c) CMOS NAND gates.                                                                                                                                                                                                                                                                                                                                                                                       | 68 |

| 6.5  | <ul><li>(a) Delay comparison CGOT vs. CMOS NOR gates. Comparison of static currents</li><li>(b) CGOT vs. (c) CMOS NOR gates.</li></ul>                                                                                                                                                                                                                                                                                                                                                               | 69 |

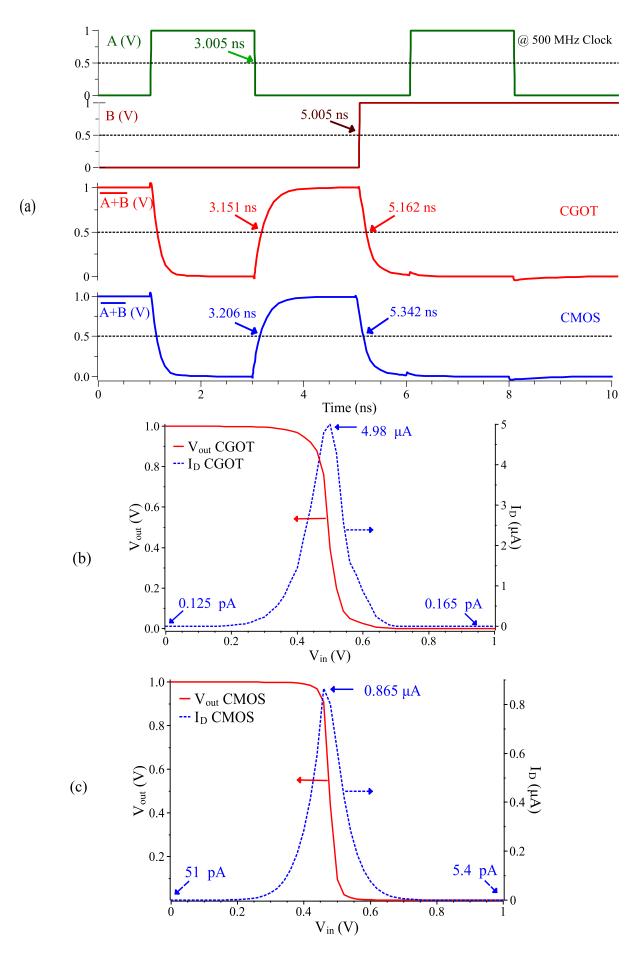

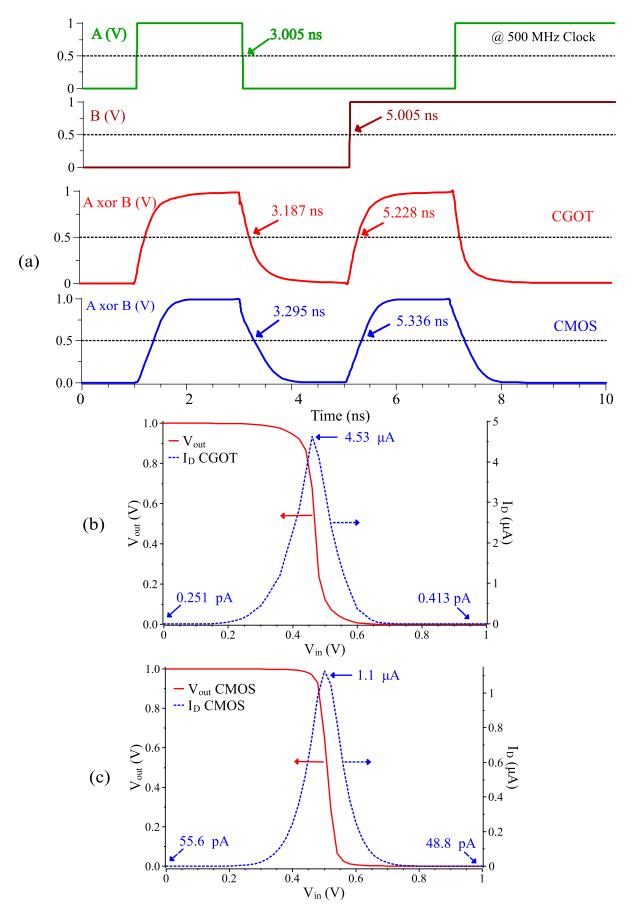

| 6.6  | (a) Delay comparison CGOT vs. CMOS XOR gates. Comparison of static currents            |    |

|------|----------------------------------------------------------------------------------------|----|

|      | (b) CGOT vs. (c) CMOS XOR gates.                                                       | 70 |

| 6.7  | Schematic of the CGOT double-tail dynamic comparator with conventional design.         | 72 |

| 6.8  | (a) Bench marking the delay characteristics of conventional CGOT vs. CMOS              |    |

|      | double-tail comparator.                                                                | 73 |

| 6.9  | (a) Static power consumption of CMOS contrasted with that of (b) CGOT                  |    |

|      | conventional double-tail comparator.                                                   | 74 |

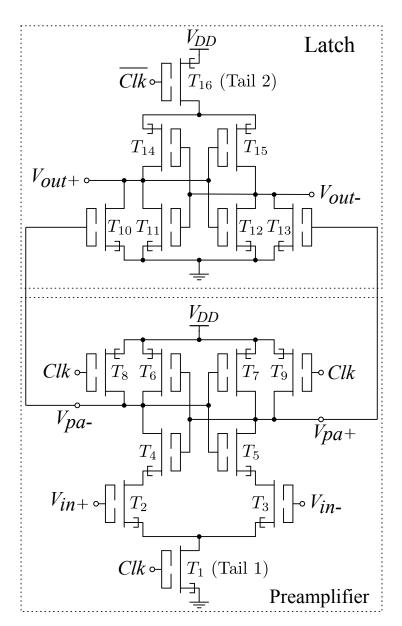

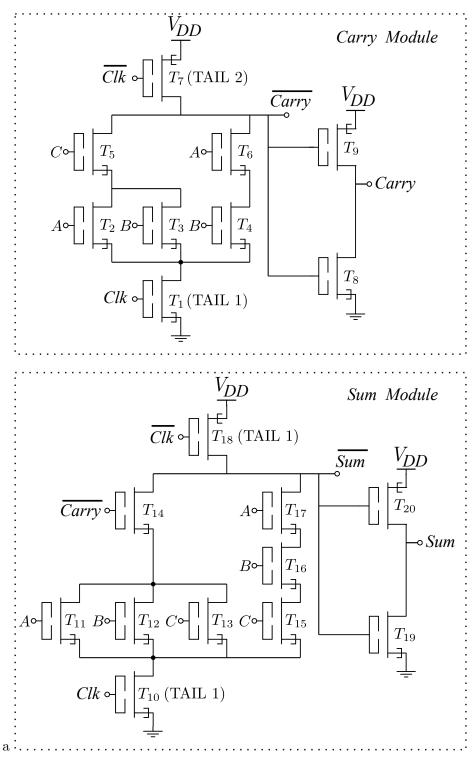

| 6.10 | Schematic of the CGOT based conventional DFA                                           | 76 |

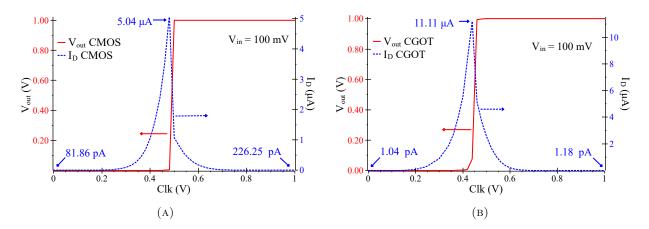

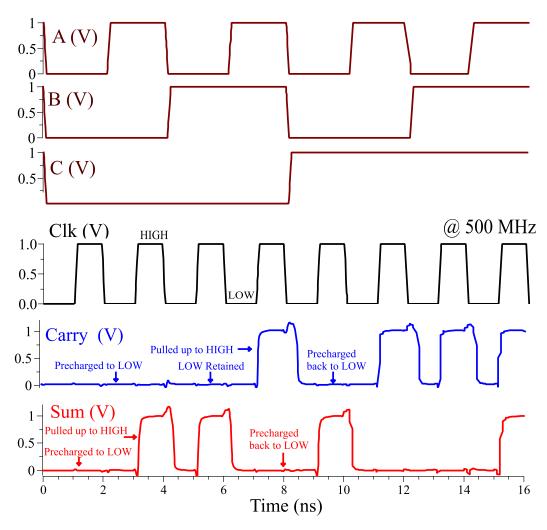

| 6.11 | Operation of CGOT DFA at 500 MHz <i>Clk</i>                                            | 77 |

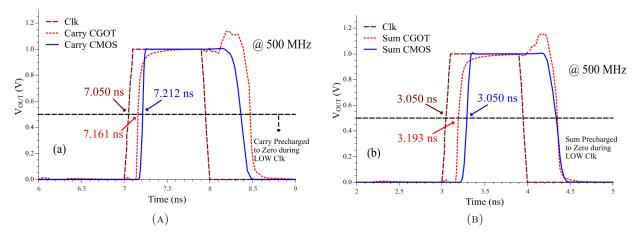

| 6.12 | Benchmarking the delay characteristics for the (a) carry $CY$ and (b) sum $S$ signals. | 78 |

| 6.13 | Static Power Consumption of (a) CMOS DFA (b) CGOT DFA                                  | 78 |

| 6.14 | Schematic of the CGOT conventional Schmitt trigger inverter/buffer                     | 79 |

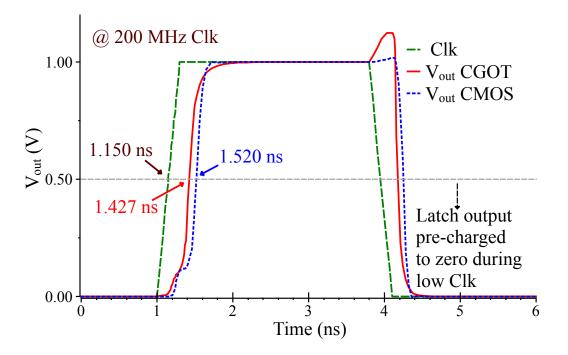

| 6.15 | Transient switching characteristics of the CGOT vs. CMOS conventional Schmitt          |    |

|      | trigger inverter/buffer at a capacitive load of 20 fF                                  | 80 |

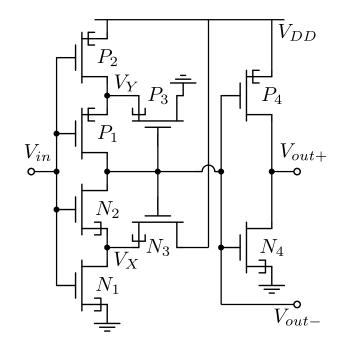

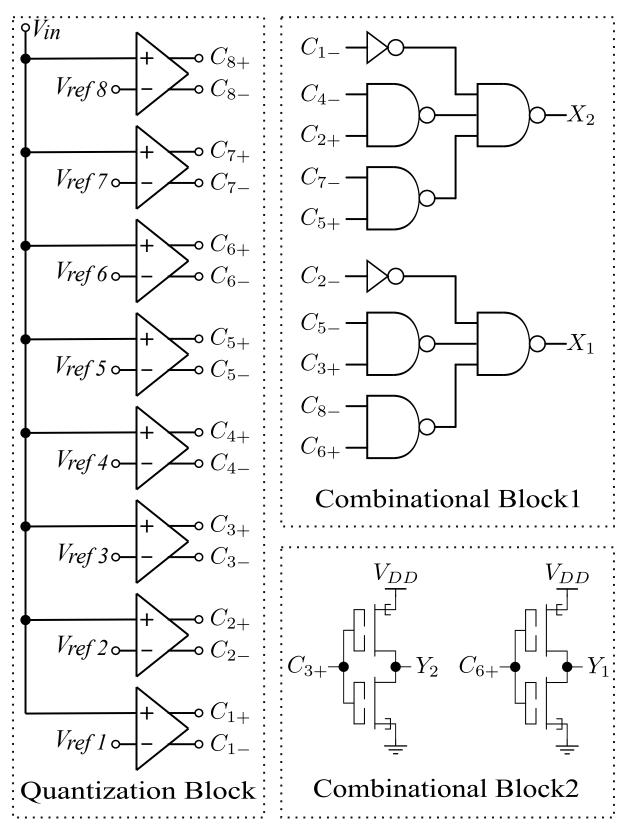

| 6.16 | Schematic of the input stage & combinational logic circuit of the proposed GOT-        |    |

|      | FET 2-bit ternary flash ADC                                                            | 83 |

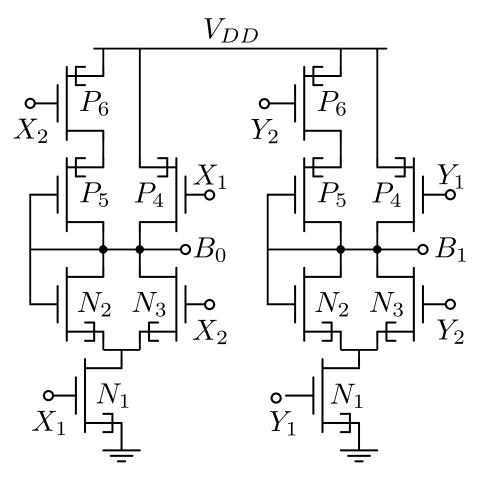

| 6.17 | Schematic of the encoder used in the output stage of the proposed CGOT 2-bit           |    |

|      |                                                                                        | 84 |

| 6.18 | Performance plot of encoder.                                                           | 84 |

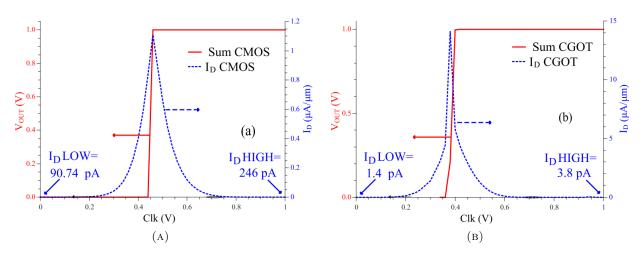

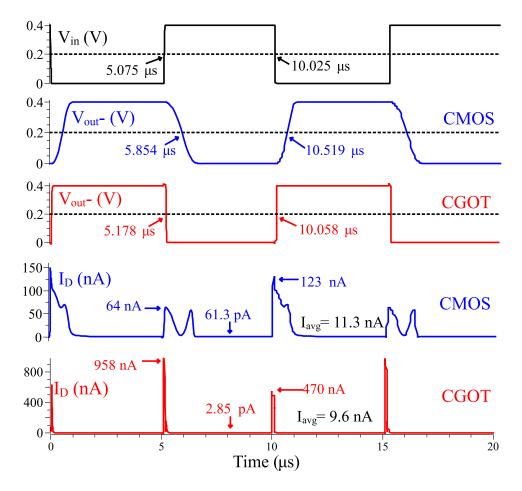

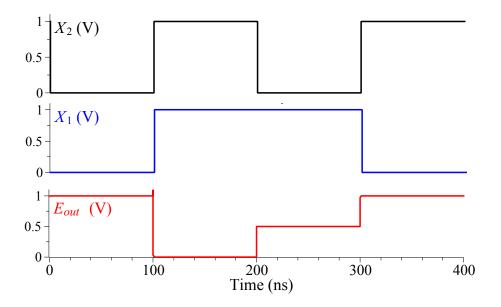

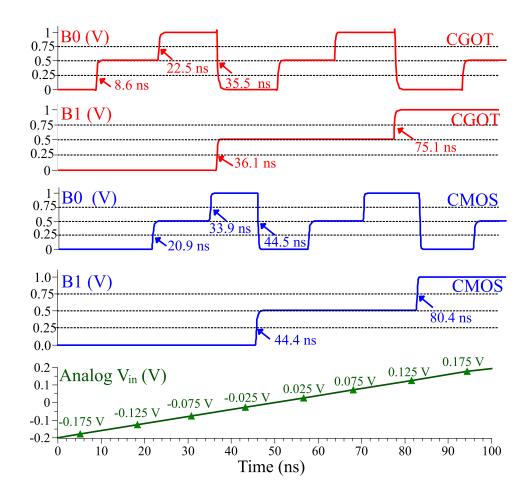

| 6.19 | Transient response of the proposed CGOT Ternary ADC output vs. CMOS ADC                |    |

|      |                                                                                        | 85 |

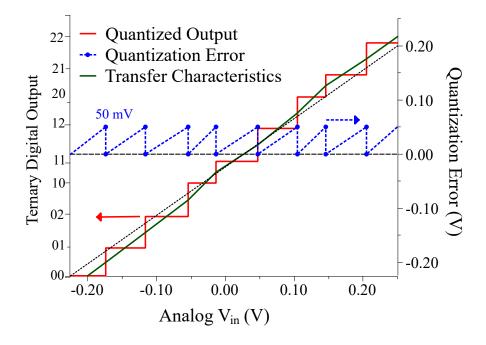

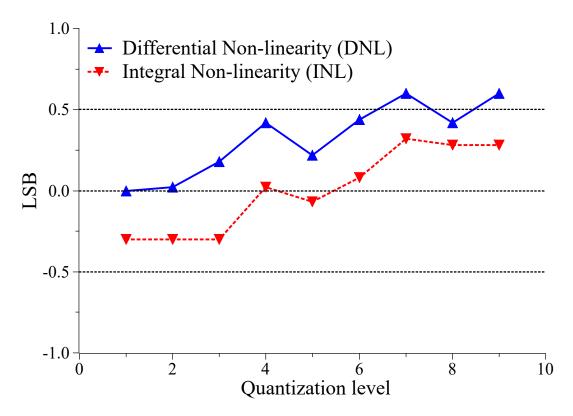

| 6.20 | Static Characteristics of proposed ternary ADC.                                        | 87 |

| 6.21 | Differential Non-linearity (DNL) and Integral Non-linearity (INL) Characteristics      |    |

|      | of proposed ternary ADC                                                                | 87 |

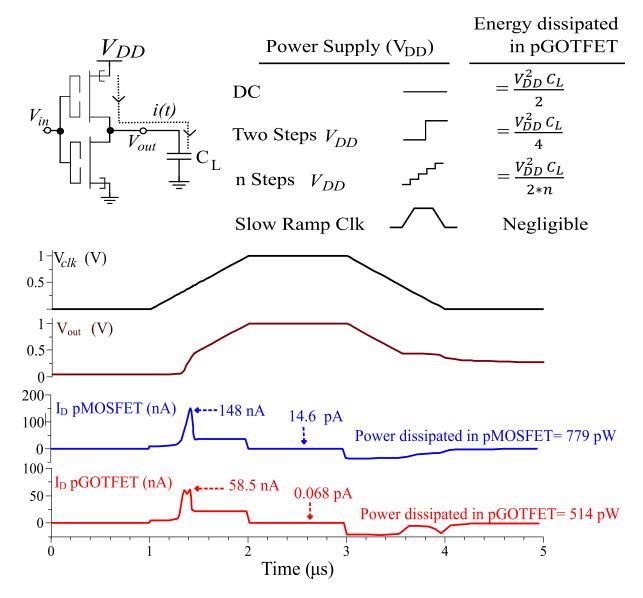

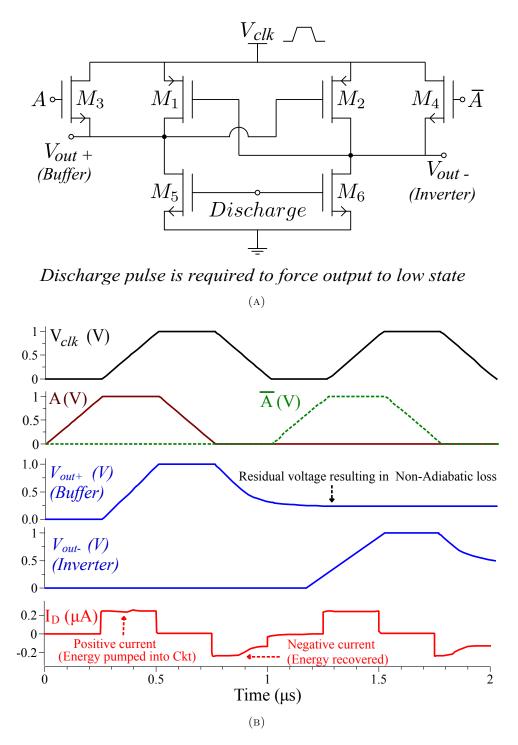

|      |                                                                                        | 89 |

|      |                                                                                        | 91 |

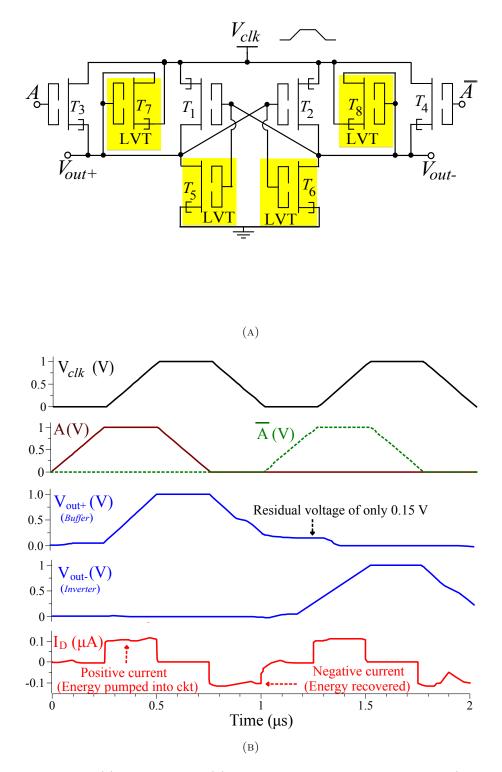

| 6.24 | (a) Schematic and (b) performance plots of GOTAL inverter/buffer                       | 93 |

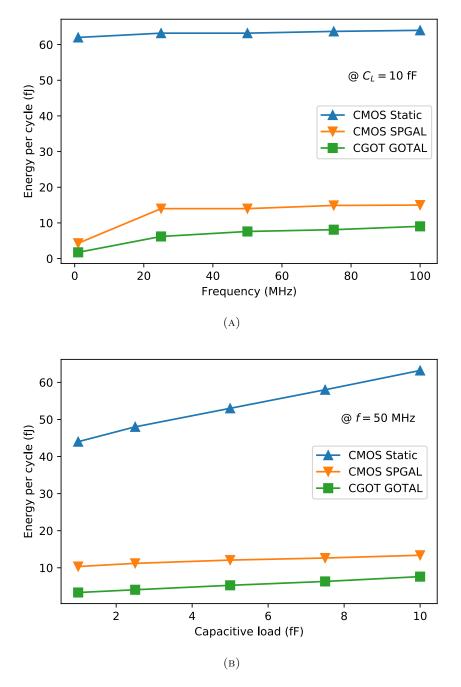

| 6.25 | Variation of the energy consumed from the power clock per cycle in GOTAL               |    |

|      | inverter/buffer circuit with (a) power clock frequency under a capacitive load of      |    |

|      |                                                                                        | 94 |

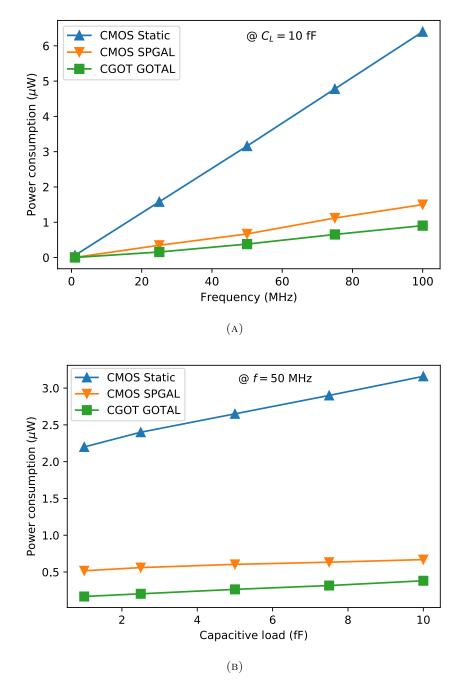

| 6.26 | Variation of the power consumed in GOTAL inverter/buffer circuit with (a) power        |    |

|      | clock frequency under a capacitive load of 10 fF and (b) capacitive load at 50         |    |

|      | MHz power clock frequency.                                                             | 95 |

## Abbreviations

| ADC                     | Analog to Digital Converter                                                                                                                                                                                                                                      |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\mathbf{BtB}$          | Band-to-Band                                                                                                                                                                                                                                                     |

| $\mathbf{CMOS}$         | Complementary Metal Oxide Semiconductor                                                                                                                                                                                                                          |

| CGOT                    | Complementary Gate-Overlap TFET                                                                                                                                                                                                                                  |

| DGTFET                  | $\mathbf{D} \mathbf{o} \mathbf{u} \mathbf{b} \mathbf{l} \mathbf{c} \mathbf{f} \mathbf{c} \mathbf{t} \mathbf{T} \mathbf{c} \mathbf{n} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{t} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} \mathbf{s} s$ |

| DMDG                    | Dual Metal Double Gate                                                                                                                                                                                                                                           |

| <b>DP-DGTFET</b>        | $\mathbf{D}$ rain- $\mathbf{P}$ ocket $\mathbf{D}$ ouble $\mathbf{G}$ ate $\mathbf{T}$ FT                                                                                                                                                                        |

| DIBL                    | Drain Induced Barrier Lowering                                                                                                                                                                                                                                   |

| DFA                     | $\mathbf{D}$ ynamic $\mathbf{F}$ ull $\mathbf{A}$ dder                                                                                                                                                                                                           |

| $\mathbf{E}\mathrm{TL}$ | Epitaxial Layer                                                                                                                                                                                                                                                  |

| GOTFET                  | Gate-Overlap Tunnel Field Effect Transistors                                                                                                                                                                                                                     |

| GAA                     | Gate All Around                                                                                                                                                                                                                                                  |

| HVT                     | High $\mathbf{V}_T$ Transistors                                                                                                                                                                                                                                  |

| HDB                     | $\mathbf{H} eterodielectric \ \mathbf{B} O X$                                                                                                                                                                                                                    |

| LGOTFETs                | $\mathbf{Line-Tunneling} \ \mathbf{Gate-Overlap} \ \mathbf{T}\mathbf{unnel} \ \mathbf{F}\mathbf{ield} \ \mathbf{E}\mathbf{ffect} \ \mathbf{T}\mathbf{ransistors}$                                                                                                |

| FA                      | $\mathbf{Full} \ \mathbf{A} \mathrm{dder}$                                                                                                                                                                                                                       |

| LVT                     | Low $\mathbf{V}_T$ Transistors                                                                                                                                                                                                                                   |

| $\mathbf{LUT}$          | $\mathbf{Look}$ - $\mathbf{Up} \ \mathbf{T}$ able                                                                                                                                                                                                                |

| MOSFETs                 | $\mathbf{M}$ etal-Oxide $\mathbf{S}$ emiconductor $\mathbf{F}$ ield $\mathbf{E}$ ffect $\mathbf{T}$ ransistors                                                                                                                                                   |

| NTI                     | Negative Ternary Inverter                                                                                                                                                                                                                                        |

| PTI                     | Positive Ternary Inverter                                                                                                                                                                                                                                        |

| PDP                     | Power Delay Product                                                                                                                                                                                                                                              |

| PTL                     | Pass Transistor Logic                                                                                                                                                                                                                                            |

| STI                     | Standard Ternary Inverter                                                                                                                                                                                                                                        |

| SS                      | Inverse Subthreshold Slope                                                                                                                                                                                                                                       |

| Silicon on Insulator                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Triple Metal Double Gate                                                                                                                                                          |

| Very Large Scale Integrated Circuit                                                                                                                                               |

| $\mathbf{D} \text{ouble } \mathbf{G} \text{ate } \mathbf{L} \text{ine } \mathbf{T} \text{unneling } \mathbf{F} \text{ield } \mathbf{E} \text{ffect } \mathbf{T} \text{ransistor}$ |

| Common Mode Rejection Ratio                                                                                                                                                       |

| Atomic Vapor Deposition                                                                                                                                                           |

| Atomic Layer Deposition                                                                                                                                                           |

| $\mathbf{F}$ ield Induced Qunatum Confinement                                                                                                                                     |

| Shockly Read Hall                                                                                                                                                                 |

| $\mathbf{V} ertical \ \mathbf{L} ine \ \mathbf{T} unneling \ \mathbf{F} ield \ \mathbf{E} ffect \ \mathbf{T} ransistor$                                                           |

| $\mathbf{T} echnology \ \mathbf{C} omputer \ \mathbf{A} ided \ \mathbf{D} esign$                                                                                                  |

|                                                                                                                                                                                   |

### Chapter 1

## Introduction

#### 1.1 Motivation and Related Work

The overall power consumption has increased over the past decade with continuous scaling and an increasing number of transistors per unit area. In power-constrained applications, in order to minimize the dynamic power  $P_{dyn}$ , consumption, we need to scale the supply voltage,  $V_{DD}$ , and correspondingly, the threshold voltage,  $V_t$ , to maintain the same on-state current,  $I_{on}$ , for the same performance [1, 2, 3]. However, in CMOS technology, static power consumption increases with the scaling of  $V_t$  due to increasing leaking currents. Reduction of static power consumption is a prominent challenge in modern computing systems, from mobile System on Chip (SOC) to data center applications. In order to maintain the same performance as required  $I_{on}$ current and power consumption,  $V_{DD}$  has been scaling down in the latest technology generations. In order to address the static power consumption problem, researchers worldwide have been exploring new transistors in the recent past. New devices such as carbon nanotube FETs (CNFETs), graphene FETs (GFETs), and tunnel FETs (TFETs) are designed by changing the structure and material properties of conventional MOS devices. Among these devices, TFETs are considered the most promising "beyond-CMOS" technology due to their compatibility with standard CMOS technology and superior inverse sub-threshold slope, SS characteristics of lower than 60 mV/dec at room temperature (T=300 K), which is the theoretical minimum SS for CMOS technology. Having lower SS than similar MOSFETs, TFETs can switch between the on and off states consuming lower  $P_{dyn}$  than equivalent MOSFETs, while lower  $I_{off}$  ensures lower leakage power than equally-sized MOSFET counterparts at the same technology nodes [4, 5]. The TFET technology replaces conventional diffusion-based minority carrier injection

in the case of MOSFETs with Band-to-Band (BtB) tunneling-based minority carrier injection into the channel [6, 7]. TFET's basic structure is the gated PIN diode whose  $I_{on}$  arises from BtB generation [8]. This significantly improves SS and power consumption characteristics far beyond the standard CMOS technology [9, 10]. SOI-based structures [11, 12] have been reported to overcome short-channel effects, lower SS, improve soft-error immunity, and improve electrostatics. If we want to replace the current MOSFETs in VLSI circuits with TFETs as viable switches [13, 14, 15], the TFET-based circuits must be as fast as the MOSFETs should have the same fan-out in the same circuit. However, the major limitation of traditional TFETs is that  $I_{on}$  is significantly lower than that of MOSFETs, and their inherent, am bipolar behavior. Inhomogeneous materials  $I_{on}$ :  $I_{off}$  ratio is poor, so it is difficult to get simultaneously high  $I_{on}$ and low  $I_{off}$ . In order to obtain high  $I_{on}$  currents,  $E_g$  should be low. However,  $I_{off}$  also increases due to Shockley Read Hall, SRH, generation-recombination mechanism. Heterojunction materials [16] are employed simultaneously to improve  $I_{on}$  currents and lower the  $I_{off}$  currents. To further improve  $I_{on}$ , properties of the gate stack, such as the gate materials, gate oxide thickness  $t_{ox}$ , and the oxide dielectric constants  $\varepsilon_{ox}$ , etc., have been engineered for optimal characteristics. Multiple gate structures like double-gate [17], gate-all-round [18], etc., improved gate control over the channel potentials improving the  $I_{on}$  current. Researchers are actively investigating alternative materials to Silicon, like Germanium [19, 20], III-V semiconductors [21, 22, 23], Nanowires [24], 2D transition metal dichalcogenides [25], etc., have been employed to boost  $I_{on}$  by reducing tunneling distances. Spacer engineering [26], asymmetric gate structure [27], and strain Engineering [28] improve the  $I_{on}$  in TFETs. Along with gate on source overlap [29, 30, 31] and source pocket [32, 33] structures were explored to improve  $I_{on}$  further.

Several researchers have analyzed the competitive benefits of TFET inverters vs. MOSFET-based CMOS inverters [34, 35, 36]. It indicates that TFET inverters are faster and more energy-efficient energy-efficient at lower supply voltages. At a low supply voltage,  $V_{DD} = 0.25$  V, TFET inverters perform ten times faster than FinFET inverters for the same static power dissipation [37]. At  $V_{DD}=0.6$  V, the authors have demonstrated an improvement in the energy consumption, and latency of the Manchester carry chain adder dynamic logic circuit utilizing the TFET compared to the FinFET [38]. A 4T TFET SRAM cell is 100 times faster than a low static power (LSP) 6T CMOS SRAM cell and uses three times less standby power than a high-performance (HP) 6T CMOS SRAM cell. In [39], the authors explained the possibility of Mixed TFET MOSFET 8T SRAM cells. The combination of TFET and MOSFET cells is more stable and efficient than the MOSFET and TFET cells alone. In addition to SRAMs, additional intriguing applications using

TFETs and flip-flops are also being studied [40, 41, 42].

TFETs have been investigated predominantly for digital applications and as a replacement for conventional MOSFETs for logic applications due to their superior sub-60 mV/dec SS characteristics and their higher  $I_{on}$ :  $I_{off}$  ratios [3]. At low supply voltages, TFET-based digital circuits have better energy efficiency compared to conventional CMOS. However, researchers have recently evaluated the merits of TFETs in different analog circuits. DC characteristics such as SS,  $I_{off}$ , threshold voltage,  $V_t$ , transconductance,  $g_m$ , output resistance,  $r_o$ , intrinsic gain, $g_m r_o$ , unity gain cut-off frequency,  $f_T$  are important analog parameters for bench-marking the TFETs with CMOS. The current saturation mechanism in the output characteristics of the TFET is quite different from the saturation mechanism of conventional MOSFET. As the channel becomes free from carriers, the currents in TFETs saturate, and the impact of drain potential on the source channel tunnel junction becomes negligible. Therefore, TFETs exhibit excellent current saturation and do not show channel length modulation. As a result,  $r_o$  of the TFETs is higher than MOSFETs [43].

In earlier papers [44, 45], CS amplifier with active load had been designed using  $g_m : I_D$  ratio method, AC gain is improved in heterojunction TFETs, HTFETs, and compared with FinFET with 14 nm technology. In [43], authors compared the performance of InAs homojunction and GaSb-InAs heterojunction TFET with Si TFET and applied to analog building blocks. The performance of analog circuits such as operational transconductance amplifier, OTA, using  $g_m : I_D$  in the sub-threshold region was studied for low-frequency operations. TFETs and HTFETs give higher DC gains than CMOS due to their higher output resistance. In [46, 47], authors showed improved performance of TFETs in cascode current mirror circuits due to their higher output resistance  $r_o$ .

#### 1.2 Objectives, Research Gaps, and Scope of this Work

Based on the literature review, the following are the research gaps and issues in TFET devices that are investigated, and the best possible LTFET structures have been proposed as part of the PhD thesis. The first aim of this research is to optimize the design of the TFET device, which will be used for designing novel analog and digital circuits with significant improvement in the performance parameters of the circuits for ultra-low power applications. Following are the proposed deliverable of this research problem, which is going to be investigated, and the optimal solutions will be addressed as part of this Ph.D. thesis

- 1. Most of the TFETs reported in the literature have low  $r_o$  and  $g_m$ , which affects their analog performance. There is a severe need to modify the design of conventional TFETs, resulting in higher  $r_o$  and  $g_m$ , which subsequently improve the analog performance.

- 2. In the literature, TFETs shown the device performance parameters improvement, but they didn't discuss the circuit performance.

- 3. Most TFETs in the literature explain how affecting the gate overlap on source length  $(L_{ov})$  improves digital circuit performance; they didn't discuss the analog performance of their circuits.

- 4. Most of the TFETs in the literature have very low  $I_{on}$  compared to MOSFETs. There is a substantial need to design a TFETs resulting in higher  $I_{on}$ , lower  $I_{off}$ , and lower SS.

- 5.  $L_{ov}$  places a significant role in LTFET devices. This thesis demonstrates the effect of  $L_{ov}$  on analog performance parameters and the circuits.

- 6. The Ternary logic design has received considerable attention from researchers worldwide because of its many advantages compared to digital logic. Hence there is a need to design the multi-threshold TFETs for ternary logic applications.

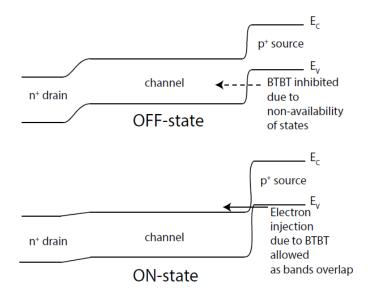

#### **1.3** Operating Principle of the Tunnel Field Effect Transistor

In MOSFETs, carrier injection is controlled by an electrostatic potential barrier at the sourcechannel pn junction. Minority carriers are injected from the source to the channel through diffusion transport. Only those injected minority carriers with energies exceeding the energy barrier can form the inverted channel and contribute to the  $I_{on}$ . On the other hand, TFETs are reverse-biased gated p-i-n tunnel diodes. These devices have asymmetric source and drain doping. Switching in TFETs is enabled by gate-controlled Band-to-band, BtB, tunneling phenomena at the source-channel junction [5]. Figure 1.1 shows the energy band diagram of an nTFET in different switching states. In its on state, band bending occurs at the source-channel junction hence the electrons from the valence band tunnel directly into the conduction band of the channel region. TFET is in its off state when the conduction band of the channel lies above the valence band of the source, preventing BtB tunneling, as depicted in Fig 1.1.

FIGURE 1.1: Energy band diagram of an nTFET [5]

#### **1.4** Contributions