# Design and Implementation of Low Complex Memristive Circuits using Machine Learning Algorithms for Signal Processing Applications

## THESIS

Submitted in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

by

## Priyanka B G

## ID. No. 2017PHXF0436H

Under the Supervision of

## Prof. BVVSN Prabhakar Rao

BITS Pilani Pilani | Dubai | Goa | Hyderabad

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

2023

## **BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI**

## **CERTIFICATE**

This is to certify that the thesis titled **Design and Implementation of Low Complex** Memristive Circuits using Machine Learning Algorithms for Signal Processing Applications submitted by Priyanka B G ID No 2017PHXF0436H for the award of Ph.D. of the Institute embodies original work done by her under my supervision.

Name in capital letters: Prof. BVVSN PRABHAKAR RAO

**Designation**: Professor,

Department of Electrical and Electronics Engineering,

BITS-Pilani, Hyderabad Campus.

Date: 20-10-23

### **Declaration of Academic Integrity**

I, Priyanka B G, declare that this written submission represents my ideas in my own words, and where others' ideas or words have been included; I have adequately cited and referenced the original sources. I also declare that I have adhered to all principles of academic honesty and integrity and have not misrepresented or fabricated, or falsified any idea/data/fact/source in my submission. I understand that any violation of the above will be cause for disciplinary action as per the rules and regulations of the Institute.

Print

Priyanka B G

### Acknowledgments

I would like to express my sincere gratitude to my supervisor Prof. BVVSN Prabhakar Rao of the Department of Electrical and Electronics Engineering, BITS Pilani, Hyderabad Campus, for giving me the opportunity to work under his guidance. My heartfelt gratitude for his valuable guidance, constant encouragement, and unwavering support throughout my research and thesis completion.

I am most grateful to Dr. Souvik Kundu for co-supervising me during his tenure at the EEE department BITS Pilani, Hyderabad Campus. His treasured guidance and relentless support have greatly facilitated my research and thesis completion.

I sincerely thank my Doctoral Advisory Committee (DAC) members, Dr. Syed Ershad Ahmed, and Dr. Chetan Kumar V, of the EEE department, for their prized suggestions and advise on my research work. My heartfelt thanks to Prof. Sanket Goel, Prof. Alivelu Manga Parimi, and Prof. Subhendu K. Sahoo, the former and the present heads of the Department of EEE, for their suggestions, help, and timely support.

I am thankful to Dr. Venkateswaran Rajagopalan, EEE department, for guiding me with his prized insights about research. I would like to thank all the faculty members, lab technicians, and office assistants of the EEE department for their extended help and support. My sincere thanks to my lab mates and scholars of the EEE department for offering a helping hand during my entire research tenure. I would also like to thank the team of undergraduate and postgraduate students who assisted me during different stages of my thesis. I also like to acknowledge the support extended by the administration, Research division, and library staff, whose student-friendly response made things easier during the Ph.D. journey.

Special thanks to Prof. Venkata Vamsi Krishna Venuganti, Associate Dean of AGSRD (Academic-Graduate Studies and Research Division) and Dr. Prashant Kumar Pattnaik, Dr. Prashant Wali, Prof. BVVSN Prabhakar Rao, and Dr. Sudha Radhika, the former and the present Conveners, Doctoral Research Committee Department of EEE, for their help with various official requirements.

I am deeply indebted to my beloved parents, Mrs. Lakshmi Bai S.N and Mr. Ganganaik N, for their immense encouragement to take up this work, untiring support, and unconditional love. I wholeheartedly dedicate this work to them.

My heartfelt gratitude to my brother, Chi. Preetham B.G. Kodavath, who has always been there. I also thank my parents-in-law, all my family members, and specially my friends, who all have been supportive and caring. This journey has been made worthwhile by my soulmate, my husband, Mr. Bharath A, I gratefully acknowledge his steadfast support and belief in me. My warmest acknowledgments to my daughter, Taneeshka K.A., who is joy of our life.

God has been always there, through thick and thin, the divine presence being my companion at the most unexpected times. I shall be eternally grateful to the divine power that guided and propelled me along the way.

Priyanka B G

#### Abstract

The idea of digital data calculation has become difficult as the prevalence of electronic gadgets in daily life has increased. The huge amount of data generated has caused computing to grow exponentially, necessitating the use of computational platforms in terms of design effectiveness and efficiency. Powerful approaches like machine learning and neural networks has been recognized as a suitable technology to deal with the enormous amount of data generated in dayto-day life. Contemporary computing systems, Von Neumann's architecture has drawback of having a constrained data transfer speed between the memory and processing units. This bottleneck has a negative impact on the performance of modern artificial intelligence (AI) algorithms. Also, it has significantly increased the energy consumption of these systems, especially in data-intensive computations. A promising solution to address this bottleneck is to integrate processing and memory by performing computations at the location where the data is stored. Thus, memory bottlenecks and high costs associated with data movements between primary memory and the processor are the challenges witnessed by modern-day computers and has led to the need for in-memory processing. Recently, memristor-enabled in-memory Processing has gained attraction as a possible solution to the Von Neumann bottleneck. Memristor has the inherent ability to store and process the data in the same location. It is a twoterminal passive device whose conductance depends on the amount of current that has passed through it. It is being proposed as a possible replacement for transistors because of its compact size, ultra-high packing density (~40% improvement), low power consumption (one-hundredth of transistors), large ON/OFF resistance ratio (105), and high switching speed (~100 ps). The most profound application of a memristive crossbar is a vector product accelerator of linear time complexity. It has an innate ability to carry out matrix-vector multiplication through varying weights, which fosters its usage for implementing machine learning algorithms. Also, it is notable to mention that memristive state transitions were made possible by utilizing external voltage sources. Importantly, the transitions traverse through intermediate resistive states that exist between the extreme resistive limits (ON and OFF states). Interestingly, these intermediate states can be explored for memory storage and computational applications. These two important aspects of the memristor has been explored and implemented in this work. In one of the studies about the fabrication of memristors, the fabrication of Pt/Cu:ZnO/Nb:STO based memristor was demonstrated and obtained improved electrical performances such as low SET/RESET voltages, high ON/OFF ratio, good data retention, and stability, all these are useful for signal processing applications. Thus throughout the thesis, we have used Cu:ZnO memristor.

In this regard, a systematic investigation has been initiated to design a memristor crossbarbased architecture to compute the Pearson Correlation Coefficient(PCC) within the memory array. Three different applications were demonstrated by computing PCC based on the proposed architecture. The first application is computing PCC between noisy and denoised Electrocardiogram(ECG) signals. Whereas the second application is face recognition, where we compute PCC between face images in the presence of occlusions and varying expressions. Finally, the third application is computing PCC between two models of H1N1 disease prediction to verify their similarity. Further, an effort is devoted to analyze the effect of device variations on these applications. An attempt is also made to perform detailed system-level comparisons of the proposed architecture against a Von Neumann architecture.

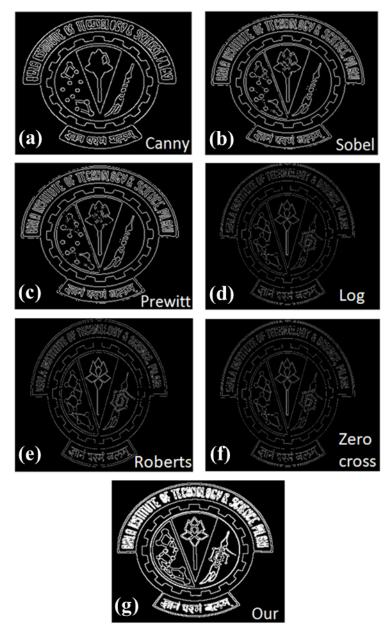

Considering the memristor's approach to use the crossbar for analog matrix multiplications, which is more suitable for data-intensive applications, efforts were directed towards creating an in-memory processor utilizing memristive crossbar architecture for Bayesian text classification. The approach involved utilizing memristive switches to store data required for text classification. Text classification is a critical aspect of digital media, including natural language processing, sentiment analysis, image labeling, chatbots, spam filtering, and translators. To evaluate the efficacy of the proposed circuit, it was tested on two different datasets comprising a total of 55,575 texts from Short Message Service (SMS) and Internet Movie Database (IMDb) datasets. Exploring the analog computing properties of the memristor, the state transition property of the memristor, which exhibits controllable transitions within its stable resistive states, is also studied. In this work, for the first time to the best of our knowledge, efforts are put into developing Memristive State Machine (MSM) through a simulation route for edge detection in an image. The idea of MSM was further extended to perform a tunable edge detection system for image processing applications. The obtained edge detection was compared with other popular conventional software-based edge detection systems such as Canny, Sobel, Prewitt, Log, Zerocross and Roberts.

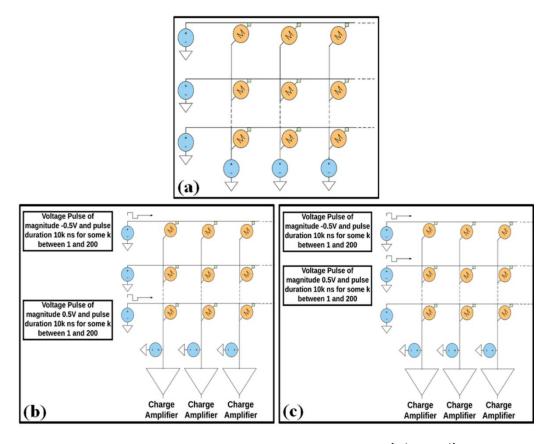

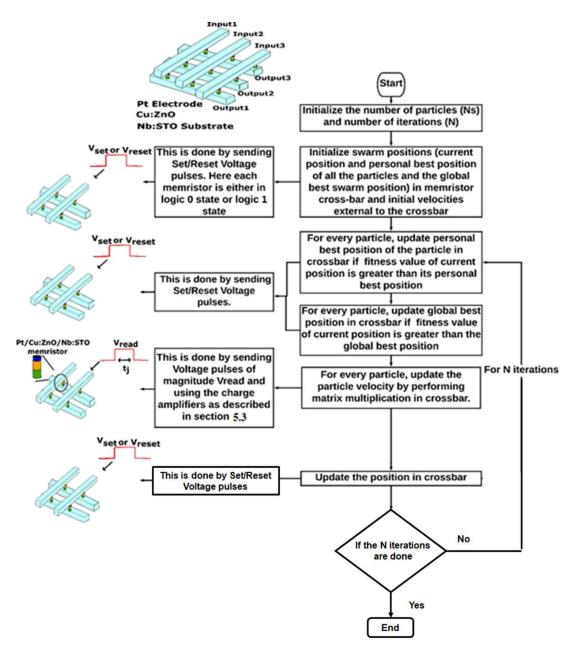

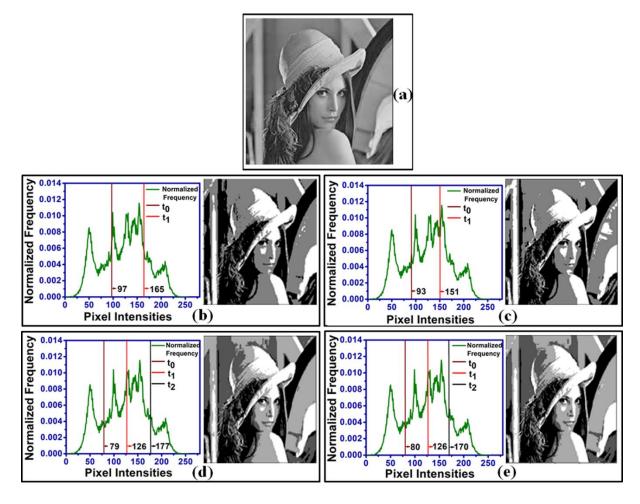

As we continue to examine the vector product accelerator application of the memristive crossbar array, we demonstrate a memristor-enabled computing in-memory architecture of an extensively utilized Binary Particle Swarm Optimization (BPSO) algorithm which has applications in diverse sectors. To the best of our knowledge, this is the first study pertaining to the implementation of BPSO on the memristor crossbar. Otsu's function and Kapur's entropy functions are considered the objective functions or the functions left for BPSO to optimize. To validate its potential, the commonly used Lena image was segmented and the performance of the memristor-crossbar was thoroughly analyzed. Further, this (Otsu and

Kapur's entropy with BPSO) is applied for thresholding four T2- weighted transaxial brain Magnetic Resonance Imaging (MRI) scans of the widely used online open-access medical image repository by Harvard Medical School. Later the values obtained by memristor implementation of BPSO are compared with the values obtained by brute force methods.

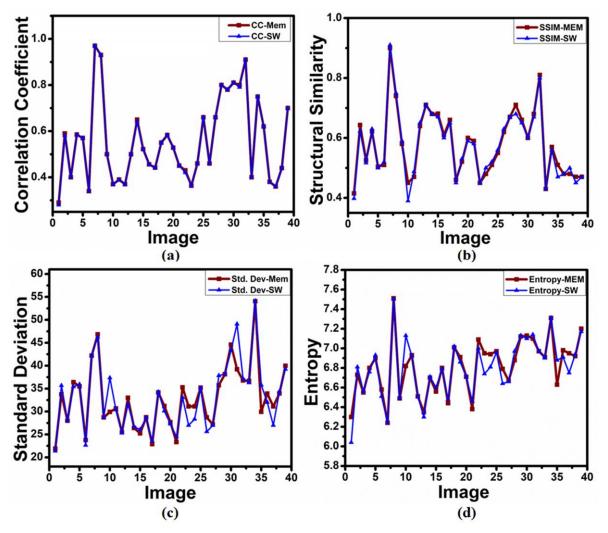

The growing use of image fusion for feature extraction, image segmentation, and object recognition in different fields necessitates a need for a faster and more efficient hardware architecture. Knowing the benefits of using memristive crossbar arrays in image processing applications, our work validates the multi-focus image fusion using a memristive crossbar array. In this work, a novel image fusion architecture is proposed using Pt/Cu:ZnO/Nb:STO memristor crossbar array to implement an iterative Kernel Principal Component Analysis (KPCA) algorithm. To test this algorithm, experiments were carried out using different multi-focus images as well as Infrared-Visible Images. A comparison between the software and hardware experiments results was drawn using different quantitative metrics like Structural Similarity, Entropy, and Correlation Coefficient. The proposed concepts in this thesis, including the impact of analog matrix multiplication and state transitions, alternative programming paradigms, and the construction of modern low-power and less complex memristive circuits, open up a new vista in the field of futuristic electronics and serve as an alternative potential to CMOS-based architectures.

## **Table of contents**

| CONTENTS                                             | Page No. |

|------------------------------------------------------|----------|

| Certificate                                          | ii       |

| Declaration                                          | iii      |

| Acknowledgments                                      | iv       |

| Abstract                                             | vi       |

| Table of contents                                    | ix       |

| List of Tables                                       | xiii     |

| List of Figures                                      | xiv      |

| List of Abbreviations                                | xviii    |

| Chapter 1                                            |          |

| 1 Introduction                                       | 1        |

| 1.1 Signal Processing                                | 2        |

| 1.1.1 Image Processing                               | 2        |

| 1.1.2 Text Classification                            | 5        |

| 1.1.3 Signal processing using Transistor-based       |          |

| Technology and its Disadvantages                     | 6        |

| 1.1.4 Disadvantages of Transistor-based Non-Volatile |          |

| Memory devices                                       | 7        |

| 1.2 Memristor                                        | 8        |

| 1.2.1 Characteristics of Memristor                   | 11       |

| 1.3 Literature Review                                | 16       |

| 1.4 Scope of the Present Investigation               | 19       |

| 1.5 Objectives of the Thesis                         | 20       |

| 1.6 Thesis Organization                              | 21       |

## Chapter 2

| 2. Memristors Enabled Computing Correlation Parameter In-Memory<br>Potential Alternative to Von Neumann Architecture | System: A<br>23 |

|----------------------------------------------------------------------------------------------------------------------|-----------------|

| 2.1 Introduction                                                                                                     | 23              |

| 2.2 Pearson Correlation Coefficient                                                                                  | 27              |

| 2.3 Implementation Section                                                                                           | 28              |

| 2.3.1 Memristor Modeling and Design Parameters                                                                       | 28              |

| 2.4 CoCoPIM Architecture                                                                                             | 30              |

| 2.4.1 Architecture                                                                                                   | 30              |

| 2.4.2 Data Encoding and Mapping                                                                                      | 42              |

| 2.4.3 Computation Steps                                                                                              | 44              |

| 2.5 Applications                                                                                                     | 46              |

| 2.5.1 Face Recognition                                                                                               | 46              |

| 2.5.2 ECG Signal Comparison                                                                                          | 49              |

| 2.5.3 H1N1 Model Comparison                                                                                          | 50              |

| 2.5.4 System-Level Variation Analysis                                                                                | 51              |

| 2.6 Results and Discussions                                                                                          | 52              |

| 2.6.1 System-Level Analysis                                                                                          | 52              |

| 2.7 Summary                                                                                                          | 55              |

## Chapter 3

| 3. Memristor-Bas<br>Classification | sed In-Memory        | Processor     | for   | High    | Precision  | Semantic | Text<br>56 |

|------------------------------------|----------------------|---------------|-------|---------|------------|----------|------------|

| 3.1 Introduc                       | tion                 |               |       |         |            |          | 56         |

| 3.2 Mathem                         | atical Analysis of ( | Classifier    |       |         |            |          | 57         |

| 3.3 Crossbar                       | Circuit for Sampl    | e Binary Dat  | aset  |         |            |          | 59         |

| 3.3.1                              | Prior Probability    |               |       |         |            |          | 60         |

| 3.3.2                              | Likelihood Proba     | bility and Ac | count | ing for | Words Abse | ent      |            |

|                                    | from the Training    | Dataset       |       |         |            |          | 60         |

| 3.4 Implementation Section                                                      | 61 |

|---------------------------------------------------------------------------------|----|

| 3.4.1 Circuit design                                                            | 61 |

| 3.5 Results and Discussions                                                     | 66 |

| 3.6 Summary                                                                     | 70 |

| Chapter 4                                                                       |    |

| 4. Realization of Memristive State Machine for Smart Edge Detector Applications | 72 |

| 4.1 Introduction                                                                | 72 |

| 4.2 Implementation Section                                                      | 74 |

| 4.2.1 Device structure and simulation setup                                     | 74 |

| 4.3 Results and Discussions | 76 |

|-----------------------------|----|

| 4.4 Summary                 | 90 |

## Chapter 5

| 5. Implementation of Binary Particle Swarm Optimization for Image Thresholding<br>Memristor Crossbar Array | <b>g using</b><br>92 |

|------------------------------------------------------------------------------------------------------------|----------------------|

| 5.1 Introduction                                                                                           | 92                   |

| 5.2 Objective Functions                                                                                    | 94                   |

| 5.2.1 Kapur's Entropy Function                                                                             | 95                   |

| 5.2.2 Otsu's Function                                                                                      | 96                   |

| 5.2.3 Binary Particle Swarm Optimization (BPSO)                                                            | 97                   |

| 5.3 Implementation Section                                                                                 | 99                   |

| 5.3.1 Implementation of BPSO using Memristor Crossbar                                                      | 99                   |

| 5.4 Results and Discussions                                                                                | 103                  |

| 5.4.1 Results and Explanation for Standard Images                                                          | 103                  |

| 5.4.2 Biomedical Image Processing using the Proposed Methodology                                           | 106                  |

| 5.5 Summary                                                                                                | 112                  |

| Chapter 6                                                                                                  |                      |

| 6. Memristor-based Image Fusion Architecture Using Iterative Kernel PCA                                    | 113                  |

| 6.1 Introduction                          | 113 |

|-------------------------------------------|-----|

| 6.1.1 Kernal Hebbian Algorithm            | 115 |

| 6.2 Implementation Section                | 118 |

| 6.2.1 Implementation of Memristor for KHA | 118 |

| 6.3 Results and Discussions               | 120 |

| 6.3.1 Performance Evaluation Metrics      | 121 |

| 6.4 Summary                               | 125 |

| Chapter 7                                 |     |

| 7. Conclusions and Future Scope           | 127 |

| 7.1 Conclusions                           | 127 |

| 7.2 Thesis Contributions                  | 129 |

| 7.3 Future Scopes                         | 130 |

| References                                | 131 |

| Appendix                                  | 147 |

| Publications                              | 189 |

| Biographies                               | 190 |

| S. No. |                                                                                                                                               | Page No. |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1      | Table 2.1: VTEAM values for Cu:Zno memristor                                                                                                  | 29       |

| 2      | Table 2.2: Von Neumann machine specifications                                                                                                 | 52       |

| 3      | Table 2.3: CoCoPIM area estimation                                                                                                            | 55       |

| 4      | Table 3.1: Sample dataset 1                                                                                                                   | 59       |

| 5      | Table 3.2: Sample dataset 2                                                                                                                   | 60       |

| 6      | Table 3.3: Likelihood probability for negative category                                                                                       | 63       |

| 7      | Table 3.4: Likelihood probability for positive category                                                                                       | 64       |

| 8      | Table 3.5: Result of testing the proposed circuit on standard datasets                                                                        | 69       |

| 9      | Table 4.1: Edge detected results for sample pixel inputs                                                                                      | 85       |

| 10     | Table 4.2: Percentage of edges detected in different algorithms                                                                               | 89       |

| 11     | <b>Table 5.1:</b> Parameters for BPSO and information about the crossbars used as suggested in the pseudo-code in section 5.2.3 and Eqn. (11) | 100      |

| 12     | Table 5.2: Results for the Lena Image                                                                                                         | 107      |

| 13     | <b>Table 5.3:</b> Results for Brain Images with Kapur's Entropy Function as the Objective Function                                            | 110      |

| 14     | Table 5.4: Results for Brain Images with Otsu's Function as the Objective Function                                                            | 111      |

| 15     | <b>Table 6.1:</b> Comparison between the results of software and hardware fusion of images using quantitative metrics                         | 123      |

## List of Figures

| S. No. |                                                                                                                                                                                                           | Page No. |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1      | <b>Fig. 1.1:</b> The four relations describing the essential two-terminal passive elements.                                                                                                               | 9        |

| 2      | <b>Fig. 1.2:</b> (a) Structure of a memristor, (b) Unipolar switching, and (c) Bipolar switching.                                                                                                         | 12       |

| 3      | <b>Fig. 1.3:</b> The crossbar array consists of perpendicular rows and columns with the memristor devices sandwiched at each cross point.                                                                 | 12       |

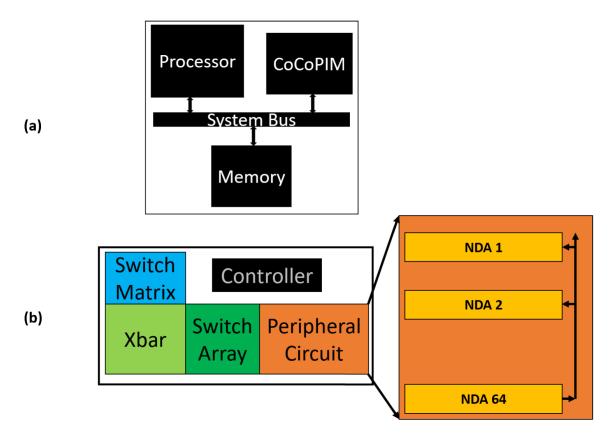

| 4      | <b>Fig. 2.1:</b> Performing matrix multiplication in the crossbar using DAC, S&H, and ADC.                                                                                                                | 29       |

| 5      | <b>Fig. 2.2</b> : (a) System on Chip Architecture and (b) CoCoPIM Architecture.                                                                                                                           | 31       |

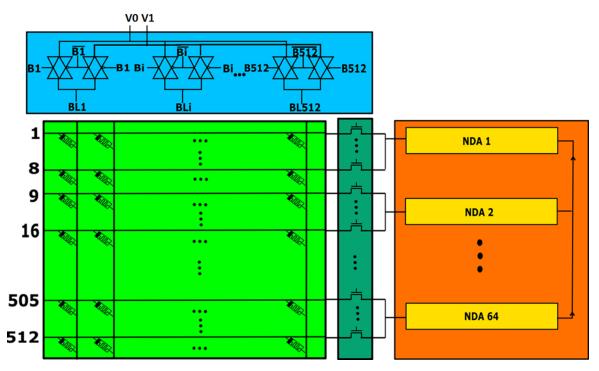

| 6      | Fig. 2.3: Proposed CoCoPIM microarchitecture.                                                                                                                                                             | 32       |

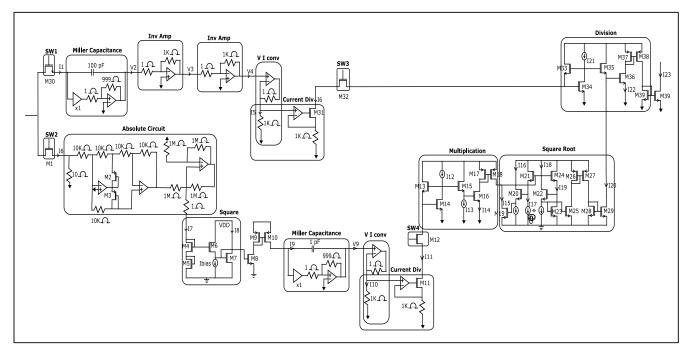

| 7      | <b>Fig. 2.4:</b> Circuits present within each of the 63 NDA blocks.                                                                                                                                       | 33       |

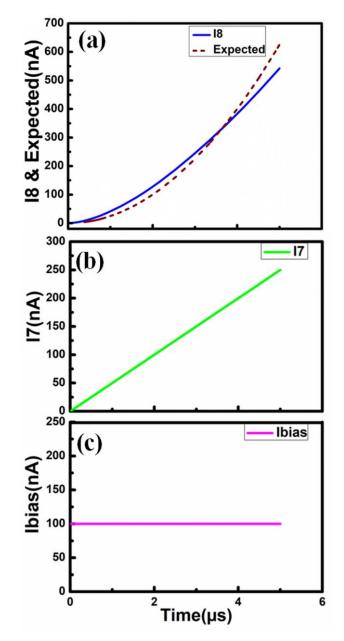

| 8      | <b>Fig. 2.5:</b> Characteristics of the square circuit. (a) The output and expected current, (b) the input, and (c) the bias current.                                                                     | 36       |

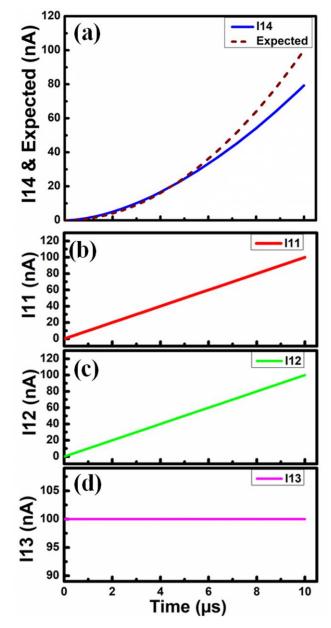

| 9      | <b>Fig. 2.6:</b> Characteristics of the multiplication circuit. (a) The output and expected current, (b) and (c) are the inputs, and (d) the bias current.                                                | 38       |

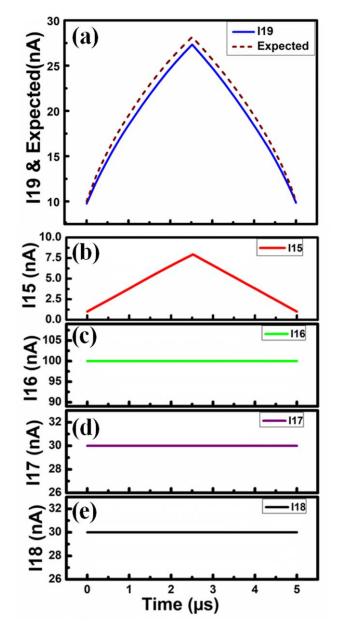

| 10     | <b>Fig. 2.7:</b> Characteristics of the square root circuit. (a) the output current I19 and the expected output current t of inputs (b) I15, (c) I16, (d) I17, and (e) I18.                               | 39       |

| 11     | <b>Fig. 2.8:</b> Characteristics of the DIV: (a) output current I22, and expected Output, (b) I20, (c) I6, and (d) I21.                                                                                   | 41       |

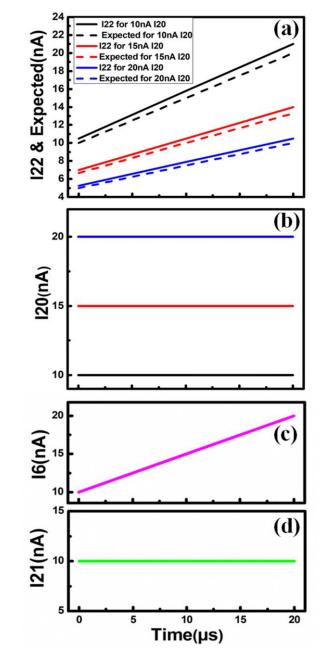

| 12     | <b>Fig. 2.9:</b> Circuits present within the NDA 64 block. It contains an absolute circuit, a square circuit, and Miller capacitance.                                                                     | 42       |

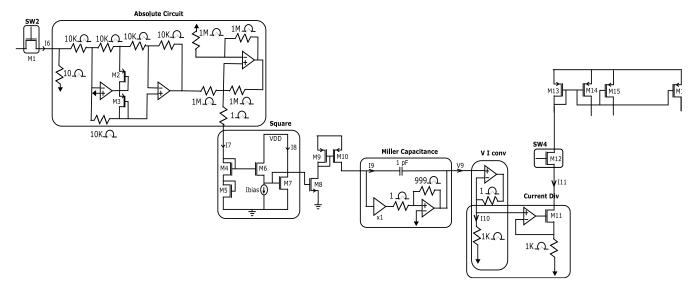

| 13     | <b>Fig. 2.10:</b> Data Mapping and Computation in CoCoPIM. (a) Numerator Computation, and (b) Denominator computation.                                                                                    | 45       |

| 14     | <b>Fig. 2.11:</b> Images of one of the 15 subjects from the Yale dataset.<br>(a) Normal image, (b) Image with Occlusion, and (c) Image with variant expression.                                           | 47       |

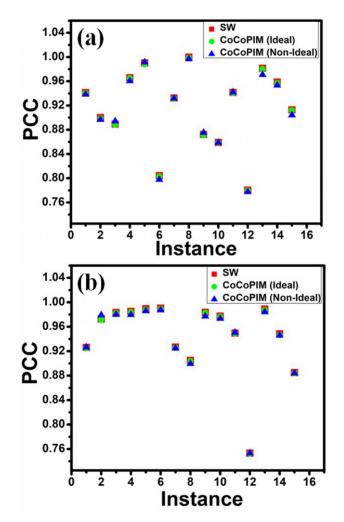

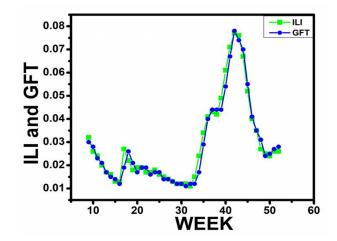

| 15     | <b>Fig. 2.12:</b> Recognition accuracy of the data obtained from Software, CoCoPIM, and CoCoPIM with variations in the (a) Occlusion task, and (b) Varying expression task.                               | 47       |

| 16     | <b>Fig. 2.13:</b> Comparisons of PCC computed using CoCoPIM (ideal), CoCoPIM (non-ideal) and the standard software (SW). PCC between a non-occluded non-varying expression image with 15 occluded images. | 48       |

| 17     | <b>Fig. 2.14:</b> Comparisons of PCC computed using CoCoPIM (ideal), CoCoPIM (non-ideal), and the standard software (SW) for the ECG dataset.                                                             | 50       |

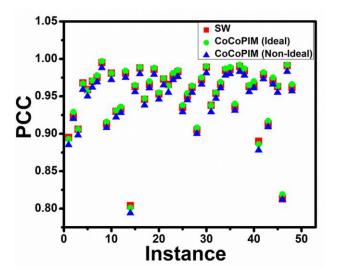

| 18     | Fig. 2.15: Estimations of GFT and ILI for 55 weeks.                                                                                                                                                       | 51       |

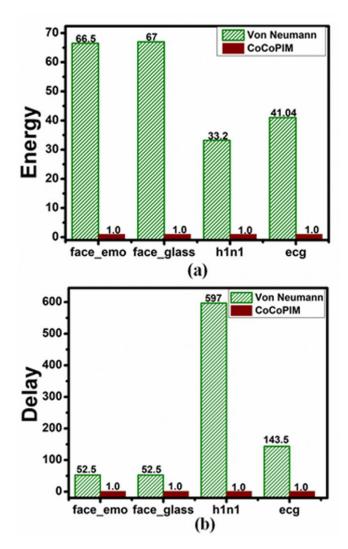

| 19     | <b>Fig. 2.16:</b> (a) Energy of von Neumann machine normalized to CoCoPIM, and (b) Delay of von Neumann machine normalized to CoCoPIM.                                                                    | 53       |

| 20  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <i>c</i> 1 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 20  | <b>Fig. 3.1:</b> Memristor crossbar network developed using dataset 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 61         |

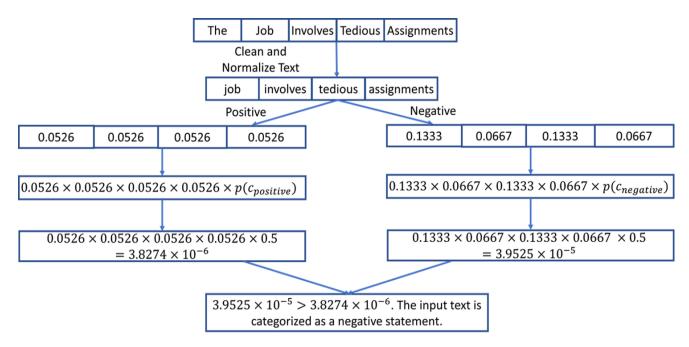

| 21  | <b>Fig. 3.2:</b> Flowchart summarizing various steps involved in Bayesian text classification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 65         |

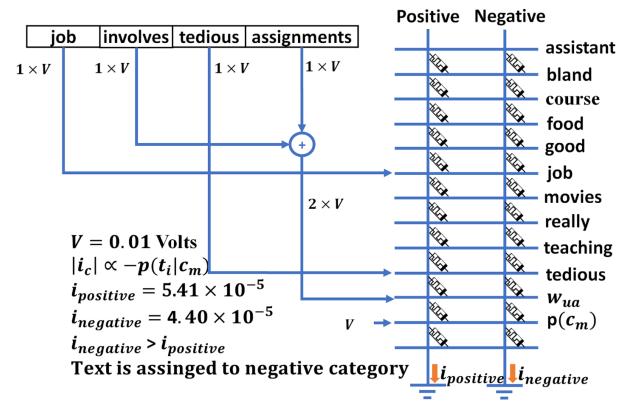

| 22  | Fig. 3.3: Memristive crossbar network for text classification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66         |

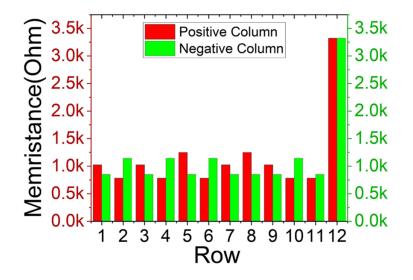

| 23  | <b>Fig. 3.4</b> Memristance <i>vs.</i> Row at the crossbar intersections.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 67         |

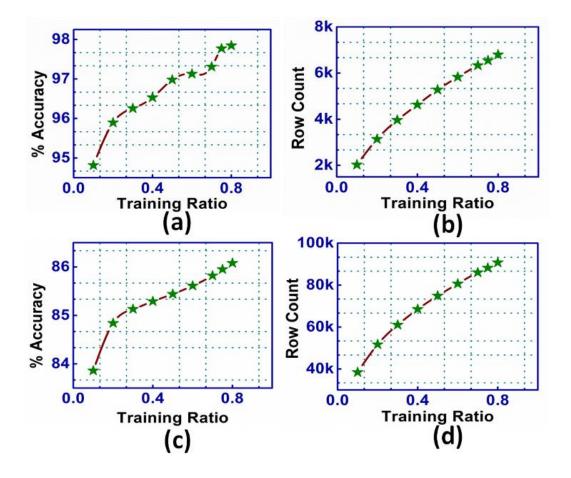

| 24  | <b>Fig. 3.5:</b> (a) Accuracy <i>vs.</i> Training ratio of classification for SMS dataset. (b) Row count <i>vs.</i> training ratio for SMS dataset. (c) Accuracy <i>vs.</i> training ratio of classification for IMDb dataset. (d) Row count <i>vs.</i> training ratio for IMDb dataset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 68         |

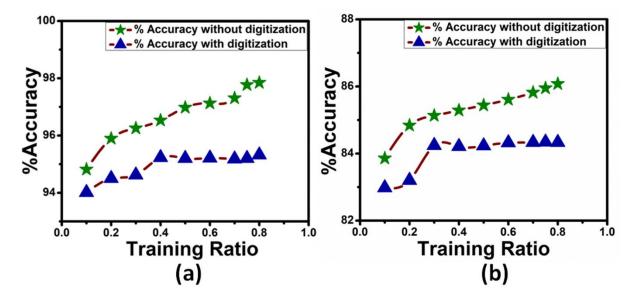

| 25  | <b>Fig. 3.6:</b> (a) Accuracy <i>vs.</i> Training ratio, classification accuracy without digitization and after digitization on SMS dataset. (b) Accuracy <i>vs.</i> Training ratio, classification accuracy without digitization and after digitization on IMDb dataset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69         |

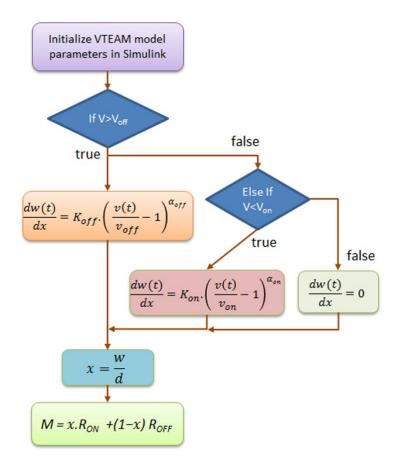

| 26  | <b>Fig. 4.1:</b> Flow chart for VTEAM model based memristor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 75         |

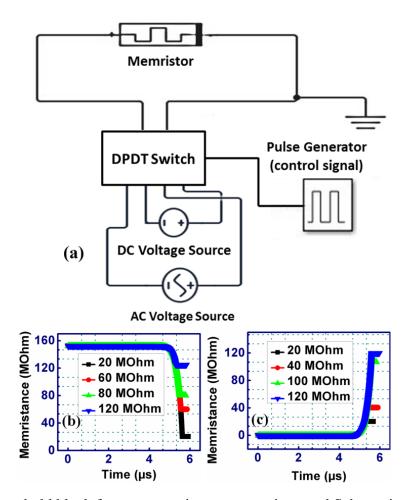

| 27  | <b>Fig. 4.2:</b> (a) Threshold block for programming one memristor and<br>Schematic of the proposed MSM circuit. The controlled<br>memristive state transitions were possible through the continuous<br>switching between the read and write cycles. (b) Decrementing<br>memristance characteristics of <i>Cu:ZnO</i> based memristor.<br>Different resistance values were written onto the memristor by<br>controlling the time duration for which the AC signal was<br>supplied. (c) Incrementing memristance characteristics. 20 M $\Omega$ ,<br>40 M $\Omega$ , 100 M $\Omega$ , and 120 M $\Omega$ were written onto the memristor<br>by utilizing the proposed switching technique. One can adjust the<br>switching time durations in order to write any required value<br>within the possible memristive states. | 77         |

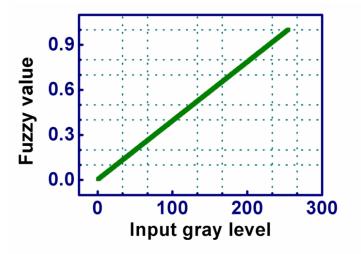

| 28  | <b>Fig. 4.3:</b> Mapping Luma values onto memristive multilevel logic states. The 0 to 255 grayscale levels were mapped to the corresponding memristive states from 0 to 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 78         |

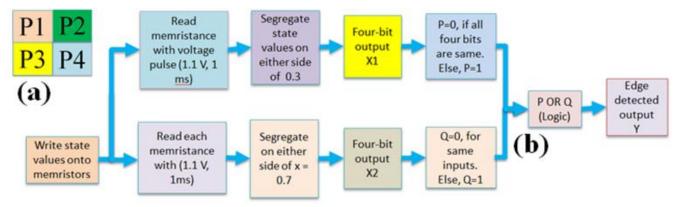

| 29  | <ul> <li>Fig. 4.4: (a) The essential 2×2-pixel array for computing edge detection. The edges were detected based on the differences in intensities between the four neighboring pixels. (b) Schematic of the computational flow through the threshold blocks. Edge detection was made possible by utilizing these logic computations.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82         |

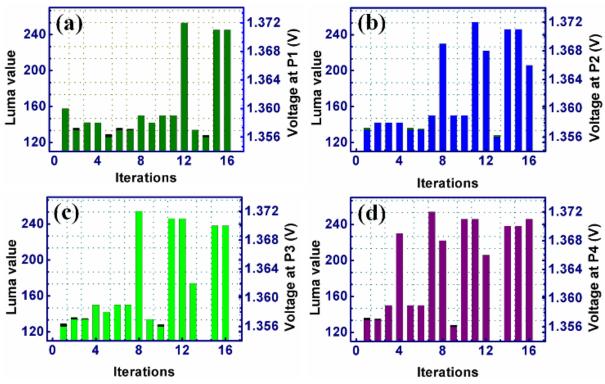

| b30 | <b>Fig. 4.5:</b> Variation of pixel grayscale intensity with the number of computational iterations for pixels P1-P4 shown in (a)-(d). Each iteration corresponds to a $2 \times 2$ submatrix in the sample $5 \times 5$ image, which traverses throughout the image.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 86         |

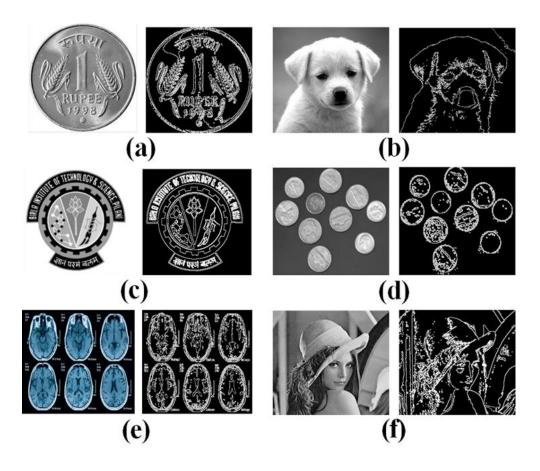

| 31  | <b>Fig. 4.6:</b> (a)-(f) Images indicating edge detection. The proposed algorithm was able to successfully detect the edges in given images.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87         |

| 32  | <b>Fig. 4.7:</b> Edge detection through utilizing (a) Canny's method, (b)<br>Sobel's method, (c) Prewitt's method (d) Log method, (e) Roberts<br>method, (f) Zerocross method and (g) our proposed method. It can<br>be seen that highest number of edges were detected by the<br>proposed method, when compared to the other cases.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88         |

| 33 | <b>Fig. 5.1:</b> (a) Memristor Crossbar Array (b) Calculating $c1r1.(x_{gb}^t - x_i^t)$ in crossbar (c) Calculating $c2r2.(x_{i,pb}^t - x_i^t)$ in crossbar.                                                                                                                                                                                                                                                         | 101 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 34 | <b>Fig. 5.2:</b> Flowchart summarizing the entire procedure.                                                                                                                                                                                                                                                                                                                                                         | 102 |

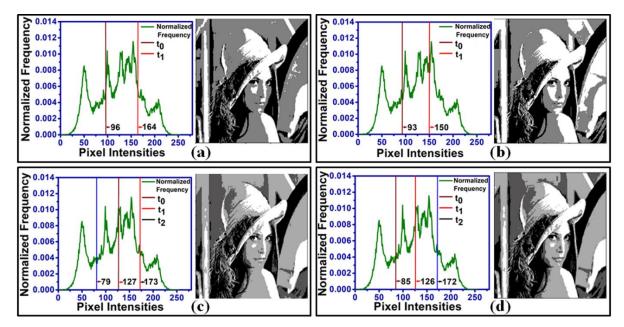

| 35 | <b>Fig. 5.3:</b> Brute Force Optimization. (a) Gray-scale Lena Image (b)<br>Histogram and Image for 2-thresholds while optimizing Kapur's<br>Entropy Function, (c) Histogram and Image for 2-thresholds<br>while optimizing Otsu's Function, (d) Histogram and Image for<br>3-thresholds while optimizing Kapur's Entropy Function, (e)<br>Histogram and Image for 3-thresholds while optimizing Otsu's<br>Function. | 104 |

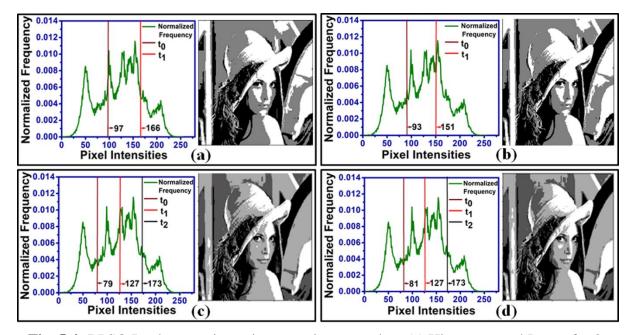

| 36 | <b>Fig. 5.4:</b> BPSO Implementation using memristor crossbar. (a) Histogram and Image for 2-thresholds while optimizing Kapur's Entropy Function, (b) Histogram and Image for 2-thresholds while optimizing Otsu's Function, (c) Histogram and Image for 3-thresholds while optimizing Kapur's Entropy Function, (d) Histogram and Image for 3-thresholds while optimizing Otsu's Function.                         | 105 |

| 37 | <b>Fig. 5.5:</b> BPSO crossbar implementation with device variations.<br>(a) Histogram and Image for 2-thresholds while optimizing Kapur's Entropy Function, (b) Histogram and Image for 2-thresholds while optimizing Otsu's Function, (c) Histogram and Image for 3-thresholds while optimizing Kapur's Entropy Function, (d) Histogram and Image for 3-thresholds while optimizing Otsu's Function.               | 106 |

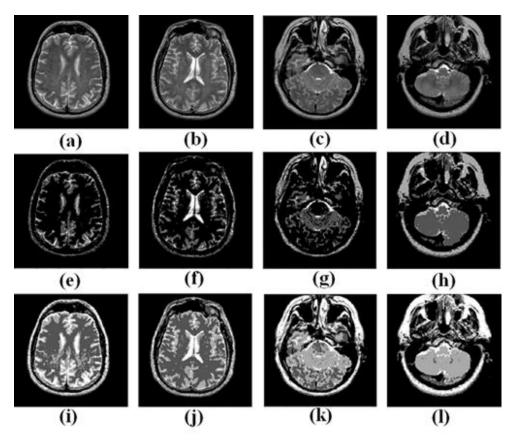

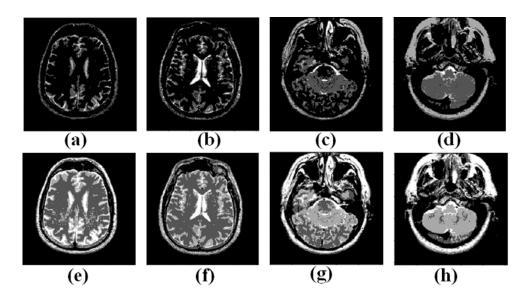

| 38 | <b>Fig. 5.6:</b> (a)-(d) Original Gray-scale Brain MR Images. (e)-(h) show the corresponding 4 gray-level thresholding by optimal values of the Kapur's Entropy Function for images (a)-(d). (i)-(l) show the corresponding 4 gray-level thresholding by optimal values of the Otsu's Function for images (a)-(d).                                                                                                   | 108 |

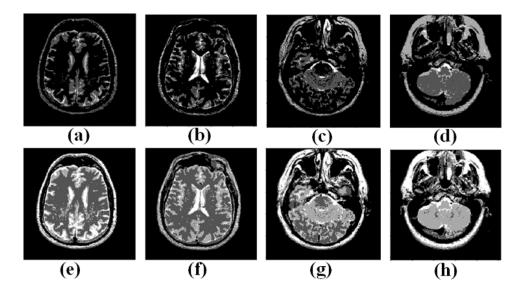

| 39 | <b>Fig. 5.7:</b> (a)-(d). show 4 gray-level thresholding by BPSO with Kapur's Entropy Function as the objective function. (e)-(h) show 4 gray-level thresholding by BPSO with Otsu's Function as the objective function                                                                                                                                                                                              | 108 |

| 40 | <b>Fig. 5.8:</b> (a)-(d). show 4 gray-level thresholding by BPSO with Kapur's Entropy Function as the objective function with 5% device variations. (e)-(h). show 4 gray-level thresholding by BPSO with Otsu's Function as the objective function with 5% device variations                                                                                                                                         | 109 |

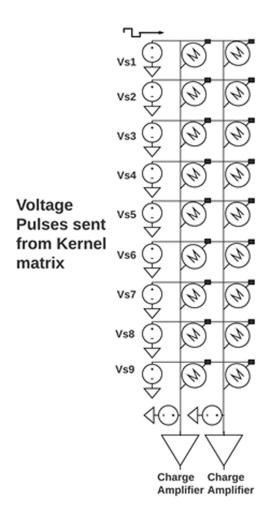

| 41 | <b>Fig. 6.1:</b> The schematic shows the Cu:ZnO Memristive Crossbar Array. The inputs are given through a voltage pulse proportional to a single column from the Kernel Matrix, and the output charge is collected using the charge Amplifier.                                                                                                                                                                       | 119 |

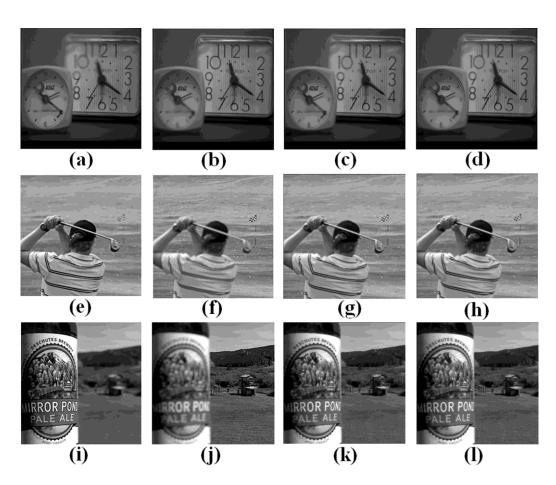

| 42 | <b>Fig. 6.2:</b> (a-l) Fusion of multi-focus images. From (L-R), the first two images are the input images, the third image is the fusion of software, and the fourth image is the result of the hardware fusion.                                                                                                                                                                                                    | 121 |

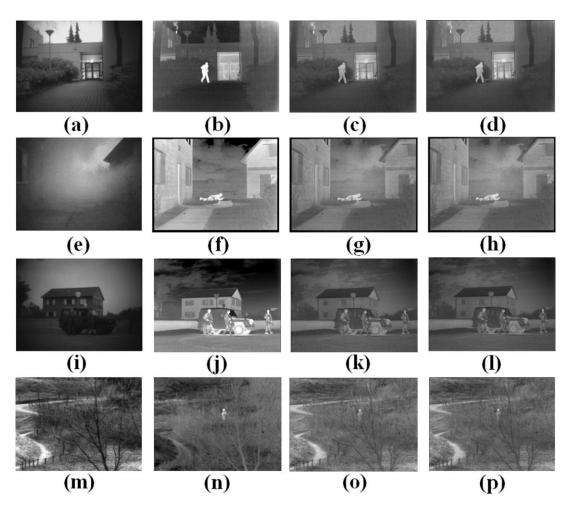

| 43 | <b>Fig. 6.3:</b> (a-p) The fusion of Visible and Infrared Images. From (L-R), the first two images are the input images, the third is the                                                                                                                                                                                                                                                                            | 124 |

|    | result of the software implementation, and the fourth is the result        |     |

|----|----------------------------------------------------------------------------|-----|

|    | of the hardware implementation.                                            |     |

| 44 | <b>Fig. 6.4:</b> (a) Correlation Coefficient (b) Structural Similarity (c) | 125 |

|    | Standard deviation, and (d)Entropy.                                        |     |

## List of Abbreviations

| AD      | Analog to Digital                         |

|---------|-------------------------------------------|

| ASA     | Analog Switch Array                       |

| ASIC    | Application Specific Integrated Circuit   |

| BL      | Bit Line                                  |

| BPSO    | Binary Particle Swarm Optimization        |

| CDC     | Centre for Disease Control                |

| CMOS    |                                           |

| CoCoPIM | Complementary Metal-Oxide-Semiconductor   |

| CPSO    | Computing Correlation Parameter In-Memory |

| CPSU    | Chaotic Particle Swarm Optimization       |

|         | Central Processing Unit                   |

| CSF     | Cerebrospinal Fluid                       |

| Cu:ZnO  | Copper doped Zinc Oxide                   |

| DA      | Digital – to – Analog                     |

| DAC     | Analog Converter                          |

| DCT     | Discrete Cosine Transform                 |

| DPDT    | Double Pole Double Throw                  |

| DRAM    | Dynamic Random Access Memory              |

| DSP     | Digital Signal Processing                 |

| DWT     | Discrete Wavelet Transform                |

| ECG     | Electrocardiogram                         |

| fMRI    | Functional Magnetic Resonance Imaging     |

| GBs     | Gigabytes                                 |

| GFT     | Google Flu Trends                         |

| GHA     | Generalized Hebbian Algorithm             |

| GPU     | General Processing Unit                   |

| HRS     | High Resistive State                      |

| ILI     | Influenza-like Illness                    |

| IMDb    | Internet Movie Database                   |

| IMPLY   | Implementation of Implication Logic       |

| IoT     | Internet of Things                        |

| ISAAC   | In-Situ Analog Arithmetic in Crossbars    |

| KHA     | Kernel Hebbian Algorithm                  |

| LERs    | Line Edge Roughnesses                     |

| LRS     | Low Resistive State                       |

| MARSS   | Micro Architectural and System Simulator  |

| MBs     | Megabytes                                 |

| McPAT   | Multicore Power, Area, and Timing         |

| MRI     | Magnetic Resonance Imaging                |

| MRIMA   | MRAM-Based In-Memory Accelerator          |

| MSE     | Mean Square Error                         |

| MSM     | Memristive State Machine                  |

| MSSIM   | Mean Structural Similarity Index Measure  |

| NLP     | Natural Language Processing               |

| NVM     | Non-Volatile Memory                       |

| OTFs    | Oxide Thickness Fluctuations              |

| PCA     | Principal Component Analysis              |

| PCC     | Pearson Correlation Coefficient           |

| PRIME   | Processing-In-Memory Architecture         |

|         |                                           |

| PSO     | Particle Swarm Optimization                |

|---------|--------------------------------------------|

| RAM     | Random Access Memory                       |

| RDDs    | Random Discrete Dopants                    |

| Re2PIM  | Reconfigurable ReRAM-Based PIM             |

| RKHS    | Reproducing Kernel Hilbert Space           |

| S&H     | Sample and Hold                            |

| SMS     | Short Message Service                      |

| SMS     | States of Memristor Switches               |

| SoC     | System on Chip                             |

| SRAM    | Static Random Access Memory                |

| Stt-CIM | Spin-Transfer Torque Compute In-Memory     |

| TL      | Translinear                                |

| TSMC    | Taiwan Semiconductor Manufacturing Company |

| TSV     | Through-silicon Via                        |

| VLSI    | Very-Large-Scale Integrated Circuitry      |

| VTEAM   | Voltage ThrEshold Adapted Memristor        |

| Vwrite  | Write Voltage                              |

| Vread   | Read Voltage                               |

| WL      | Word Line                                  |

## **Chapter 1**

## Introduction

The fact that massive amount of data have been continuously generated at unprecedented and ever-increasing scales is clear evidence that we live in a data deluge era. Numerous fields, including engineering sciences, social networks, business, biomolecular research, and security, collect and analyze large amount of data [1]. Notably, the amount of digital data produced by various digital gadgets is increasing at incredible rate. State-of-the-art computing systems suffer from the drawbacks of Von Neumann's architecture, which offers a limited rate of data transfer between the processing units and the memory. This bottleneck has significantly increased the energy consumption of these systems, especially in data-intensive computations. An intuitive solution to overcome the memory bottlenecks is to place the processor as close as possible to the primary memory [2]. However, such architectures, known as near-memory processors, have low data transfer latency and higher data bandwidths. The recent advancements in 3D silicon technologies have facilitated the fabrication of near-memory computers in which the processor is placed vertically on top of the memory using Through-Silicon Via (TSV) [3]. Despite its advantages, near-memory computing suffers from several drawbacks, such as difficulties in implementing virtual memory, cache coherency, data synchronization, memory management, etc. [2].

An alternative to near-memory computing is in-memory computing, where the computation happens within the memory unit [4]. In this architecture, there are no data movements and, as a result, do not suffer from the limitations of data latency and bandwidth. Memristor is proven to be an effective emerging device for in-memory processing, which is also a potential alternative to the CMOS technology. In concern to this, work further concentrates on the various applications of memristor cross bar array and its implementation in signal processing applications using machine learning algorithms.

### **1.1 Signal Processing**

Signal processing is an interdisciplinary field that involves systems engineering, electrical engineering, and applied mathematics. It deals with the analysis of analog and digitized signals that represent various physical quantities. A wide range of signals can be analyzed in signal processing, including analog and digital signals that reflect physical quantities. These signals can be diverse, such as sound, electromagnetic radiation, images and videos, electrical signals acquired by different sensors, or waveforms generated by biological, control, or telecommunication systems [5]. Digital Signal Processing (DSP) is a critical field that focuses on the analysis of digitized and discrete sampled signals. It has significant applications in various areas of science and engineering, such as communications, control, computers, and economics. The common signals that are most used in all of these areas are image and text [5, 6]. The advancements in the field of signal and image processing have inspired researchers to create and deploy diverse algorithms and mathematical tools in recent times [7].

With the growing usage of electronic devices in day-to-day life, the amount of data or signals collected and its characteristics are challenging the traditional approaches of signal processing technologies as they are massive, unreliable, unstructured, and barely fit the statistical assumptions about the underlying system. Thus, the idea of digital data computation has become challenging. This has led to an exponential increase in computation which necessitated the need for computational platforms in terms of design performance and efficiency [8].

### **1.1.1 Image Processing**

Our aspirations increased dramatically with the development of contemporary technology, which knows no limitations. The discipline of digital image processing is currently the subject

of extensive research. The rate of research has continuously increased exponentially [9]. Image processing, a field of signal processing and a technique that converts an input image into a digital platform and processes it in such a way as to enhance the image or to get some helpful information out of it. In today's modern world, it is a vast area of research with many different applications such as image morphology, neural networks, color image processing, medical image processing, image data compression, image recognition or face recognition, image fusion, edge detection, image thresholding pattern recognition, video processing, image enhancement or image sharpening, image segmentation, and so on [10], [11].

### **1.1.1.1 Face Recognition**

Face recognition is one of the most important and trending applications of image processing. Current generation needs automatic face detection since it is crucial to robotics and artificial intelligence [10]. The essential phase of computerized face analysis is face detection. The output of a face detection system can serve as an input for various other systems, including face recognition, face tracking, face authentication, facial expression recognition, and facial gesture recognition. These systems are essential components of applications such as personal identity and access control, videophone and teleconferencing, forensic investigations, humancomputer interaction, automated surveillance, cosmetology, and various other fields [12].

As the human face belongs to a dynamic object, many challenges like pose, occlusion, facial expression, existence or nonexistence of structural components, image orientation, and imaging conditions are prevalent in automatic face image analysis. Thus to overcome these challenges, algorithms with good accuracy and computational platforms with good efficiency are the need of the hour [12].

### 1.1.1.2 Edge Detection

Edge detection is a fundamentally important issue in picture analysis. Edge points can be

viewed as places on a pixel where the gray level changes suddenly [13]. A border between two areas with comparatively unique gray-level characteristics is referred to as an edge so that only gray-level discontinuities can be used to detect where two sections merge. Edges are prominently useful for image segmentation, registration, and identifying objects in images as they define object boundaries [14].

Besides, it has several other applications in the field of computer vision, medicine, artificial intelligence, and biometric-based identification systems, which have become an essential part of our day-to-day life. Many researchers are striving to find an efficient algorithm or computational architecture for edge detection systems [15].

### **1.1.1.3 Image Thresholding**

One of the essential initial stages of the image comprehension process, called image segmentation, tries to divide an image into areas so that each region groups adjacent pixels with comparable characteristics (intensity, color, etc.) [16]. It is crucial as the outcomes of all subsequent processes, including feature extraction, classification, and recognition, rely significantly on it. Numerous picture segmentation approaches have been documented in the literature as a result of extensive studies on the topic. These methods may generally be divided into four categories: thresholding, edge base, region growth, and clustering methods. The most fundamental technique is Image thresholding [17]. It is a straightforward and effective approach to distinguish objects from the background, as gray levels of pixels belonging to the object in most image processing applications differ significantly from those of pixels belonging to the background [18]. The thresholding operation involves dividing an image into segments that can be analyzed based on their shapes, sizes, relative positions, and other characteristics. This operation can be classified into two categories: global thresholding and local thresholding. Further, they are classified based on the gray levels, histogram, entropy, number of clusters, higher-order statistics, and local characteristics of the image [19], [20]. Known for their wide

applications and different methods, many algorithms are evolved in recent years, which also has led to the challenges of implementing such algorithms without compromising the efficiency and computational complexity is the need of the hour.

### 1.1.1.4 Image Fusion

The usage of pictures in different applications is increasing rapidly by the day. In recent years, there has been much interest in image fusion. Image fusion is the process of combining multiple images to improve the information content in a picture [21]. It is used for object detection and has importance in many fields like military, medical, automated industry, etc. Image fusion is most important in medical imaging- combining Computed Tomography (CT) scans and MRI imaging [22]. Different fusion techniques have been proposed, primarily in remote sensing and computer vision (such as night vision). At the same time, hardware implementations have also been made to address real-time processing in many application domains.

Multiple methods can be used to perform image fusion for a broad range of applications that involve high data transfer rates. Thus, in order to eliminate the need to transfer data from different memory sources, new device opportunities are being explored, including memristors for various logic implementations and memory operations [23].

### 1.1.2 Text Classification

In recent times, text classification issues have received extensive study and have been addressed in numerous practical applications. Many academics are currently interested in developing applications that make use of text classification techniques, particularly in the context of recent advances in Natural Language Processing (NLP) and text mining. It can classify new documents into pre-defined classes [24]. Currently, it is a sophisticated process involving not only training of models but also numerous additional procedures, for example pre-processing data transformation and dimensionality reduction. It is possible to break down vast majority of text classification and document categorization systems into four steps such as feature extraction, dimension reduction, classifier selection, and assessments. It continues to be a significant research area, with researchers exploring various techniques and their combinations in complex systems [25].

Thus, recent developments in various signal and image processing fields have inspired researchers to design and deploy different algorithms and mathematical tools. However, as the era of big data approaches, datasets are becoming increasingly large and complex, making it challenging to process them using traditional learning methods. Also, learning from conventional datasets were not designed to handle the high volume of data, and as a result, it may not work effectively with large and complex datasets [7]. As a result, artificial intelligence (AI) techniques have emerged as a solution. In the past decade, machine learning techniques have been widely adopted in several large and complex data-intensive fields such as medicine, astronomy, biology, and more. These techniques offer potential solutions for extracting valuable information from vast amounts of data [1].

The challenges witnessed by conventional computing architectures (Von Neumann architecture) used today for processing such algorithms with huge volumes of data are memory bottlenecks and high costs associated with constant data movements between the memory and the processor, creating the need for a system that significantly reduces the memory bottleneck and improves the efficiency of the system in terms of power consumption and speed [26].

### 1.1.3 Signal Processing using Transistor-based Technology and its Disadvantages

The majority of signal processing hardware systems currently available use multiplexing to consolidate multiple recording channels into one or several processing units to handle complex computational tasks [27]. These systems are typically built using silicon-based Complementary Metal-Oxide Semiconductor (CMOS) technology and employ the conventional von Neumann

architecture, where memory and data computing units are physically separated. Memory bottlenecks and high costs associated with data movements between the primary memory and the processor are the challenges witnessed by modern-day computers. Typically, these systems convert analog signals received into digital signals first and then compress and process them in the digital domain using various Application-Specific Integrated Circuits (ASICs) [28]-[31]. The implementation of machine learning algorithms and spiking neural networks in hardware has been an active research field, and recent publications have shown that it is feasible to apply these techniques to industrial applications, such as signal processing of complex data sets [32]-[34]. Recent advancements in nanotechnology have allowed for low power and high device integration, reigniting interest in the development of neural networks in hardware. This has led to the development of neuromorphic circuits that incorporate resistive nanoscale devices into crossbar topology with CMOS circuitry. BCrossnets is one such example that demonstrates the challenges and techniques involved in the design of neuromorphic circuitry using this approach [35], [36]. However, the design of such systems is still facing many challenges, such as power budget, delay, and scalability, mainly to catch up with the exponentially increasing number of data sets. Memristor, proposed by Chua in [37], is a promising element in this area as it may overcome the above mentioned inabilities. This inability is reduced by two factors: the small size of the memristors concerning their functionality and the ability to connect the memristors with crossbars [38].

### 1.1.4 Disadvantages of Transistor-based Non-Volatile Memory Devices

A Non-Volatile Memory (NVM) is a type of memory that can continue to store data in the computing system even when the power source is off [39]. Modern computing systems typically use transistor-based memory such as Static Random Access Memory (SRAM), Dynamic Random-Access Memory (DRAM), and Flash memory for data storage applications [40]. The major drawbacks of these transistor-based memories are, for instance, that SRAM is

expensive, non-volatile only while powered, and has a small storage size in terms of megabytes (MBs). Although DRAM is cost-effective and highly scalable, it consumes more power, is volatile, and has a moderate storage size in gigabytes (GBs). Flash memory or hard disk is non-volatile and has a storage capacity of more than 100 GB but has poor latency [40]. Most essentially, it is vital to note that further miniaturization of the transistors would lead to undesirable device performances, such as junction breakdowns and tunneling phenomena. It was predicted, by Gordon Moore (in 2015), that Moore's law would conclude within the next decade [41]. These primary limitations of the above-mentioned existing data storage technologies have created the need for the invention of a novel data storage and computing element that has the advantages of above mentioned current technologies, consumes less power and area, and has more latency. The necessity for this kind of device, having future scope for improvements in their data storage and computational capabilities, has led to the discovery of memristors [42].

#### 1.2 Memristor

A memristor is a short form of "memory & resistor". It is a nonlinear two-terminal passive electrical component that exhibits a unique property known as memristance. Memristance is the ability of the device to remember the history of the current that has flowed through it and to adjust its resistance accordingly. This makes the memristor a promising key element for next-generation memory and other applications, such as artificial neural networks and analog signal processing [43]. It has a smaller device dimensions of < 50% chip area per bit, compared to flash memory. It stores data in its resistance value that depends on the applied voltage's polarity, magnitude, and frequency, resulting in much simpler read and write cycles [42]. Analogous to transistors, they can be miniaturized in their device dimensions and are used in analog and digital electronic systems. Unlike transistors, memristors can store analog values in the form of device resistance [44], [45]. Memories based on memristors also have other

advantages, including very high packing density, zero power dissipation during data retention, and fewer components per computation, compared to their transistor counterparts [14].

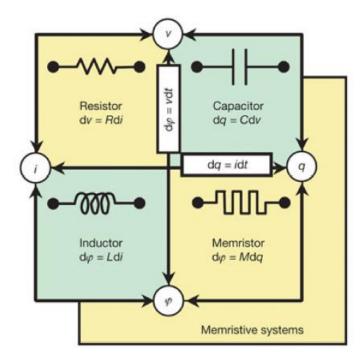

**Fig 1.1:** The four relations describing the essential two-terminal passive elements [40].

The memristor is the fourth fundamental circuit element, which was theoretically formulated by Chua [46]; the other three basic circuit elements are the resistor, capacitor, and inductor, which are as shown in Fig. 1.1. It is a two-terminal electronic circuit element that exhibits controllable resistive state transitions based on the amount of charge that has passed through it. Resistance of the memristor, known as memristance, is defined by Chua as the rate of flux ( $\phi$ ) versus charge (q) passing through it (i.e., M = d $\phi$ /dq) [47]. It is important to mention that there exists two types of memristors. If the *q* and  $\phi$  relation is such that *q* is the independent variable, then it is charge-controlled. i.e.,

$$\varphi = f(q) \tag{1.1}$$

Differentiating both sides of the above equation with respect to time t results in,

$$\frac{\mathrm{d}\varphi}{\mathrm{d}t} = \frac{\mathrm{d}f(q)}{\mathrm{d}q}\frac{\mathrm{d}q}{\mathrm{d}t} \tag{1.2}$$

The above equation can be written as:

$$v(t) = M(q)i(t) \tag{1.3}$$

where M(q) is memristance in  $\Omega$ .

$$M(q) = df(q)/dq \tag{1.4}$$

On the other side, if q and  $\varphi$  are related such that q is expressed in terms of  $\varphi$ , then it is a fluxcontrolled memristor [40]. Analogous to the previous case,

$$q = f(\varphi) \tag{1.5}$$

$$\frac{\mathrm{dq}}{\mathrm{dt}} = \frac{\mathrm{d}f(\varphi)}{\mathrm{d}\varphi}\frac{\mathrm{d}\varphi}{\mathrm{d}t} \tag{1.6}$$

$$i(t) = W(\varphi)v(t) \tag{1.7}$$

where  $W(\varphi)$  is the conductance of the memristor (or memductance), which has the units of *Siemen*.

$$W(\varphi) = \frac{df(\varphi)}{d\varphi}$$

(1.8)

It is important to note that q and  $\varphi$  are expressed mathematically as the time integral of i(t) and v(t), respectively, and need not have any physical interpretations [42]. Observe that Eqn. (1.3) and Eqn. (1.4) can be interpreted as Ohm's law except that the memristance M(q) at any time t = t0 depends on the entire history of i(t) from t =  $-\infty$  to t = t0. Similarly, the memductance W( $\varphi$ ) in Eqn. (1.8) depends on the entire history of v(t) from t =  $-\infty$  to t = t0. It results from Eqn. (1.3) that the charge-controlled memristor defined in Eqn. (1.1) is equivalent to the charge-dependent Ohm's law. Similarly, a flux-controlled memristor corresponds to the flux-

dependent Ohm's law [42]. In 2008 a solid-state memristor was developed and implemented by Hewlett-Packard (HP) Labs. It was proven that it is a novel nonlinear two-terminal nanoscale element with unique properties like memory capacity, a switching characteristic, and continuous input and output properties [48].

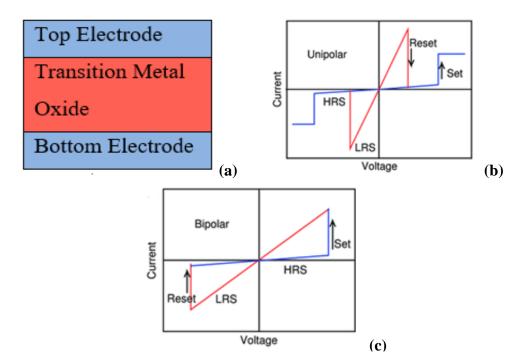

#### **1.2.1** Characteristics of Memristor

A memristor is a device that stores information on how much charge has passed through it, and in which direction. This information is encoded in its internal state variable; the resistance of the memristor increases if current passes in one direction and decreases otherwise. It is wellknown for its basic structure of two terminals and a non-volatile internal state variable resistance [40]. It consists of a transition metal oxide sandwiched between two electrodes, as shown in Fig. 1.2 (a) [49]. It has two resistive states; the Low Resistive State (LRS) of the memristor represents logic 1, whereas the High Resistive State (HRS) is read as logic 0. When the memductance is the least, the device is said to be in HRS, whereas the condition after electroforming is the LRS [40, 42]. The most significant feature of a memristor is the pinched hysteresis loop in its I-V characteristics. When a variable power source is applied to the memristor, the current through it is zero if the applied voltage is zero and vice-versa. When the voltage has gradually increased, the device, which is initially in the HRS , will change to LRS at the SET voltage. Further, if the voltage is slightly increased or decreased, the device will remain in its LRS. In order to RESET the device back to its HRS, one needs to reduce the voltage below the threshold value of the device.

There are two kinds of resistive switching mechanisms, namely, unipolar and bipolar, as shown in Fig 1.2 (b) and Fig. 1.2 (c), respectively [49]. In the case of unipolar switching, both *set* and *reset* mechanisms occur at the same polarity of voltage; whereas in bipolar switching, logic 1

and logic 0, are written onto the memristor by passing positive and negative currents, respectively [49].

Fig 1.2: (a) Structure of a memristor, (b) Unipolar switching, and (c) Bipolar switching [49].

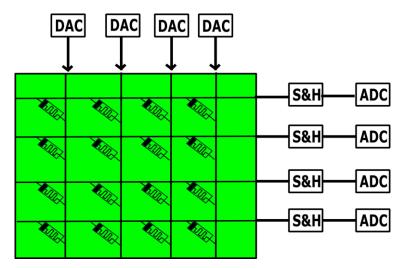

**Fig 1.3:** The crossbar array consists of perpendicular rows and columns with the memristor devices sandwiched at each cross point [14].

Memristive devices are customarily manufactured in a crossbar array architecture as shown in Fig. 1.3. Memristive crossbar array architecture facilitates dense memory of  $4F^2$  (F is the feature size) and is less expensive because of the simplicity of the cross bar array manufacturing

process [40]. The principal advantage of this crossbar array is the simplicity of its structure. This architecture is proven to be power efficient, has high-speed computation, and has a long retention time of up to ten years [40]. Thus, the memristor continues to show great potential in processing in-memory and computational applications.

In one of the recent studies, the fabrication of Pt/Cu:ZnO/Nb:STO based memristors has been demonstrated and obtained improved electrical performances such as low SET/RESET voltages, high ON/OFF ratio, good data retention, and stability, which are useful for various signal processing applications [50]. Moreover, the Cu:ZnO based memristor is a bipolar switching device, which has a stable switching attributed by retention up to  $10^6$  s, high endurance [50] and  $R_{on}/R_{off}$  ratio of ~ 2 X 10<sup>3</sup> which provides highly varied range for the state variable (ranging from 0 to 1). The fabricated Pt/Cu:ZnO/Nb:STO memristor was mimicked by utilizing The Voltage ThrEshold Adapted Memristor (VTEAM) model [51], and circuits were simulated using MATLAB Simulink. In the literature, other important models namely ion drift, Berkeley and Yakopcic's models were explored and many challenges were present to model fit the device [52]. In order to point out the important features, the ion drift model works more aptly on devices that has transition hysteresis for all voltages (eg: TiO<sub>2</sub> memristor). However, this model is not suitable for ferroelectric or zinc oxide memristors or for our case where the ion drift occurs only beyond certain threshold voltage. Similarly, the Berkeley model and Yakopcic's model have been prototyped based on the concept that the current variation takes place instantaneously irrespective of its previous state [53]. Unlike aforementioned models, the VTEAM model closely mimicked the fabricated device owing to the precisely controlled current variation based on applied voltage [54]. Thus as per the above mentioned reasons, in each work mentioned in this dissertation, Pt/Cu:ZnO/Nb:STO memristor is used and VTEAM model is chosed to behaviourally model the device. Details of the VTEAM modelling of memristor is as given below:

At any instant of time, a voltage-controlled memristor can be mathematically represented as:

$$\frac{dw}{dt} = f(w, v) \tag{1.9}$$

$$i(t) = G(w, v).v(t)$$

(1.10)

w is the internal state variable of the device. v(t) and i(t) are the voltage across the device and the current passing through the device, respectively. G is the conductance of the device. As per the VTEAM model, f (w,v) is:

$$\frac{dw}{dt} = \begin{cases} k_{off} \left(\frac{v(t)}{v_{off}} - 1\right)^{a_{off}} f_{off}(w), 0 < v_{off} < v \\ 0, v_{on} < v < v_{off} \\ k_{on} \left(\frac{v(t)}{v_{on}} - 1\right)^{a_{on}} f_{on}(w), v < v_{on} < 0 \end{cases}$$

(1.11)

Here,  $v_{on}$  and  $v_{off}$  are known as the on and off voltages, respectively. The parameters  $k_{off}$ ,  $k_{on}$ ,  $a_{off}$  and  $a_{on}$  are constants and these are device dependent.  $f_{off}$  and  $f_{on}$  are known as the window functions, and they are used to ensure that w is bounded such that  $w \in [w_{on}, w_{off}]$ . They are rectangular step-functions defined as follows:

$$f_{off} = \begin{cases} 1 \ if \ w < 1\\ 0 \ otherwise \end{cases}$$

(1.12)

$$f_{on} = \begin{cases} 1 \ if \ w > 0\\ 0 \ otherwise \end{cases}$$

(1.13)

For the model described in [53],

$$w = \frac{x}{D} \tag{1.14}$$

Where x is the length of the doped/polarized region and D is the active material thickness. The current-voltage relationship for the model is:

$$v(t) = i(t) * (R_{on} + (R_{off} - R_{on})(\frac{w - w_{on}}{w_{off} - w_{on}}))$$

(1.15)

As x can take values between 0 and D,  $w_{on}=0$  and  $w_{off}=1$ . Substituting this in the above equation, it can be deduced as:

$$v(t) = i(t) * (R_{on} + (R_{off} - R_{on})w)$$

(1.16)

The logic state of a memristor can be changed by applying sufficient voltage across it. To change state from 0 to 1, a negative voltage,  $v_{set}$ , with magnitude greater than  $v_{on}$  is applied across the memristor. Similarly, to change the logic state from 0 to 1 a positive voltage,  $v_{reset}$ , of magnitude greater than  $v_{off}$  is applied across the memristor. Apart from these binary states, the analogue nature of memristors permit multiple states in between the LRS and HRS.