### Design and Synthesis of Carbon Nanotube Field Effect Transistor (CNFET)-based Ternary Logic Circuits

### THESIS

Submitted in partial fulfillment

of the requirements for the degree of

### DOCTOR OF PHILOSOPHY

by

Chetan Kumar V

### ID No. 2009PH230006H

Under the Supervision of

Prof. M. B. Srinivas

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

#### 2018

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

#### CERTIFICATE

This is to certify that the thesis titled <u>Design and Synthesis of Carbon Nanotube Field</u> <u>Effect Transistor (CNFET)-based Ternary Logic Circuits</u> and submitted by <u>Chetan</u> <u>Kumar V</u> ID No <u>2009PH230006H</u> for award of PhD of the Institute embodies original work done by him under my supervision.

Signature of the Supervisor Name: Dr. M. B. SRINIVAS Designation: Professor Date:

## Acknowledgments

First and foremost, I would like to express my sincere gratitude to my supervisor Prof. M. B. Srinivas for his constant support, patience and valuable guidance through out my work.

I would also like to thank my Doctoral Advisory Committee members, Prof. BVVSN Prabhakar Rao, Dr. Surya Shankar Dan and Prof. Y Yoganandam for their time and their constructive comments and suggestions.

Next I would like to express my deep sense of gratitude to BITS Pilani, Hyderabad Campus for providing all the necessary facilities and support to complete the research work.

I am thankful to Sai Phaneendra P. for the help I received in developing the circuit simulation framework. I also appreciate the help from Goutham M, Avinash S Vaidya and Ganesh Kumar, during different stages of my work.

Furthermost, I would like to thank all members of Department of Electrical Engineering at BITS-Pilani, Hyderabad Campus, who have supported me by their suggestions and discussions.

Finally, I dedicate this work to my parents Pampana Gowda and Vishalakshi. Words can not express my gratitude to them for their constant support, inspiration and love. I deeply value the encouragement and support from my wife, Nydhili and my sister, Swetha.

Hyderabad

Chetan Kumar V

### Abstract

Multi-Valued Logic (MVL) circuits have attracted the attention in recent times because of the advantages they offer in reducing the interconnect complexity and increasing the information content per unit area. Ternary Logic is a special case of MVL that has three logic levels. Implementation of voltage mode ternary logic circuits requires transistors with different threshold voltages. Since traditional Metal-Oxide-Semiconductor (MOS) transistors use body biasing to change the threshold voltage, design of ternary logic circuits using MOS transistors becomes complex. On the otherhand, Carbon-Nanotube Field Effect Transistor (CNFET) are becoming popular in the implementation of ternary logic circuits. This is because Carbon-Nanotube (CNT) is used as a conduction channel in CNFET and variations of the diameter of CNT results in variation in threshold voltage of CNFET. This property of CNFET makes it suitable for implementation of MVL circuits in general and ternary logic circuits in particular.

In this thesis, we initially present three general design approaches to implement basic ternary logic circuits. The first design approach avoids the use of decoder and uses a novel low-power encoder resulting in ternary circuits that have low transistor count when compared to existing approaches. The second design approach uses a delay optimized decoder and low-power encoder leading to energy efficient ternary circuits. The third design approach uses 2:1 multiplexers to realize basic ternary logic circuits. This approach leads to ternary circuits which have low power consumption but large delay. Basic 2-input circuits are implemented and their design parameters are compared with that of existing approaches.

The second contribution of this thesis is two design techniques to implement multi-

digit adders. The first technique is a half-adder based ripple carry adder, in which outputs (instead of main inputs) are used for carry-out computation resulting in delayoptimized carry propagation path. The second design technique uses the concept of carry propagate-generate. In this thesis, a technique is presented, which enables the use of propagate-generate concept and aids in realizing ternary prefix adders. The proposed adder designs are compared with existing CNFET-based multi-digit ternary adders with respect to different design parameters.

The analysis of ternary adders shows that, the ternary encoder is a critical element and contributes significantly to the overall power consumption of the ternary circuit. In this thesis, new designs for CNFET-based ternary encoders, which are optimized for delay and power consumption, are presented. These designs are used to develop encoder based optimization algorithms which choose appropriate encoder for different outputs of a ternary logic circuit. The proposed algorithms are applied on an example ternary circuit to show their advantages in optimizing the design parameters of the circuit.

Apart from novel designs, this thesis also presents a synthesis technique to implement ternary logic circuits. Traditionally Binary Decision Diagram (BDD) and Ternary Decision Diagram (TDD) based algorithms have been used to synthesize binary and ternary logic functions respectively. This thesis presents a synthesis technique based on proposed Ternary-Transformed Binary Decision Diagram (TBDD), to implement ternary logic circuits using 2:1 multiplexers. This technique is used to synthesize a set of benchmark ternary functions and the resulting circuits are compared with circuits synthesized using existing techniques.

# Contents

| A        | Acknowledgements iii |                                                     |     |  |  |

|----------|----------------------|-----------------------------------------------------|-----|--|--|

| A        | bstra                | $\operatorname{ct}$                                 | iv  |  |  |

| C        | onter                | nts                                                 | vi  |  |  |

| Li       | st of                | Figures                                             | ix  |  |  |

| Li       | st of                | Tables                                              | xiv |  |  |

| Li       | st of                | Abbreviations                                       | xvi |  |  |

| 1        | Intr                 | oduction                                            | 1   |  |  |

|          | 1.1                  | Overview and Motivation                             | 1   |  |  |

|          | 1.2                  | Contributions                                       | 3   |  |  |

|          | 1.3                  | Thesis Outline                                      | 4   |  |  |

| <b>2</b> | Bac                  | kground and Related Work                            | 6   |  |  |

|          | 2.1                  | Ternary Logic                                       | 6   |  |  |

|          | 2.2                  | Carbon-Nanotube Field Effect Transistor (CNFET)     | 7   |  |  |

|          | 2.3                  | Ternary Logic Circuits using CNFETs                 | 11  |  |  |

|          | 2.4                  | Research Gaps, Objectives and Scope of Current Work | 15  |  |  |

| 3        | Des                  | ign Approaches for Basic Ternary Circuits           | 17  |  |  |

|          | 3.1                  | Introduction                                        | 17  |  |  |

|          | 3.2                  | Existing Design Approaches                          | 18  |  |  |

|   |     | 3.2.1  | Decoder   | -Encoder based approach                                | 18 |

|---|-----|--------|-----------|--------------------------------------------------------|----|

|   |     | 3.2.2  | Multiple  | exer based approach                                    | 20 |

|   | 3.3 | Novel  | Approach  | nes to Design Ternary Logic Circuits                   | 21 |

|   |     | 3.3.1  | Approac   | ch I: Using Low-power Encoder and without Decoder      | 21 |

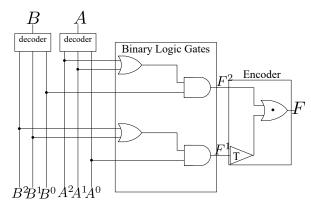

|   |     |        | 3.3.1.1   | Overview                                               | 21 |

|   |     |        | 3.3.1.2   | Steps Involved                                         | 23 |

|   |     |        | 3.3.1.3   | Function Simplification                                | 23 |

|   |     |        | 3.3.1.4   | Implementation of Unary Functions                      | 25 |

|   |     |        | 3.3.1.5   | Low-power Encoder                                      | 27 |

|   |     | 3.3.2  | Approac   | ch II: Using low-delay Decoder and low-power Encoder . | 30 |

|   |     |        | 3.3.2.1   | Low-Delay Decoder                                      | 32 |

|   |     |        | 3.3.2.2   | Alternate Representation of Logic Expressions          | 32 |

|   |     | 3.3.3  | Approac   | ch III: Using 2:1 Multiplexers                         | 35 |

|   |     |        | 3.3.3.1   | Basic Idea                                             | 35 |

|   |     |        | 3.3.3.2   | Ternary circuits using CNFET-based 2:1 Multiplexers    | 37 |

|   | 3.4 | Implei | mentation | and Simulation                                         | 39 |

|   |     | 3.4.1  | Simulati  | ion Environment                                        | 39 |

|   |     | 3.4.2  | Results   | and Discussion                                         | 42 |

|   |     |        | 3.4.2.1   | Impact of Process, Voltage and Temperature (PVT)       |    |

|   |     |        |           | Variations                                             | 47 |

|   |     |        | 3.4.2.2   | Noise Immunity Analysis                                | 49 |

|   | 3.5 | Conclu | usions .  |                                                        | 50 |

| 4 | Des | ign of | Multi-d   | igit Ternary Adders                                    | 52 |

|   | 4.1 | Introd | luction . |                                                        | 52 |

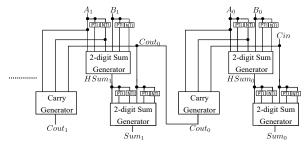

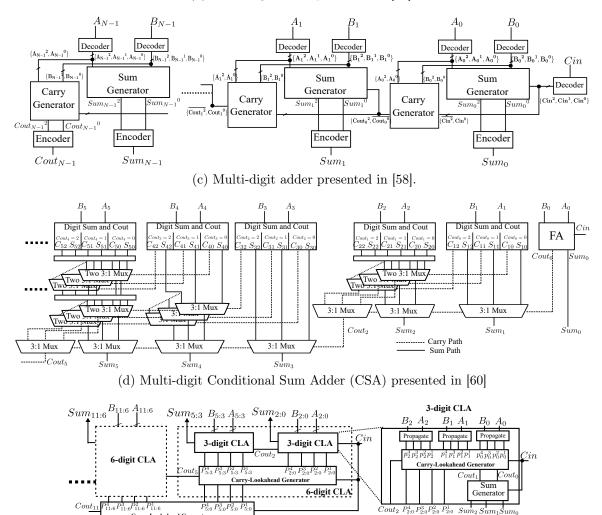

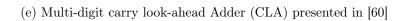

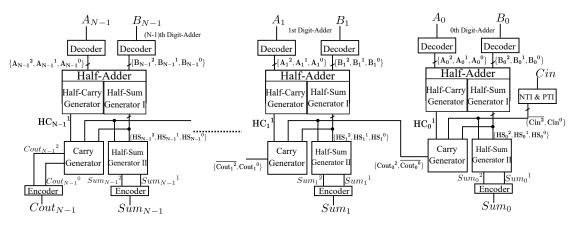

|   | 4.2 | Previo | ous Work  | on CNFET-based Ternary Adders                          | 53 |

|   |     | 4.2.1  | Single-D  | Digit Adders                                           | 53 |

|   |     | 4.2.2  | Multi-di  | git Adders                                             | 55 |

|   | 4.3 | Propo  | sed Half- | Adder Based Ripple-carry Ternary Adders                | 59 |

|   |     | 4.3.1  | Basic Id  | ea                                                     | 59 |

|     | 4.3.2                                                       | Impleme                                                                                                                                                                                   | ntation using CNFET                                   | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                             | 4.3.2.1                                                                                                                                                                                   | Designs for Decoder and Half-Adder                    | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

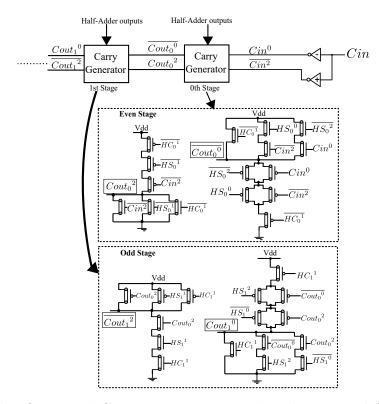

|     |                                                             | 4.3.2.2                                                                                                                                                                                   | Design of Carry Generator Block                       | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

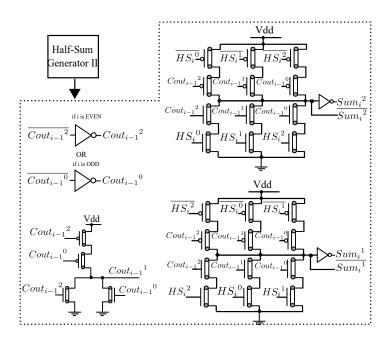

|     |                                                             | 4.3.2.3                                                                                                                                                                                   | Design of Final Half-Sum Generator                    | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

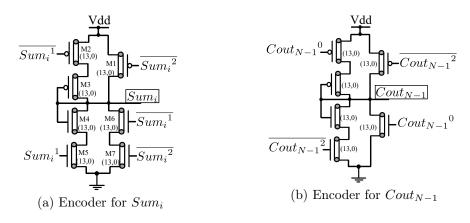

|     |                                                             | 4.3.2.4                                                                                                                                                                                   | Design of Low-Power Encoder                           | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.4 | Propos                                                      | sed Terna                                                                                                                                                                                 | ry Prefix Adder designs                               | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 4.4.1                                                       | Concept                                                                                                                                                                                   | of Carry Propagate-Generate in Binary Addition        | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

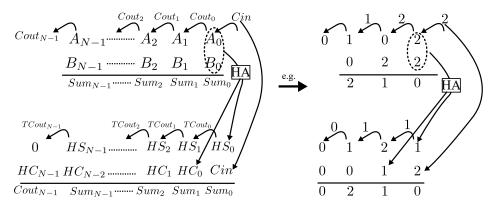

|     | 4.4.2                                                       | Basic Ide                                                                                                                                                                                 | ea for Ternary Prefix Adders                          | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 4.4.3                                                       | Proposed                                                                                                                                                                                  | d Implementation of Ternary Prefix Adders using CNFET | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                             | 4.4.3.1                                                                                                                                                                                   | Propagate and Generate for Ternary Adders             | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                             | 4.4.3.2                                                                                                                                                                                   | Carry Generation using Binary Prefix networks         | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

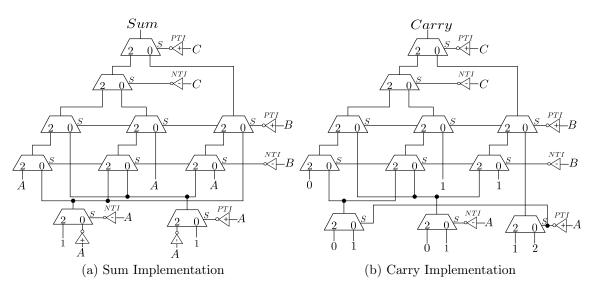

|     |                                                             | 4.4.3.3                                                                                                                                                                                   | Final Sum and Carry Computation                       | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.5 | Simula                                                      | ation Resu                                                                                                                                                                                | ılts                                                  | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 4.5.1                                                       | Results a                                                                                                                                                                                 | and Discussion                                        | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4.6 | Conclu                                                      | usions                                                                                                                                                                                    |                                                       | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Enc | oder-b                                                      | ased Op                                                                                                                                                                                   | timization of Ternary Circuits                        | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                             | -                                                                                                                                                                                         | ·                                                     | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                             |                                                                                                                                                                                           |                                                       | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                             |                                                                                                                                                                                           |                                                       | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | -                                                           |                                                                                                                                                                                           | v                                                     | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                             |                                                                                                                                                                                           |                                                       | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     | 0                                                           |                                                                                                                                                                                           |                                                       | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |                                                             |                                                                                                                                                                                           |                                                       | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                                                             |                                                                                                                                                                                           |                                                       | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |                                                             |                                                                                                                                                                                           |                                                       | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5.6 |                                                             | -                                                                                                                                                                                         |                                                       | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.0 | LAGIN                                                       | ole: Enco                                                                                                                                                                                 | der-Dased Optimization of Multi-Digit Termary Adder . | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     | 4.5<br>4.6<br><b>Enc</b><br>5.1<br>5.2<br>5.3<br>5.4<br>5.5 | 4.4       Propose $4.4.1$ $4.4.2$ $4.4.3$ $4.4.3$ $4.5.1$ $4.5.1$ $4.6$ Conclustion $5.1$ Introd $5.2$ Review $5.3$ Propose $5.4$ Effects $5.5.1$ $5.5.1$ $5.5.3$ $5.5.3$ $5.5.4$ $5.5.4$ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$ | 4.3.2.1       Designs for Decoder and Half-Adder         4.3.2.2       Design of Carry Generator Block         4.3.2.3       Design of Final Half-Sum Generator         4.3.2.4       Design of Low-Power Encoder         4.4       Proposed Ternary Prefix Adder designs         4.4       Proposed Ternary Prefix Adder designs         4.4.1       Concept of Carry Propagate-Generate in Binary Addition         4.4.2       Basic Idea for Ternary Prefix Adders         4.4.3       Proposed Implementation of Ternary Prefix Adders using CNFET         4.4.3       Propagate and Generate for Ternary Adders         4.4.3.1       Propagate and Generate for Ternary Adders         4.4.3.2       Carry Generation using Binary Prefix networks         4.4.3.3       Final Sum and Carry Computation         4.5       Simulation Results         4.5.1       Results and Discussion         4.6       Conclusions         5.1       Introduction         5.2       Review of Ternary Encoders         5.3       Proposed Ternary Encoders         5.4       Effects of varying chiralities of CNFETs that are used in Encoders         5.5.1       Problem Formulation         5.5.2       Power optimization         5.5.3       Delay Optimization      < |

| 6                          | $\mathbf{Syn}$ | thesis | of Ternary Logic Circuits using 2:1 Multiplexers              | 113   |

|----------------------------|----------------|--------|---------------------------------------------------------------|-------|

|                            | 6.1            | Introd | luction                                                       | 113   |

|                            | 6.2            | Prelin | ninaries                                                      | 114   |

|                            |                | 6.2.1  | Binary Decision Diagrams                                      | 114   |

|                            |                | 6.2.2  | Ternary Decision Diagrams                                     | 115   |

|                            | 6.3            | Propo  | sed Synthesis Methodology                                     | 116   |

|                            |                | 6.3.1  | General Ternary-Transformed Binary Decision Diagrams (TBDD    | ) 116 |

|                            |                | 6.3.2  | TBDD-based synthesis for 1-input ternary functions (Unary Op- |       |

|                            |                |        | erators)                                                      | 120   |

|                            |                | 6.3.3  | TBDD-based synthesis for 2-input ternary functions            | 125   |

|                            |                | 6.3.4  | TBDD-based synthesis for $n$ -input ternary functions         | 129   |

|                            | 6.4            | Algori | thm for 2:1 Multiplexer based Synthesis                       | 130   |

| 6.5 Synthesis using CNFETs |                |        | 133                                                           |       |

| 6.6 Results                |                | S      | 136                                                           |       |

|                            |                | 6.6.1  | Synthesis                                                     | 136   |

|                            |                | 6.6.2  | SPICE Simulation                                              | 138   |

|                            | 6.7            | Conclu | usions                                                        | 141   |

| _                          | G              |        |                                                               | 1 40  |

| 7                          | Sun            | nmary  | and Future Work                                               | 143   |

|                            | 7.1            | Summ   | ary                                                           | 143   |

|                            | 7.2            | Future | e Work                                                        | 145   |

# List of Figures

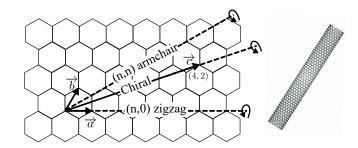

| 2.1  | Unrolled sheet of graphite and the rolled lattice structure of CNT [42]              | 8  |

|------|--------------------------------------------------------------------------------------|----|

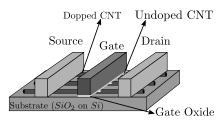

| 2.2  | 3D view of Carbon-Nanotube Field Effect Transistor (CNFET) $~$                       | 8  |

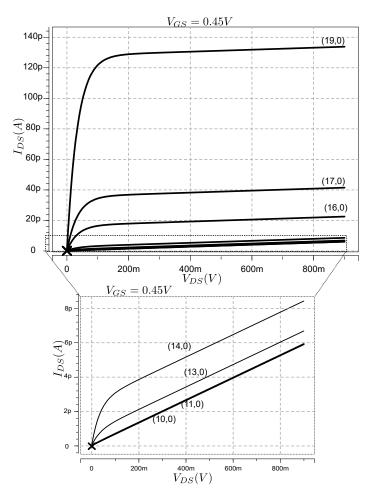

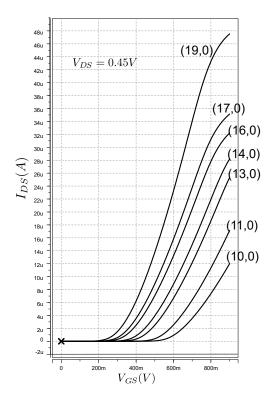

| 2.3  | I-V Characteristics of N-CNFET                                                       | 12 |

| 2.4  | I-V Characteristics of N-CNFET                                                       | 12 |

| 3.1  | Realization of a ternary function using existing decoder-encoder based               |    |

|      | approach                                                                             | 19 |

| 3.2  | Implementation of function shown in Table 3.1 using 3:1 Mux based                    |    |

|      | approach [60]                                                                        | 20 |

| 3.3  | Transistor level Implementation of 3:1 Multiplexer [60] $\ldots \ldots \ldots$       | 21 |

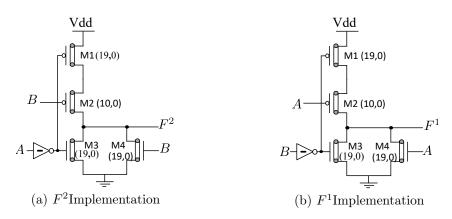

| 3.4  | Implementation of $F^2$ and $F^1$ in proposed approach $\ldots \ldots \ldots \ldots$ | 22 |

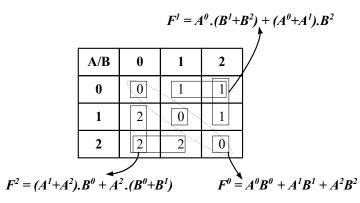

| 3.5  | K-Map simplification for function $F$                                                | 24 |

| 3.6  | Transistor level realization of $X^0$ , $X^1$ and $X^2$ unary terms $\ldots \ldots$  | 26 |

| 3.7  | Transistor level realization of $X^0 + X^1$ , $X^1 + X^2$ and $X^0 + X^2$ unary      |    |

|      | terms                                                                                | 27 |

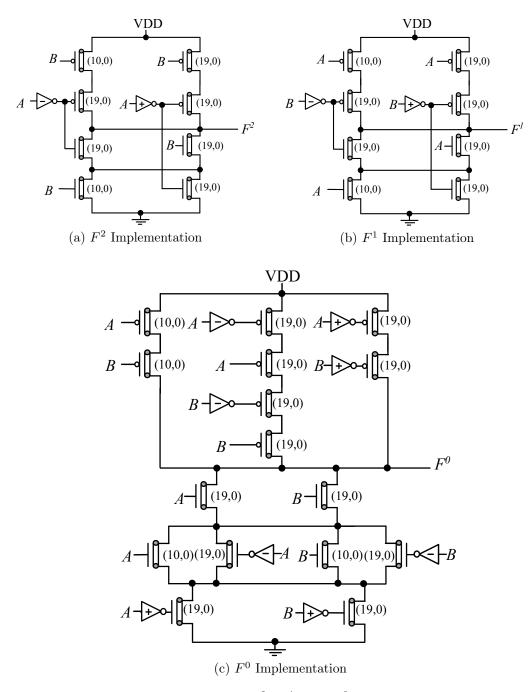

| 3.8  | Implementation of $F^2$ , $F^1$ and $F^0$ using proposed approach $\ldots \ldots$    | 28 |

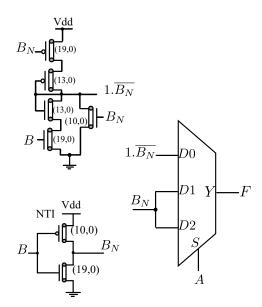

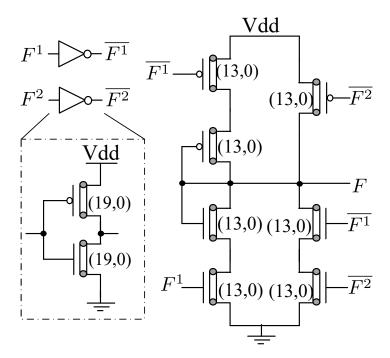

| 3.9  | Encoder with $F^2$ and $F^1$ as inputs $((F^2, F^1)$ -Encoder)                       | 29 |

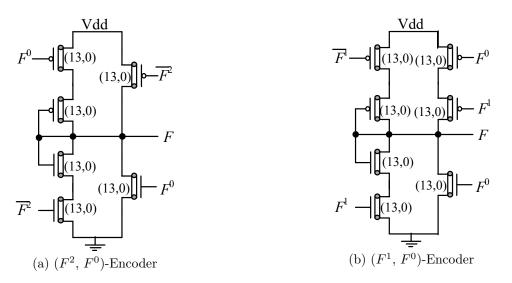

| 3.10 | Encoder design for $(F^2, F^0)$ and $(F^1, F^0)$ combination                         | 30 |

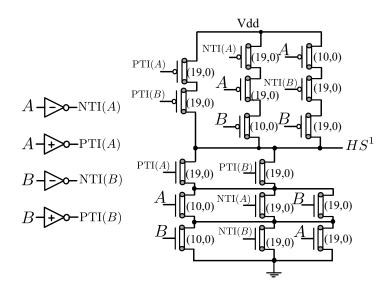

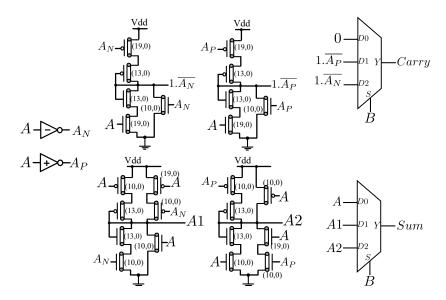

| 3.11 | Implementation of Half-Sum using Decoderless approach                                | 31 |

| 3.12 | Implementation of Half-Sum using Existing Decoder-encoder based ap-                  |    |

|      | proach (all CNFETs have chirality as $(19,0)$ )                                      | 31 |

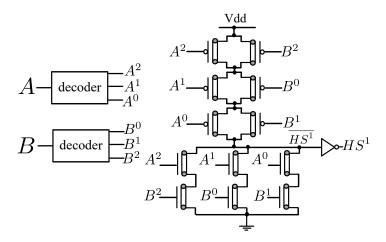

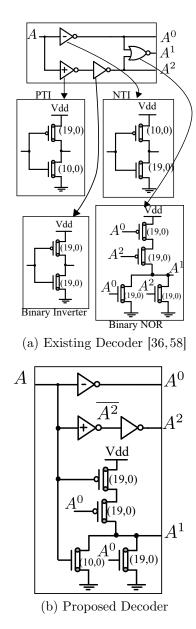

| 3.13 | Decoder Implementations                                                              | 33 |

| 3.14 | Implementation of Half-Sum with reduced Transistor Stacking (all CN- $$   |    |

|------|---------------------------------------------------------------------------|----|

|      | FETs have chirality as $(19,0)$ )                                         | 35 |

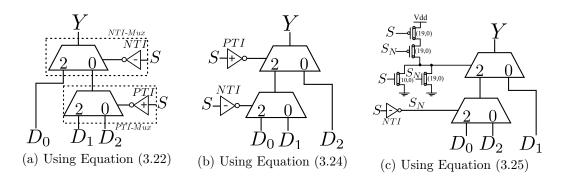

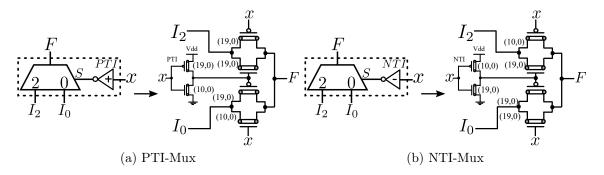

| 3.15 | A 3:1 Multiplexer operation using 2:1 Multiplexers                        | 37 |

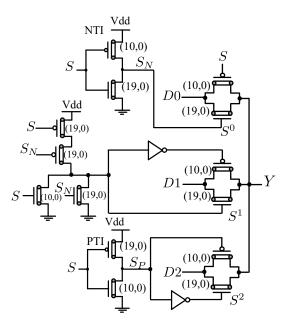

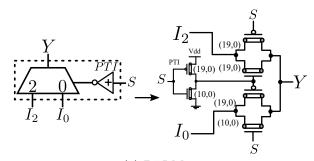

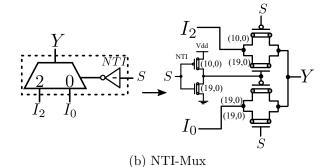

| 3.16 | CNFET-based Implementation of NTI-Mux and PTI-Mux                         | 37 |

| 3.17 | 2:1 Multiplexer based Implementation for Ternary Function in Table        |    |

|      | 3.4                                                                       | 38 |

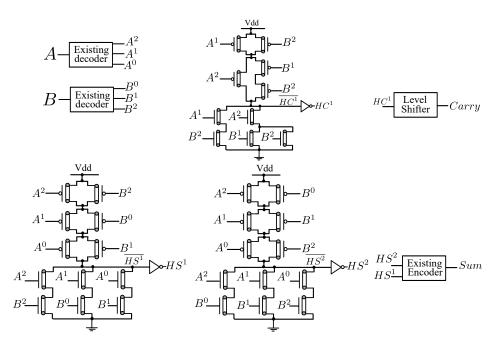

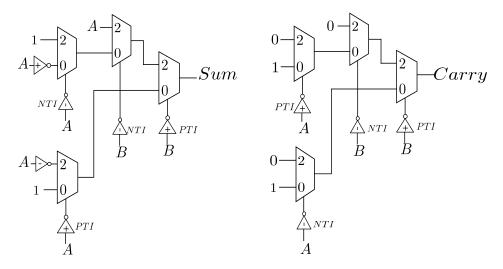

| 3.18 | Half-Adder using Existing Decoder-Encoder based Approach (all CN-         |    |

|      | FETs have chirality as $(19,0)$ )                                         | 40 |

| 3.19 | Half-Adder using Existing 3:1 Multiplexer based Approach                  | 40 |

| 3.20 | Half-Adder using Proposed Decoderless Approach (I) $\ldots \ldots \ldots$ | 41 |

| 3.21 | Half-Adder using Proposed Decoder-Encoder based Approach (II) (all        |    |

|      | CNFETs have chirality as $(19,0)$ )                                       | 41 |

| 3.22 | Half-Adder using Proposed 2:1 Multiplexer based Approach (III)            | 42 |

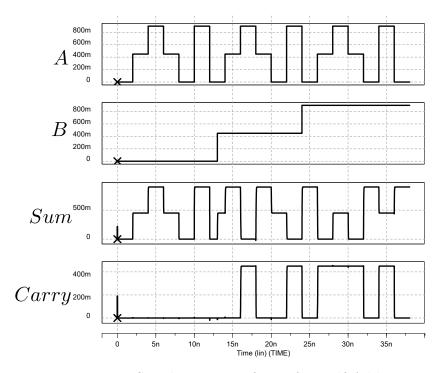

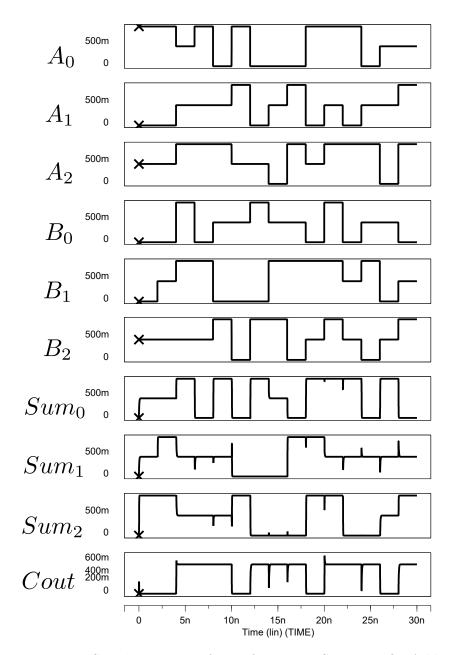

| 3.23 | Simulation Waveforms for Half-Adder                                       | 43 |

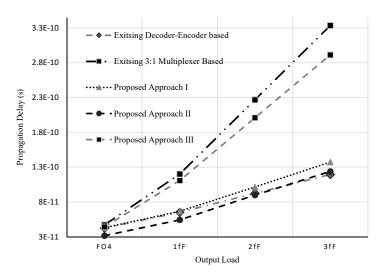

| 3.24 | Propagation Delay Vs Output Load for Half-adder                           | 46 |

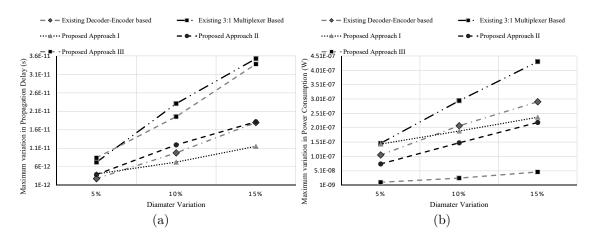

| 3.25 | Monte-Carlo Simulations for (a) Delay (b) Power                           | 48 |

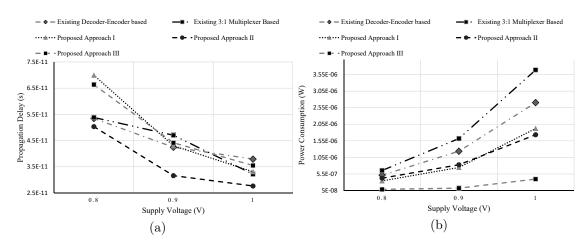

| 3.26 | (a) Delay (b) Power for Supply Voltage Variation                          | 48 |

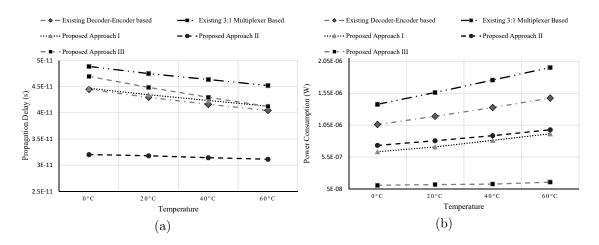

| 3.27 | (a) Delay (b) Power for Temperature Variation                             | 49 |

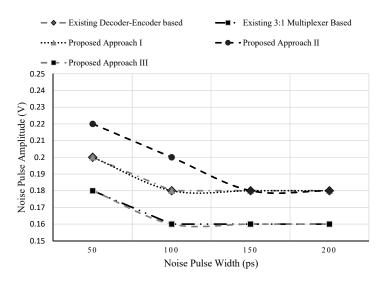

| 3.28 | Noise Immunity Curve for Half-Adders                                      | 50 |

| 4.1  | Design techniques used to implement Multi-digit adders                    | 54 |

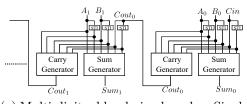

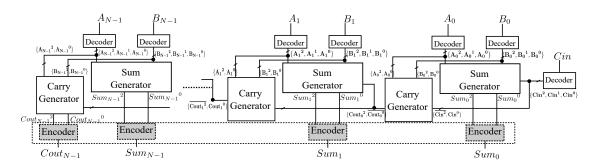

| 4.2  | Proposed design technique to implement Multi-digit adders                 | 58 |

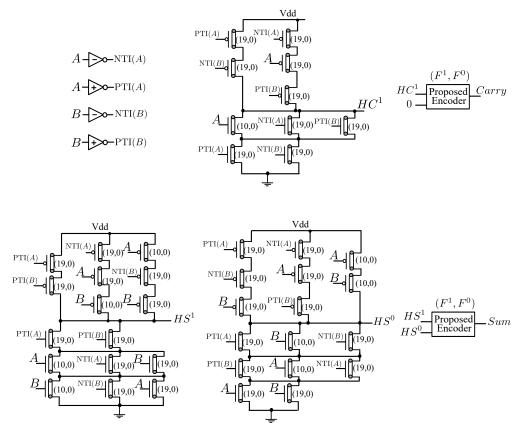

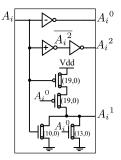

| 4.3  | Decoder Implementation                                                    | 61 |

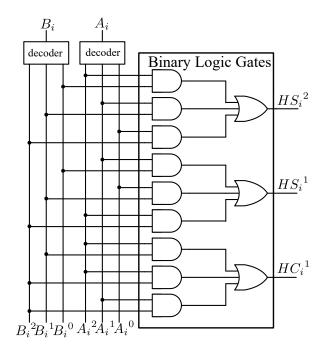

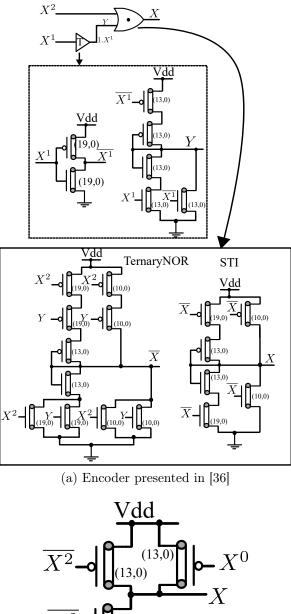

| 4.4  | Gate-level Implementation to generate Half-Adder outputs [36]             | 62 |

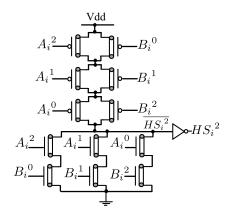

| 4.5  | Transistor-level Implementation for $HS_i^2$                              | 62 |

| 4.6  | Proposed Transistor-Level Implementation of Half-carry Generator and      |    |

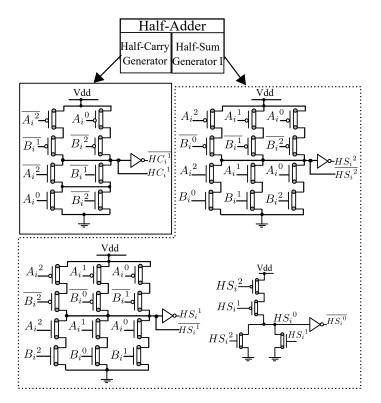

|      | half-sum Generator I (all transistors with chirality of $(19,0)$ )        | 63 |

| 4.7  | Delay-Optimized Carry Propagation Path with Proposed Carry Gen-           |    |

|      | erator Blocks (all transistors with chirality of $(19,0)$ )               | 65 |

| 4.8  | Transistor-level implementation of Half-sum generator II (all transis- |     |

|------|------------------------------------------------------------------------|-----|

|      | tors with chirality of $(19,0)$ )                                      | 66  |

| 4.9  | Designs for Encoder                                                    | 67  |

| 4.10 | Table showing Carry Propagate and Generate conditions for Binary       |     |

|      | addition                                                               | 68  |

| 4.11 | Example of ternary addition using proposed transformation              | 69  |

| 4.12 | Table showing Carry Propagate and Generate conditions for ternary      |     |

|      | addition                                                               | 70  |

| 4.13 | Table showing Carry Propagate and Generate conditions after pro-       |     |

|      | posed transformation                                                   | 71  |

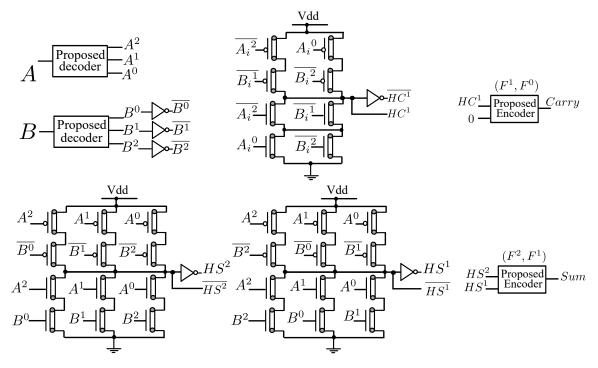

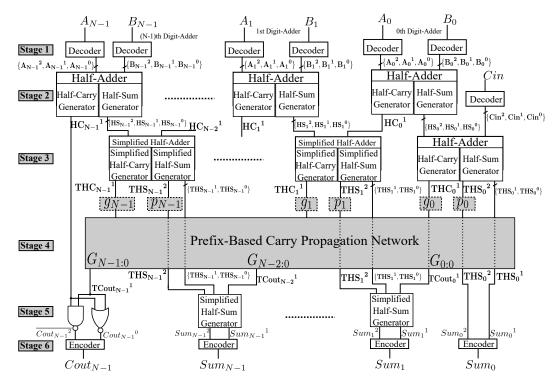

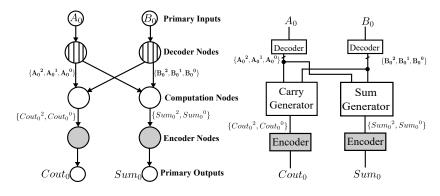

| 4.14 | Block-level Implementation of Proposed Ternary Adders                  | 72  |

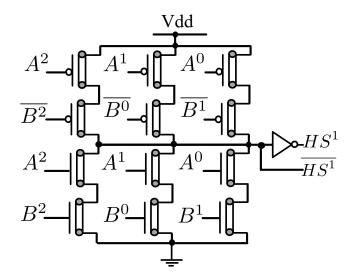

| 4.15 | CNFET-based Implementation of Simplified Half-Adder (all CNFETs        |     |

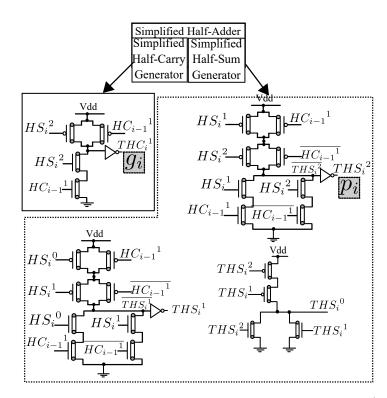

|      | have chirality of $(19,0)$ )                                           | 74  |

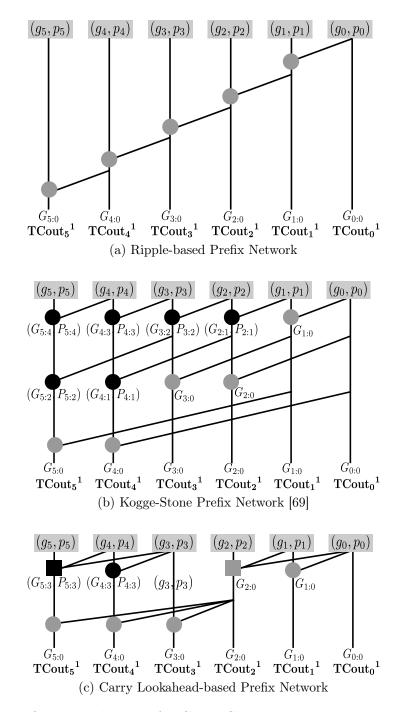

| 4.16 | Prefix Networks used for Carry Computation in 6-digit Ternary Adder    | 76  |

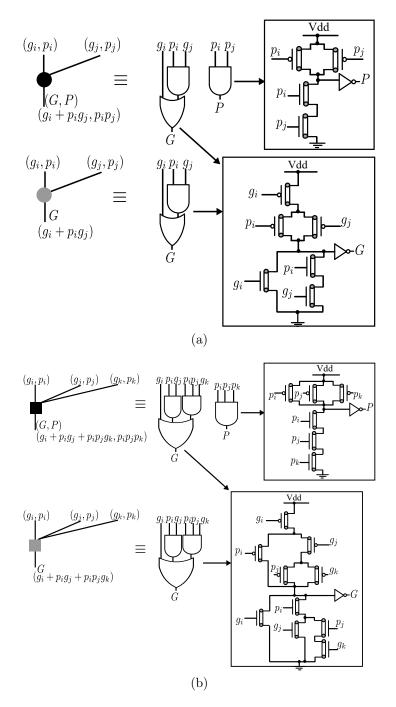

| 4.17 | CNFET-based Implementation of Cells used in Prefix Networks (all       |     |

|      | CNFETs have chirality of $(19, 0)$ )                                   | 77  |

| 4.18 | Simulation Waveforms for Kogge-Stone Prefix Adder                      | 80  |

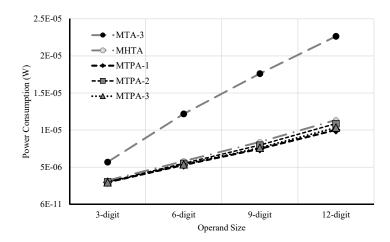

| 4.19 | A Comparison of Power consumption                                      | 81  |

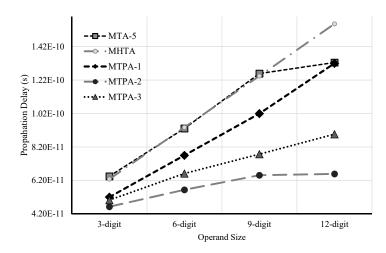

| 4.20 | A Comparison of Propagation Delay for FO4 load                         | 82  |

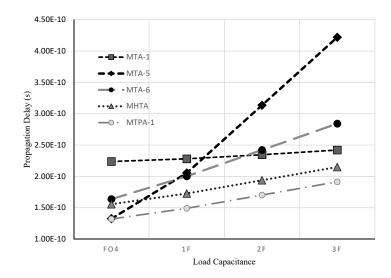

| 4.21 | Propagation delay vs load for 12-digit adder                           | 84  |

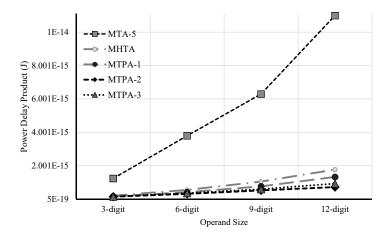

| 4.22 | A Comparison of PDP                                                    | 85  |

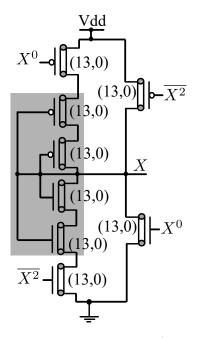

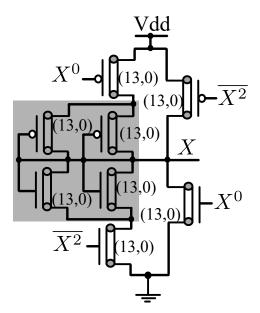

| 5.1  | Ternary Encoders                                                       | 90  |

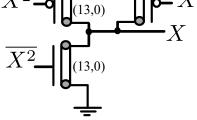

| 5.2  | Proposed Encoder (with inputs $\overline{X^2}$ and $X^0$ )             | 92  |

| 5.3  | Proposed Low-Power Encoder (with inputs $X^2$ and $X^0$ )              | 93  |

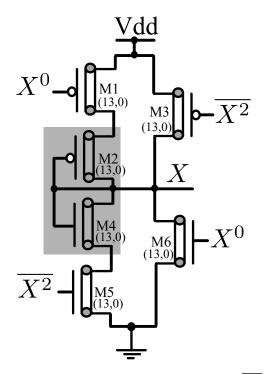

| 5.4  | Proposed Low-Delay Encoder (with inputs $X^2$ and $X^0$ )              | 93  |

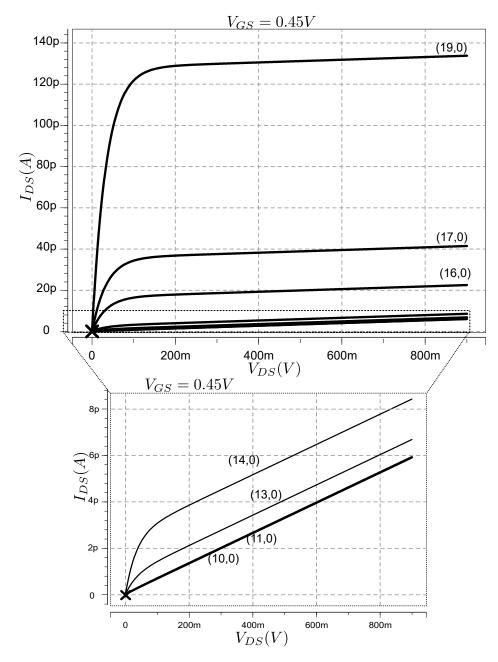

| 5.5  | I-V Characteristics of N-CNFET                                         | 96  |

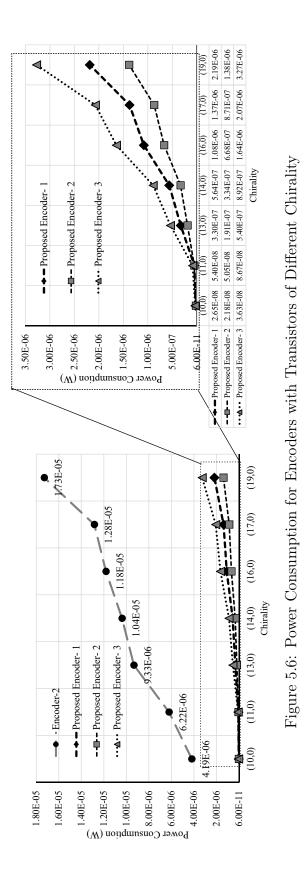

| 5.6  | Power Consumption for Encoders with Transistors of Different Chirality | 97  |

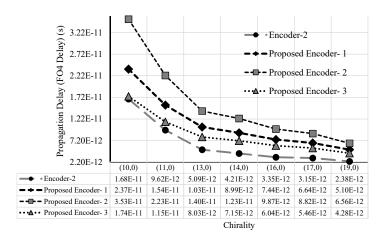

| 5.7  | Propagation Delay for Encoders with Transistors of Different Chirality | 98  |

| 5.8  | Ternary Circuit as a Graph                                             | 100 |

| 5.9  | Multi-digit adder presented in [58]                                 | 107 |

|------|---------------------------------------------------------------------|-----|

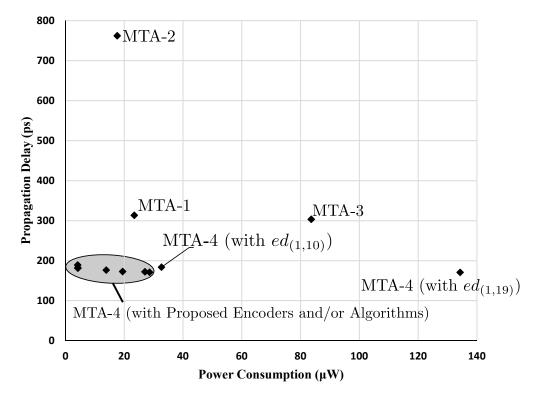

| 5.10 | Power Consumption Vs Propagation Delay for 9-digit Ternary Adders   | 112 |

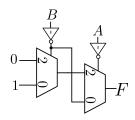

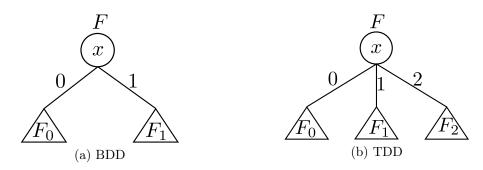

| 6.1  | Binary and Ternary Decision Diagrams                                | 114 |

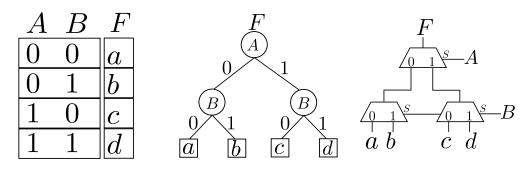

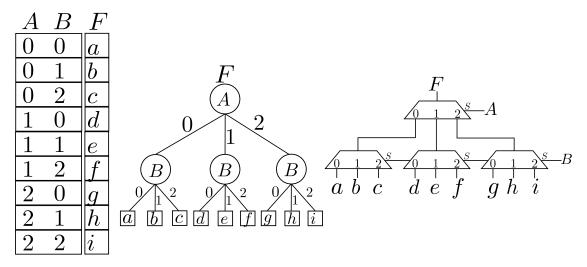

| 6.2  | BDD and its 2 : 1 Mux based implementation for a given Truth-table  | 115 |

| 6.3  | TDD and its 3 : 1 Mux based implementation for a given Truth-table  | 115 |

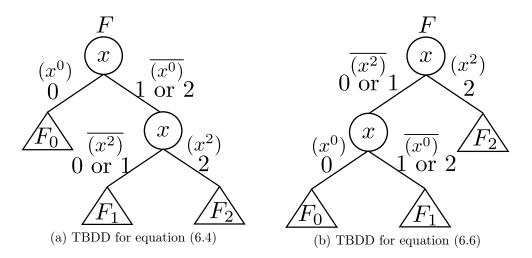

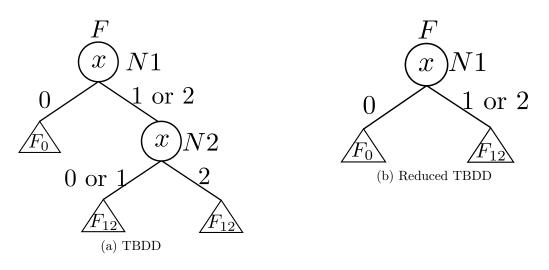

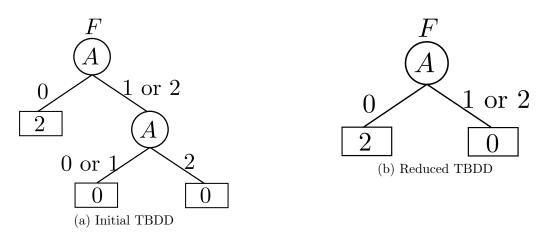

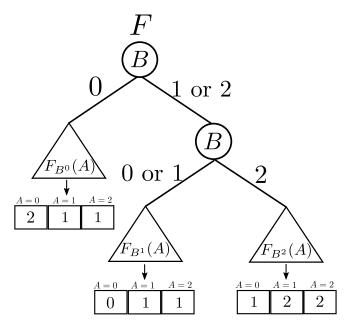

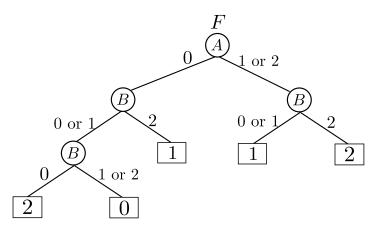

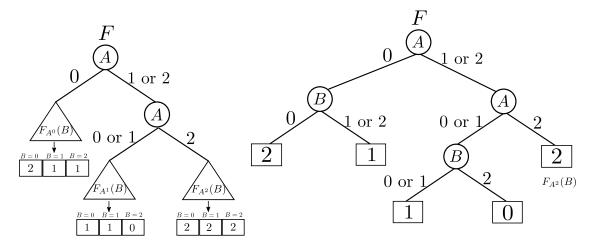

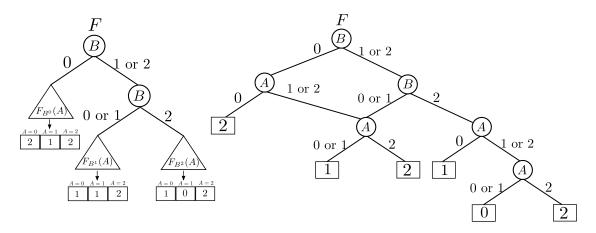

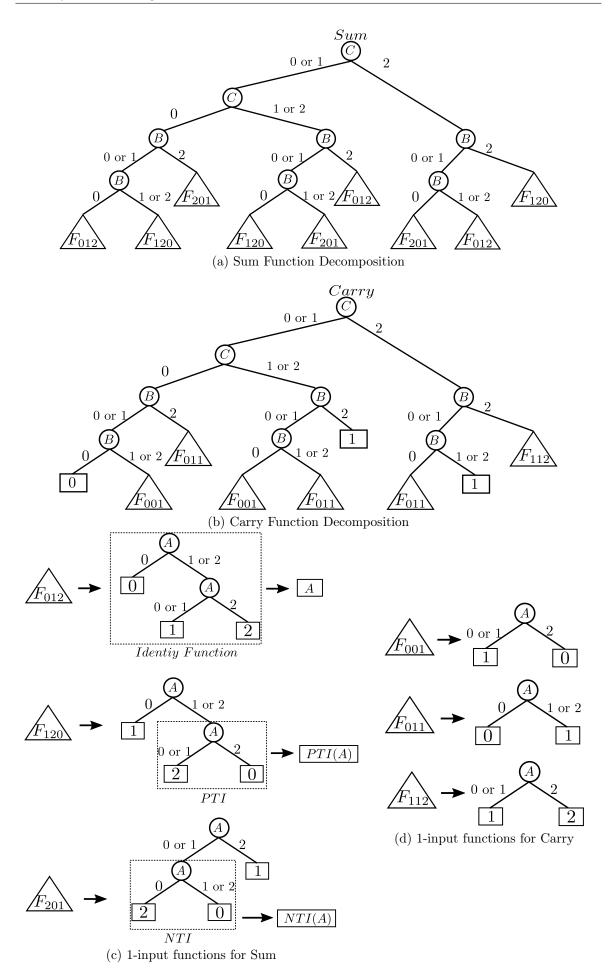

| 6.4  | Ternary-Transformed Binary Decision Diagram                         | 118 |

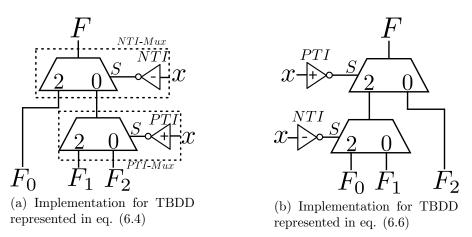

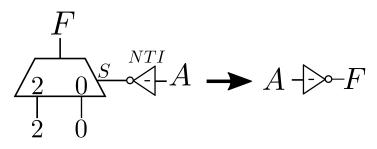

| 6.5  | 2:1 Multiplexer based implementation of TBDD                        | 118 |

| 6.6  | Illustration for Rule 1 $\ldots$                                    | 119 |

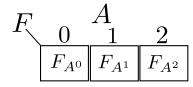

| 6.7  | K-map for 1-input Ternary Function                                  | 121 |

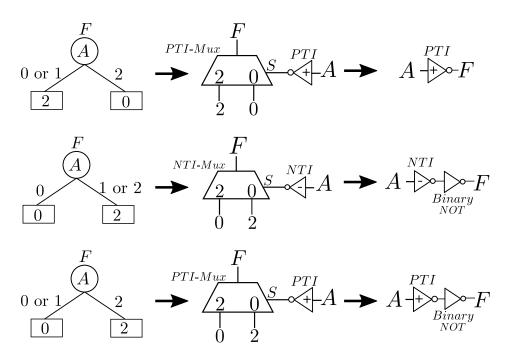

| 6.8  | TBDDs for 1-input Ternary Function                                  | 121 |

| 6.9  | TBDD for $F_{A^0} = 2$ , $F_{A^1} = 0$ and $F_{A^2} = 0$            | 122 |

| 6.10 | Multiplexer-based implementation of Reduced TBDD in Figure 6.9      |     |

|      | and its equivalent Ternary Gate                                     | 122 |

| 6.11 | TBDD templates, their 2:1 multiplexer based implementations and     |     |

|      | equivalent gates                                                    | 122 |

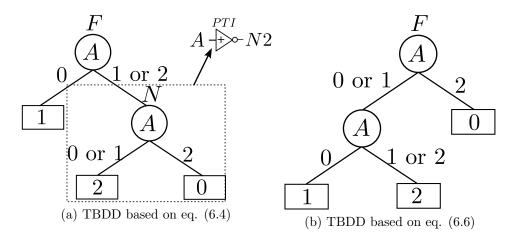

| 6.12 | TBDD Example for Proposition 6.4                                    | 123 |

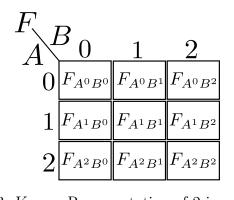

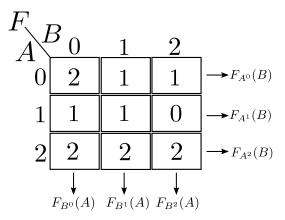

| 6.13 | K-map Representation of 2-input Function                            | 125 |

| 6.14 | K-map Representation of of 2-input Function using 1-input Functions | 126 |

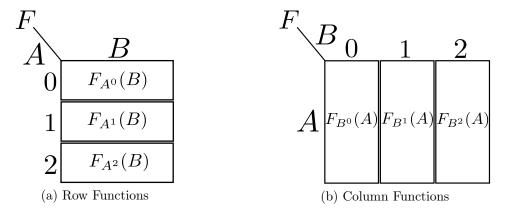

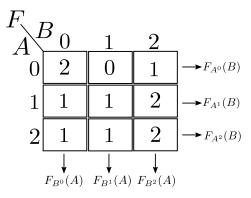

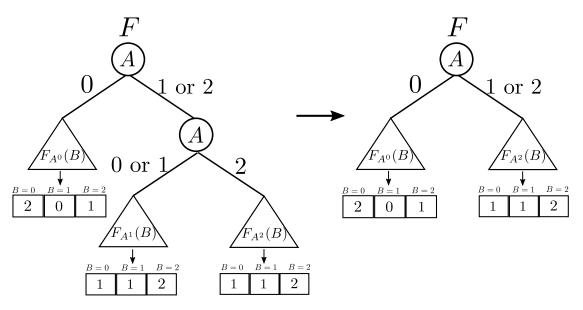

| 6.15 | An Example for 2-input Function                                     | 127 |

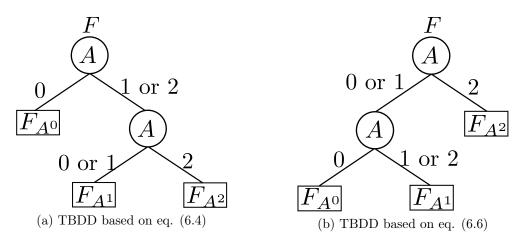

| 6.16 | TBDD representation when decomposed w.r.t $A$                       | 127 |

| 6.17 | TBDD representation when decomposed w.r.t $B$                       | 128 |

| 6.18 | TBDD representation for 2 input function in Figure 6.15 $\ldots$    | 128 |

| 6.19 | An Example for 2-input Function                                     | 129 |

| 6.20 | TBDD representation for function in Figure 6.19, when decomposed    |     |

|      | w.r.t <i>A</i>                                                      | 129 |

| 6.21 | TBDD representation for function in Figure 6.19, when decomposed    |     |

|      | w.r.t <i>B</i>                                                      | 130 |

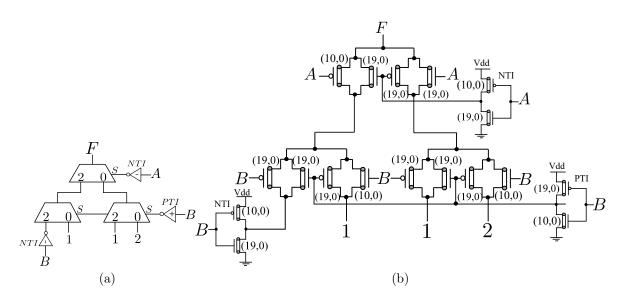

| 6.22 | TBDD for Ternary Full Adder                                         | 134 |

| 6.23 | Implementation of 2:1 Multiplexers                                  | 135 |

| 6.24 | Implementation of TBDD in Figure 6.18  | <br>136 |

|------|----------------------------------------|---------|

| 6.25 | Implementation of Ternary Full Adder . | <br>137 |

# List of Tables

| 2.1 | Ternary Inverters [36]                                              | 7   |

|-----|---------------------------------------------------------------------|-----|

| 2.2 | Logic Symbols                                                       | 7   |

| 2.3 | Relation Between Chirality, CNT Diameter and Threshold Voltage [44] | 10  |

| 2.4 | Technology Parameters for CNFET model in $[44, 45, 53]$             | 11  |

| 3.1 | Truth Table (Example 1)                                             | 19  |

| 3.2 | Truth Table (Example 2)                                             | 24  |

| 3.3 | Half-Sum $(HS)$                                                     | 30  |

| 3.4 | Ternary Function (Example 1)                                        | 38  |

| 3.5 | Truth-Table for basic Ternary Circuits                              | 39  |

| 3.6 | Simulation Results for Basic Circuits                               | 44  |

| 3.7 | Propagation Delay vs Load                                           | 46  |

| 3.8 | ANTE for Ternary Half-Adders                                        | 50  |

| 4.1 | Half-Adder Karnaugh Maps                                            | 61  |

| 4.2 | Truth-Table for Carry-Out                                           | 64  |

| 4.3 | Average Power Consumption for N-digit Adders                        | 79  |

| 4.4 | Propagation (FO4) Delay for $N$ -digit Adders                       | 81  |

| 4.5 | Delay for $N$ -digit Adders for different output loads              | 83  |

| 4.6 | Power-Delay Product for N-digit Adders                              | 84  |

| 4.7 | Number of Transistors required for $N$ -digit Adders                | 85  |

| 5.1 | A Comparison of Encoders                                            | 94  |

| 5.2 | Encoder Mapping for Ternary Adders                                  | 108 |

| 5.3 | Simulation Results for $N$ -digit Ternary Adders                     | 111 |

|-----|----------------------------------------------------------------------|-----|

| 6.1 | Unary Operators                                                      | 124 |

| 6.2 | Comparison of Transistor Count of Proposed 2:1 Multiplexer based     |     |

|     | Algorithm with that of Exitsing 3:1 Multiplexer based Algorithm [41] | 139 |

| 6.3 | Simulation Results for Ternary Benchmark Circuits                    | 140 |

| 6.4 | Comparison of Ternary Adders                                         | 141 |

| 6.5 | Comparison of Existing Manual Designs with those Generated using     |     |

|     | the Proposed Algorithm                                               | 142 |

# List of Abbreviations

| ANTE   | Average Noise Threshold Energy                    |

|--------|---------------------------------------------------|

| BDD    | Binary Decision Diagram                           |

| CMOS   | Complementary Metal-Oxide-Semiconductor           |

| CNFET  | Carbon-Nanotube Field Effect Transistor           |

| CNT    | Carbon-Nanotube                                   |

| CSA    | Conditional Sum Adder                             |

| НС     | Half-Carry                                        |

| HS     | Half-Sum                                          |

| IC     | Integrated circuit                                |

| MHTA   | Multi-Digit Half-Adder based Ternary Adder        |

| MOS    | Metal-Oxide-Semiconductor                         |

| MOSFET | Metal-Oxide Semiconductor Field Effect Transistor |

| MSD    | Most Significant Digit                            |

| MTA    | Multi-Digit Ternary Adders                        |

| MTPA   | Multi-Digit Ternary Prefix Adder                  |

| MVL    | Multi-Valued Logic                                |

| NIC    | Noise Immunity Curve                        |

|--------|---------------------------------------------|

| NWFET  | Nano-Wire Field Effect Transistor           |

| PDP    | Power-Delay Product                         |

| qFET   | Quantum-dot gate field effect transistor    |

| QROBDD | Quasi Reduced BDD                           |

| QROTDD | Quasi Reduced TDD                           |

| RBDD   | Reduced BDD                                 |

| RTDD   | Reduced TDD                                 |

| TBDD   | Ternary-Transformed Binary Decision Diagram |

| TDD    | Ternary Decision Diagram                    |

| VLSI   | Very Large Scale Integrated Circuit         |

## Chapter 1

## Introduction

#### 1.1 Overview and Motivation

Integrated circuit (IC) technology has enabled rapid advances in design and implementation of innovative devices, and systems that have changed the way we live and communicate. Integration of more transistors increases the computing power and helps in building efficient systems [1]. The number of transistors that can be integrated on a chip has been doubling every 1-2 years as predicted by the Gordon Moore, an industry pioneer, in 1960s [2]. This prediction, famously known as Moore's Law, has been proven correct, time and again. This has been made possible mainly due the continuous scaling or miniaturization of components that are integrated onto a chip [3]. For example, in CMOS technology, the gate length of a Metal-Oxide Semiconductor Field Effect Transistor (MOSFET) has been scaling by a factor of 0.7 every two years. Over the last few years, FinFET [4] (a variation of MOSFET) based devices have been fabricated at 22nm and the 14nm technology is foreseen to be reached in near future [5]. CMOS technology scaling beyond deep sub-micron/nano range, while enabling higher integration of VLSI designs, has caused various reliability issues. Some of the issues of CMOS scaling beyond nanometer range are increased leakage current, processes variations etc [6]. These non-idealities have caused the I-V characteristics of MOSFETs to be different from what is expected. It has become more difficult to improve performance by technology scaling.

This has led to the emergence of alternate computing paradigms (reversible computing [7], multi-valued logic (MVL) computing [8]) coupled with emerging devices (carbon-nanotube field effect transistor (CNFET) [9], Quantum-dot gate field effect transistor (qFET) [10]etc). Researchers have also been investigating new materials and devices in sub-10nm which could possibly replace MOS based transistors. Based on ITRS road map [5], some of the emerging devices that have the characteristics to replace traditional MOS based devices are Carbon-Nanotube Field Effect Transistor (CNFET) [11, 12], Nanowire Field Effect Transistor (NWFET) [13], Graphene Transistor [14, 15] and III-V compound semiconductor [16, 17].

One of the computing paradigms that has received considerable attention over the last few decades is MVL [18]. Three-valued or Ternary Logic, which is a special case of MVL has attracted considerable interest over the last couple of decades. A recent survey presents various contemporary aspects related to MVL [8]. Some of the advantages of MVL include reduced interconnect complexity, less device count etc. This is due to the fact that more information is embedded per digit. For example, it is possible to represent a 14-digit (N-digit) binary number using only 9 ( $\log_3(2^N - 1)$ ) ternary digits . Ternary logic is a special case of MVL with three significant states. There have been many CMOS-based implementations for ternary logic [19,20]. It has been shown that the performance of CMOS-based designs is enhanced by adding Multi-Valued Logic (MVL) blocks to binary designs [21,22]. A design for ternary wallace-tree multiplier has been implemented in [24]. Apart from the works which focus on novel designs [23-26], there have been many works which focus on synthesis of MVL logic circuits [27-29].

The CMOS implementations of MVL are mainly classified as current-mode circuits [30] which require transistor biasing and voltage-mode circuits [22] which require additional voltage sources to create multi-threshold transistors. Due to the problems in MOS-based devices and non-availability of appropriate devices, design of efficient MVL circuits has for long remained a concern [18]. But, the emergence of several new device technologies [9, 10, 31] has led to renewed interest in ternary and quaternary logic in particular.

CNFETs have been used widely in the implementation of ternary logic circuits. CNFET is one of the promising alternatives to MOSFET due to their unique onedimensional band-structure that suppresses backscattering and makes near-ballistic operation a realistic possibility [32–35]. CNFETs use single walled CNT as a conducting channel, which is conducting or semiconducting depending on the angle of atom arrangement along the tube also called as chirality vector. Unlike in MOS technology, where body biasing is used to control threshold voltages, in CNFET technology the threshold voltage is controlled by changing the diameter of CNT which in turn depends on the chirality vector. [36]. This dependence makes CNTFET suitable for implementation of MVL circuits.

There have been many CNFET-based design [36–40] and synthesis techniques [41] that are used to realize ternary logic circuits. The existing work on CNFET-based ternary logic circuits is relatively recent and there is scope to explore new design techniques to realize efficient ternary circuits. Therefore in this thesis, new design and synthesis techniques, which aid in realizing efficient CNFET-based ternary logic circuits, have been investigated.

#### 1.2 Contributions