# Low-Power High-Speed and Compact Ternary VLSI Circuit Designs using Carbon Nanotube Field Effect Transistors

#### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of **DOCTOR OF PHILOSOPHY**

by

SNEH LATA MUROTIYA

2010PHXF026P

Under the Supervision of **Prof. Anu Gupta**

BIRLA INSTITUTE OF TECHNOLOGY & SCIENCE, PILANI 2015

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

## **CERTIFICATE**

This is to certify that the thesis entitled "Low-Power High-Speed and Compact Ternary VLSI Circuit Designs using Carbon Nanotube Field Effect Transistors" and submitted by Sneh Lata Murotiya, ID No 2010PHXF026P for award of Ph.D. of the Institute embodies original work done by her under my supervision.

(Signature of the Supervisor) **Dr. Anu Gupta**Associate Professor

Birla Institute of Technology & Science, Pilani

Pilani - 333031 (Rajasthan) INDIA

Date:

# Dedicated

To

My Beloved and Inspiring Parents

Shrimati Manju Devi

And

Shri Suresh Kumar Murotiya

## **ACKNOWLEDGEMENTS**

Foremost, I would like to express my humble gratitude and sincere thanks to my supervisor Prof. Anu Gupta for her valuable guidance, encouragement, suggestions, and moral support throughout the period of this research work. It has been a privilege for me to work and learn under her.

Next I would like to express my deep sense of satisfaction to BITS Pilani for providing all the necessary facilities and support to complete the research work. My special thanks to Prof. V.Sambasiva Rao, Acting Vice Chancellor, BITS Pilani, and Prof. Ashoke Kumar Sarkar, Director, BITS Pilani, Pilani campus, for giving me an opportunity to pursue my research successfully.

I am thankful to Prof. Sanjay Kumar Verma, Dean, Academic Research (Ph.D. Programme), BITS Pilani, and Dr. Hemant R. Jadhav, Professor-in-Charge, Academic Research (Ph.D. Programme), BITS Pilani, Pilani Campus, for providing all necessary guidelines and extending full support which were crucial for the completion of this thesis.

I am thankful to members of Doctoral Advisory Committee, Prof. Navneet Gupta and Prof. Abhijit Rameshwar Asati, for their critical comments, which helped me improve the quality of manuscript.

Thanks are due to Prof. Vinod Kumar Chaubey, Prof. Surekha Bhanot, Mr. Pawan Sharma, Ms. Vinita Tiwari, Mr. Nitin Chaturvedi and other faculty colleagues of Dept. of Electrical & Electronics Engineering for their constant motivation and encouragement.

Lastly, in everyday life, the portion of Earth exposed to Sun is said to have day, whereas the remaining portion is said to have night. Similarly behind all accomplishments there are equal sacrifices. I am thankful to Almighty Gods for giving their divine blessings to my husband Mr. Deepak Kabra and our daughter Ms. Vaani Kabra. I deeply value the cooperation and support received from my mother in-law Sumitra Devi, father in-law Shri Babu Lal Kabra, Sisters Mrs. Suman Ladda, Mrs. Saroj Kaliya, Ms. Sangeeta Murotiya and Ms. Soniya Murotiya, Brother Mr. Kamlesh Murotiya, Mrs. Vanita Murotiya and other family members.

Sneh Lata Murotiya

#### **ABSTRACT**

Carbon nanotube field effect transistor (CNTFET) shows great promises as extension to Silicon MOSFET for building high performance and low power VLSI circuit. Three-valued (ternary) logic is a promising alternative to traditional binary logic for accomplishing simplicity and energy efficiency in modern digital design. Ternary logic has an elegant association with CNTFET because the best way to design ternary circuit is the multiple-threshold method and desired threshold voltage can be easily achieved by utilizing different diameter of CNT in CNTFET device.

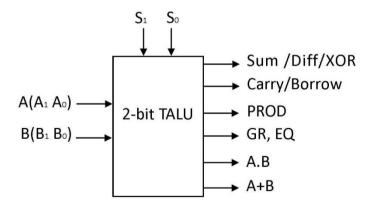

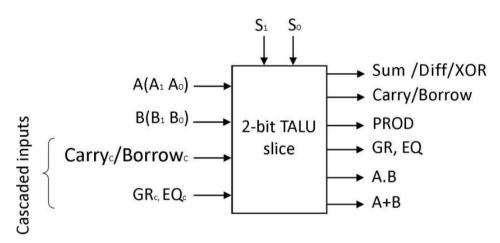

This thesis develops designs of ternary arithmetic and logic unit (TALU) and content addressable memory cell using CNTFETs. First, 2-bit hardware optimized ternary ALU (HO-TALU) is presented. 2-bit HO-TALU gets minimization in required hardware at both architectural as well as at circuit level. At architecture level, HO-TALU has a new addersubtractor (AS) module which performs both addition and subtraction operations using an adder module only with the help of multiplexers. Thus, it eliminates a subtractor module from the conventional architecture. At circuit level, HO-TALU minimizes ternary function expressions and utilizes binary gates along with ternary gates in realization of functional modules: AS, multiplier, comparator and exclusive-OR. AS module has a minor loss in power-delay product (PDP) but multiplier, comparator and exclusive-OR modules show improved PDP. As a consequence, HO-TALU gets significant reduction in device count with marginally increase in PDP for addition and subtraction operations only in comparison with CNTFET-based ternary designs available in the literature. Design of 2-bit HO-TALU is modified to develop a 2-bit HO-TALU slice which could be easily cascaded to construct N-bit HO-TALU.

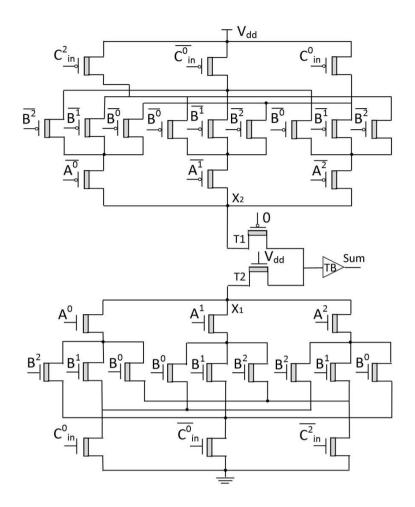

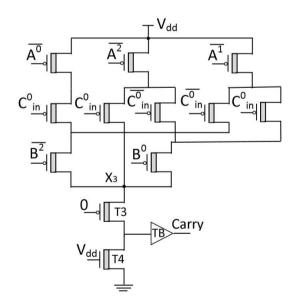

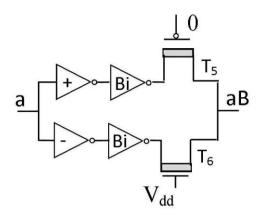

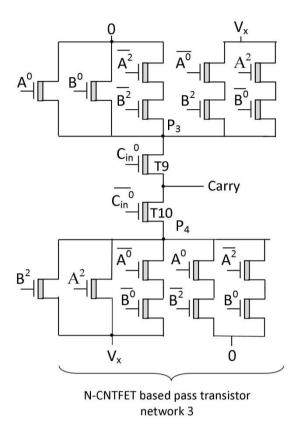

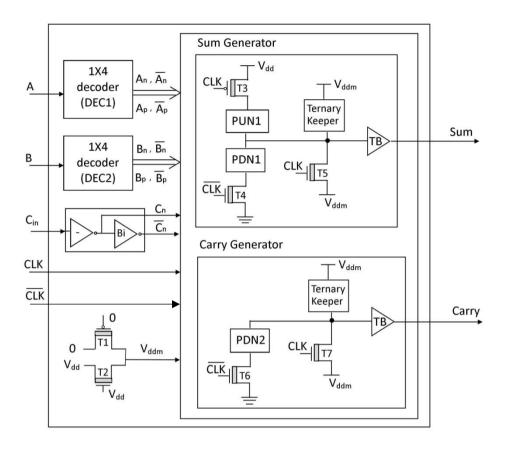

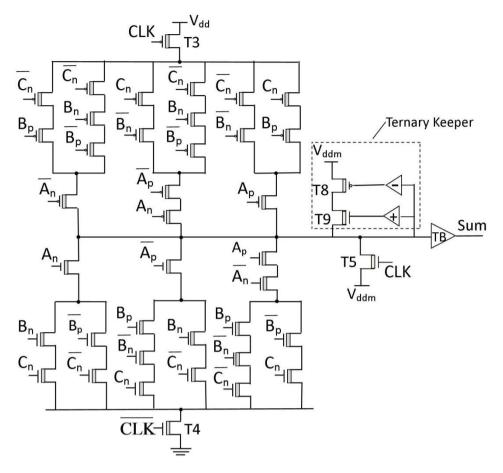

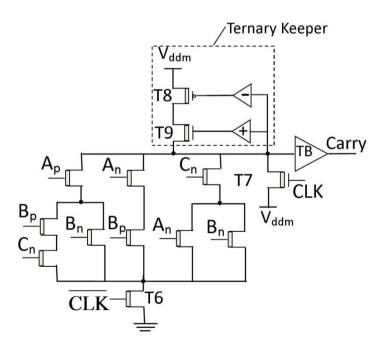

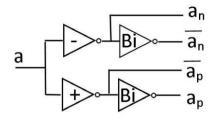

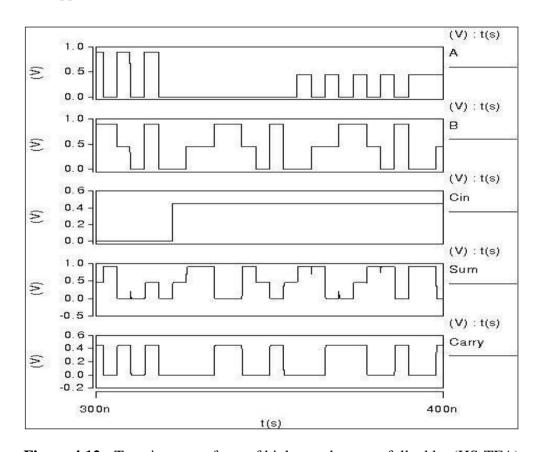

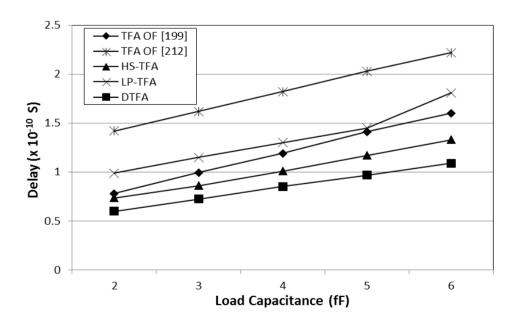

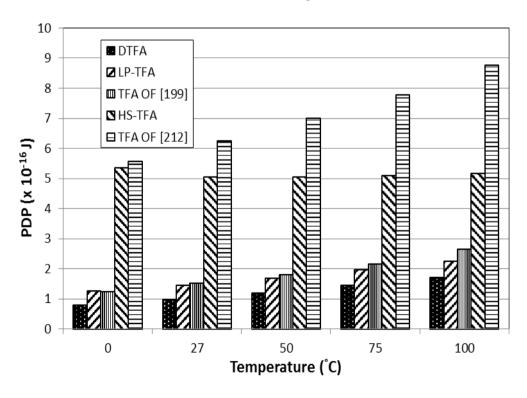

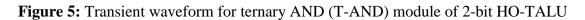

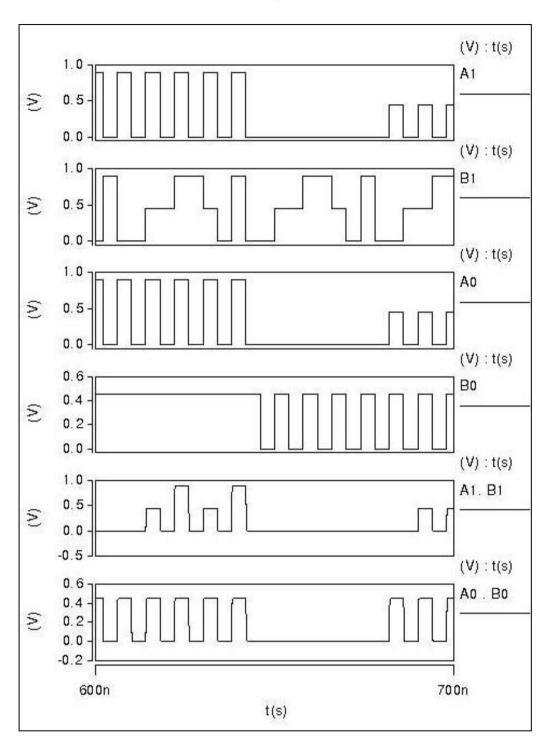

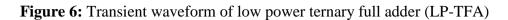

Ternary full adder (TFA) which is a basic sub-block of AS module, is modified using different circuit techniques to improve its efficiency in terms of PDP. Three new designs of TFA are presented. The first TFA design named as high speed TFA (HS-TFA) uses a symmetric pull-up and pull-down networks along with a resistive voltage divider as its integral part, which is configured using transistors. Compared to recently developed TFA available in literature, HS-TFA gets improved speed but high power dissipation. In order to reduce power consumption, a second TFA named as low power TFA (LP-TFA) is proposed. LP-TFA makes use of complimentary pass transistor logic style and achieves low power consumption with marginal decrease in PDP. To get improved PDP further, a third TFA is implemented in dynamic logic. This TFA is named as dynamic TFA (DTFA) which uses a

keeper designed for ternary values in order to alleviate charge sharing problem. The realization of all three TFA takes the advantages of inherent binary nature (0 and 1) of input carry leading to simplicity in designs.

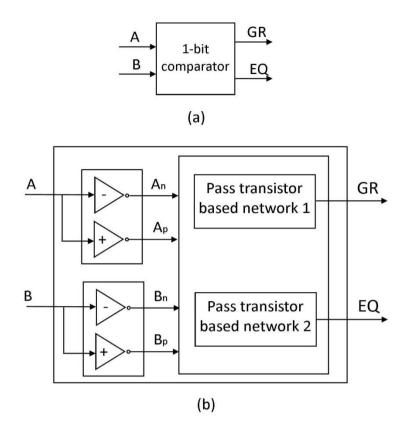

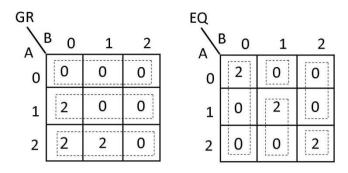

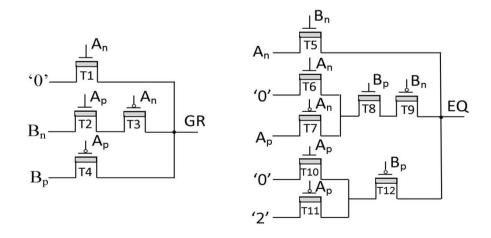

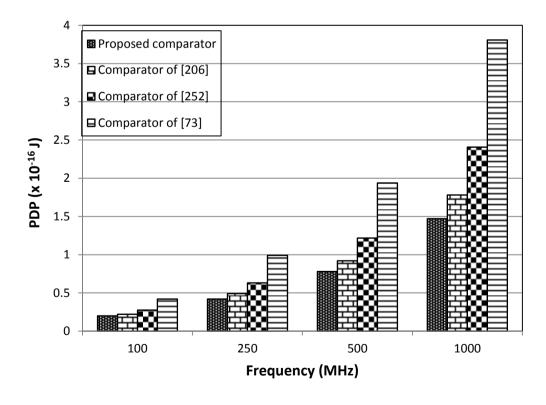

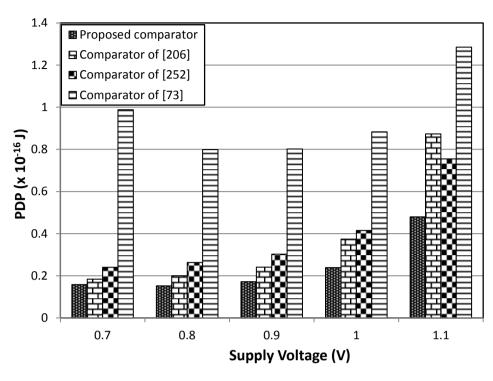

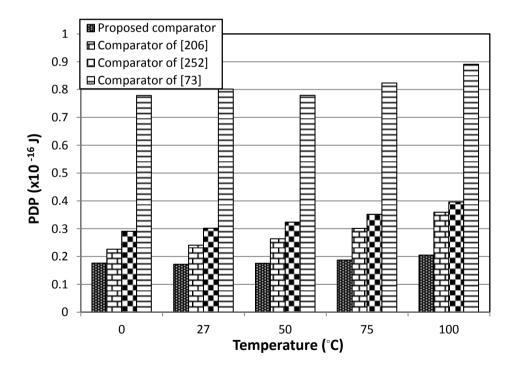

Next, a new design of comparator module of 2-bit HO-TALU is presented. First, 1-bit comparator is developed using pass transistor logic with reduced number of stages in critical delay path. Then, 1-bit design is utilized to create 2-bit and N-bit comparator where a static binary tree configuration is used to correct the voltage levels. The proposed 2-bit comparator achieves better PDP in comparison with that of available counterparts. This comparator, HS-TFA and DTFA have high driving capability. Moreover, all new TFAs and 2-bit comparator are less sensitive to voltage and temperature variations with respect to existing designs.

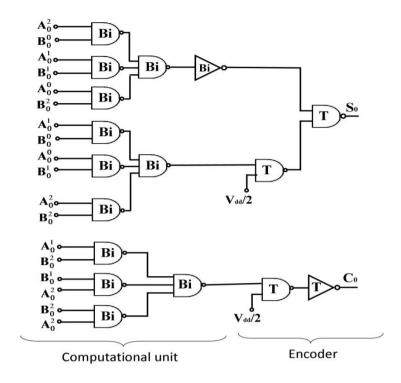

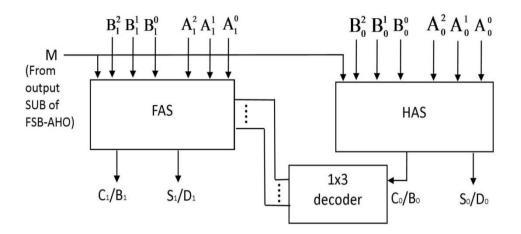

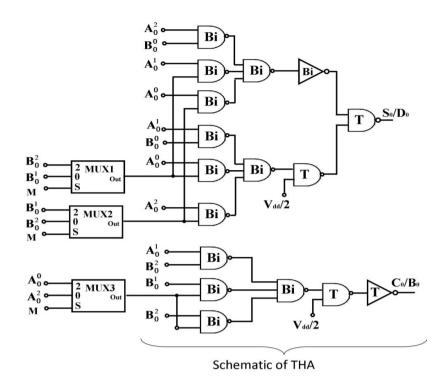

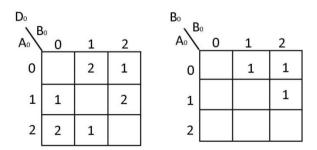

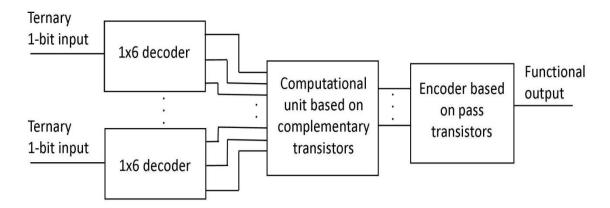

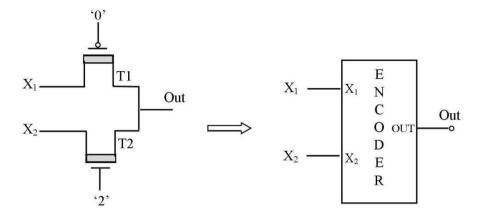

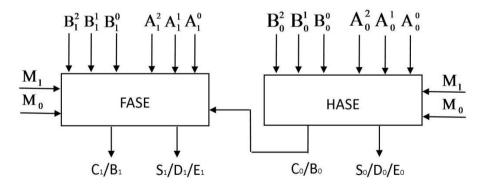

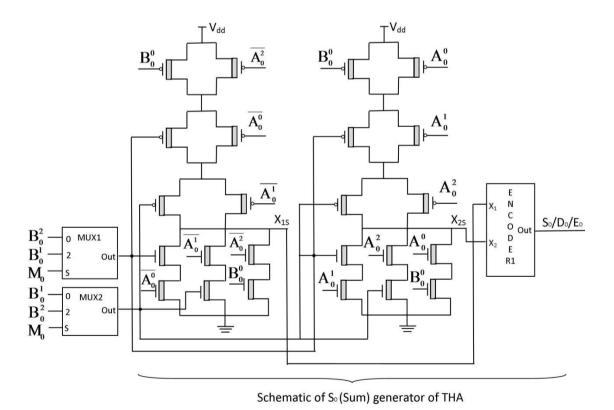

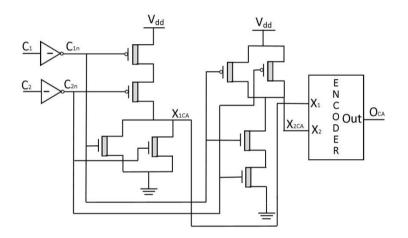

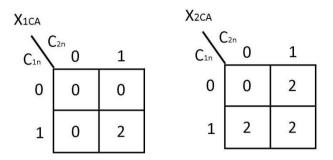

Next, design of 2-bit power optimized ternary ALU (PO-TALU) using CNTFETs is presented. 2-bit PO-TALU functional modules: adder-subtractor-exclusive-OR (ASE) and multiplier, are designed using new complementary CNTFET-based binary computational unit and a low complexity encoder. ASE eliminates exclusive-OR and subtractor modules from the conventional architecture. Multiplier uses a new efficient carry-add (CA) block in place of ternary half adder. As a result, PO-TALU design gets significant improvements in terms of power and power-delay product with device count compared to existing designs. Design of 2-bit PO-TALU slice is shown so that parallel N-bit PO-TALU can be constructed with N/2 slices connected in cascade.

Further, increased attraction for bandwidth-hungry real-time applications like internet has raised a demand for high speed CAM circuits to perform table lookup task. Binary CAM (BCAM) and ternary CAM (TCAM) cells designed based on low capacitance search logic are presented in CNTFET technology. A new three-valued CAM (3CAM) cell is also presented. This cell uses CNTFETs with two different threshold voltages in implementation of low capacitance search network which leads to a fast and compact CAM design with respect to CNTFET based 3CAM cell recently published in the literature.

# TABLE OF CONTENTS

| CE  | ERTIFICATE                                                             | i   |

|-----|------------------------------------------------------------------------|-----|

| AC  | CKNOWLEDGEMENTS                                                        | iii |

| AE  | BSTRACT                                                                | iv  |

| TA  | ABLE OF CONTENTS                                                       | vi  |

| LIS | ST OF TABLES                                                           | ix  |

| LIS | ST OF FIGURES                                                          | X   |

| LIS | ST OF ABBREVIATIONS                                                    | XV  |

| 1.  | Introduction                                                           | 1   |

|     | 1.1. Background                                                        | 1   |

|     | 1.2. Motivation and Objectives                                         | 6   |

|     | 1.3. Thesis Outline                                                    | 11  |

| 2.  | Literature Review                                                      | 13  |

|     | 2.1. Introduction                                                      | 13  |

|     | 2.2. Carbon Nanotube Field Effect Transistor (CNTFET)                  | 13  |

|     | 2.3. Three-valued (Ternary) Arithmetic and Logic Circuits              | 19  |

|     | 2.3.1. Ternary Circuit based on MOSFET                                 | 19  |

|     | 2.3.2. Ternary Circuit based on CNTFET                                 | 24  |

|     | 2.4. Content Addressable Memory (CAM) Cell                             | 29  |

|     | 2.4.1. CAM Cell based on MOSFET                                        | 29  |

|     | 2.4.2. CAM Cell based on CNTFET                                        | 33  |

|     | 2.5. Research Gaps and Scope of the Presented Work                     | 35  |

| 3.  | Design of 2-bit Hardware Optimized Ternary ALU (HO-TALU) using CNTFETs | 36  |

|     | 3.1. Introduction                                                      | 36  |

|     | 3.2. Design of Ternary Logic Gates                                     | 37  |

|     | 3.3. Architecture & Functions of 2-bit HO-TALU                         | 41  |

|     | 3.4. Synthesis, Minimization and Realization of 2-bit HO-TALU Function | 47  |

|     | 3.5. Design & Implementation of 2-bit HO-TALU Functional Module        | 49  |

|     | 3.5.1. Adder-Subtractor (AS) Module                                    | 49  |

|     | 3.5.2. Comparator Module                                               | 56  |

|     | 3.5.3. Exclusive-OR Module                                             | 60  |

|    | 3.5.4. Multiplier Module                                                                                  | 62  |

|----|-----------------------------------------------------------------------------------------------------------|-----|

|    | 3.5.5. T-OR/T-NOR/ T-AND/T-NAND Module                                                                    | 64  |

|    | 3.6. 2-bit HO-TALU Slice for N-bit HO-TALU                                                                | 65  |

|    | 3.7. Results and Discussion                                                                               | 68  |

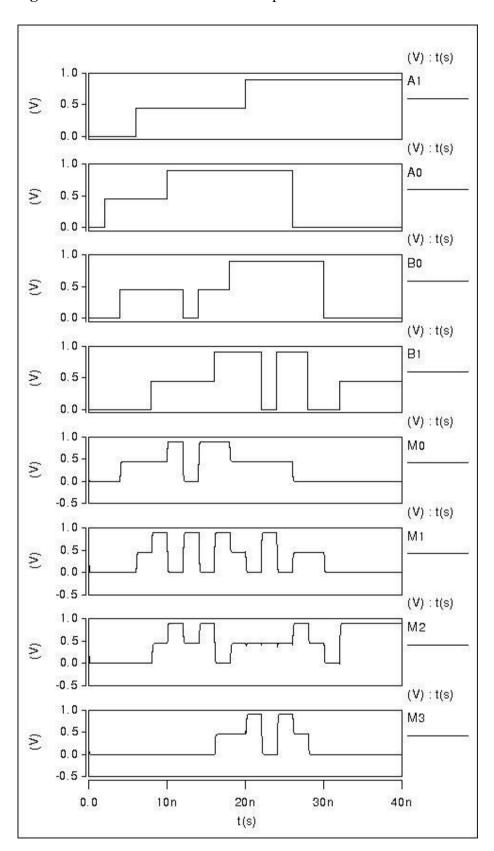

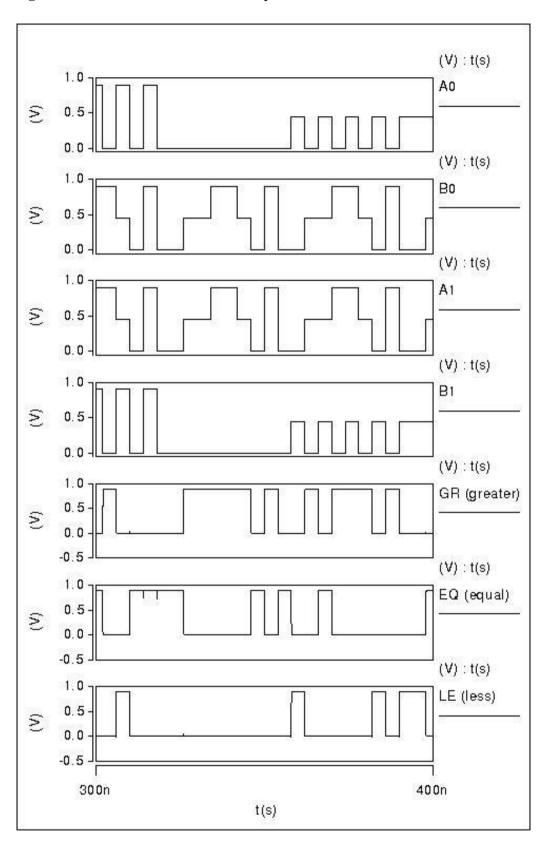

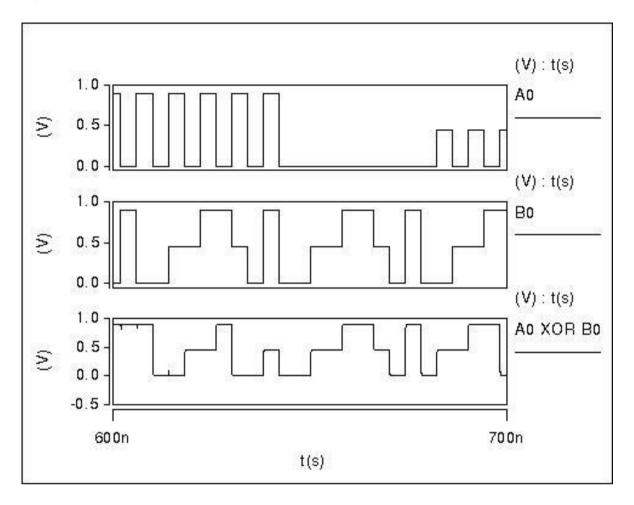

|    | 3.7.1. Functional Verification of 2-bit HO-TALU                                                           | 69  |

|    | 3.7.2. Hardware Efficiency Evaluation of 2-bit HO-TALU                                                    | 70  |

|    | 3.7.3. Performance Evaluation of 2-bit HO-TALU                                                            | 71  |

|    | 3.8. Conclusion                                                                                           | 73  |

| 4. | Performance Boosted Designs of Sub-Blocks of 2-bit Hardware Optimized Ternary ALU (HO-TALU) using CNTFETs | 75  |

|    | 4.1. Introduction                                                                                         | 75  |

|    | 4.2. Designs of Ternary Full Adder (TFA)                                                                  | 76  |

|    | 4.2.1. High Speed TFA (HS-TFA)                                                                            | 76  |

|    | 4.2.2. Low Power TFA (LP-TFA)                                                                             | 82  |

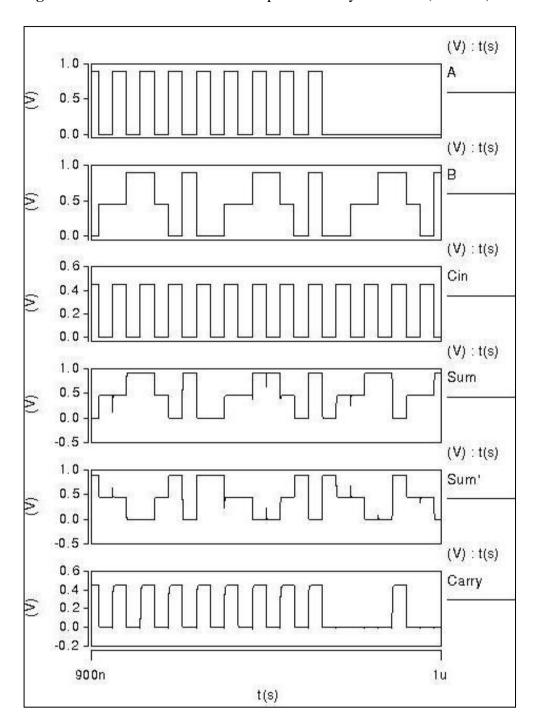

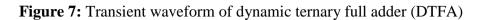

|    | 4.2.3. Dynamic TFA (DTFA)                                                                                 | 87  |

|    | 4.2.4. Results and Discussion                                                                             | 90  |

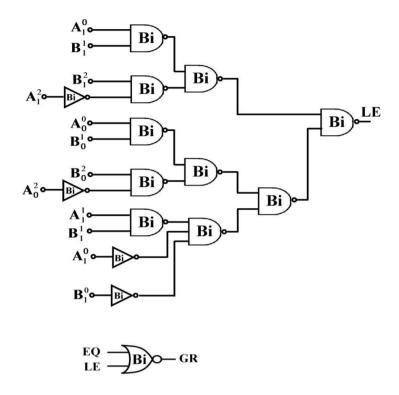

|    | 4.3. Design of Comparator Module                                                                          | 98  |

|    | 4.3.1. 1-bit Comparator                                                                                   | 98  |

|    | 4.3.2. Design of N-bit Comparator                                                                         | 101 |

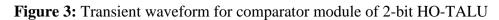

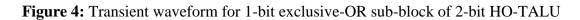

|    | 4.3.3. Results and Discussion                                                                             | 103 |

|    | 4.4. Conclusion                                                                                           | 110 |

| 5. | Design of 2-bit Power Optimized Ternary ALU (PO-TALU) using CNTFETs                                       | 111 |

|    | 5.1. Introduction                                                                                         | 111 |

|    | 5.2. Architecture & Functions of 2-bit PO-TALU                                                            | 112 |

|    | 5.3. Minimization and Realization of 2-bit PO-TALU Functions                                              | 117 |

|    | 5.4. Design & Implementation of 2-bit PO-TALU Functional Module                                           | 119 |

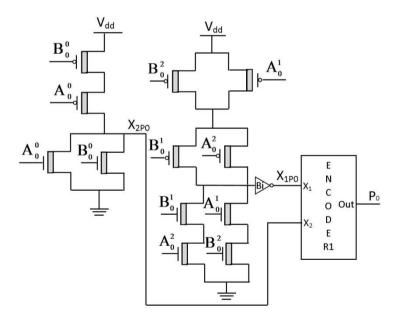

|    | 5.4.1. Adder-Subtractor-Exclusive-OR (ASE) Module                                                         | 119 |

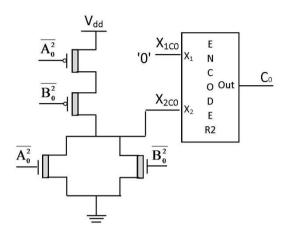

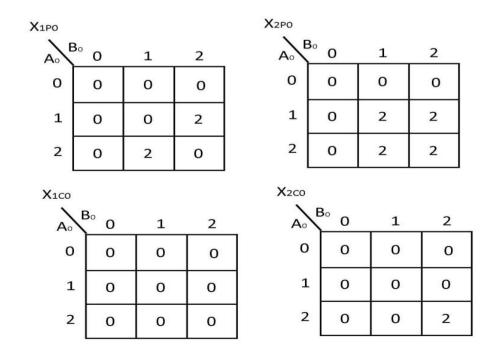

|    | 5.4.2. Multiplier Module                                                                                  | 130 |

|    | 5.4.3. Comparator Module                                                                                  | 134 |

|    | 5.5. Implementation of 2-bit PO-TALU Slice                                                                | 134 |

|    | 5.6. Results and Discussion                                                                               | 136 |

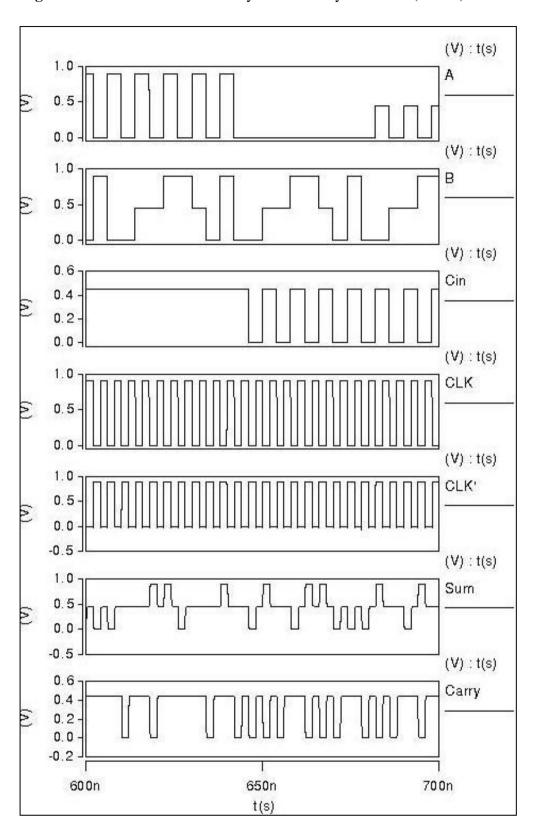

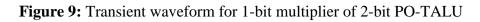

|    | 5.6.1. Functional Verification of 2-bit PO-TALU                                                           | 137 |

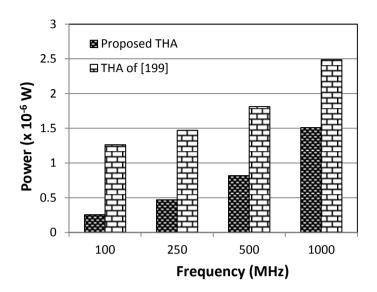

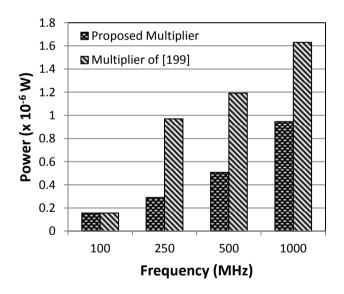

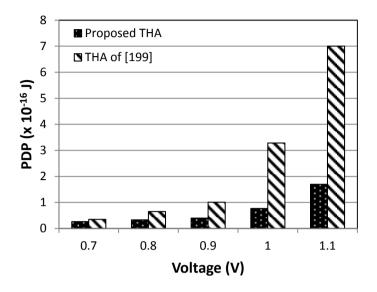

|    | 5.6.2 Performance Evaluation of 2 hit PO TALLI                                                            | 137 |

| 5.7. Conclusion                                                              | 144 |

|------------------------------------------------------------------------------|-----|

| 6. Design of High Speed Content Addressable Memory (CAM) Cells using CNTFETs | 145 |

| 6.1. Introduction                                                            | 145 |

| 6.2. Design of CAM Cells                                                     | 146 |

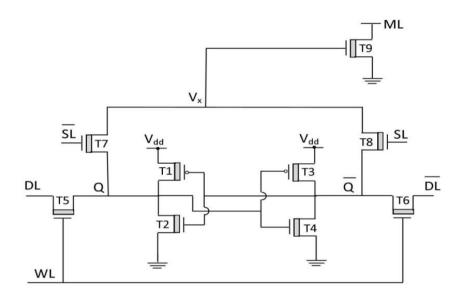

| 6.2.1. Binary CAM (BCAM) Cell                                                | 146 |

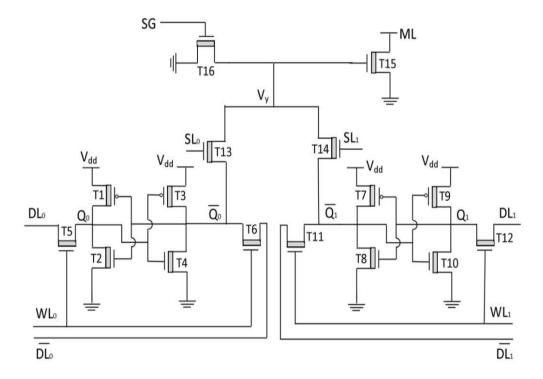

| 6.2.2. Ternary CAM (TCAM) Cell                                               | 147 |

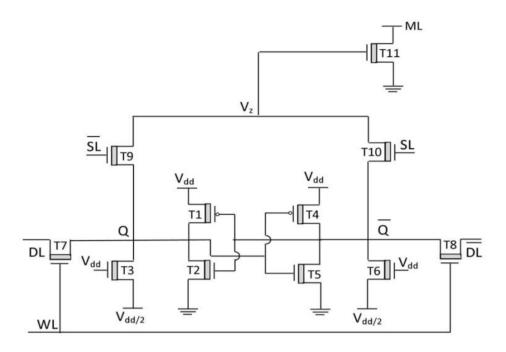

| 6.2.3. Three-Valued CAM (3CAM) cell                                          | 149 |

| 6.3. Results and Discussion                                                  | 152 |

| 6.4. Conclusion                                                              | 156 |

| 7. Conclusion and Future work                                                | 157 |

| 7.1. Conclusion                                                              | 157 |

| 7.2. Future Scope of Work                                                    | 160 |

| REFERENCES                                                                   | 161 |

| APPENDIX I                                                                   | 187 |

| APPENDIX II                                                                  | 200 |

| LIST OF PUBLICATION                                                          | 204 |

| BRIEF BIOGRAPHY OF THE CANDIDATE                                             | 205 |

| BRIEF BIOGRAPHY OF THE SUPERVISOR                                            | 206 |

# **LIST OF TABLES**

| Table 2.1  | Technology parameters for CNTFET [117]                                                   |         |

|------------|------------------------------------------------------------------------------------------|---------|

| Table 3.1  | Definition of logic states in ternary logic                                              |         |

| Table 3.2  | Truth table of ternary inverters                                                         |         |

| Table 3.3  | Truth table of ternary NAND and NOR gates                                                |         |

| Table 3.4  | Function table of HO-TALU                                                                |         |

| Table 3.5  | Truth table of ternary half adder (THA)                                                  | 48      |

| Table 3.6  | Truth table of ternary half subtractor (THS)                                             |         |

| Table 3.7  | Truth table of ternary full adder (TFA) and full subtractor (TFS)                        |         |

| Table 3.8  | Truth table of 2-bit ternary comparator                                                  | 56-57   |

| Table 3.9  | Truth table of 1-bit ternary XOR                                                         |         |

| Table 3.10 | Truth table of 1-bit ternary multiplier                                                  |         |

| Table 3.11 | Comparison of ternary circuits based on device count                                     | 70      |

| Table 3.12 | Simulation results of ternary circuits                                                   | 72      |

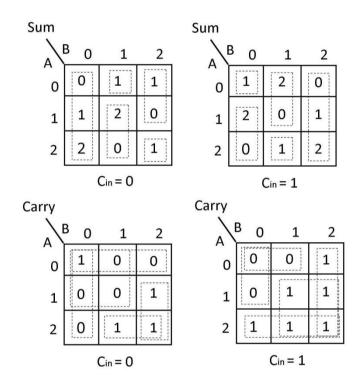

| Table 4.1  | Truth table of ternary full adder (TFA)                                                  | 77-78   |

| Table 4.2  | Switching activity for Sum and Carry generator of high speed ternary full adder (HS-TFA) | 78      |

| Table 4.3  | Truth table of 1-to-6 ternary decoder                                                    | 80      |

| Table 4.4  | Simulation results of CNTFET-based ternary full adder (TFA) designs                      | 93      |

| Table 4.5  | Decoding of outputs for comparison response                                              | 98      |

| Table 4.6  | Truth table of 1-bit comparator                                                          | 99      |

| Table 4.7  | Simulation results of 2-bit comparator circuits                                          | 105     |

| Table 5.1  | Function table of 2-bit PO-TALU                                                          | 113     |

| Table 5.2  | Truth table of ternary encoder                                                           | 118     |

| Table 5.3  | Function select table for ASE module                                                     | 120     |

| Table 5.4  | Addition rules for ternary half adder (THA)                                              | 121     |

| Table 5.5  | Subtraction rules for ternary half subtractor (THS)                                      | 123     |

| Table 5.6  | Addition rules for ternary full adder (TFA)                                              | 127     |

| Table 5.7  | Subtraction rules for ternary full subtractor (TFS)                                      | 128-129 |

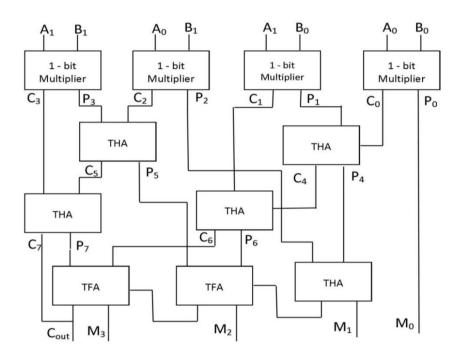

| Table 5.8  | Truth table of carry add (CA)                                                            | 131     |

| Table 5.9  | Design rules for ternary 1-bit multiplication                                            | 133     |

| Table 5.10 | Decoding of outputs for comparison response                                              | 134     |

| Table 5.11 | Simulation results of CNTFET-based adder circuits                                        | 139     |

| Table 5.12 | Simulation results of CNTFET-based multiplier circuits                                   | 140     |

| Table 6.1  | Ternary encoding for 16T TCAM cell                                                       | 148     |

# **LIST OF FIGURES**

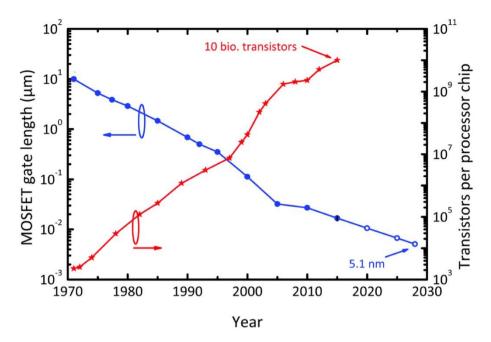

| Figure 1.1  | Evolution of MOSFET gate length (filled blue circles and open blue circles for ITR targets) and integration complexity of microprocessor chip (red stars), as a function of time [7] |    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

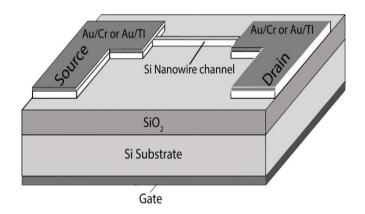

| Figure 1.2  | Schematic view of Si based NWFET [30]                                                                                                                                                | 3  |

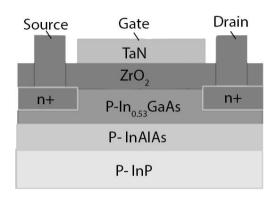

| Figure 1.3  | Schematic view of n-type III-V compound semiconductor FET [33]                                                                                                                       |    |

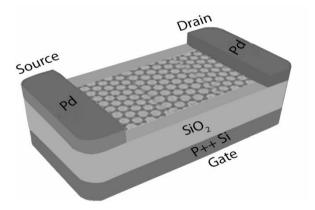

| Figure 1.4  | Schematic view of graphene nanoribbon transistor [22]                                                                                                                                | 4  |

| Figure 1.5  | Schematic view of CNTFET [39]                                                                                                                                                        | 5  |

| Figure 1.6  | Advantages of ternary logic circuits [61]                                                                                                                                            | 8  |

| Figure 2.1  | Unrolled sheet of graphite and the rolled lattice structure of CNT [86]                                                                                                              |    |

| Figure 2.2  | e 2.2 Carbon nanotube field effect transistor (CNTFET) (a) schematic view of a CNTFET device, (b) SB-CNTFET, (c) M-CNTFET, (d) T-CNTFET                                              |    |

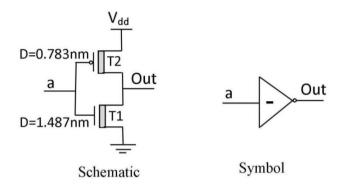

| Figure 3.1  | Negative ternary inverter (NTI) [199]                                                                                                                                                | 39 |

| Figure 3.2  | Positive ternary inverter (PTI) [199]                                                                                                                                                | 39 |

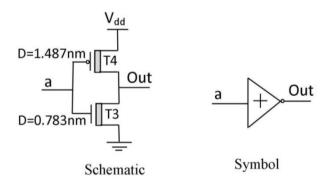

| Figure 3.3  | Standard ternary inverter (STI) [199]                                                                                                                                                | 40 |

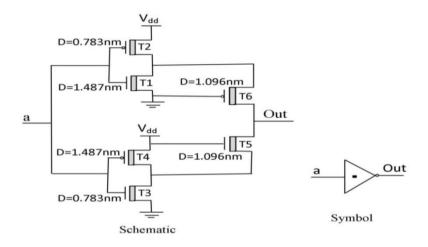

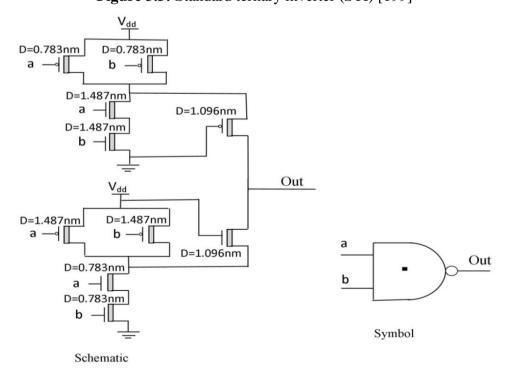

| Figure 3.4  | Standard ternary NAND (STNAND) gate [199]                                                                                                                                            | 40 |

| Figure 3.5  | Standard ternary NOR (STNOR) gate [199]                                                                                                                                              | 41 |

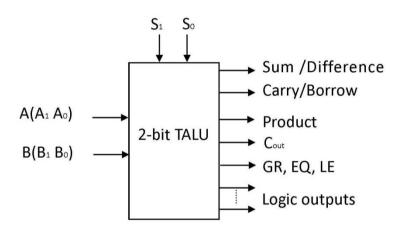

| Figure 3.6  | (a) Pin out diagram of 2-bit HO-TALU                                                                                                                                                 | 42 |

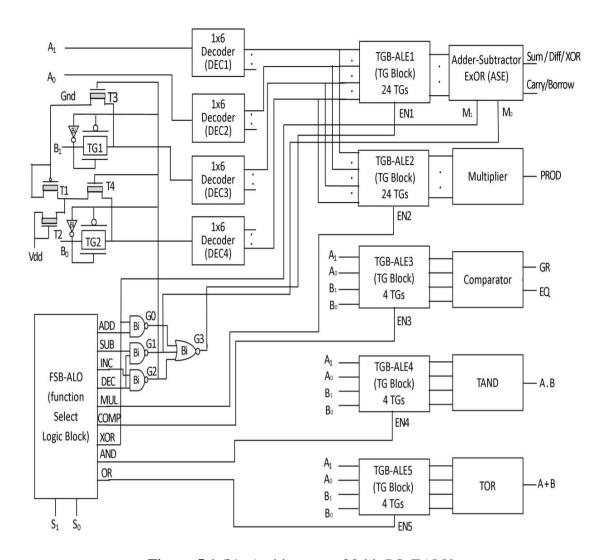

| Figure 3.6  | (b) Architecture of 2-bit HO-TALU                                                                                                                                                    | 43 |

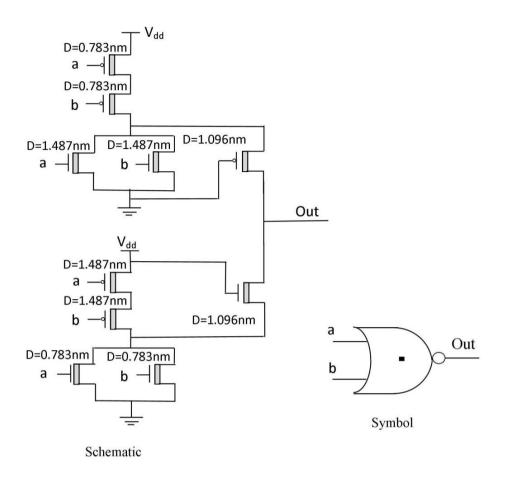

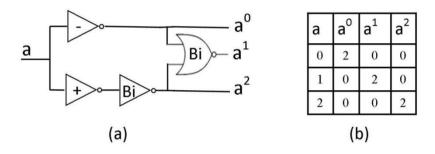

| Figure 3.7  | 1-to-3-line ternary decoder (a) logic level diagram (b) truth table                                                                                                                  | 44 |

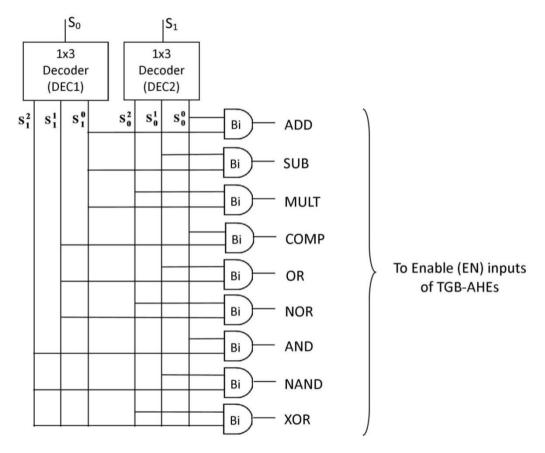

| Figure 3.8  | Logic level diagram of function selection logic block with active high outputs (FSB-AHO)                                                                                             | 45 |

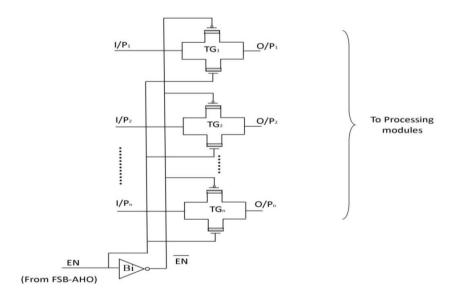

| Figure 3.9  | Logic level diagram of transmission gate block with active high enable (TGB-AHE)                                                                                                     | 46 |

| Figure 3.10 | Ternary function implementation for 2-bit HO-TALU                                                                                                                                    | 47 |

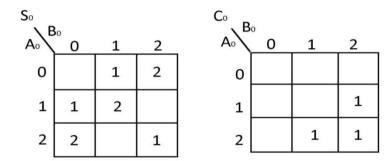

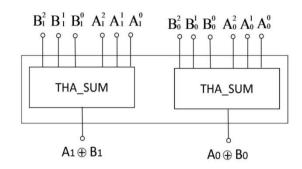

| Figure 3.11 | K-map of ternary half adder (THA)                                                                                                                                                    | 48 |

| Figure 3.12 | Logic level diagram of ternary half adder (THA)                                                                                                                                      | 49 |

| Figure 3.13 | Logic level diagram of 2-bit ternary adder-subtractor (AS)                                                                                                                           | 50 |

| Figure 3.14 | Logic level diagram of ternary half adder-subtractor (HAS)                                                                                                                           | 51 |

| Figure 3.15 | K-map of ternary half subtractor (THS)                                                                                                                                               | 52 |

| Figure 3.16 | (a) Logic diagram of $S_1/D_1$ generator of ternary full adder-subtractor (FAS)                                                                                                      | 53 |

| Figure 3.16 | (b) Logic diagram of $C_1/B_1$ generator of ternary full adder-subtractor (FAS)                                                                                                      | 53 |

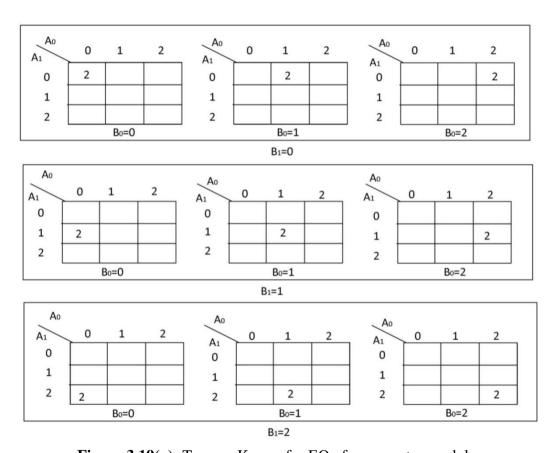

| Figure 3.17 | K-map for ternary full adder (TFA)                                                                                                                                                   | 55 |

| Figure 3.18 | K-map for ternary full subtractor (TFS)                                                                                                                                              | 55 |

| Figure 3.19 | (a) Ternary K-map for EQ of comparator module                                                                                                                                        | 58 |

| Figure 3.19 | (b) Ternary K-map for LE of comparator module                                                                                                                                        | 59 |

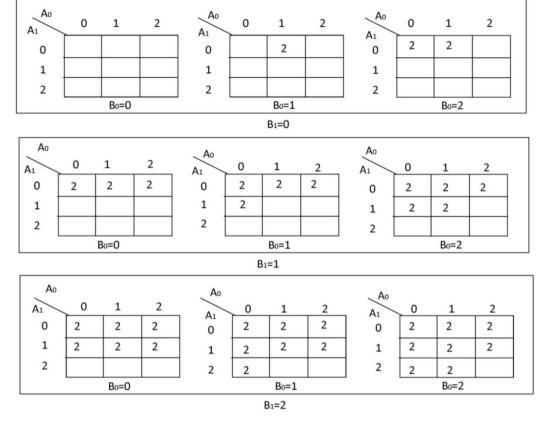

| Figure 3.20 | (a) Logic level diagram for EQ generator of comparator module                       |    |

|-------------|-------------------------------------------------------------------------------------|----|

| Figure 3.20 | (b) Logic level diagram for LE and GR generator of comparator module                |    |

| Figure 3.21 | Block diagram of the exclusive-OR module                                            |    |

| Figure 3.22 | Logic level diagram of THA_SUM block of exclusive-OR module                         |    |

| Figure 3.23 | Block diagram of multiplier module                                                  |    |

| Figure 3.24 | K-map of 1-bit ternary multiplier                                                   |    |

| Figure 3.25 | Logic level diagram of 1-bit ternary multiplier                                     | 64 |

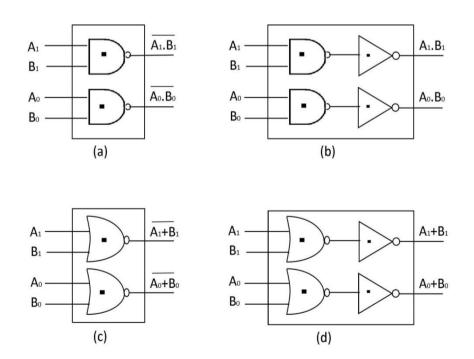

| Figure 3.26 | Logic level diagram of (a) T-NAND (b) T-AND (c) T-NOR (d) T-OR modules              | 64 |

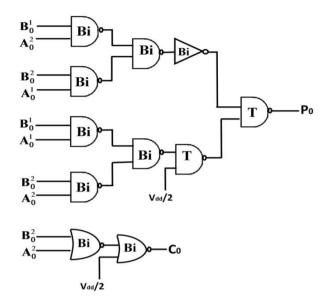

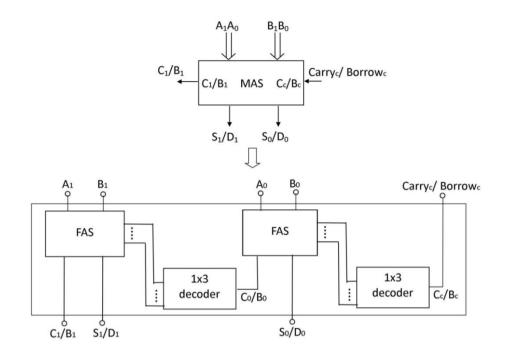

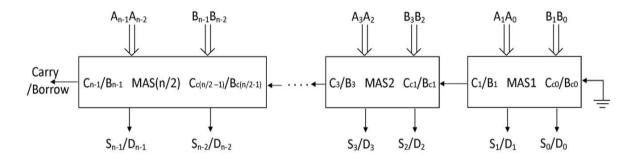

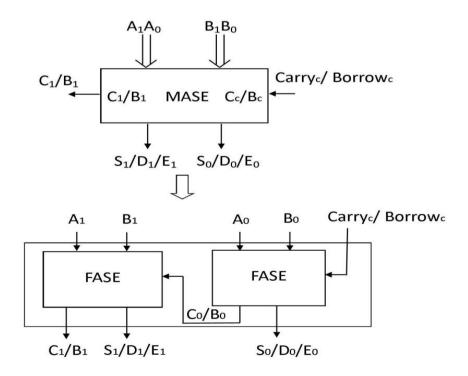

| Figure 3.27 | Block diagram of 2-bit HO-TALU slice                                                | 65 |

| Figure 3.28 | Block diagram for modified adder-subtractor (MAS)                                   | 66 |

| Figure 3.29 | Cascaded configuration of modified adder-subtractor (MAS) for N-bit HO-TALU         |    |

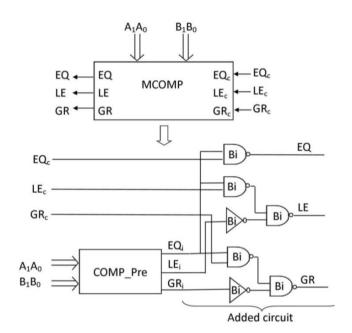

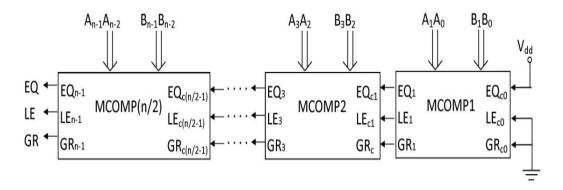

| Figure 3.30 | Logic diagram for modified comparator (MCOMP)                                       | 67 |

| Figure 3.31 | 3.31 Cascaded configuration of modified comparator (MCOMP) for N-bit HO-TALU        |    |

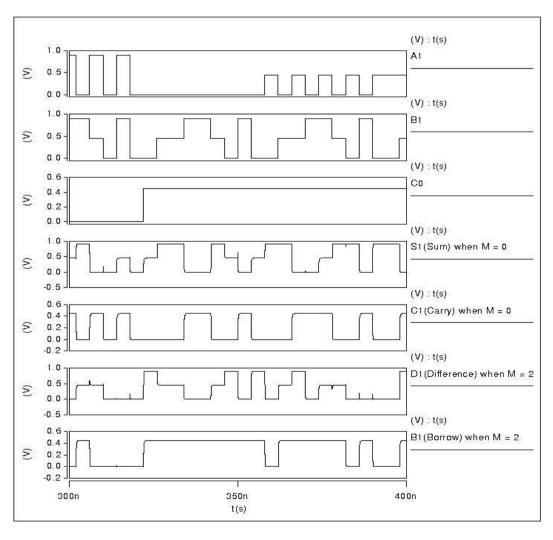

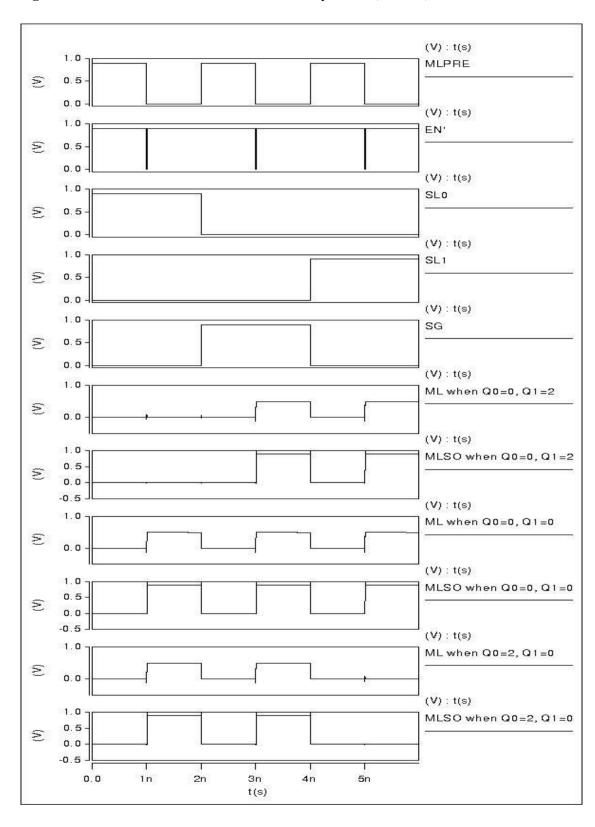

| Figure 3.32 | Transient waveform of full adder-subtractor (FAS)                                   | 69 |

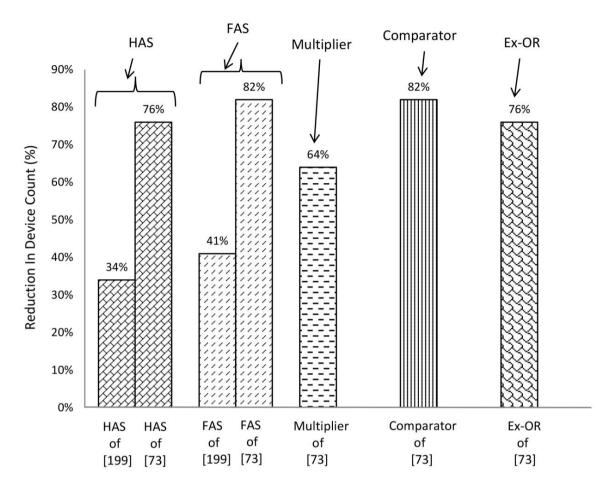

| Figure 3.33 | Comparison of ternary circuits based on device count                                | 71 |

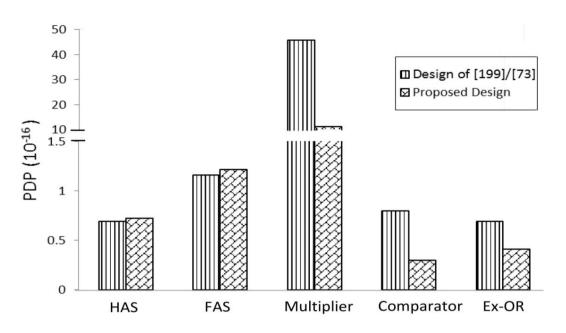

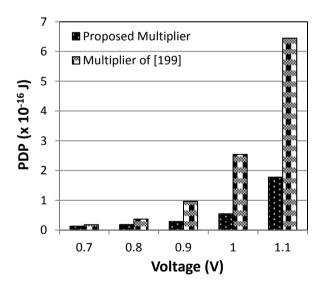

| Figure 3.34 | Comparison of HO-TALU sub modules based on PDP                                      | 73 |

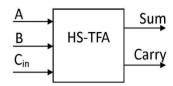

| Figure 4.1  | (a) Pin diagram of high speed ternary full adder (HS-TFA)                           | 76 |

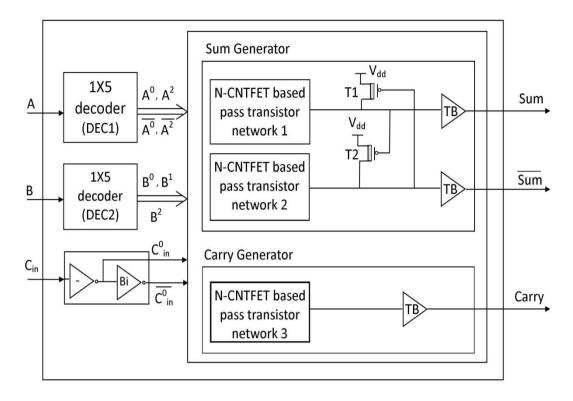

| Figure 4.1  | (b) Block diagram of high speed ternary full adder (HS-TFA)                         | 77 |

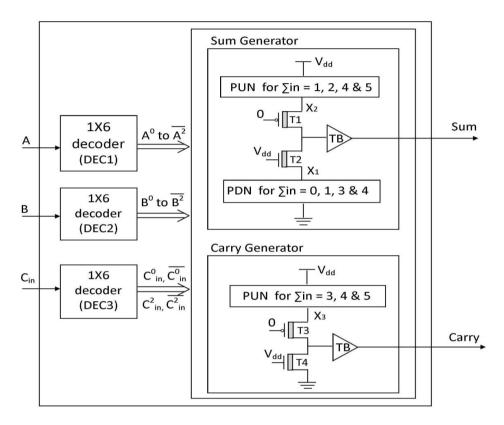

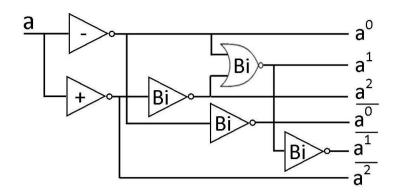

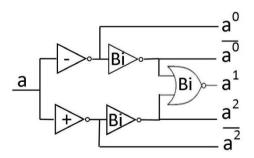

| Figure 4.2  | Logic level diagram of 1-to-6-line ternary decoder                                  | 80 |

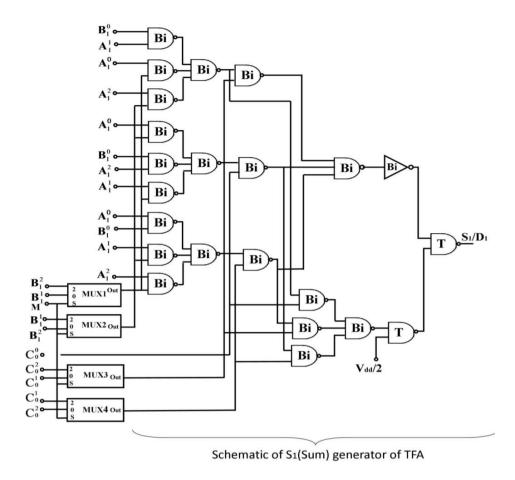

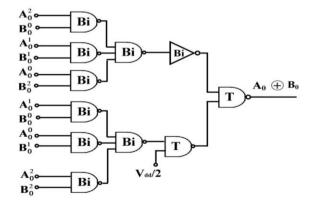

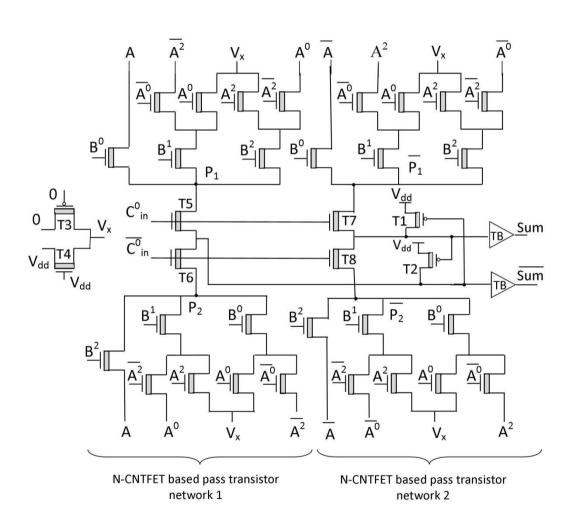

| Figure 4.3  | (a) Schematic diagram for Sum generator of high speed ternary full adder (HS-TFA)   | 81 |

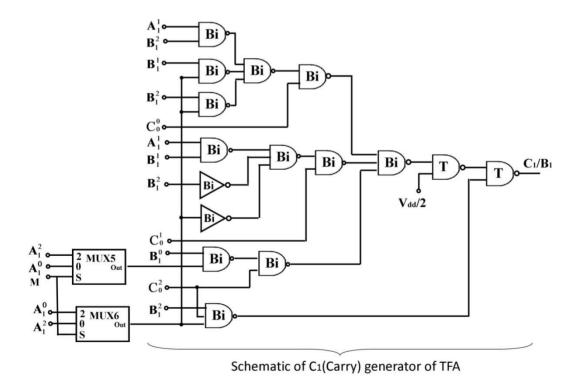

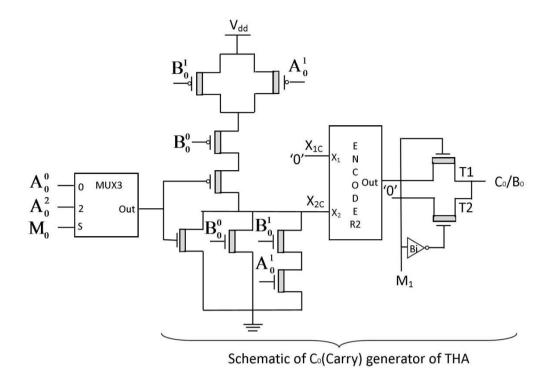

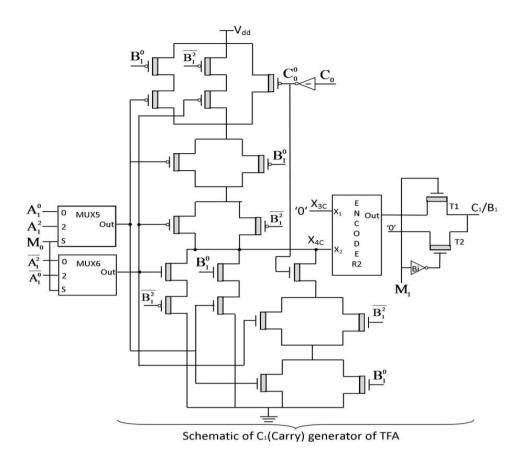

| Figure 4.3  | (b) Schematic diagram for Carry generator of high speed ternary full adder (HS-TFA) | 81 |

| Figure 4.4  | Schematic diagram of ternary buffer (TB)                                            | 82 |

| Figure 4.5  | (a) Pin diagram of low power ternary full adder (LP-TFA)                            | 82 |

| Figure 4.5  | (b) Block diagram of low power ternary full adder (LP-TFA)                          | 83 |

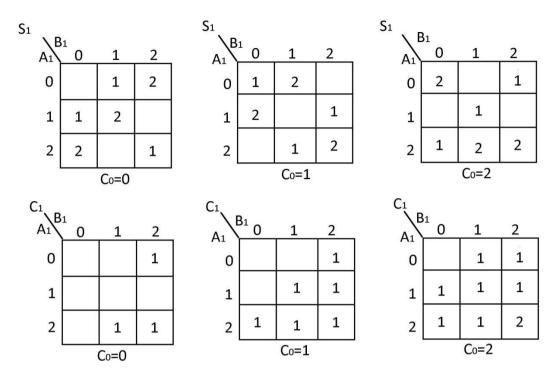

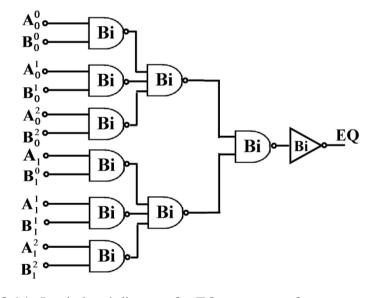

| Figure 4.6  | K-map of low power ternary full adder (LP-TFA) for (a) Sum (b) Carry                | 84 |

| Figure 4.7  | Schematic diagram of a 1-to-5-line ternary decoder                                  | 84 |

| Figure 4.8  | (a) Schematic diagram of Sum generator of low power ternary full adder (LP-TFA)     | 85 |

| Figure 4.8  | (b) Schematic diagram of Carry generator of low power ternary full adder (LP-TFA)   | 86 |

| Figure 4.9  | (a) Pin diagram of dynamic ternary full adder (DTFA)                                | 87 |

| Figure 4.9  | (b) Block diagram of dynamic ternary full adder (DTFA)                              | 88 |

| Figure 4.10 | (a) Schematic diagram of Sum generator of dynamic ternary full adder (DTFA)         |    |

| Figure 4.10 | (b) Schematic diagram of Carry generator of dynamic ternary full adder (DTFA)       | 89 |

| Figure 4.11 | Schematic diagram of 1-to-4-line ternary decoder                                                          |     |

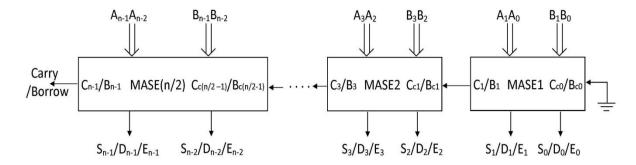

|-------------|-----------------------------------------------------------------------------------------------------------|-----|

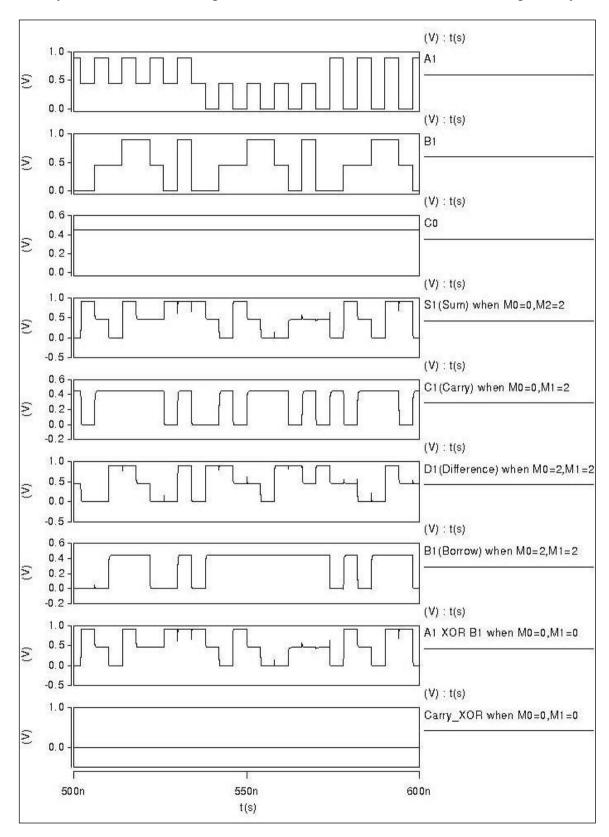

| Figure 4.12 | Transient waveform of high speed ternary full adder (HS-TFA)                                              |     |

| Figure 4.13 | 3 (a) Delay versus output load capacitor plot for five ternary full adder (TFA) designs                   |     |

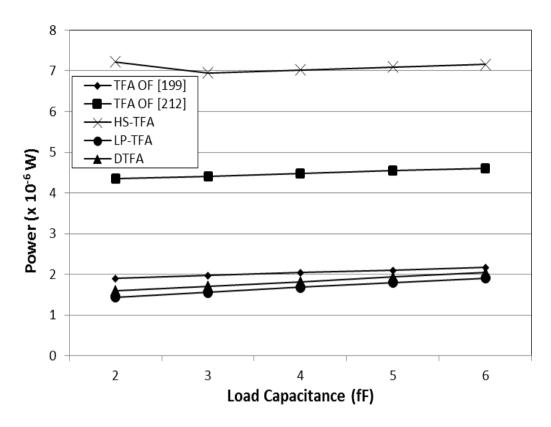

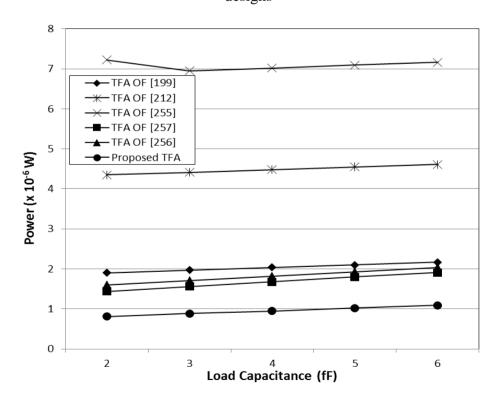

| Figure 4.13 | (b) Power consumption versus output load capacitor plot for five ternary full adder (TFA) designs         |     |

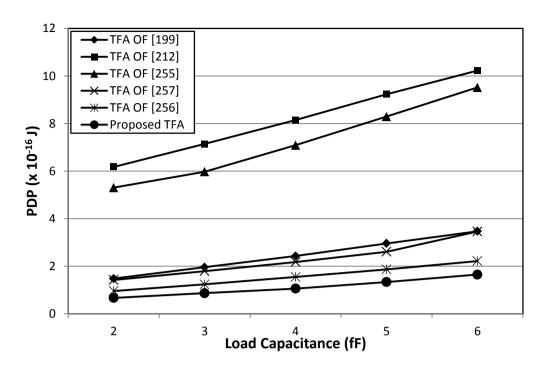

| Figure 4.13 | (c) Power-delay product (PDP) versus output load capacitor plot for five ternary full adder (TFA) designs |     |

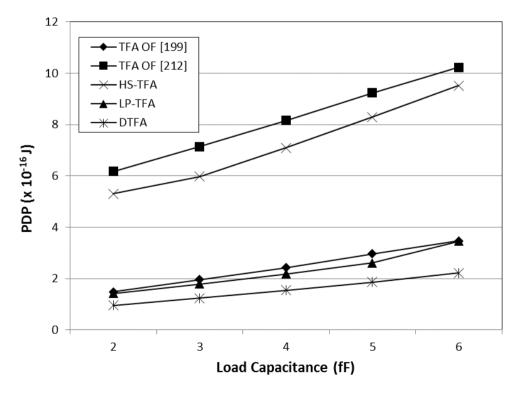

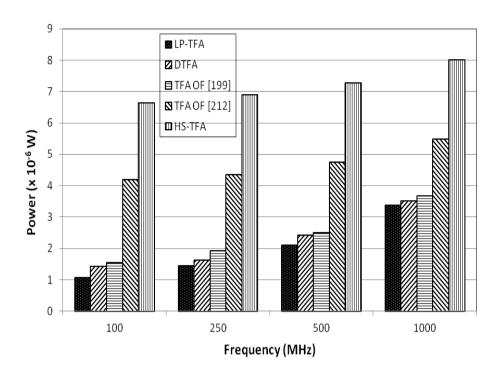

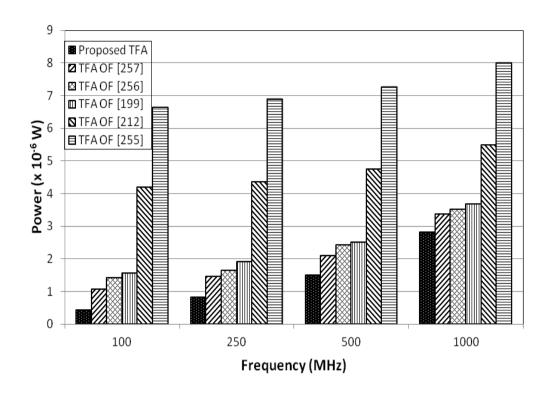

| Figure 4.14 | Power consumption versus operating frequency plot for five ternary full adder (TFA) designs               |     |

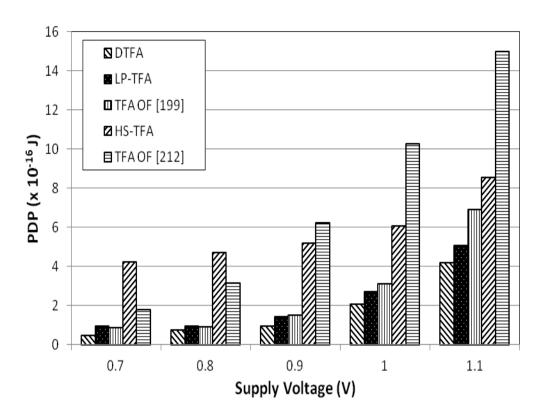

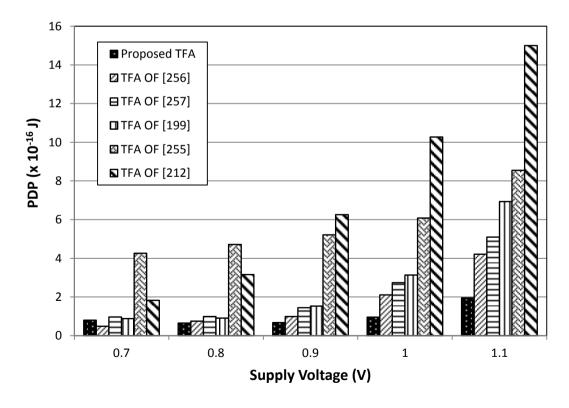

| Figure 4.15 | Power-delay product (PDP) versus supply voltage plot for five ternary full adder (TFA) designs            |     |

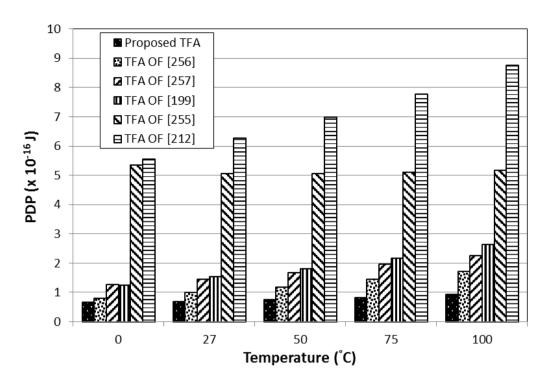

| Figure 4.16 | 1.16 Power-delay product (PDP) versus temperature plot for five ternary full adder (TFA) designs          |     |

| Figure 4.17 | 1-bit comparator (a) pin diagram (b) block diagram                                                        | 99  |

| Figure 4.18 | 8 K-map for 1-bit comparator                                                                              |     |

| Figure 4.19 | 4.19 Schematic diagram of 1-bit comparator                                                                |     |

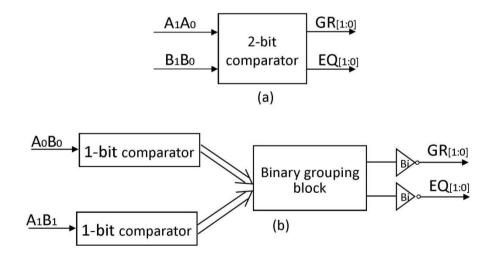

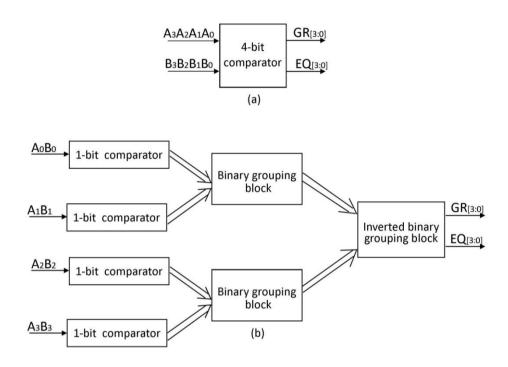

| Figure 4.20 | 2-bit comparator (a) pin diagram (b) block diagram                                                        | 101 |

| Figure 4.21 | 4-bit comparator (a) pin diagram (b) block diagram                                                        |     |

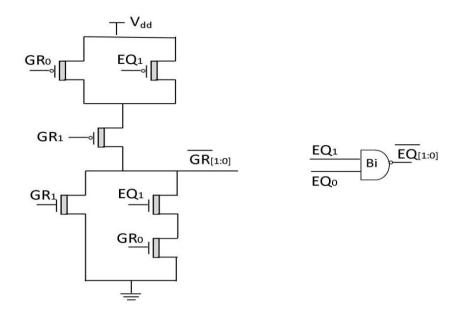

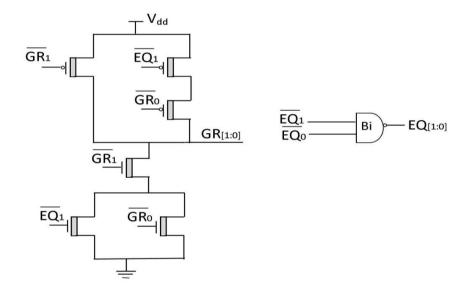

| Figure 4.22 | (a) Schematic diagram of binary grouping block                                                            | 103 |

| Figure 4.22 | (b) Schematic diagram of inverted binary grouping block                                                   | 103 |

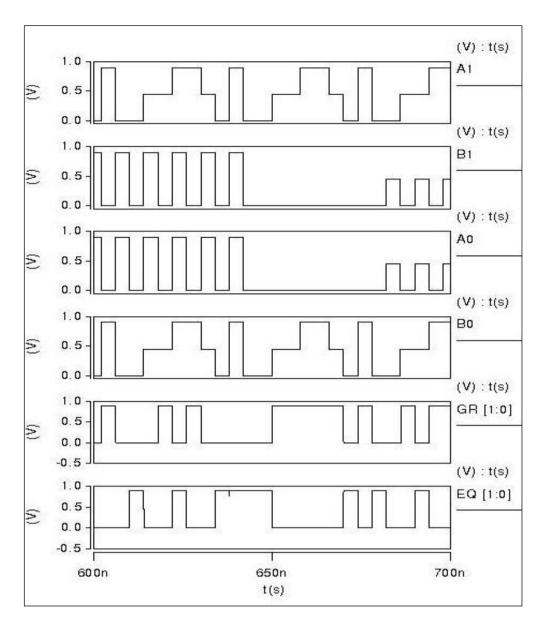

| Figure 4.23 | Transient waveform of 2-bit comparator                                                                    | 105 |

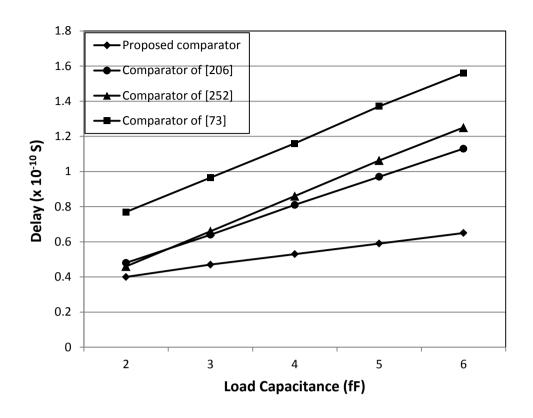

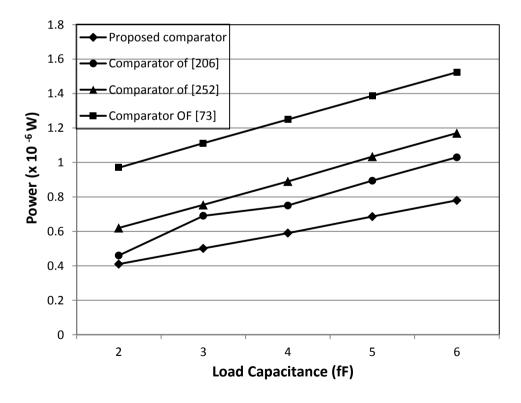

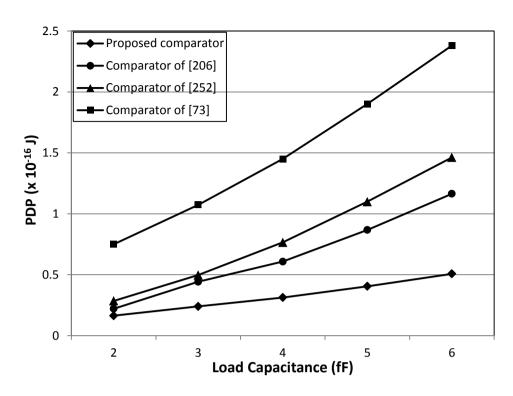

| Figure 4.24 | (a) Delay versus output load capacitor plot for 2-bit comparator circuits                                 | 107 |

| Figure 4.24 | (b) Power consumption versus output load capacitor plot for 2-bit comparator circuits                     | 107 |

| Figure 4.24 | (c) Power-delay product (PDP) versus output load capacitor plot for 2-bit comparator circuits             | 108 |

| Figure 4.25 | 25 Power consumption versus operating frequency plot for 2-bit comparator circuits                        |     |

| Figure 4.26 | 4.26 Power-delay product (PDP) versus supply voltage plot for 2-bit comparator circuits                   |     |

| Figure 4.27 | Power-delay product (PDP) versus temperature plot for 2-bit comparator circuits                           | 109 |

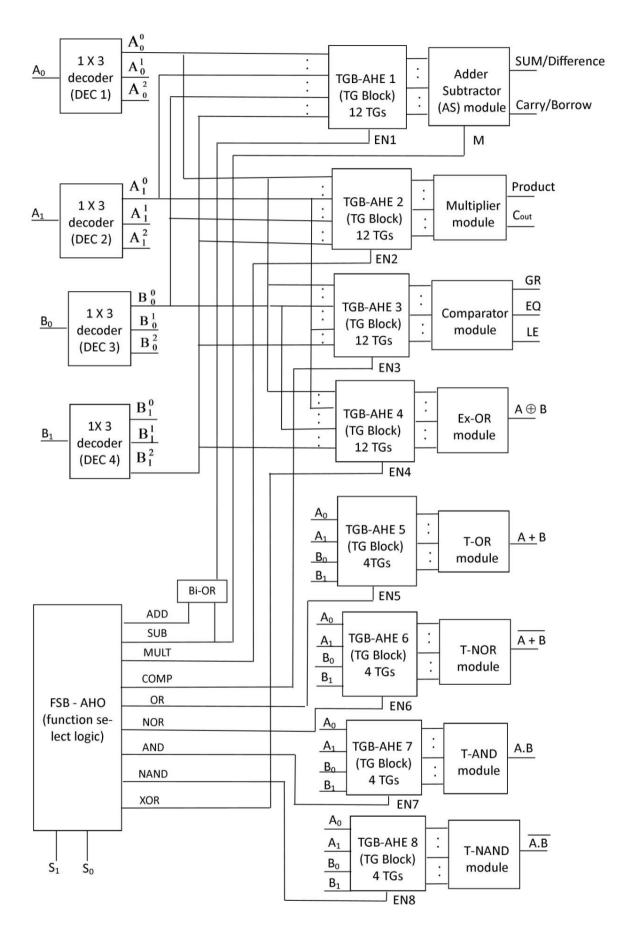

| Figure 5.1  | (a) Pin diagram of 2-bit PO-TALU                                                                          | 112 |

| Figure 5.1  | (b) Architecture of 2-bit PO-TALU                                                                         | 113 |

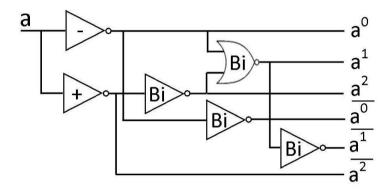

| Figure 5.2  | Logic level diagram of 1-to-6-line ternary decoder                                                        | 114 |

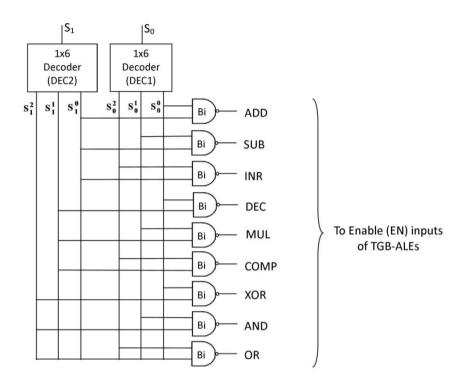

| Figure 5.3  | Logic level diagram of function select logic block with active low outputs (FSB-ALO)                      |     |

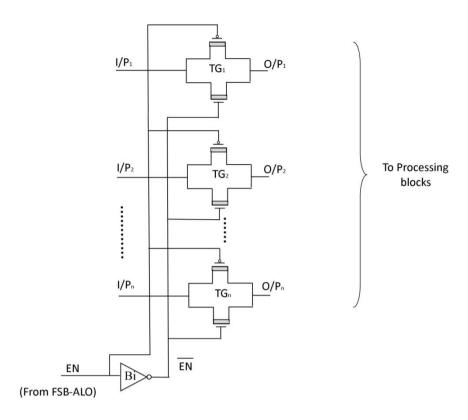

| Figure 5.4  | Logic level diagram of transmission gate block with active low enable (TGB-ALE)                           | 117 |

| Figure 5.5  | Ternary function implementation for 2-bit PO-TALU                                                         | 118 |

| Figure 5.6  | Design of ternary encoder                                                                                |     |

|-------------|----------------------------------------------------------------------------------------------------------|-----|

| Figure 5.7  | Block diagram of adder-subtractor-exclusive-OR (ASE) module                                              |     |

| Figure 5.8  | (a) Schematic diagram of S0/D0/E0 generator of half adder-subtractor-exclusive-OR (HASE)                 |     |

| Figure 5.8  | (b) Schematic diagram of $C_0/B_0$ generator of half adder-subtractor-exclusive-OR (HASE)                |     |

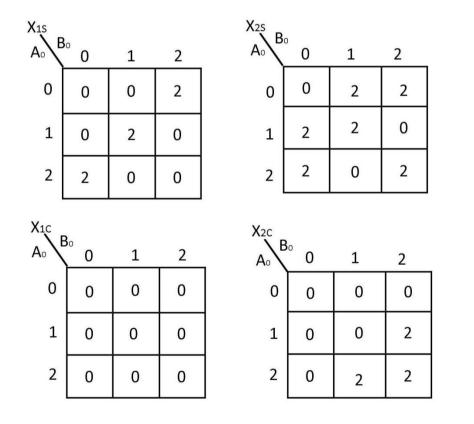

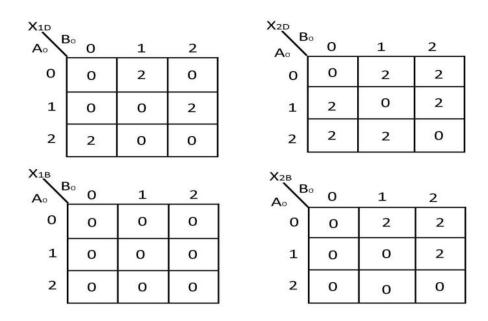

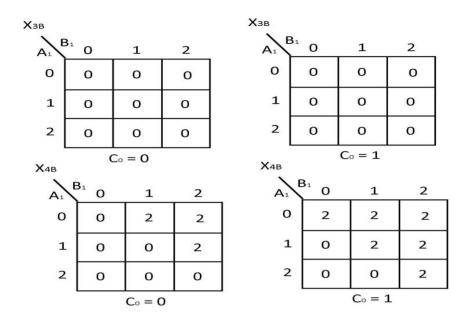

| Figure 5.9  | K-maps of $X_{1S}$ , $X_{2S}$ , $X_{1C}$ and $X_{2C}$ for ternary half adder (THA)                       |     |

| Figure 5.10 | K-maps of $X_{1D}$ , $X_{2D}$ , $X_{1B}$ and $X_{2B}$ for ternary half subtractor (THS)                  |     |

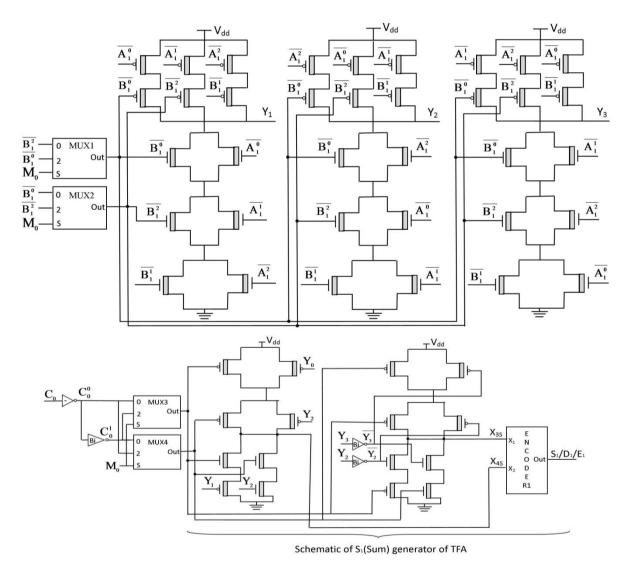

| Figure 5.11 | (a) Schematic diagram of S1/D1/E1 generator of full adder-subtractor-exclusive-OR (FASE)                 |     |

| Figure 5.11 | (b) Schematic diagram of $C_1/B_1$ generator of full adder-subtractor-exclusive-OR (FASE)                |     |

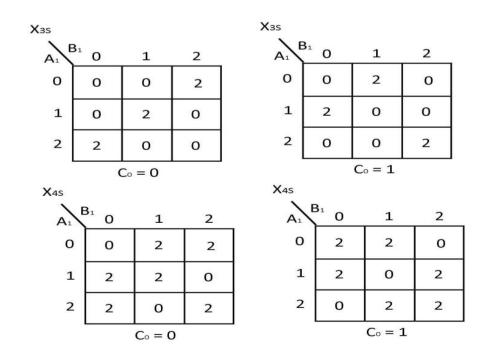

| Figure 5.12 | (a) K-maps of $X_{3S}$ and $X_{4S}$ for ternary full adder (TFA)                                         | 126 |

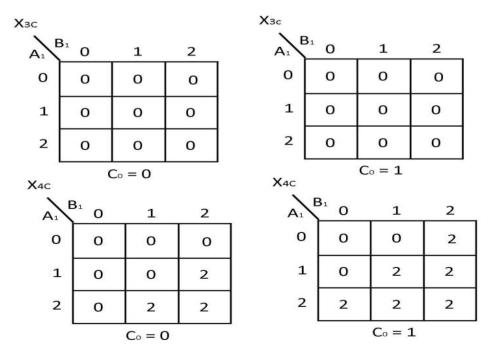

| Figure 5.12 | (b) K-maps of $X_{3C}$ and $X_{4C}$ for ternary full adder (TFA)                                         | 127 |

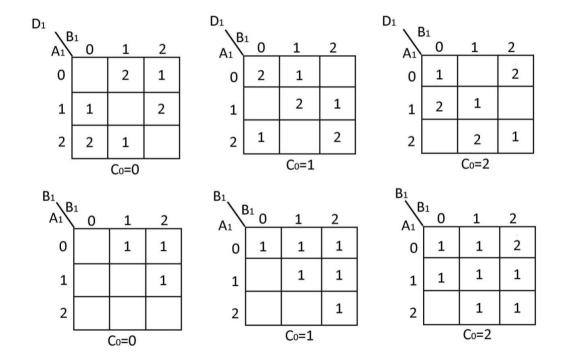

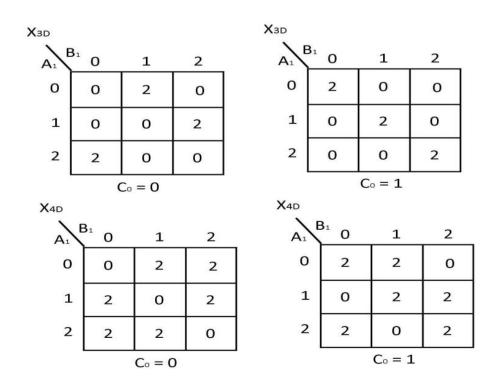

| Figure 5.13 | (a) K-maps of $X_{3D}$ and $X_{4D}$ for ternary full subtractor (TFS)                                    | 129 |

| Figure 5.13 | (b) K-maps of $X_{3B}$ and $X_{4B}$ for ternary full subtractor (TFS)                                    | 130 |

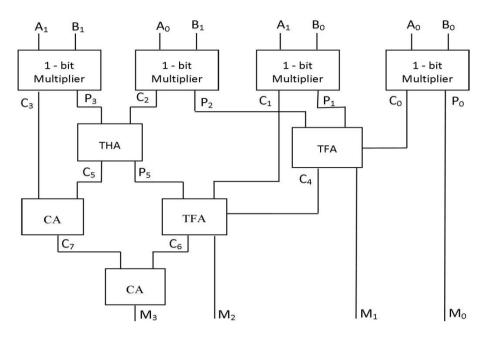

| Figure 5.14 | Block diagram of multiplier functional module                                                            | 131 |

| Figure 5.15 | Logic level diagram of carry add (CA)                                                                    | 131 |

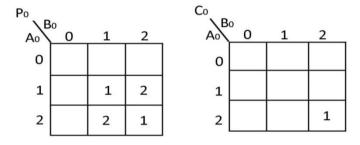

| Figure 5.16 | K-maps of $X_{1CA}$ and $X_{2CA}$ for carry add (CA)                                                     | 132 |

| Figure 5.17 | (a) Schematic diagram for P <sub>0</sub> (Product) generator of ternary 1-bit multiplier                 | 132 |

| Figure 5.17 | (b) Schematic diagram for C <sub>0</sub> (Carry) generator of ternary 1-bit multiplier                   |     |

| Figure 5.18 | K-maps of $X_{1P0}$ , $X_{2P0}$ , $X_{1C0}$ and $X_{2C0}$ for ternary 1-bit multiplier                   | 133 |

| Figure 5.19 | Pin diagram of 2-bit PO-TALU Slice                                                                       | 135 |

| Figure 5.20 | Block diagram for modified adder-subtractor-exclusive-OR (MASE)                                          |     |

| Figure 5.21 | ure 5.21 Cascaded configuration for modified adder-subtractor-exclusive-OR (MASE) of N-bit PO-TALU       |     |

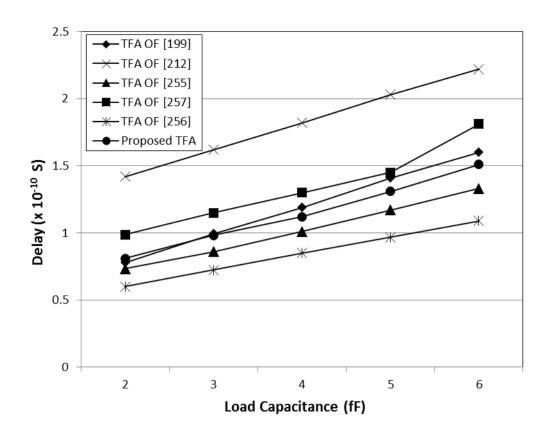

| Figure 5.22 | 22 Transient waveform of full adder-subtractor-exclusive-OR (FASE)                                       |     |

| Figure 5.23 | 5.23 (a) Delay versus output load capacitor plot for six ternary full adder (TFA) designs                |     |

| Figure 5.23 | 5.23 (b) Power consumption versus output load capacitor plot for six ternary full adder (TFA) designs    |     |

| Figure 5.23 | (c) Power-delay product (PDP) versus output load capacitor plot for six ternary full adder (TFA) designs | 142 |

| Figure 5.24 | 4 Power consumption versus operating frequency plot for six ternary full adder (TFA) designs             |     |

| Figure 5.25 | 25 Power-delay product (PDP) versus supply voltage plot for six ternary full adder (TFA) designs         |     |

| Figure 5.26 | Power-delay product (PDP) versus temperature plot for six ternary full adder (TFA) designs               | 144 |

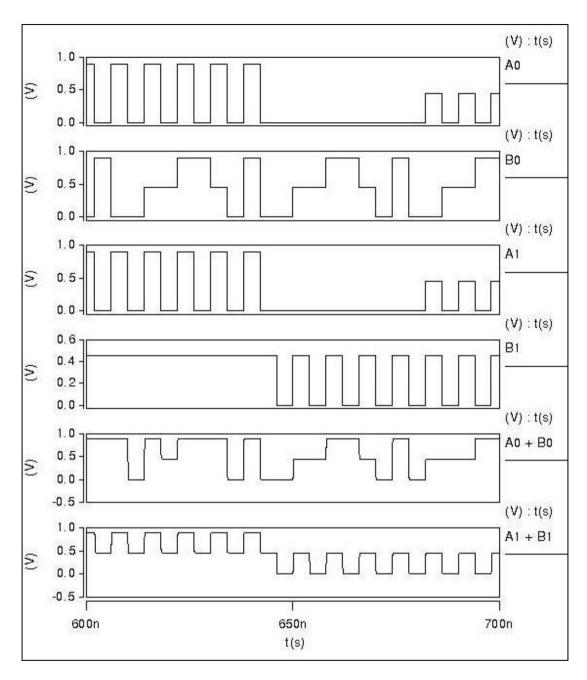

| Figure 6.1  | Schematic diagram of 9T binary CAM (BCAM) cell                                                           | 146 |

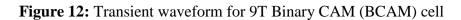

| Figure 6.2 | Schematic diagram of 16T ternary CAM (TCAM) cell        | 148 |

|------------|---------------------------------------------------------|-----|

| Figure 6.3 | Schematic diagram of 11T three-valued CAM (3CAM) cell   | 150 |

| Figure 6.4 | Schematic diagram for current race sensing scheme [232] | 153 |

| Figure 6.5 | Transient waveform of 11T three-valued CAM (3CAM) cell  | 154 |

### **LIST OF ABBREVIATIONS**

3CAM Three-valued Content Addressable Memory

AHAL Active High/Active Low

ALU Arithmetic and Logic Unit

AS Adder-Subtractor

ASE Adder-Subtractor-Exclusive-OR

BCAM Binary Content Addressable Memory

BTA Balanced Ternary Adder

CA Carry-Add

CAM Content Addressable Memory

CMOS Complementary Metal Oxide Semiconductor

CNT Carbon Nanotube

CPL Complementary Pass-transistor Logic

CPU Central Processing Unit

CNTFET Carbon Nanotube Field Effect Transistor

DECMOS Depletion Enhancement Complementary Metal Oxide Semiconductor

DRAM Dynamic Random Access Memory

DTFA Dynamic Ternary Full Adder

FA Full Adder

FAS Full Adder-Subtractor

FASE Full Adder- Subtractor-Exclusive-OR

FSB-AHO Function Selection logic Block with Active High Outputs

FSB-ALO Function Select logic Block with Active Low Outputs

HA Half Adder

HAS Half Adder-Subtractor

HASE Half Adder- Subtractor-Exclusive-OR

HO-TALU Hardware Optimized Ternary ALU

HS-TFA High Speed Ternary Full Adder

IC Integrated Circuit

LP-TFA Low Power Ternary Full Adder

LSB Least Significant Bit

MAS Modified Adder-Subtractor

MASE Modified Adder-Subtractor-Exclusive-OR

M-CNTFET MOSFET-like CNTFET

MCOMP Modified Comparator

MSB Most Significant Bit

MVL Multiple-Valued Logic

NTI Negative Ternary Inverter

NTNAND Negative Ternary NAND

NTNOR Negative Ternary NOR

NWFET Nanowire Field Effect Transistor

Pd Palladium

PDN Pull-Down Network

PDP Power-Delay Product

PO-TALU Power Optimized Ternary ALU

PTI Positive Ternary Inverter

PTNAND Positive Ternary NAND

PTNOR Positive Ternary NOR

PU Pull-Up

PUN Pull-Up Network

QAT Quasi-Adiabatic Ternary

QoS Quality of Service

RBSD Redundant Binary Signed Digit

RSFG Recharged CMOS Semi Floating Gate

SB Schottky Barrier

SB-CNTFET Schottky Barrier CNTFET

Si Silicon

SNM Static Noise Margin

SRAM Static Random Access Memory

STDL Simple Ternary Differential Logic

STI Standard Ternary Inverter STNAND Standard Ternary NAND STNOR Standard Ternary NOR

SUS-LOC Supplementary Symmetrical Logic Circuit Structure

SWCNT Single Walled Carbon Nanotube

TALU Ternary ALU

TAND Ternary AND

TB Ternary Buffer

TC Two's complement

TCAM Ternary Content Addressable Memory

T-CNTFET Tunneling CNTFET

TDDL Ternary Dynamic Differential Logic

TFA/S Ternary Full Adder/ Subtractor

THA/S Ternary Half Adder / Subtractor

TGB-AHE Transmission Gate Block with Active High Enable

TGB-ALE Transmission Gate Block with Active Low Enable

TG Transmission Gate

TOR Ternary OR

### 1.1 Background

Since the introduction of integrated circuits (ICs) in 1952 [1] and the realization of the first IC at Texas Instruments in 1958 [2], the last five decades witnessed a phenomenal growth of Silicon (Si) based microelectronics industry. Rapid advancements in this industry are achieved mainly due to continuous scaling or miniaturization of all electronics components (passive and active) integrated on the ICs. IC miniaturization techniques sustained the scaling of complementary metal oxide semiconductor (CMOS) devices and metallic interconnects that used for the connection of device terminals with power supply voltage [3]. Miniaturization in IC technology makes less testing requirements at system level, achieves significant cost savings and faster switching, and leads to compact, low power and highly reliable designs. As a consequence, it provides faster and improved ICs for high definition digital television, digital receiver, DSP, high speed microprocessor, communication, business transactions, traffic control, space guidance, medical treatment, weather monitoring, internet, and many other commercial, industrial, and scientific enterprises [4]. Further, according to Moore's law, the number of transistors that can be manufactured on a single chip is expected to grow exponentially with time [5]. This prediction turned out to be true as illustrated in Figure 1.1 [6-7]. Figure 1.1 plots the decrement in number of transistors integrated on a single microprocessor chip as a function of time. As can be observed, integration density doubles in every 18 months. To meet the IC density predicted by Moore's law, technology scaling has been pursued aggressively until today since 1970s. The gate length of a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is scaled down by a factor of 0.7 in every 2 years, as shown in Figure 1.1. Since 2006, at 65 nm technology node the gate length of a MOSFET has arrived at deep sub-micron/nano range. Today, technology node is 20 nm, and 14 nm has been expected as feature size in the near future [7-8].

**Figure 1.1:** Evolution of MOSFET gate length (filled blue circles and open blue circles for ITR targets) and integration complexity of microprocessor chip (red stars), as a function of time [7].

Further, scaling down the gate length of CMOS technology in nano ranges results in various critical challenges and reliability issues. One of the issues is increased leakage current which occurs due to various quantum mechanical tunneling including band-to-band tunneling, direct gate oxide tunneling, and source to drain tunneling [9]. Other issues are large process variations, the effects of crystal misalignments, the randomness of discrete doping, and increment of interface scatterings since the mean free path of electrons becomes comparable to component dimensions [8-9]. These device-level effects cause the current-voltage (I-V) characteristics to be substantially different from well-tempered MOSFET. As a result, researchers have major concerns regarding further improving device performance by scaling down the feature size of MOSFET. Besides, circuit level effects such as short channel effects, increment in the resistance of metallic on-chip interconnects and power dissipation will surely reduce the suitability of MOSFET for advanced applications in time to come [10-13].

Researchers developed double-gate MOSFETs and FinFET/tri-gate devices [14-15] to reduce short channel effects. In these devices, gate is placed on two/three sides of the channel, which results in better control on the channel and considerable reduction in drain to source sub-threshold leakage current.

Researchers also have begun the exploration of new devices and channel material in sub10 nm technology node, which could be the possible alternatives to Si-CMOS. Based on

ITRS [16], some of the emerging devices which have the capabilities to replace Sitechnology in post Si era are nanowire field effect transistor (NWFET) [17], III-V

compound semiconductor field effect transistor [18-21], graphene field effect transistor

[22-24], and carbon nanotube field effect transistor (CNTFET) [25-27].

NWFET uses a semiconducting nanowire having diameter around 0.5 nm as a channel material. This nanowire can be made from Si, germanium, III-V, In<sub>2</sub>O<sub>3</sub>, ZnO or SiC semiconductors [28-29]. The schematic view of silicon based NWFET is shown in Figure 1.2 [30]. The main advantages offered by NWFET due to use of small diameter are 1-D conduction and minimized short channel effects. The basic challenge faced by this device is fabrication of diffused P-N junctions. For this, current technology utilizes metal drain source junctions which result in ambipolar conduction [31] but produces a large OFF state current.

**Figure 1.2:** Schematic view of Si based NWFET [30]

In the III-V compound semiconductor FET, III-V compound semiconductor like InSb, InAs, InGaAs is used as a channel material. These materials provide high mobility of carriers in the channel. As a consequence, these III-V compound semiconductor FETs are able to deliver three times higher performance with same power consumption or they can reduce power by one tenth with same performance, compared to Si-MOSFETs [32]. The schematic view of an n-type transistor is shown in Figure 1.3 where ZrO<sub>2</sub> and InGaAs are used as the gate dielectric and the channel material, respectively [33]. In this device, the carrier mobility is found to be 3000 cm<sup>2</sup>/V-S. Two major challenges faced by III-V

compound semiconductor FET are lower bandgap of III-V material which results in excessive leakage and large static power consumption, and formation of a compatible high-k dielectric interface [34] which is necessary in the electrostatic control of the device.

**Figure 1.3:** Schematic view of n-type III-V compound semiconductor FET [33]

The graphene nanoribbon transistor uses a monolayer of carbon atoms, packed into a 2-D honeycomb lattice as the channel material. Figure 1.4 shows the schematic view of this device which is fabricated with nanoribbons having a width around 2 nm [22]. The use of graphene as channel material provides very high mobility (15,000 cm²/V-S) resulting in fast switching, monolayer thin body for optimum electrostatic scaling, and excellent thermal conductivity [35]. Consequently, graphene nanoribbon transistor is capable to deliver 100 or 1000 times higher performance than Si-MOSFET [36]. The main challenge faced by this device is the comparatively low I<sub>ON</sub>/I<sub>OFF</sub> ratio (~7) [37], which cause an enormous amount of energy in the integrated circuit made of billions of graphene transistors [38].

**Figure 1.4:** Schematic view of graphene nanoribbon transistor [22]

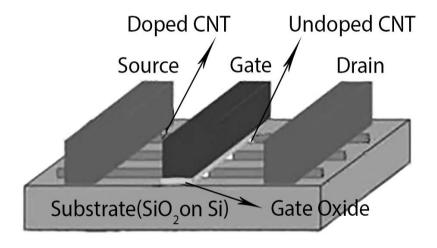

CNTFET uses a single or an array of semiconducting single wall carbon nanotubes (SWCNTs) as a channel material. The gate electrode is placed above the CNT channel and separated from it by a thin layer of gate dielectric. The schematic view of CNTFET is shown in Figure 1.5, where an array of four SWCNTs is used for channel [39]. CNTFET could be more achievable and promising candidate to extend or complement traditional Si device due to its excellent properties such as ballistic transport operation [40], high carrier mobility (10<sup>3</sup>-10<sup>4</sup> cm<sup>2</sup>/V-S) [41], easy integration of high-k dielectric material [42] (other than SiO<sub>2</sub>) resulting in better gate electrostatics, strong chemical bonding, high thermal conductivity (1700-3000 W/mK), high chemical stability [41], and better matching of P and N-type CNTFETs which simplifies transistor sizing in complex circuits.

Figure 1.5: Schematic view of CNTFET [39]

The first CNT-based transistor is announced by Martel et al. [43] & Tans et al. [44] in 1998. After that, significant advancements were achieved in the fabrication of CNT-based devices and circuits. Based on CNTFETs, some state-of-the-art designs such as logic gates, five-stage ring oscillator fabricated along a single CNT, a capacitive sensor interface circuit, a percolation-transport-based decoder, stand-alone circuit elements such as half-adder sum generators, D-latches and static random access memory (SRAM) cells have been fabricated [44-50]. In 2006, IBM demonstrated the first IC built using SWCNTs [51]. Cao et al. [52] announced that they made medium scale IC using CNTFETs on a thin plastic substrate. Recently, Shulaker et al. [53] used the CNT imperfection-immune methodology presented in [54-55] to fabricate first CNT computer entirely using CNTFETs. Similar to the first

silicon based computer, the CNT computer is a synchronous digital system which runs stored programs and is programmable. The operating system of this computer achieves multitasking by executing a counting program and an integer-sorting program concurrently. Although the operating frequency of the CNT computer is reported to be 1 KHz only due to academic experimental limitations and capacitive loading introduced by the measurement setup, this demonstration is an important milestone in the development of complex and highly energy-efficient CNT based electronic system. At present, the fundamental challenges faced by CNT technology are the CNT misalignment and unwanted growth of metallic tubes [56].

The above mentioned emerging devices have the potential to become the successor of Si-CMOS in near future. CNTFET and NWFET are 1-D devices, graphene nanoribbon FET is a 2-D device, and the III-V compound semiconductor FET is a 3-D device. 1-D devices provide ballistic transport operation without any scattering and therefore, attain superior performance in comparison with 2-D and 3-D devices. CNTFET provides easy integration of high-k dielectric material due to the absence of dangling bonds, which in turn results in lower sub-threshold slopes and lower OFF current. As previously mentioned, the mobility of carriers in NWFET, graphene FET, III-V semiconductor FET and CNTFET is higher than Si-MOSFET, which results in higher carrier velocities and fast switching. In CNTFET and graphene transistors, the carrier mobility is in the same order of magnitude (10<sup>3</sup>-10<sup>4</sup>cm<sup>2</sup>/V-S) which makes them promising candidates for future high speed circuits. Furthermore, based on ITRS 2009 [16], CNTFET and graphene transistors demonstrated the highest possibility to become a part of future devices. When this research work begun, R&D in CNTFET was ahead compared to that of graphene transistor. Therefore, in this thesis, CNTFET-based circuits are targeted.

### 1.2 Motivation and Objectives

As described earlier, the scaling of CMOS technology has been pursued aggressively over the last few decades to integrate more number of transistors on a single chip. However, material properties are directly related to dimension. For traditional Si-based devices, as the physical gate length is reached to nanoscale range, many device-level effects (such as increased leakage current, variations in doping, larger process variations and reduced gate control) are exhibited with MOSFETs [9]. To overcome these issues, researchers are exploring new alternatives of Si-CMOS process. CNTFET has proved to be a promising

alternative due to its various superior properties such as unique 1-D band structure, ballistic transport operation and low OFF-current [40-42], together with its resemblance to MOSFET in terms of intrinsic attributes. Thereby, CNTFET is a promising device which enables high performance and low power designs for the next generation of modern electronics [57-58].

Further, digital system design has traditionally been associated with the binary logic where digital computations are performed on two possible logic values that are '0' and '1' in the Boolean space. Since the world around us is multi-valued, many practical applications such as robotics, process control and decision support systems need more than two-valued logic for efficient and optimum solution. In 1921, Post [59] demonstrated a definition of multi-valued logic (MVL) as an extension of conventional binary logic. In 1964, Alexander et al. [60] announced that the most efficient radix for realization of switching circuits is a natural base (e = 2.7183) which shows that the best integer radix is three rather than two. In 1970's, MVL-based system implementations were reported in the technical literature and referred as voltage mode ternary circuits [61-63].

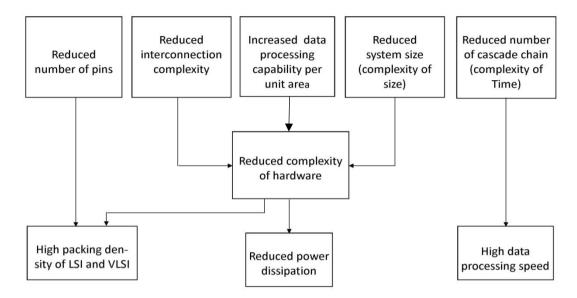

Over the last couple of decades, three-valued or ternary logic has attracted considerable interest because of several advantages with respect to the binary logic in design of digital VLSI circuits. Figure 1.6 summaries the advantages offered by ternary logic [61]. This logic reduces chip area occupied by the interconnection wires and functional units in VLSI integration. Ternary signals carry more information on a single wire, thus reduces number of wires and IC pins required for the same range of data. This decreases number of interconnects and consequently, leads to increased space between any two wires without any increment of total silicon area. This also decreases resistance and capacitances associated with interconnect and contacts, and as a consequence, ternary logic achieves simplicity and increased energy efficiency in digital design [62]. Furthermore, other added advantages are less complex error detection/error correction code and high speed serial/ serial-parallel arithmetic operation. For example, 14-bit binary addition can be obtained by a 9-bit ternary adder which reduces number of ripple carriers to approximately half with respect to its binary implementation and thus, increase the speed of electronic circuits approximately by the factor of two. Raychowdhury and Roy [64] demonstrated that an efficient MVL implementation of a signed 32-bit multiplier is able to reduce both chip area and power by more than 50% in comparison to its fastest binary counterpart. In [65], MVL blocks have been added with binary logic ICs to improve the overall performance of system. Similarly, the advantages of ternary logic have been confirmed in a number of the applications

including memory, communication, machine learning, fuzzy logic, artificial intelligence, robotics, data mining, digital signal processing, digital control systems and image processing etc. [66].

Figure 1.6: Advantages of ternary logic circuits [61]

Voltage-mode MVL circuit processes information based on voltage levels. The best way to design and implement these circuits is using multi-threshold method [64]. In CMOS technology, multi-threshold design relies on body effects where different bias voltages are applied to the base or buck terminal of the transistors. To get these bias voltages, multiple supply voltages are required which leads to costly as well as complex power grid design. On the other hand, ternary logic has an elegant association with CNTFET devices. In particular, CNTFET provides a unique opportunity of achieving two distinct threshold voltages merely by employing CNTs with different diameters [67-69]. Therefore, a multi-threshold design can be accomplished easily in the CNTFETs.

In the past, the important concerns of VLSI designers were propagation delay, area, cost and reliability. However, increasing power consumption is being given importance along with others constraints in the recent years, due to increasing levels of integration and desire for portability. There is a remarkable success and growth of portable applications including notebook and laptop computers, audio and video based multimedia products, personal wireless communications systems such as digital assistants and communicators which requires high speed computation and vastly increased capabilities with low power consumption [5]. The ever increasing market segment of portable electronic devices enables

the implementation of long-lasting battery-operated systems. The progress of battery technology is slow compared to advances in microelectronics technology. Thus, it is unlikely to give a power solution for the mobile systems [70]. It has become imperative to develop VLSI circuits and systems which reduce heat dissipation in order to allow a large density of functions on a single chip. The situation has been further aggravated by the fact that the clock rate of microprocessor have already reached at 1 GHz mark, leading to a significant increase in switching power consumption. Furthermore, energy efficient circuits are also required in high performance computers, AC powered systems in which sinking large amount of heat through packages is becoming a difficult problem. Hence, designers are facing with more constraints: small chip area, high throughput, high speed, and at the same time, low-power dissipation.

In today's digital world, the operations such as automation, process control and many other complex computations are accomplished by various programmable chips like microprocessors, microcontroller and dedicated processors etc. The most basic and important processing unit of these chips is an arithmetic and logic unit (ALU) which is responsible for performing various arithmetic and logic operations such as addition, subtraction, multiplication, magnitude comparison and XOR etc. ALU is the heart of the instruction execution portion of every processor. For example, architecture of 8085 microprocessor includes 8-bit ALU to process binary data. Some other state-of-art binary and ternary ALU designs can be found in [71-73]. The increasing demand of high performance in modern information processing systems clearly points to the need of efficient implementation of ALU designs in terms of hardware, speed and power. Therefore, it is essential to develop an efficient ALU using CNTFETs for ternary logic.

In this thesis, we target the realization of CNTFET-based ternary ALU (TALU) for advanced electronic systems. Novel designs of TALU as well as its functional modules which include adder, subtractor, multiplier, comparator and exclusive-OR, are introduced and compared with the existing state-of-art works. These designs are evaluated based on four metrics: device count, propagation delay, power dissipation and power-delay-product. As the driving capability is an important parameter for the digital circuits, presented designs are tested under different loading conditions. These designs are also analyzed at different frequencies to examine their performance with variation in operating frequency. Further, another important characteristic of digital designs which should be considered is their susceptibility to voltage and temperature variations. For this, the presented circuits are evaluated over a

vast range of supply voltage and temperature.

On the other hand, increased attraction for bandwidth-hungry real-time applications and more usage of internet have raised a demand for very high speed networks. On the internet, a message like e-mail or webpage is transferred by first breaking it into data packets, and then, sending them towards the destination. Each data packet contains a header which has the information like data length, data type, sequence number, source address and destination address, and a payload [74]. Based on the information of the header, data packet is transferred to an output port by the network switch. A router which is a more sophisticated switch maintains a routing table and route incoming data packets from source to destination according to the information stored in the routing table [74]. Routers also send information to each other for the updating of their routing tables.

In general, optical fiber based physical medium transport the data packet from one router to another. Advances in optical fiber technologies like wavelength division multiplexing, have achieved very high-speed data transportation on optical fibers. To get the benefits offered by optical fiber technology, routers or network switches should have the ability to meet the increased data transfer rates [75]. In a network switch, the most time consuming task is table lookups. New approaches like policy based routing, flow analysis and Quality of Service (QoS) are increasing the number and variety of table lookups. The low priority packets, like data are transferred after the high priority packets such as voice and video, to maintain the QoS. These new approaches need multiple look up for each packet before it is delivered.

For table lookup task, software solutions like radix tree are relatively slow and not scalable with the size of the table. The hash function can perform lookup task in one memory access under normal conditions, however, its worst case search time is considerably higher than that of tree searches [76]. As a consequence, many of software solutions executing table lookup tasks at different network layers are now being substituted by their hardware counterparts. One of the most efficient hardware solutions is content addressable memory (CAM) which can be integrated as a co-processor with network processing unit to perform table lookup task. Further, CAMs are also used in many other key applications including tag directories in associative cache memory system [77-78], translation look-aside buffers in virtual memories [79-80], parametric curve extraction [81], data compression [82], image coding [83], real-time pattern searching in virus (or intrusion) detection systems [84] and gene pattern matching in bioinformatics [85] etc. Since most of these applications use smaller CAMs, the

current research related to CAMs is mainly governed by network applications which demand high density CAMs with low power and high search speed.

Design of low power and high speed CAM structures continues to be in high demand, and ballistic transport operation and low off current characteristics of CNTFET make them excellent candidate for high speed and increased integration density of CAM design. In this thesis, designing of CNTFET-based CAM cells is focused for fast match operation. Novel CAM structures are presented and compared with their existing counterparts.

### **Objectives of the Research are:**

- 1) To develop architectures and circuits of ternary logic based ALU (TALU) optimized in terms of hardware using CNTFETs.

- To improve the performance of sub-blocks of above hardware efficient TALU for power-delay product (PDP) efficiency using different circuit techniques.

- 3) To find a new architecture of TALU and circuits of its sub-blocks optimized for low power ternary system using CNTFETs.

- 4) To design ternary logic based CAM cell for fast search operation using CNTFETs.

#### 1.3 Thesis Outline

This thesis is organized as follows:

Chapter 2 deals with literature survey. First, details of CNTFET device are given, and then ternary logic and arithmetic circuits implemented in CMOS and CNTFET technology are reviewed. Further, a survey of CAM cells realized using CMOS as well as CNTFET is included.

Chapter 3 presents a design of 2-bit hardware optimized TALU (HO-TALU) using CNTFETs. Architecture and functionality of the 2-bit HO-TALU are described. HO-TALU introduces adder-subtractor (AS) module which eliminates a subtractor block from the conventional architecture. This section is followed by the description of ternary function minimization and realization. Design and implementation of HO-TALU functional modules and their integration over TALU slice are explained. HO-TALU modules utilize binary gates with ternary gates. The last section of this chapter demonstrates results for functional test and performance evaluation of HO-TALU including its hardware assessment.

Chapter 4 explained the performance boosted designs of sub-blocks of 2-bit HO-TALU

using CNTFETs. First, three designs of ternary full adder (TFA) which is an important subblock of AS module, are described. The first TFA design contains a symmetric pull-up and pull-down networks along with a resistive voltage divider as its integral part, which is configured using transistors and leads to a high speed design. The second TFA is designed based on complimentary pass transistor logic style in order to achieve low power consumption. The third TFA is implemented using dynamic logic style in order to get reduced power-delay-product. All new TFA designs are analyzed, evaluated and compared with the existing adder designs. This section is followed by the demonstration of design of new comparator module of 2-bit HO-TALU. This circuit is designed using pass transistor logic style and minimizes the number of stages to get improved performance. It is used in implementation of 2-bit and N-bit comparators which use binary tree configuration to correct the voltage levels. New design of comparator is analyzed, evaluated and compared with the existing comparator designs.

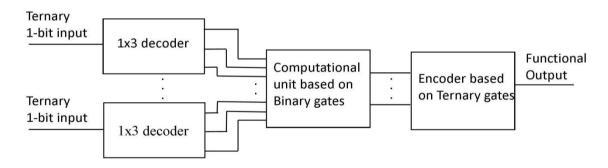

Chapter 5 describes a design of 2-bit power optimized TALU (HO-TALU) using CNTFETs. The architecture and functions of 2-bit PO-TALU are explained which is followed by the demonstration of ternary function minimization and realization. PO-TALU functional blocks: adder-subtractor-exclusive-OR (ASE) and multiplier, are designed using complementary CNTFET-based binary computational unit and a low complexity encoder. ASE eliminates exclusive-OR and subtractor blocks from the conventional architecture. Multiplier uses a new carry-add (CA) block in place of ternary half adder. Implementation of these blocks is shown which is followed by the extension of PO-TALU for 2-bit slice. The last section of this chapter demonstrates simulation results and comparison with existing CNTFET-based designs.

**Chapter 6** presents Binary CAM (BCAM) and ternary CAM (TCAM) cells designed based on low capacitance search logic in CNTFET technology. A new three-valued CAM (3CAM) cell is also presented using CNTFETs. This cell uses multi threshold voltage structure in implementation of low capacitance search network which leads to fast and compact CAM design. The presented CAM cells are simulated and compared with the existing memory designs.

Finally, **chapter 7** presents the summary of the work demonstrated in this thesis, by including key findings, main contributions and important observations, and also discusses possible directions for the future work.

### 2.1 Introduction

In chapter 1, the potential of CNTFET for high performance and low power modern designs due to its various excellent properties such as unique 1-D band structure, ballistic transport operation and low OFF-current [40-42], has been demonstrated. The relevance and motivation to develop CNTFET-based designs of ternary (three-valued) arithmetic and logic unit (TALU), and content addressable memory (CAM) cells, have also been discussed. Scientists and researchers interest in ternary logic is increasing over the past few decades because of providing several advantages such as reduced chip area and less number of interconnects, less complex error detection/error correction code and high speed serial/serial-parallel arithmetic operations etc. As a consequence, significant published literature is available on design and implementation of ternary arithmetic and logic circuits using MOSFETs [61-63]. In addition, due to the unique property of CNTFET for controlling threshold voltage by the CNT diameter, a number of researchers have found it as a fundamental device for the ternary design [64] [67-68]. In this chapter, the literature available on the designs and circuit implementations of ternary arithmetic and logic circuits based on CMOS as well as CNTFET technology is reviewed. Further, CAM has been in research since last few decades. Several circuit techniques and architectures have been developed to reduce the cell area, delay and power consumption of CAMs. This chapter provides a brief review of various designs of CAM cell developed in CMOS and CNTFET technology.

In section 2.2, electronics properties of CNTFET which make it very competitive in future electronics, is provided. Ternary logic and arithmetic circuits implemented in CMOS and CNTFET technology are reviewed in section 2.3. A review of CAM designs realized using CMOS as well as CNTFET is given in section 2.4. This is followed by the section 2.5 in which gaps in the published research work have been compiled along with the problem statement of the thesis.

### 2.2 Carbon Nano Tube Field Effect Transistor (CNTFET)

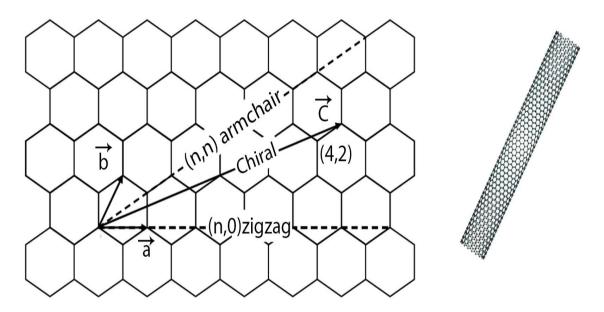

Carbon nanotube (CNT) is an allotrope of carbon with cylindrical structure, which could be single-walled (SWCNT) or multi walled. A SWCNT is obtained by rolling up a sheet of graphite along a wrapping vector  $C_h = n_1 a + n_2 b$ , where  $n_1$  and  $n_2$  are positive integers which

specify the chirality of the tube, and 'a' and 'b' are lattice unit vectors [86], as shown in Figure 2.1. Depending upon the value of  $n_1$  and  $n_2$ , SWCNT can be either metallic or semiconducting. If  $n_1$ - $n_2$  is a multiple of 3, SWCNT is metallic or else it is semiconducting [87]. Similarly, SWCNT is further classified into three groups according to value of  $n_1$  and  $n_2$ : (1) armchair CNT when  $n_1 = n_2 = n$ , (2) zigzag CNT when  $n_1 = 0$  or  $n_2 = 0$ , and (3) chiral CNT when  $n_1$  and  $n_2$  are different and nonzero. All armchair CNTs behave as conductors. On the other hand, zigzag and chiral CNTs show conductor behavior when the difference between the indices  $(n_1$ - $n_2)$  is an integer multiple of 3 otherwise they are semiconducting CNTs, which are used in CNTFET [88].

Figure 2.1: Unrolled sheet of graphite and the rolled lattice structure of CNT [86]

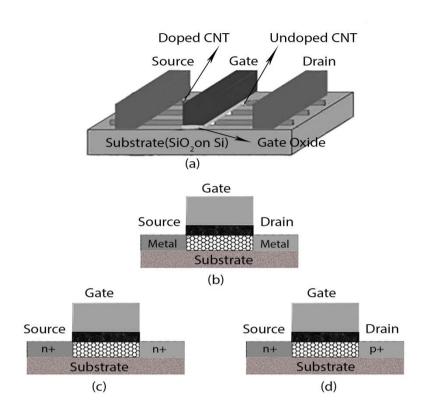

CNTFET is a type of FET that makes use of a single or an array of semiconducting SWCNTs as a channel formed between two metal electrodes acting as a source and drain contacts. Device is turned ON and OFF through the gate electrode placed around CNT channel. The schematic view of CNTFET is shown in Figure 2.2 (a) [39]. Undoped segments of CNTs serve as a channel under the gate electrode, while heavily doped CNT segments placed between the gate and the source/drain electrodes offer low electrical resistance in the ON-state of CNTFET [89]. Since the electrons are only confined to the narrow CNTs, carrier mobility goes up substantially on account of ballistic transport operation, in comparison with the bulk MOSFET.

**Figure 2.2:** Carbon nanotube field effect transistor (CNTFET) (a) Schematic view of a CNTFET device, (b) SB-CNTFET, (c) M-CNTFET, (d) T-CNTFET

Three types of CNTFET devices have been reported in the literature. They are known as schottky barrier CNTFET (SB-CNTFET), MOSFET-like CNTFET (M-CNTFET) and band-to-band tunneling CNTFET (T-CNTFET). SB-CNTFET works on the principle of direct tunneling through a schottky barrier (SB) at the source/drain-channel junction. This device is fabricated by making a direct contact between metal and semiconducting CNT, and shown in Figure 2.2 (b). The presence of SB at the CNT-metal junction limits the trans-conductance of the CNTFET in the ON state and decrease current deliver capability, which in turn reduce the suitability of SB-CNTFET for high-speed applications. Besides, SB-CNTFET shows strong ambipolar behavior which limits the usage of this device in complementary transistors-based circuits.

To eliminate the above mentioned drawback of SB-CNTFET, M-CNTFET has been developed and shown in Figure 2.2 (c). This device operates like a normal MOSFET with high speed and low power consumption. It is fabricated using heavily-doped source and drain CNT regions. Due to absence of SB at source/drain-channel junction, M-CNTFET has significantly higher ON current which makes it very suitable for ultra-high-performance

digital circuits. T-CNTFET which is shown in Figure 2.2 (c) has low ON current and very good cut-off characteristics. As a result, this device proves to be a super candidate for subthreshold and ultra-low-power design [90].

Based on the stated advantages as well as similarities of M-CNTFET with MOSFET in terms of operation and intrinsic attributes, this kind of CNTFET is used in this thesis for implementation of the presented circuits.

The gate width of CNTFET can be approximated as [91]:

$$W \approx \min(W_{\min}, N \times S) \tag{2.1}$$

Where  $W_{min}$  is the minimum gate width, N is the number of tubes and S is the pitch which is the distance between the centers of two adjoining CNTs under the same gate. The threshold voltage is the voltage needed to turn ON the device electro-statically via the gate. For a CNTFET, it can be approximated to the first order as the half band gap and can be calculated as [91]:

$$V_{th} \approx \frac{E_g}{2e} = \frac{1}{\sqrt{3}} \frac{aV_{\pi}}{eD_{CNT}} \approx \frac{0.43}{D_{CNT}(nm)}$$

(2.2)

Where  $V_{\pi}$  (= 3.033 eV) is the carbon  $\pi$ - $\pi$  bond energy in the tight bonding model, a (= 0.249 nm) is the carbon-carbon atom distance and e is the unit electron charge.  $D_{CNT}$  is the diameter of the CNT, which depends on the chirality vector ( $n_1$ ,  $n_2$ ) and can be calculated as [91]:

$$D_{CNT} = \frac{\sqrt{3}a}{\pi} \left( \sqrt{n_1^2 + n_2^2 + n_1 n_2} \right) \approx 0.0783 (nm) \left( \sqrt{n_1^2 + n_2^2 + n_1 n_2} \right)$$

(2.3)

According to the eq. (2.2) and (2.3), the threshold voltage of CNTFET is inversely proportional to the CNT diameter, and CNT diameter is directly proportional to chirality vector. For a CNTFET with (19, 0), CNT diameter is 1.487 nm and consequently, threshold voltage is 0.289 V. Similarly, for a CNTFET with (13, 0), CNT diameter is 1.02 nm and consequently, threshold voltage is 0.422V. The threshold voltage of P-CNTFET is same as that of N-CNTFET with an opposite sign. As the chirality vector increases, threshold voltage of CNTFET deceases. Thereby, CNTFET provides a unique opportunity for setting threshold voltage by varying the chirality vector of CNT. Different research group have demonstrated advances on manufacturing process for well controlled CNTs. For example, Li et al. [92] have used discrete catalytic nano-particles of various sizes for growth of single wall CNTs

(SWCNTs) with controlled chirality vectors. Ohno et al. [93] have presented a possibility of chirality assignment of SWCNT by micro-photocurrent spectroscopy. Wang et al. [94] has described a synthesis process using different carbon precursors on Co–Mo catalysts for fabricating SWCNTs with well-controlled chirality structure. Lin et al. [95] has reported post-processing techniques to control the threshold voltage of multiple-tube CNTFET.

Other excellent properties which make CNTFET a potential candidate for building highly efficient electronic system requiring high performance and low power are mentioned as follows:

- 1. Long scattering mean free path ( $\sim 1 \mu m$ ) [96] which leads to lower delay and less heating which is very consequential from IC point of view [97-98].

- 2. High carrier mobility  $(10^3-10^4\text{cm}^2/\text{V-S})$  in semiconducting CNTs [41] which provides high ON current (>1mA/ $\mu$ m).

- 3. Easy integration of high-k dielectric material (other than SiO<sub>2</sub>) due to the absence of dangling bonds, resulting in better gate electrostatics [42].

- 4. Strong chemical bonding, high thermal conductivity (1700-3000 W/mK) and chemical stability lead to high current densities ( $\sim 10^{10} \text{A/cm}^2$ ) [41].

- 5. Better matching of complementary CNTFETs: P and N-type CNTFETs with same sizes have equal carrier mobility, thereby deliver same drive currents, which is very important for transistor sizing of complex circuits [98].

Besides the mentioned advantages of this emerging technology, it also faces some major challenges that must be resolved to make it feasible for commercial purpose. These challenges are mentioned as follows:

- 1. CNT packing density [89]

- 2. CNT diameter [99] and density variation [100]

- 3. CNT misalignment [101-102]

- 4. Metallic-CNT (m-CNT) growth

Encouraging efforts are being made for resolving these challenges in time to time. Perfectly aligned and denser SWCNTs array based CNTFET was demonstrated in [103-104]. CNT synthesis processes such as wafer-scale CNT transfer along with wafer-scale-aligned growth [104], multiple cycles of chemical vapor deposition growth [105] and CNT transfer through multiple sacrificial layers [106] etc., enable us to pack nearly 5-50 CNTs/μm. Durkop et al. [42] developed CNTFET with high-quality ohmic contacts, high-k dielectrics HfO<sub>2</sub> films