# Mitigation of Power Quality Problems Using Interline Dynamic Voltage Restorer

# **THESIS**

Submitted in partial fulfilment of the requirements for the degree of

**DOCTOR OF PHILOSOPHY**

by

RAMCHANDRA NITTALA ID NO. 2012PHXF0508H

Under the Supervision of **Dr. Alivelu M. Parimi**

&

Under the Co-Supervision of **Dr. K. Uma Rao**

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

2018

# **BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI**

# **CERTIFICATE**

This is to certify that the thesis entitled <u>Mitigation of Power Quality Problems Using</u>

<u>Interline Dynamic Voltage Restorer</u> submitted by <u>RAMCHANDRA NITTALA</u> ID.No

<u>2012PHXF0508H</u> for award of Ph.D. of the Institute embodies original work done by him/her under my supervision.

| Signature of the Supervisor    | Signature of the Co-supervisor              |

|--------------------------------|---------------------------------------------|

| Dr. ALIVELU M. PARIMI          | Dr. K. UMA RAO                              |

| Asst. Professor, Dept. of EEE, | Professor, Dept. of EEE,                    |

| BITS-Pilani, Hyderabad Campus. | R. V. College Of Engineering,<br>Bengaluru. |

| Date:                          | Date:                                       |

# Acknowledgements

As I am reaching the end of a long journey with ups and downs, I wish to acknowledge the remarkable individuals who stood with me in my ups and downs. I want to give thanks to God for sustaining me and guiding me throughout this arduous journey.

At an outset, I would like to express my deep sense of gratitude and thanks to **Dr. Alivelu Manga Parimi**, my thesis supervisor and **Dr. K Uma Rao**, my thesis co-supervisor. I will always be grateful, for their valuable guidance and constant encouragement.

I would like to thank my Doctoral Advisory Committee members, **Prof. BVVSN Prabhakar Rao** and **Dr. Shaikshavali Chitraganti** for their inspiring support and invaluable scientific suggestions from time to time. They always extended helpful hands towards me whenever I needed them.

I would like to thank **Prof. Y. Yoganandam**, for his moral support throughout my thesis.

I express my sincere thanks to all the faculty members, Research Scholars and Technicians of Department of Electrical Engineering, BITS Pilani, Hyderabad campus for their kind help and encouragement in carrying out my research work.

Constant moral support extended by my friends and well-wishers are gratefully acknowledged. The Financial assistance from BITS Pilani, Hyderabad is gratefully acknowledge.

Words are inadequate to express thanks and appreciation to my wife, **V. Sumadeepthi** for all her love and support when I was irritable and depressed. Her patience and sacrifice will remain my inspiration throughout my life.

I appreciate the unending love and affection from my parents, **Dr. N.Parthasarathy** and **Smt. N.Jwalamamba**. They have sacrificed many things for me. I have no phrases to praise them. Their blessings have helped me in reaching this goal. Love you both for your everlasting supports extended towards me.

My heart felt regard goes to my father in law and my mother in law, Sh.V.SubbaRao and Smt.

**V.Jayasree** for their love and moral support. Last but not the least, the undying love and affection who directly or in-directly had influence on me in the path of achieving the goal can never be completely expressed with words alone.

Ramchandra Nittala

# **Abstract**

# Mitigation of Power Quality problems using Interline Dynamic Voltage Restorer

## by Ramchandra Nittala

The effective function of sensitive loads is dependent on the quality of power delivered to it and quantified in terms of its efficiency, security and reliability of loads connected to the same distribution line. However the loads connected on the same end are diversified from electronically controlled loads to heavy machinery. These cause minor to major power quality issues on the distribution system. However the sensitive electronic equipment loads are more effected with the power quality problems especially the voltage sag which eventually cause disruption in the performance of the load, raise in temperature, and damage to equipment etc. Mitigating voltage sag at the distribution level of power system network is of vital importance for enhanced performance of these loads. Custom power devices have been the part of the latest technology which provides the compensating measure as the mitigation equipment and thus improving the equipment immunity.

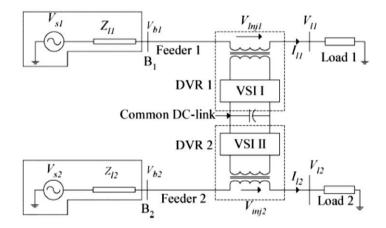

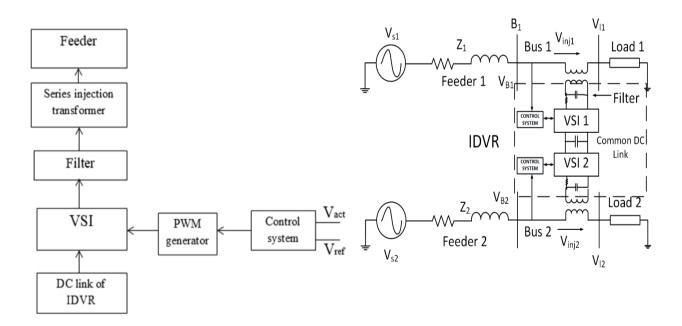

Among the customer power devices also referred to as the distribution Flexible AC Transmission System (D-FACTS) devices, the Interline dynamic voltage restorer (DVR) device, is utilized for mitigation of voltage sag/swell. The IDVR system comprises of several DVRs connected to different feeders with a common DC link. This IDVR scheme facilitates transfer of power between loads on different individual line through the common DC link of the DVRs. When one of the DVRs in IDVR system compensates for voltage sag in one feeder by importing real power from the DC link, the other DVRs replenish the DC-link energy to maintain the DC-link voltage at a specific level. In order to have control required output from IDVR detailed modelling of the components of IDVR is very important.

The DC link of IDVR provides the required energy to the IDVR for mitigating the voltage sag. The restoration of the DC link energy of the IDVR is a weighted factor in the robust operation of IDVR. The proposed novel methods to replenish the DC link of IDVR, employ Phase Shifting Transformer and PV system.

The advantage of IDVR over the other D-FACTS devices is the ability to mitigate voltage sag in multiple feeders at same instance of time. This is called multidirectional compensation. To test the functionality of IDVR with two DVRs in the bidirectional compensation, IDVR is tested in a two line power system and a voltage sag is applied in two feeders at same instance of time. This part of bidirectional compensation of IDVR is also verified with the experimental results obtained from a hardware IDVR prototype set up.

Additionally current source inverters (CSI) have certain advantages like current control capability, more regulation of ac voltage. Implementing CSI in IDVR to inject voltage for improvement of power quality is investigated. With usage of the current source inverters the injected voltage from IDVR may get improved. Hence in the proposed research the current source inverters are replaced with voltage source inverters and the comparison of the two inverters as the building blocks of IDVR are analysed in a test power system.

The functionality of IDVR is also tested by simulating the IDVR with a real time data. The real time data of some institute or industry is considered in the proposed research and the probable chances of voltage sag occurrences in that load are analysed. The efficiency of IDVR in compensating the voltage sags is also analysed. This real time simulation of IDVR brings more practicality towards the research on IDVR. Hence the overall research brings about the design of IDVR in mitigating voltage sag/swell, its DC link restoration and more importantly the bidirectional compensation ability of IDVR sustained by the experimental results obtained from a laboratory prototype model.

# **Contents**

| Certificate                                        | i   |

|----------------------------------------------------|-----|

| Acknowledgements                                   | ii  |

| Abstract                                           | iv  |

| Contents                                           | vi  |

| List of Figures                                    | X   |

| List of Tables                                     | xiv |

| 1. Introduction                                    | 1   |

| 1.1 Background                                     | 1   |

| 1.1.1 Sag                                          | 1   |

| 1.1.2 Harmonics                                    | 2   |

| 1.2 Motivation of the Research                     | 4   |

| 1.3 Aims and Objectives of the Research            | 5   |

| 1.4 Organization of the Research                   | 7   |

| 2. Literature Survey                               | 9   |

| 2.1 Introduction                                   | 9   |

| 2.1.1 Static Capacitors                            | 11  |

| 2.1.2 Synchronous Condensers                       | 12  |

| 2.1.3 Shunt Reactors                               | 13  |

| 2.1.4 Voltage Regulators                           | 13  |

| 2.1.5 Static Synchronous Compensator (STATCOM)     | 15  |

| 2.1.6 Static Synchronous Series Compensator (SSSC) | 16  |

| 2.1.7 Unified Power Flow Controller (UPFC)         |     |

| 2.1.8 Interline Power Flow Controller (IPFC)       |     |

| 2.2.C                                              | 1/  |

|   | 2.2.1 Custom Power Devices                                     | 20 |

|---|----------------------------------------------------------------|----|

|   | 2.3 Distribution STATCOM (DSTATCOM)                            | 21 |

|   | 2.3.1 Principle of operation of Shunt-Connected VSC            | 22 |

|   | 2.4 Dynamic Voltage Restorer (DVR)                             | 24 |

|   | 2.4.1 Principle of operation of Series-connected VSC (DVR)     | 25 |

|   | 2.5 Literature Survey of DVR                                   | 27 |

|   | 2.6 Unified Power Quality Conditioner (UPQC)                   | 28 |

|   | 2.7 Literature Survey of UPQC                                  | 30 |

|   | 2.8 Limitations to the DVR and UPQC                            | 31 |

|   | 2.9 Interline Dynamic Voltage Restorer (DVR)                   | 32 |

|   | 2.10 Literature Survey of IDVR                                 | 33 |

|   | 2.11 Gaps in Research                                          | 35 |

|   | 2.12 Discussion                                                | 36 |

| 3 | . Modelling of IDVR                                            | 38 |

|   | 3.1 Introduction                                               | 38 |

|   | 3.2 Interline Dynamic Voltage Restorer                         | 38 |

|   | 3.2.1 Inverters                                                | 39 |

|   | 3.2.2 DC Link of IDVR                                          | 41 |

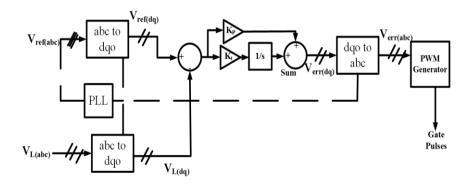

|   | 3.2.3 Control System                                           | 41 |

|   | 3.2.4 Series Injection Transformer                             | 41 |

|   | 3.3 Modelling of IDVR                                          | 42 |

|   | 3.3.1 Inverter Modelling                                       | 43 |

|   | 3.3.2 DC link Capacitor Modelling                              | 46 |

|   | 3.4 Control Systems of IDVR                                    | 48 |

|   | 3.5 Results                                                    | 49 |

|   | 3.6 Conclusion                                                 | 52 |

| 4 | . Replenishing DC Link of IDVR                                 | 54 |

|   | 4.1 Introduction                                               | 54 |

|   | 4.2 DC Link of IDVR                                            | 54 |

|   | 4.2.1 Literature Review on Replenishing DC Link Energy of IDVR | 55 |

|   | 4.3 DC Link Controller                                         | 56 |

|   | 4.4 Phase Shifting Transformers                                | 58 |

|   | 4.5 PV Source                                                  | 60 |

|   | 4.6 Results                                                    | 61 |

| 4.6.1 Voltage sag Observed in first feeder and restoring of the DC link energy with P source |       |

|----------------------------------------------------------------------------------------------|-------|

| 4.6.2 Voltage sag Observed in first feeder and restoring the DC link energy with PST         |       |

| 4.6.3 Voltage sag Applied in two feeders in the absence of PV and PST for restoration        | n 67  |

| 4.7 Conclusion                                                                               | 69    |

| 5. CSI Based IDVR                                                                            | 70    |

| 5.1 Introduction                                                                             | 70    |

| 5.2 Current Source Inverters                                                                 | 70    |

| 5.3 Super Conducting Magnetic Energy Storage System (SMES)                                   | 72    |

| 5.4 Results                                                                                  |       |

| 5.4.1 Comparison of VSI and CSI on an IEEE 8 Bus System                                      | 73    |

| 5.4.2 Summary of the Cases                                                                   | 81    |

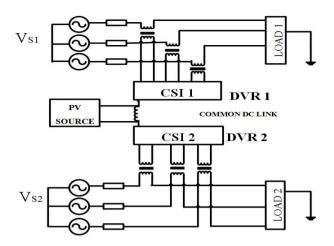

| 5.5 Simulation Results of IDVR with CSI as Building Block                                    | 82    |

| 5.5.1 Using sudden start of induction motor at feeder 1                                      | 84    |

| 5.5.2 Voltage sag/swell with a LG fault at feeder 1                                          | 85    |

| 5.5.3 Multiple sags at feeder 1                                                              | 87    |

| 5.5.4 Simultaneous Voltage Sag in Both Feeders                                               | 88    |

| 5.6 Conclusion                                                                               | 90    |

| 6. Real Time Simulation of IDVR                                                              | 92    |

| 6.1 Introduction                                                                             | 92    |

| 6.2 Description of the Real Time Load                                                        | 92    |

| 6.3 Results                                                                                  | 95    |

| 6.3.1 Switching On induction motor load                                                      | . 100 |

| 6.3.2 LG Fault at Substation 2                                                               | . 101 |

| 6.4 Conclusion                                                                               | . 102 |

| 7. Laboratory Prototype of IDVR                                                              | . 103 |

| 7.1 Introduction                                                                             | . 103 |

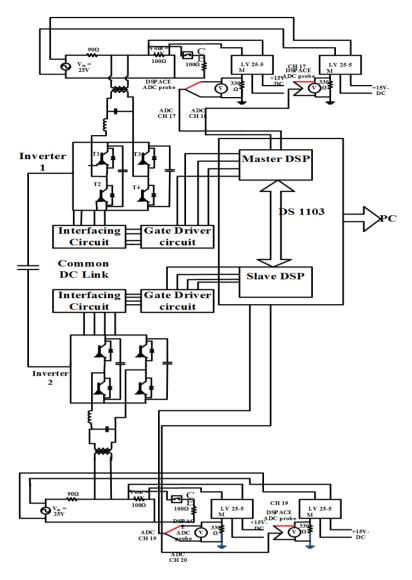

| 7.2 Control System of IDVR                                                                   | . 105 |

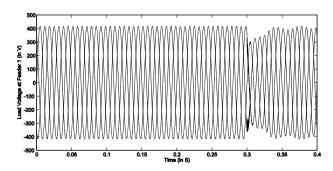

| 7.3 Simulation Results                                                                       | . 107 |

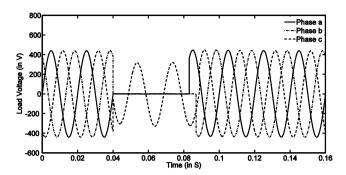

| 7.3.1 Case 1- Load 1 and Load 3 Replaced as RL Loads                                         | . 109 |

| 7.3.2 Case 2-Load 1 and Load 3 Replaced as RC loads                                          | . 109 |

| 7.4 Experimental Results                                                                     | .112  |

| 7.5 Conclusion                                                                               | .116  |

| 8. Conclusion                                                                                | . 117 |

| 9.1 Canalysian                                                                               | 117   |

| 8.2 Future W | ork | <br> | 118 |

|--------------|-----|------|-----|

|              |     |      |     |

|              |     |      |     |

| Bibliography |     | <br> | 120 |

# **List of Figures**

| Fig. 1.1        | Wave form with sag                                         | 2  |

|-----------------|------------------------------------------------------------|----|

| Fig. 1.2        | Waveform with harmonics                                    | 2  |

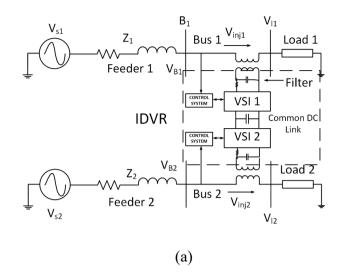

| Fig. 1.3        | Schematic diagram of an IDVR in a two-feeder system        | 3  |

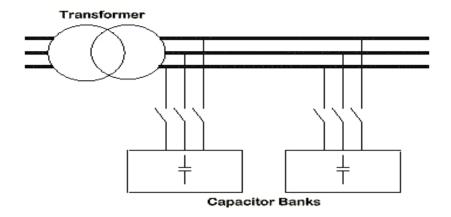

| Fig. 2.1        | Static Capacitor or shunt capacitor banks                  | 12 |

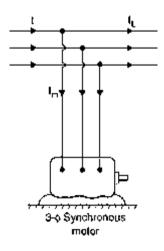

| Fig. 2.2        | Synchronous Condenser                                      | 12 |

| Fig. 2.3        | Shunt Reactors                                             | 13 |

| Fig. 2.4        | Schematic diagram of STATCOM                               | 15 |

| Fig. 2.5        | Schematic diagram of SSC                                   | 16 |

| Fig. 2.6        | Schematic diagram of UPFC                                  | 17 |

| Fig. 2.7        | Schematic diagram of IPFC                                  | 18 |

| Fig. 2.8        | Schematic representation of the DSTATCOM                   | 21 |

| Fig. 2.9        | Single line diagram of shunt connected VSC                 | 23 |

| Fig. 2.10       | Simplified line diagram of shunt connected VSC             | 23 |

| Fig. 2.11       | Phasor diagram of voltage dip mitigation using shunt VSC   | 24 |

| Fig. 2.12       | Schematic representation of the DVR                        | 24 |

| Fig. 2.13       | Single line diagram of series connected VSC                | 25 |

| Fig.2.14        | Simplified line diagram of series connected VSC            | 26 |

| Fig. 2.15       | Phasor diagram of voltage mitigation using series VSC      | 26 |

| Fig. 2.16       | Basic Block Diagram of UPQC                                | 29 |

| Fig. 2.17       | Basic Layout of two line IDVR                              | 32 |

| Fig. 3.1        | Schematic layout of two line IDVR                          | 38 |

| Fig. 3.2(a),(b) | (a) Schematic layout of two line IDVR (b) One line diagram |    |

|                 | of one of the feeder                                       | 45 |

| Fig. 3.3        | Phasor diagram of in phase method of compensation          | 45 |

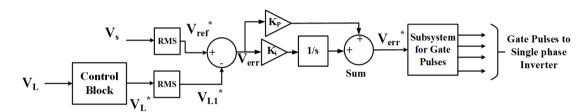

| Fig. 3.4        | Schematic Layout of Control System                         | 48 |

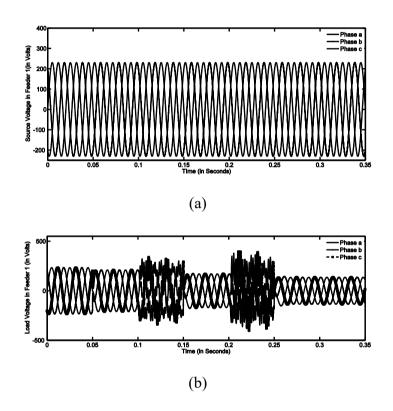

| Fig. 3.5(a),(b) | (a) Source Voltage waveform (b) Load Voltage waveform in   |    |

|                 | feeder 1 without IDVR                                      | 50 |

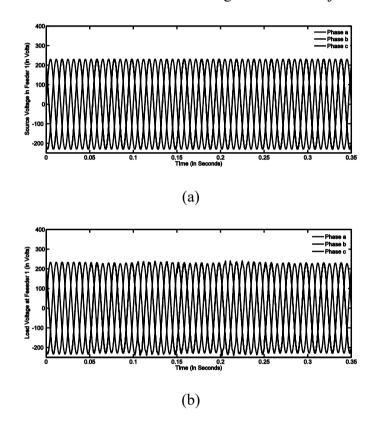

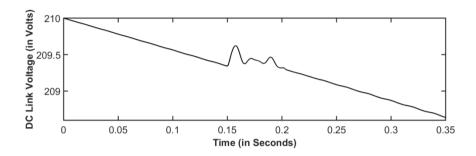

| Fig. 3.6(a),(b) | (a) Source Voltage waveform (b) Load Voltage waveform in    |    |

|-----------------|-------------------------------------------------------------|----|

|                 | feeder 1 with IDVR                                          | 51 |

| Fig. 3.7        | DC Link Capacitance Voltage                                 | 52 |

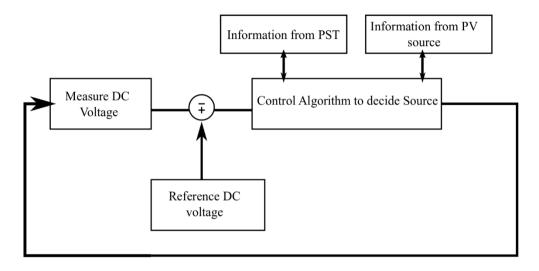

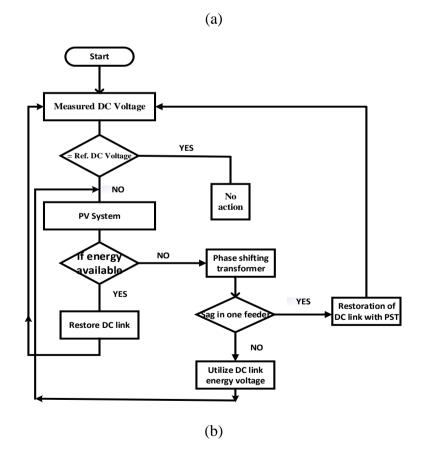

| Fig. 4.1(a),(b) | (a) Schematic Block Diagram of DC Link Controller of        |    |

|                 | IDVR (b). Control algorithm of DC link controller           | 58 |

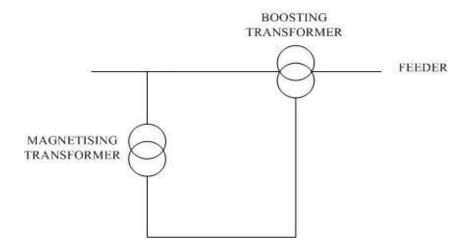

| Fig.4.2         | Schematic Layout of Phase Shifting Transformers             | 59 |

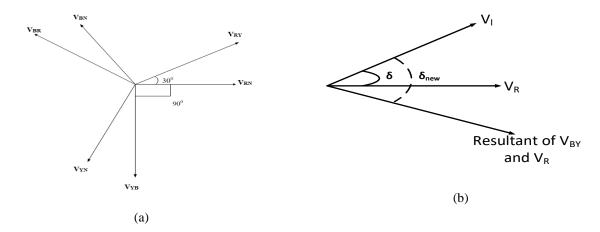

| Fig.4.3(a),(b)  | (a) Phasor Diagram of Voltages in healthy feeder with PST   |    |

|                 | (b) resultant phasor diagram of healthy feeder              | 60 |

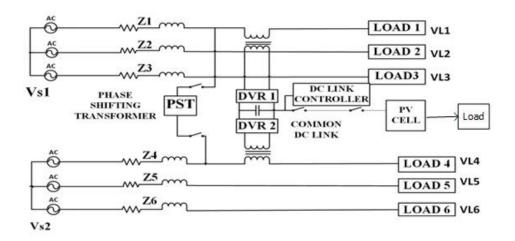

| Fig.4.4         | Simulink model of IDVR                                      | 61 |

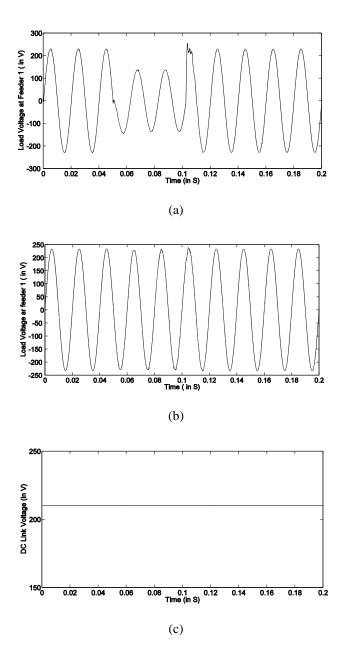

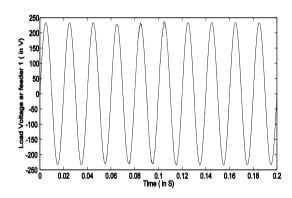

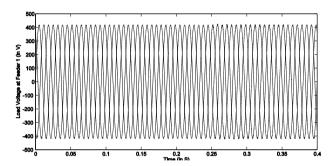

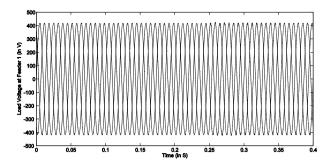

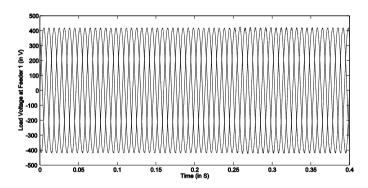

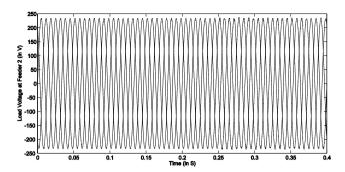

| Fig.4.5(a),(b), | (a) Load Voltage at feeder 1 (in Volts) without IDVR (b)    |    |

| (c)             | Load voltage in feeder 1 (in Volts) (c) DC link voltage (in |    |

|                 | volts) with IDVR and PV system                              | 64 |

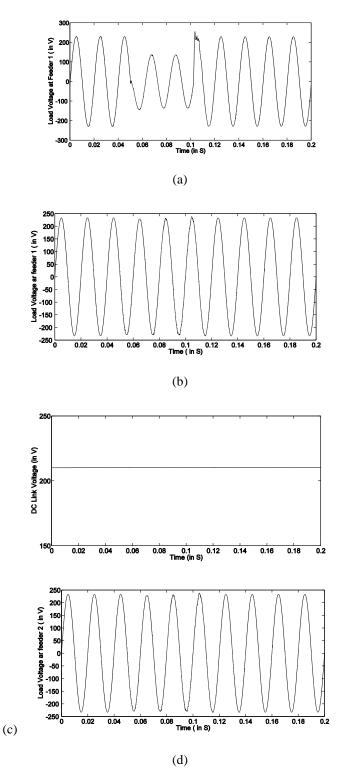

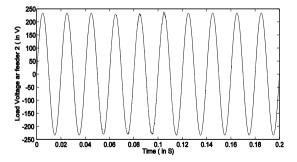

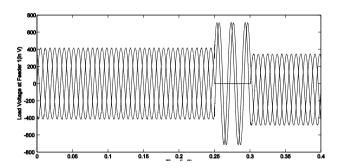

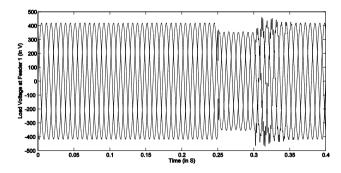

| Fig.            | (a) Load voltage at feeder 1 (in Volts) without IDVR (b)    |    |

| 4.6(a),(b),(c), | Load voltage in feeder 1 (in Volts) (c) DC link voltage (in |    |

| (d)             | volts) with IDVR and Phase Shifting transformer (d) Load    |    |

|                 | voltage at feeder 2 (in Volts)                              | 66 |

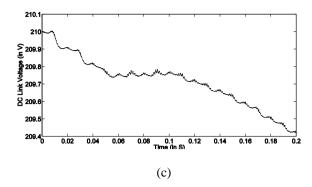

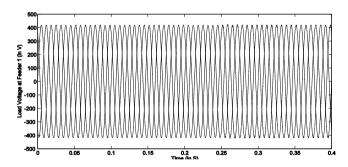

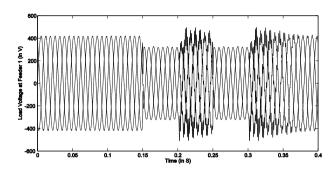

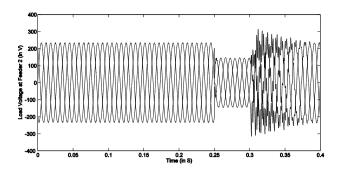

| Fig.4.7(a),(b), | (a) Load voltage in feeder 1 and in feeder 2(in Volts)      |    |

| (c)             | without IDVR (b) Load voltage in feeder 1 and feeder 2(in   |    |

|                 | Volts) with IDVR (c) DC link voltage (in volts) without PV  |    |

|                 | system and PST                                              | 69 |

| Fig. 5.1        | Schematic diagram of VSI                                    | 71 |

| Fig. 5.2        | Schematic diagram of the total system                       | 75 |

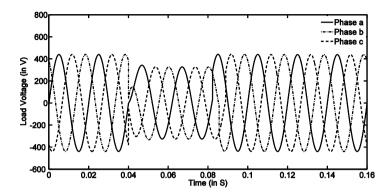

| Fig. 5.3        | Load Voltage without IDVR                                   | 76 |

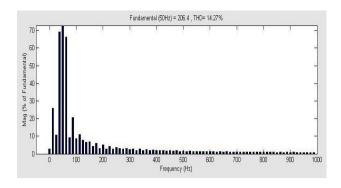

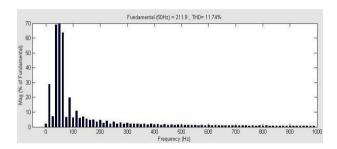

| Fig. 5.4        | THD without IDVR                                            | 76 |

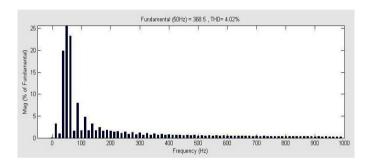

| Fig. 5.5        | Load voltage with VSI based IDVR                            | 77 |

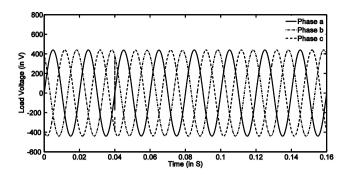

| Fig. 5.6        | Load voltage with CSI based IDVR                            | 77 |

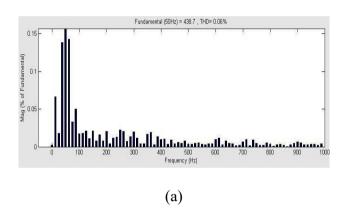

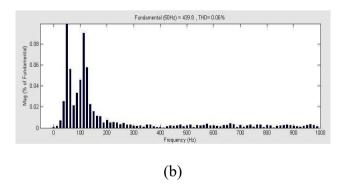

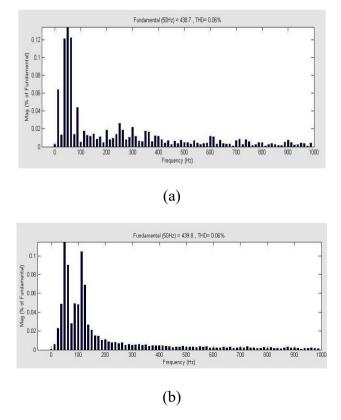

| Fig. 5.7(a),(b) | THD (a) with VSI (b) with CSI as building blocks of IDVR.   | 78 |

| Fig. 5.8        | Load voltage for single phase to ground fault without       |    |

|                 | IDVR                                                        | 78 |

| Fig. 5.9        | THD for single phase to ground fault                        | 79 |

| Fig.            | THD (a) with VSI (b) with CSI as building blocks of IDVR.  | 79  |

|-----------------|------------------------------------------------------------|-----|

| 5.10(a),(b)     |                                                            |     |

| Fig. 5.11.      | Load voltage during double phase to ground without IDVR    | 80  |

| Fig. 5.12.      | THD during double phase to ground fault                    | 80  |

| Fig.            | THD (a) with VSI (b) with CSI as building blocks of IDVR.  | 80  |

| 5.13(a),(b)     |                                                            |     |

| Fig. 5.14       | Schematic diagram of total system simulated in MATLAB      | 83  |

| Fig. 5.15       | Load voltage with induction motor as load without IDVR     | 84  |

| Fig. 5.16       | Load voltage with induction motor as load with IDVR        | 85  |

| Fig. 5.17       | Load voltage at feeder 1 with LG fault without IDVR        | 86  |

| Fig. 5.18       | Load Voltage at feeder 1 with LG fault with IDVR           | 86  |

| Fig. 5.19       | Load voltage with multiple sags without IDVR               | 87  |

| Fig. 5.20       | Load voltage with multiple sags with IDVR                  | 88  |

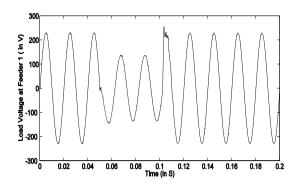

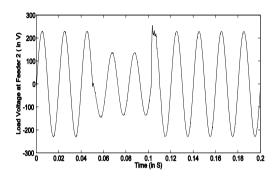

| Fig. 5.21       | Load Voltage at feeder 1 without IDVR                      | 88  |

| Fig. 5.22       | Load Voltage at feeder 2 without IDVR                      | 89  |

| Fig. 5.23       | Load voltage at feeder 1 with IDVR                         | 89  |

| Fig. 5.24       | Load voltage at feeder 2 with IDVR                         | 90  |

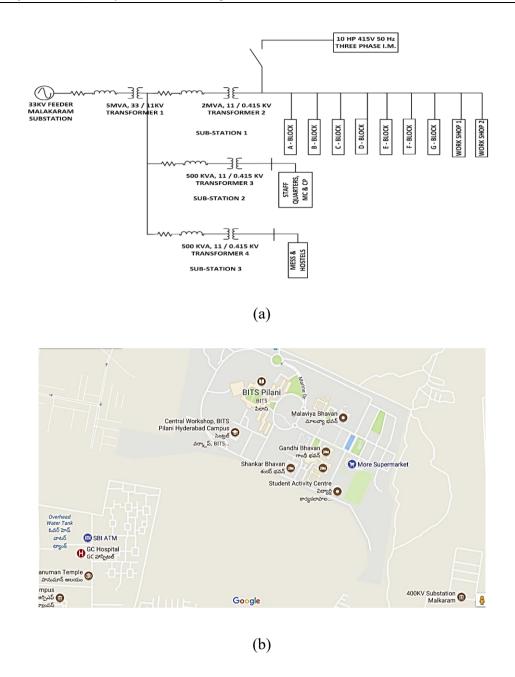

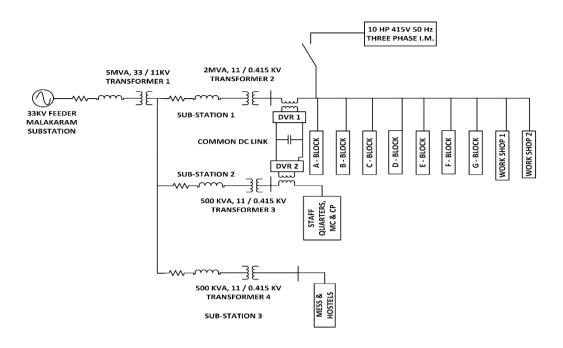

| Fig. 6.1(a),(b) | (a) Schematic layout of the real time load. (b) Google Map |     |

|                 | of BITS Campus                                             | 93  |

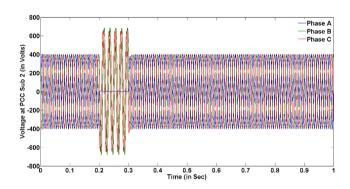

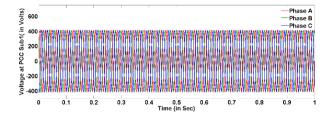

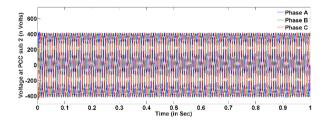

| Fig. 6.2        | Voltage at PCC of Substation 2 when A LG fault is applied  | 96  |

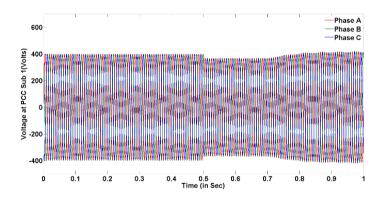

| Fig. 6.3        | Voltage at PCC of Substation 1                             | 98  |

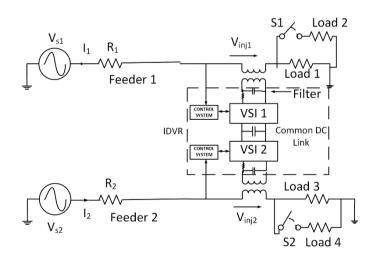

| Fig.6.4         | Schematic layout of real time load with IDVR (VSI)         | 100 |

| Fig.6.5         | Voltage at PCC of substation1 when the induction motor is  |     |

|                 | switched ON in the presence of IDVR                        | 101 |

| Fig. 6.6        | Voltage at PCC of substation 2 when LG fault is applied    |     |

|                 | with IDVR                                                  | 101 |

| Fig. 7.1        | Schematic Diagram of IDVR                                  | 103 |

| Fig. 7.2        | Control System of IDVR                                     | 107 |

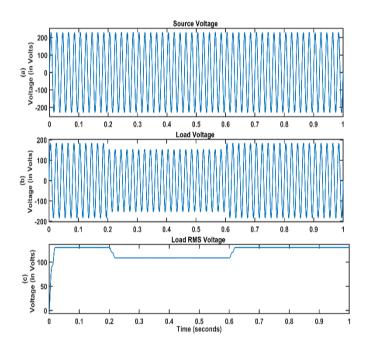

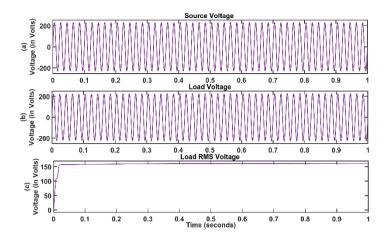

| Fig.            | (a) Source Voltage of Feeder 1 (b) Load Voltage of Feeder  |     |

| 7.3(a),(b),(c)  | 1 (c) RMS Voltage of Load 1 in the absence of IDVR         | 110 |

| Fig.            | (a) Source Voltage of Feeder 2 (b) Load Voltage of Feeder 2  |     |

|-----------------|--------------------------------------------------------------|-----|

| 7.4(a),(b),(c)  | (c) RMS Voltage of Load 2 in the absence of IDVR             | 110 |

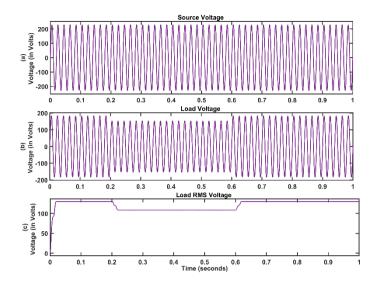

| Fig.            | (a) Source Voltage of Feeder 1 (b) Load Voltage of Feeder 1  |     |

| 7.5(a),(b),(c)  | (c) RMS Voltage of Load 1 in the presence of IDVR            | 110 |

| Fig 7.6 (a),    | (a) Source Voltage of Feeder 2 (b) Load Voltage of Feeder 2  | 111 |

| (b), (c)        | (c) RMS Voltage of Load 2 in the presence of IDVR            |     |

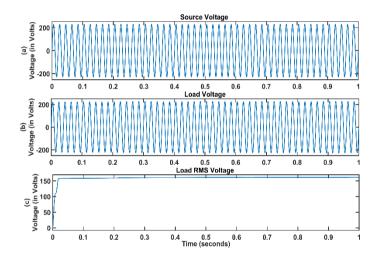

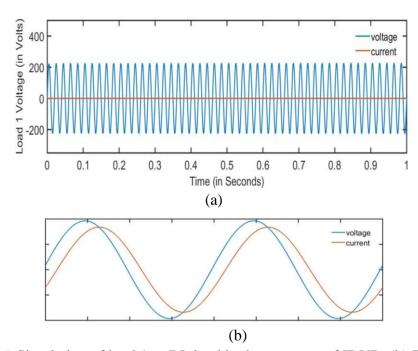

| Fig. 7.7(a),(b) | (a) Simulation of load 1 as RL load in the presence of IDVR. |     |

|                 | (b) Zoomed Portion of voltage and current in 7.7 (a)         | 112 |

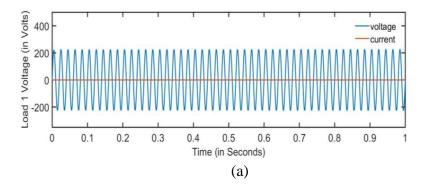

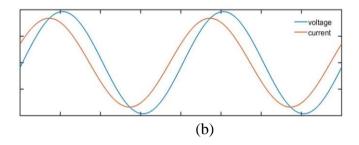

| Fig. 7.8(a),(b) | (a) Simulation of load 1 as RC load in the presence of       |     |

|                 | IDVR. (b) Zoomed Portion of voltage and current in 7.8(a)    | 112 |

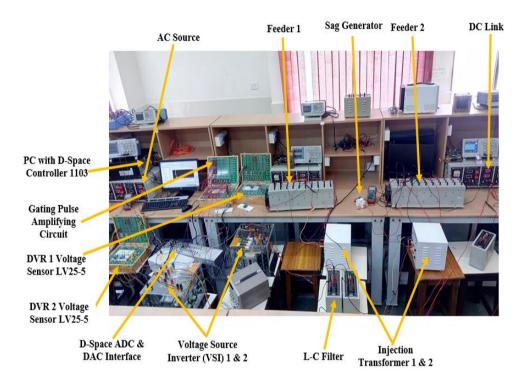

| Fig. 7.9        | Laboratory Prototype of IDVR system                          | 114 |

| Fig. 7.10       | Schematic diagram of hardware prototype                      | 115 |

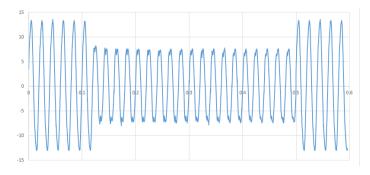

| Fig. 7.11       | Load Voltage of Feeder 1 in the absence of IDVR              | 115 |

| Fig. 7.12       | Load Voltage of Feeder 2 in the absence of IDVR              | 116 |

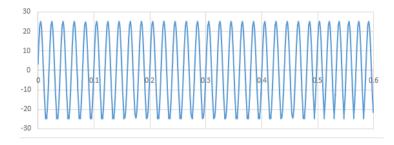

| Fig. 7.13       | Load Voltage of Feeder 1 in the presence of IDVR             | 116 |

| Fig 7 14        | Load Voltage of Feeder 2 in the presence of IDVR             | 116 |

# **List of Tables**

| 2.1 | Summary of FACTS configuration on transmission side | 18  |

|-----|-----------------------------------------------------|-----|

| 3.1 | Parameters of the Two Line IDVR Shown in Fig 3.2(a) | 47  |

| 4.1 | Parameters of two line IDVR                         | 62  |

| 4.2 | Summary of the three cases considered               | 63  |

| 5.1 | Line data of the system.                            | 74  |

| 5.2 | Summary of simulation cases                         | 82  |

| 5.3 | Parameter two Feeder IDVR system                    | 84  |

| 6.1 | Load ratings of each block the BITS campus          | 96  |

| 6.2 | The parameters of IDVR                              | 99  |

| 7.1 | Parameters of Simulink Block Diagram                | 107 |

| 7.2 | Parameters of Prototype Model                       | 113 |

# Chapter 1

# **Introduction**

# 1.1 Background

Power Systems is sub-divided into Generation, Transmission and Distribution where the power is generated from the generation side and is fed to the various loads on the distribution side by other transmission line. In addition to the variability of the power deliver to the loads, power quality is also a vital importance. Subsequently lack of quality effects the customers with sensitive loads. Although the distribution side contains different loads, the sensitive loads are the one which are effected by these power quality problems. The escalation of sensitive loads such as life support operation theatres in hospitals, data base systems, processing plants contain the semiconductor devices and air control traffic equipmements and numerous other data processing and service providers requires clean and uninterrupted power. Such customers are very vary of dips since each interruption cause some substantial amount of money. Consequently the power quality is an important role on the distribution side. Power quality sets the limits of electrical properties that allows electrical systems to function in their intended manner without significant loss of performance or life. Among the several power quality problems, the problems considered in the thesis are voltage sag and harmonics.

#### 1.1.1 Sag

Sag is a reduction of AC voltage at a given frequency for the duration of 0.5 cycles to 1 minute's time as shown in fig 1.1. Sags are usually caused by system faults, and are also often the result of switching on loads with heavy start up currents.

Common causes of sags include starting large loads (such as one might see when they first start up a large air conditioning unit) and remote fault clearing performed by utility equipment. Similarly, the starting of large motors inside an industrial facility can result in significant voltage drop (sag). A

motor can draw six times its normal running current, or more, while starting. A large amount of reactive power is absorbed by the motor during its starting. This leads to formation of voltage sag.

Fig. 1.1 Wave form with Sag.

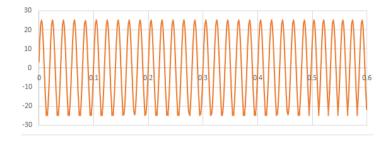

#### 1.1.2 Harmonics

Harmonic distortion is the corruption of the fundamental sine wave at frequencies that are multiples of the fundamental. (e.g., 150Hz is the third harmonic of a 50Hz fundamental frequency; 3 X 50 = 150) as shown in fig 1.2. The power electronics loads produce harmonics because of their switching action of power electronic switches.

Symptoms of harmonic problems include overheated transformers, neutral conductors, and other electrical distribution equipment, as well as the tripping of circuit breakers and loss of synchronization on timing circuits that are dependent upon a clean sine wave trigger at the zero crossover point.

Fig. 1.2 Waveform with harmonics.

Custom power is a technology-driven product and service solution which embraces a family of devices to provide power-quality enhancement functions. Among the several novel custom-power devices, the Interline dynamic voltage restorer (DVR) [1], [2] is the most technically advanced and economical device for voltage-sag mitigation in distribution systems. The Interline Dynamic Voltage Restorer (IDVR) system consists of several DVRs protecting sensitive loads in different

distribution feeders emanating from different grid substations, and these DVRs share a common DC link. The interline power-flow controller (IPFC) addresses the problem of compensating a number of transmission lines at a given substation. The IPFC scheme provides a capability to transfer real power directly between the compensated lines, while the reactive power is controllable within each individual line. The IDVR scheme provides a way to transfer real power between sensitive loads in individual line through the common DC link of the DVRs, as it does in the IPFC. However, the lines in the IPFC originate from a single grid substation while the lines in the IDVR system originate from different grid substations.

Fig. 1.3 Schematic diagram of an IDVR in a two-feeder system.

When one of the DVRs in IDVR system compensates for voltage sag in a feeder it draws energy from the DC link, the other DVRs replenish the DC-link energy to maintain the DC-link voltage at a specific level. Thus the IDVR provides a way to replenish the energy in the common DC-link energy storage dynamically. An example of a potential location for such a scheme is an industrial park where power is fed from different feeders connected to different grid substations, those that are electrically far apart. The sensitive loads in this park may be protected by DVRs connected to respective loads. The DC links of these DVRs can be connected to a common terminal, thereby forming an IDVR system. This would cut down the cost of the custom-power device, as sharing common DC link reduces the size of the DC-link storage capacity substantially, compared to that of a system in which loads are protected by clusters of DVRs with separate energy storage systems.

## 1.2 Motivation of the Research

Literature on IDVR presents various methodologies for restoring the DC energy and controlling the voltage compensation ability of IDVR. There were many schemes proposed in the research for replenishing the DC link energy of IDVR. When one of the DVR's is working in voltage compensation mode, the second DVR of IDVR works in power compensation and restore the DC link energy. The limitation for this type of restoration is, one of the DVR should always be working in power compensation mode, which implies that the feeder connected to that particular DVR will be treated as healthy feeder in all conditions. This is a big deviation from practical scenario.

The second gap in the research of IDVR are bidirectional compensation and utilisation of current source inverters in the building blocks of IDVR. The IDVR constitutes of two or more DVRs sharing a common DC link. Since these DVRs are connected to multiple feeders, the voltage compensation in multiple feeders can be performed with each one of them at one instance. This type of compensation is called as bidirectional compensation. This is the unique capability of IDVR to mitigate voltage sag in multiple feeders at same instant and yet to be investigated. To examine the functionality of IDVR in the bidirectional compensation, a two line IDVR system will be considered and voltage sag will be applied in two feeders at same instant. The efficiency of IDVR in compensating the voltage sag can be tested. This part of bidirectional compensation of IDVR will be verified with the experimental results obtained from a hardware IDVR prototype set up.

The third major gap in the IDVR research is use of current source inverters as the building blocks of IDVR. The voltage source inverters are utilized as the traditional building blocks of IDVR. The current source inverters have certain advantages like current control capability, more regulation of AC voltage etc. The possibility of the improvement of voltage sag mitigation with CSI is too investigated. Hence this current source inverters will replace with voltage source inverters and the

comparison of the two inverters as the building blocks of IDVR will be performed in a test power system.

The functionality of IDVR in mitigating the voltage will be examined with a real time electrical load network data. In previous research on IDVR [3]–[11], the simulations on IDVR were performed with a test power system. A basic power system network was considered and various possible ways of occurrence of sag were analysed. Using these results, the IDVR cannot be concluded as ideal device for mitigating voltage sag/swell. This is the fourth deviation observed. Hence in order to prove the reliability of IDVR, a real time electrical network load is to be considered. The real time data of would be the distribution network of BITS Pilani Hyderabad Campus. The efficiency of IDVR in compensating the voltage sags will be analysed in the network. This real time simulation of IDVR brings more practical weight towards the research on IDVR. Hence these are four major research gaps on IDVR to be addressed.

Considering the literature review on IDVR, the research gaps are identified. To address these research gaps, the objectives of the research are contributed as.

# 1.3 Aims and Objectives of the Research

- 1. Mathematical Modelling of IDVR: The main aim of IDVR is mitigation of power quality problems. In order to inject the required voltage for voltage sag mitigation, a controller has to be designed for IDVR which requires modelling of IDVR. The mathematical model includes the components of IDVR i.e. the inverter and DC link. The study and performing the calculations relating to methods of voltage compensation and control are done. The modelling of IDVR is discussed in chapter 3.

- 2. Incorporation of IDVR into a Power Distribution Network: Once the modelling of IDVR is established, it is incorporated in the power system network and its performance is to be investigated and analysed for voltage sag mitigation.

- 3. Restoring the DC link with PST and PV: The DC link of IDVR provides the required energy to the IDVR for mitigating the voltage sag, due to this the DC link energy diminishes. The restoration of the DC link energy of the IDVR is a weighted factor in the robust operation of IDVR. One of the methods employed is by utilizing the capacity of phase shifting transformer to shift the phase and controlling the power necessary to change the DC link. Additionally a PV system is utilized which is connected across the DC link to aid in the restoration process. A controlled algorithm is designed between PST and PV source depending upon the loading conditions of the feeder and surplus power available with the PV source respectively to replenish DC link energy.

- 4. IDVR Performance by replacement of VSI with CSI: The performance of IDVR with VSI and CSI as its building will be compared for a test power system. In addition the bidirectional compensation will be verified with the adopted controlling technique and replenishing using current source inverters.

- 5. Simulation of IDVR with Real Time Data: The adaptability of IDVR in real time scenario to be verified. The real time data of various loads in BITS Pilani Hyderabad Campus will be considered. The protection offered by the IDVR to the sentive loads is practically examined.

- 6. Experimental set up of IDVR: The simulation results of voltage sag and harmonics mitigation by IDVR is to be substantiated with experimental prototype model of IDVR. A small scale power distribution network is considered and effectiveness of IDVR in bidirectional compensation is to be proven.

Thus the IDVR mitigation of few power quality problems will be demonstrated.

# 1.4 Organization of the Research

The thesis is organised in the following chapters to report the results of the above studies.

Chapter 1: The summary of the problem addressed is described in this chapter. The aims and objectives of proposed research is covered in this thesis.

Chapter 2: In this chapter, a survey of the literature on various Power Quality issues are discussed. A review of various compensation techniques utilized to compensate the voltage sag and harmonics is described followed by the FACTS devices utilized for the voltage compensation is presented. Based on the literature survey, the chapter concludes highlighting the research gaps that are being taken forward in the successive chapters.

Chapter 3: This chapter discusses about the mathematical modelling of IDVR and its design. The design part of IDVR includes rating of individual inverter, DC link and the series injection transformer.

Chapter 4: This chapter establishes the control system developed for IDVR to compensate the voltage sag and the restoration of the DC link energy through the novel techniques by utilizing the phase shifting transformers (PST) and PV Source.

Chapter 5: In this chapter, voltage source inverters are replaced with current source inverters and the comparison of the two inverters as the building blocks of IDVR is performed in a test power system to mitigate voltage sag/swell.

Chapter 6: In this chapter, IDVR is simulated using a real time data. An IDVR is designed for a specific application at the network of BITS Pilani Hyderabad Campus to mitigate power quality problems.

Chapter 7: In this chapter, a laboratory prototype of IDVR is developed with the two feeder power system using VSI (semikron make) and DSPACE 1103 integrated with MATLAB to test

effectiveness of IDVR in mitigating voltage sag/swell in practical scenario.

Chapter 8: Finally, this chapter summarizes the specific contributions of the current study and conclusions gained from this research. Further, future scope and directions for research in this area is also been presented.

# Chapter 2

# **Literature Survey**

## 2.1 Introduction

This chapter gives the review of various conventional methods for mitigation of voltage sag and harmonics in the distribution side of power system. The limitations of the traditional devices are discussed. These limitations are overcome by FACTS devices. Various FACTS devices utilised on the distribution side are described. Finally the importance of Interline Dynamic Voltage Restorer in mitigating voltage sag and harmonics along with its literature review is covered.

Day by day the load demand is increasing at the distribution side. The loads of sensitive nature are increasing. Power Quality is a bigger concern to these sensitive loads. According to the Institute of Electrical and Electronics Engineers (IEEE) standards IEEE1100 defines power quality as the "concept of powering and grounding sensitive electronic equipment in a manner suitable for the equipment" [12]. The issues related to power quality faced by the sensitive loads on the distribution side are called power quality problems. There are many power quality problems on the distribution side. The major of the power problems occurring on the distribution side are

- 1. Transients

- 2. Interruptions

- 3. Sag / Under voltage

- 4. Swell / Overvoltage

- 5. Harmonics

- 6. Frequency variations

- 7. Voltage fluctuations

**Transients:** Sudden disturbance in AC waveform evidenced by a sharp, brief discontinuity of the waveform. Transients occur when there is a sudden change in voltage or current in power system.

**Interruptions:** A small disturbance in the voltage magnitude for a period of time. Interruptions can be short term and long term.

**Sag/Under voltage:** A reduction in the voltage magnitude for a small period of time is called voltage sag and if this reduction in the voltage magnitude last for more than 30 cycles it is referred to as under voltage.

**Swell/Over voltage:** An increment in the voltage magnitude for a small period of time is called voltage swell and if this increase in the voltage magnitude last for more than 30 cycles it is referred to as over voltage.

**Harmonics:** Harmonic distortion is the corruption of the fundamental sine wave at frequencies that are multiples of the fundamental.

**Frequency Variations:** Changes in the fundamental frequency are referred as frequency variations.

**Voltage fluctuations:** A sudden increase or decrease in the voltage magnitude for a very short duration are called voltage fluctuations.

Among the above mentioned power quality problems, the most severely occurring the power quality problems is voltage sag and harmoincs. According to the IEEE standards voltage sag is defined as "the drop in voltage magnitude from 10 to 90 percent of the nominal value for a duration of half cycle to one minute". Harmonics are referred as "superimposition of various frequencies over fundamental frequencies"[13]. Common causes of sags include starting large loads (such as one might see when they first start up a large air conditioning unit) and remote fault clearing performed by utility equipment. Similarly, the starting of large motors inside an industrial facility

can result in significant voltage drop (sag). A motor can draw six times its normal running current, or more, while starting. Creating a large and sudden electrical load such as this will likely cause a significant voltage drop to the rest of the circuit it resides on. The common cause of harmonics are power electronic loads, faults or any other malfunctions. The effects of voltage sag or harmonics are loss of data, frequent tripping of circuit breaker and most important damage of the sensitive loads. In the recent years sensitive loads are becoming more in number at the distribution side of the power system. These sensitive loads have low resistance towards the voltage sag/swell and get easily damaged when there is a voltage deviation.

To mitigate the voltage sag/swell and protect the sensitive loads, there are some traditional devices developed which are listed below,

- 1. Static Capacitors

- 2. Synchronous condensers

- 3. Shunt reactors

- 4. Voltage Regulators

## 2.1.1 Static Capacitors

Shunt or static capacitors shown in fig 2.1 are primarily used to improve the power factor in transmission and distribution network, resulting in improved voltage regulation, reduced network losses, and efficient capacity utilization. Improved transmission voltage regulation can be obtained during heavy power transfer conditions when the system consumes a large amount of reactive power that must be replaced by compensation [14]–[16].

At the line surge impedance loading level, the shunt capacitor would decrease the line losses by more than 30%. In distribution and industrial systems, it is common to use shunt capacitors to compensate for the highly inductive loads, thus achieving reduced delivery system losses and network voltage drop.

Fig. 2.1 Static Capacitor or shunt capacitor banks

# 2.1.2 Synchronous Condensers

An over excited synchronous machine running on no load is called is called synchronous condenser which is represented in fig 2.2. When the synchronous condenser is placed in parallel to the system it regulated the power factor by controlling the reactive power. By maintaining the reactive power the voltage regulation is possible. The reactive power taken by a synchronous motor depends on two factors, DC filed excitation and mechanical load delivered by the motor. Maximum leading power is taken by a synchronous motor with maximum excitation and zero load [17], [18].

Fig. 2.2 Synchronous Condenser

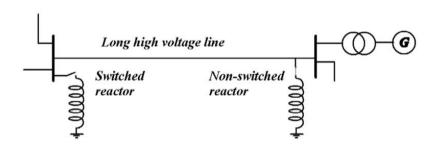

#### 2.1.3 Shunt Reactors

The primary purpose of the shunt reactor is to compensate for capacitive charging voltage, a phenomenon getting prominent for increasing line voltage. Long high voltage transmission lines and relatively short cable lines (since a power cable high capacitance to earth) generate a large amount of reactive power during light power transfer conditions which must be absorbed by compensation. Otherwise, the receiving terminals of the transmission lines will exhibit a voltage rise voltages. A better fine tuning of the reactive power can be made by the use of a tap changer in the shunt reactor .It can be possible to vary the reactive power between 50 to 100% of the needed power.

Fig. 2.3 Shunt Reactors

#### 2.1.4 Voltage Regulators

A voltage regulator generates a fixed output voltage of a constant magnitude regardless of changes to its input voltage or load conditions. There are two types of voltage regulators: linear and switching. A linear regulator employs an active (BJT or MOSFET) pass device (series or shunt) controlled by a high gain differential amplifier. It compares the output voltage with a precise reference voltage and adjusts the pass device to maintain a constant output voltage. A switching regulator converts the dc input voltage to a switched voltage applied to a power MOSFET or BJT switch. The filtered power switch output voltage is fed back to a circuit that controls the power

switch on and off times so that the output voltage remains constant regardless of input voltage or load current changes.

The traditional methods have advantages like

- 1. The usage of capacitor banks improves power factor along with voltage regulation

- 2. The installation of shunt reactors and series capacitors is easy.

- 3. All the devices can work under normal atmospheric conditions. No special temperature conditions should maintained for their function.

- 4. With the use of synchronous condensers faults can be removed easily because of the high thermal stability of the motor.

- 5. Simple and robust customer solution with low installation costs and minimum maintenance

However, the disadvantages of these traditional methods are

- 1. Short Service

- 2. The devices get easily damaged if the voltage exceeds the rated value.

- 3. Once damaged their repair is uneconomical.

- 4. Using synchronous condensers creates additional losses and noise.

- 5. As the synchronous motor has no self-staring torque, additional equipment has to be installed.

Due to these disadvantages the traditional devices are slowly replaced with Flexible AC Transmission Systems (FACTS) devices. The IEEE definition of FACTS devices is "a power electronic based system and other static equipment that provide control of one or more AC transmission system parameters to enhance controllability and increase power transfer capability"[19]. The early FACTS devices were mostly thyristor controlled devices. Most of the installed FACTS devices are the thyristor controlled reactor or capacitor based Static VAR Compensator (SVC), which mainly controls voltage by injecting to or absorbing reactive power

from the grid. With the drastic developments in the area of power electronics, the research on FACTS devices is mainly focused on Voltage Source Inverter (VSI) based devices. VSI utilizes self-commutated power electronics devices, such as GTOs and IGBTs, to invert the DC supply to AC supply.

The FACTS devices are used in both transmission and distribution side. The major FACTS devices utilized on the transmission side are [19]

- 1. Static Synchronous Compensator (STATCOM).

- 2. Static Synchronous Series Compensator (SSSC).

- 3. Unified Power Flow Controller (UPFC).

- 4. Interline Power Flow Controller (IPFC).

## 2.1.5 Static Synchronous Compensator (STATCOM)

A STATCOM shown in fig 2.4 is comparable to a Synchronous Condenser (or Compensator) which can supply variable reactive power and regulate the voltage of the bus where it is connected. STATCOM is a VSI in shunt connected to the grid. The VSI is controlled to inject or absorb reactive current to or from the grid, thus supporting the voltage and improving the system stability [20]–[23].

Fig. 2.4 Schematic diagram of STATCOM

Fig 2.4 represents the general configuration of STATCOM. The compensation provided by the STATCOM is with the exchange of reactive power, hence the active power capability of the STATCOM is very low.

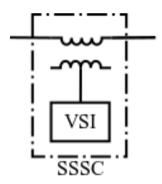

## 2.1.6 Static Synchronous Series Compensator (SSSC)

SSSC is a VSI connected in series with the grid through a transformer. The device injects voltage in series to the receiving end voltage to control power flow and thereby to improve the power oscillation damping on power grids. Fig 2.5 shows the configuration of SSSC. The operation of SSSC has some similarity to a controllable series capacitor and series inductor. The major difference is that its injected voltage is not related to the line intensity and can be managed independently. This primary feature allows the SSSC to work satisfactorily with high loads as well as with lower loads.

Fig. 2.5 Schematic diagram of SSSC

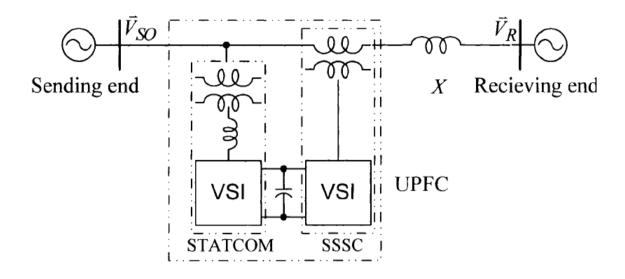

## 2.1.7 Unified Power Flow Controller (UPFC)

UPFC is the combination of a STATCOM and a SSSC by back-to-back connecting them together with a common DC link. With this combination, the UPFC inherits all the functions of the STATCOM and SSSC and maximize the operational region. UPFC mainly provides fast acting reactive power compensation on high voltage electricity transmission networks. The UPFC can control both active and reactive power flows in the transmission line. The controllable parameters by UPFC in the line are reactance in the line, phase angle and voltage. Fig 2.6 shows the

configuration of UPFC. As shown in fig 2.6 the series and shunt device share a common DC link. Therefore the active or reactive power needed by one device can be supplied by the other device [24]–[28].

Fig. 2.6 Schematic diagram of UPFC

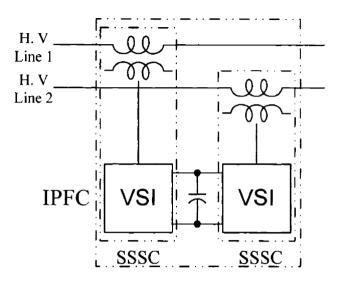

## 2.1.8 Interline Power Flow Controller (IPFC)

IPFC is designed for the compensation of active and reactive power in a multi-line transmission system. The VSIs share a common DC link, and are connected in series to different transmission lines. In other word, an IPFC is a combination of several SSSCs with one common DC link. Fig 2.7 gives the configuration of IPFC. In this structure, power flows from line to line through the DC link. With proper control, the power exchange between different lines can be conditioned and optimized. Similar to SSSC, an IPFC controls the grid's voltage, phase and impedance [29]–[32].

Fig. 2.7 Schematic diagram of IPFC

The table 2.1 summarizes the circuit structures of the FACTS devices on the transmission side.

Table 2.1: Summary of FACTS configuration on transmission side

| Number of Converters | Configuration                                      |

|----------------------|----------------------------------------------------|

| 1                    | Shunt                                              |

| 1                    | Series                                             |

| 2                    | Combined Shunt and Series  connected back to back  |

| 2                    | Combined Series and Series connected back to back. |

|                      | 1 2                                                |

The FACTS devices discussed are implemented in the transmission line. However, as the power quality issues are observed on the distribution side of the grid network, consequently FACTS devices installed on the distribution side to mitigate the power quality issues. These FACTS Devices on the distribution side are called custom power devices.

## 2.2 Custom Power

Custom power is the employment of power electronic or static controllers in medium and low voltage distribution systems for the purpose of supplying a level of reliability and/or power quality that is needed by electric power customers sensitive to power quality variations. In other words custom power is intended to protect the customers from interruptions and voltage reductions originating in the utility system as well as those transferred to customers from other customers via the utility system and even internal disturbances.

Custom power devices, or controllers, include static switches, active filters, DVRs, injection transformers, energy storage modules that have the ability to perform current interruption and voltage regulation functions in a distribution system to improve reliability and/or power quality.

In a Custom Power system customer should receive specified power quality from a utility or a service provider which includes an acceptable combination of the following features:

- No (or rare) power interruptions

- Magnitude and duration of voltage reductions within specified limits.

- Magnitude and duration of over voltages within specified limits.

- Low harmonic voltage.

- Low phase unbalance

The need for the Custom Power concept arises from the fact that:

1. Most of the interruptions and voltage reductions occur in the utility system on account of lightning faults on transmission and distribution lines, trees touching the wires, equipment failure, switching, etc. Voltage sag may also be a consequence of large load changes affecting customers own equipment or affecting other equipment via the utility system.

- 2. Impulses, switching surges and over voltages affecting the insulation, would most likely result from lightning strikes and switching events in the transmission and distribution system.

- 3. Temporary over voltages lasting from several cycles to several seconds would largely result from large load changes, capacitor switching, transformer switching, excessive leading-VARs during light loads, etc. in the utility system.

- 4. Voltage unbalances in a three-phase supply would occur mostly due to large unbalanced loads on a utility's distribution lines and long lines with unbalanced phase impedances.

- 5. Harmonics would most likely be the consequence of high harmonics in the customer load, or the saturation of a utility's transformers. These harmonics would then be amplified by the natural resonances in the utility system and/or the customer system.

#### 2.2.1 Custom Power Devices

Just as FACTS controllers improve the reliability and quality of power transmission systems, the custom power enhances the quality and reliability of power delivered to customer. Custom Power Devices are intended for improving the power quality of distribution networks against disturbances such as

- Sags, swells,

- Transients, harmonics.

The incorporation of the classical devices, such as D-STATCOM (Distribution Static Synchronous Compensator), DVR (Dynamic Voltage Restorer), and UPQC (Unified Power Quality Conditioner), means a continuous control, with a very fast response time, and they allow and assure an improvement in the wave quality of the power supply.

A DSTATCOM can compensate for distortion and unbalance in a load such that a balanced sinusoidal current flows in the feeder. A DVR can compensate for voltage sag/swell and distortion

in the supply side voltage such that the voltage across a sensitive/critical load terminal is perfectly regulated. A UPQC can perform the functions of both DSTATCOM and DVR.

# 2.3 Distribution STATCOM (DSTATCOM)

The DSTATCOM is basically one of the custom power devices. It is similar to STATCOM but used at the Distribution level. The key component of the DSTATCOM is a power VSC that is based on high power electronics technologies.

The Distribution STATCOM is a versatile device for providing reactive compensation in AC networks. The control of reactive power is achieved via the regulation of a controlled voltage source behind the leakage impedance of a transformer, in much the same way as a conventional synchronous compensator. However, unlike the conventional synchronous compensator, which is essentially a synchronous generator where the field current is used to adjust the regulated voltage, the DSTATCOM uses an electronic voltage sourced converter (VSC), to achieve the same regulation task. The fast control of the VSC permits the STATCOM to have a rapid rate of response [33]–[37].

Fig. 2.8 Schematic representation of the DSTATCOM

The DSTATCOM is the solid – state based power converter version of the SVC. Operating as a shunt – connected SVC, its capacitive or inductive output currents can be controlled independently

from its connected AC bus voltage. Because of the fast switching characteristic of power converters, the DSTATCOM provides much faster response as compare to SVC. DSTATCOM is a shunt connected, reactive compensation equipment, which is capable of generating and or absorbing reactive power whose output can be varied so as to maintain control of specific parameters of the electric power system. DSTATCOM provides operating characteristics similar to a rotating synchronous compensator without mechanical inertia, due to the DSTATCOM employ solid state power switching devices it provides rapid controllability of the three phase voltages, both in magnitude and phase angle.

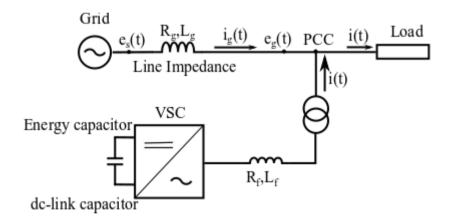

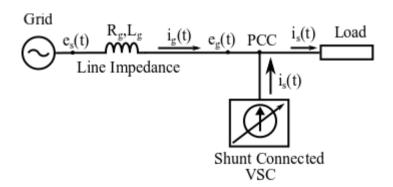

#### 2.3.1 Principle of operation of Shunt-Connected VSC

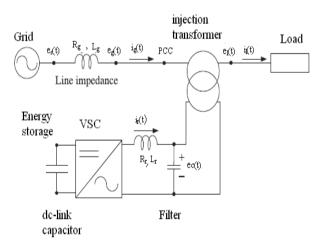

The basic idea of the shunt-connected VSC is to dynamically inject a current  $I_r(t)$  of desired amplitude, frequency and phase into the grid. The typical configuration of a shunt-connected VSC is shown in fig 2.9. The device consists of a VSC, an injection transformer, an AC filter and a DC link capacitor. Energy storage can also be mounted on the dc link to allow active power injection into the AC grid.

The line impedance has a resistance  $R_g$  and inductance  $L_g$ . The grid voltage and current are denoted by Es (t) and Ig (t), respectively. The voltage at the point of common coupling (PCC), which is also equal to the load voltage, is denoted by  $E_g(t)$  and the load current by  $i_I(t)$ . The inductance and resistance of the ac-filter reactor are denoted by  $L_r$  and  $R_r$  respectively.

Fig 2.10 shows a simplified single-line diagram, where the VSC is represented as a current source. Amplitude, frequency and phase of the current  $I_r(t)$  can be controlled. By injecting a controllable current, the shunt-connected VSC can limit voltage fluctuation leading to flicker and cancel harmonic currents absorbed by the load, thus operating as an active filter. In both cases, the principle is to inject a current with same amplitude and opposite phase as the undesired frequency components in the load current, so that they are cancelled in the grid current.

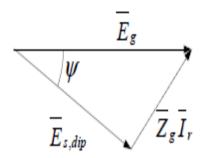

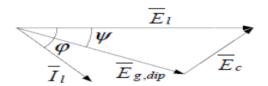

These mitigation actions can be accomplished by only injecting reactive power. A shunt-connected VSC can also be used for voltage dip mitigation. In this case, the device has to inject a fundamental current in the grid, resulting in increased voltage amplitude at the PCC, as shown in the phasor diagram in fig 2.11. The voltage phasor at PCC is denoted by  $E_g$ ,  $Z_g$  is the line impedance,  $E_s$ , dip is the grid voltage phasor during the dip and  $\Psi$  is the phase-angle jump of the dip. From the diagram it is possible to understand that when the shunt-connected VSC is used to mitigate voltage dips, it is necessary to provide energy storage for injection of active power in order to avoid phase-angle jumps of the load voltage.

If only reactive power is injected, it is possible to maintain the load voltage amplitude  $E_g$  to the prefault conditions but not its phase. Therefore, the voltage dip mitigation capability of a shunt-connected VSC depends on the rating of the energy storage and on the rating in current.

Fig. 2.9 Single line diagram of shunt connected VSC

Fig. 2.10 Simplified line diagram of shunt connected VSC

Fig. 2.11 Phasor diagram of voltage dip mitigation using shunt VSC

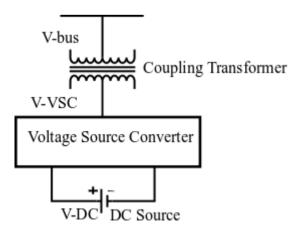

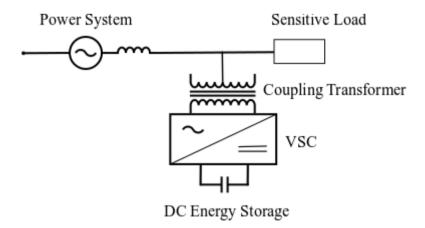

## 2.4 Dynamic Voltage Restorer (DVR)

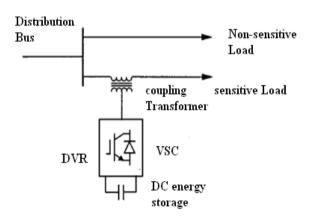

The DVR is a powerful controller that is commonly used for voltage sags mitigation at the point of connection. The DVR employs VSC, coupling Transformer and DC energy storage capacitor and the coupling transformer connected in series with the ac system, as illustrated in fig 2.12. The VSC generates a three-phase AC output voltage, which is controllable in phase and magnitude. These voltages are injected into the AC distribution system in order to maintain the load voltage at the desired voltage reference [37]–[43].

Fig. 2.12 Schematic representation of the DVR

The DVR is a solid state DC to AC switching power converter that injects a set of three single phase AC output voltages in series with the distribution feeder and in synchronism with the voltages of the distribution system. By injecting voltages of controllable amplitude, phase angle and

frequency (harmonic) into the distribution feeder in instantaneous real time via a series injection transformer, the DVR can restore the quality of voltage at its load side terminals when the quality of the source side terminal voltage is significantly out of specification for sensitive load equipment.

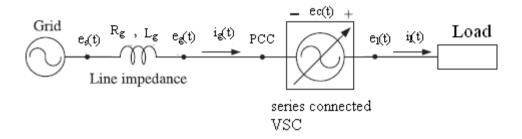

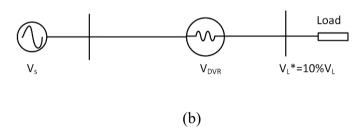

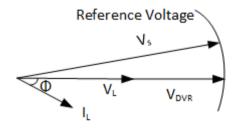

#### 2.4.1 Principle of operation of Series-connected VSC (DVR)

The basic idea involved in principle of operation is to inject a voltage  $e_c(t)$  of desired amplitude, frequency and phase between the Point of comon Coupling (PCC) and the load in series with the grid voltage. A typical configuration of the DVR is shown in fig.2.12. The simplified single-line diagram of the system with DVR is shown in fig 2.13. The DVR can be represented as a voltage source with controllable amplitude, phase and frequency.

The DVR is mainly used for voltage dip mitigation. The device maintains the load voltage  $E_{l}$  (t) to the pre-fault condition by injecting a fundamental voltage of appropriate amplitude and phase. Fig 2.11 shows the phasor diagram of the series injection principle during voltage dip mitigation, where Ec is the phasor of the voltage injected by the compensator,  $I_{L}$  is the phasor of the load current and where  $\Psi$  is the angle displacement between load voltage and current.

Fig. 2.13 Single line diagram of series connected VSC

In order to be able to restore both magnitude and phase of the load voltage to the pre-fault conditions, the DVR has to inject both active and reactive power. The voltage dip mitigation capability of this device depends on the rating of the energy storage and on the voltage ratings of the VSC and the injection transformer

Fig.2.14 Simplified line diagram of series connected VSC

Fig. 2.15 Phasor diagram of voltage mitigation using series VSC

The reactive power exchanged between the DVR and distribution system is internally generated by the DVR without any AC passive reactive components, i.e. reactors and capacitors. For large variations in the source voltage, the DVR supplies partial power to the load from a rechargeable energy source attached to the DVR dc terminal. The DVR, with its three single phase independent control and inverter design is able to restore line voltage to critical loads during sags caused by unsymmetrical L-G, LL, L-L-G, as well as symmetrical three phase faults on adjacent feeders or disturbances that may originate many miles away on the higher voltage interconnected transmission system. Connection to the distribution network is via three single-phase series transformers there by allowing the DVR to be applied to all classes of distribution voltages. At the point of connection the DVR will, within the limits of its inverter, provide a highly regulated clean output voltage.

## 2.5 Literature Survey of DVR

The basic topology under which DVR was classified as DVR with medium voltage and DVR with low voltage. In both systems the purpose of the DVR was mitigate the voltage sag but the difference between low and medium voltage level connection was the flow of zero sequence currents and generation of zero sequence voltages. DVR compensates the voltage sag by injecting the proper amount of voltage in series with supply voltage so that the load voltage is maintained within the specified limits [38], [44], [45]. The DVR consists of an energy storage device, series inverter which was coupled to the grid via series injection transformer. The control strategy for DVR majorly has two parts detection and determining the reference signal. The first one was mainly about the voltage sag detection in grid. There are different detection methods such as peak measurement, doo component measurement, phasor parameters estimation using kalman filtering or complex Fourier transformation [39], [46]–[48]. The second one was about the determination of the reference signal of the series injected voltage. The method to determine the reference signal generation depends upon the energy storage device that DVR contains.

The voltage sag compensation of DVR was classified into three methods; in phase compensation, pre-sag, energy minimized. The in phase compensation method is the straightest method of compensation where the injected voltage by the DVR was in phase with the source voltage irrespective of the pre fault condition [49]–[51]. The commonly used method of compensation was pre-sag compensation method. In this method, the load voltage was restored to level before the occurrence of the voltage sag. Since the load voltage was compensated to pre-sag condition, the compensation was done with respect to the magnitude as well with the phase. In the first two methods of compensation the active power was injected by the DVR. The injected power was supplied from the energy storage device at the DC link. Thus the active power should be supplied to DC link or the DC link voltage will be dropped. To avoid such pressure on the DC link, the next method of compensation is energy minimized compensation. The basic principle of this method was

injecting to or absorbing from power grid as much reactive power as possible to compensate the voltage sag. Therefore, the DVR voltage must be controlled in such a way that the DVR does not exchange active power with power grid and as result, the amount of active power needed from the dc-link can be minimized. Therefore with the three methods the DVR is able to compensate voltage sag able to maintain the load voltage to its specified value.

## 2.6 Unified Power Quality Conditioner (UPQC)

Poor power quality in a system could be due to different factors such as voltage sag, voltage swell, voltage outage and over correction of power factor and unacceptable levels of harmonics in the current and voltage. Modern solution for poor power quality is to take advantage of advanced power electronics technology [52]–[56].

Recent research efforts have been made towards utilizing a device called unified power quality conditioner (UPQC) to solve almost all power quality problems. The main purpose of a UPQC is to compensate for supply voltage flicker/imbalance, reactive power, and harmonics. In other words, the UPQC has the capability of improving power quality at the point of installation on power distribution systems or industrial power systems. The UPQC, therefore, is expected as one of the most powerful solutions to large capacity loads sensitive to voltage flicker/imbalance.

Unified Power Quality Conditioner (UPQC) for non-linear and voltage sensitive loads has following facilities.

- It eliminates the harmonics in the supply current, thus improves utility current quality for nonlinear loads.

- UPQC provides the VAR requirement of the load, so that the supply voltage and current are always in phase, therefore, no additional power factor correction equipment is necessary.

- UPQC maintains load end voltage at the rated value even in the presence of supply voltage sag.

• The voltage injected by UPQC to maintain the load end voltage at the desired value is taken from the same dc link, thus no additional dc link voltage support is required for the series compensator.

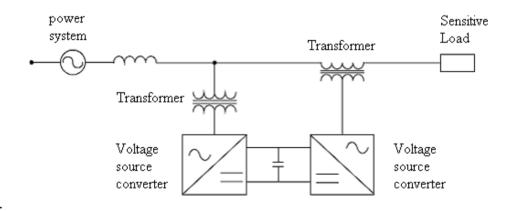

The UPQC in fig 2.16 consists of two three phase inverters (VSI) connected which are also known as active power filters in cascade in such a manner that one inverter is connected in parallel with the load. Second Inverter is connected in series with the supply voltage through a transformer.

The main purpose of the shunt compensator is to compensate for the reactive power demanded by the load, to eliminate the harmonic components of nonlinear loads in such a way that the source current is sinusoidal and balanced. This equipment is a good solution for the case when the voltage source presents distortion and a harmonic sensitive load is close to a nonlinear load.

The series compensator is operated in PWM voltage controlled mode. It injects voltage in quadrature advance to the supply voltage (current) such that the load end voltage is always maintained at the desired value. The two inverters operate in a coordinated manner.

Fig. 2.16 Basic Block Diagram of UPQC

If UPQC is connected between two feeders it would be called as Interline Unity Power Quality conditioner (IUPQC). This IUPQC comes under series-shunt facts device.

## 2.7 Literature Survey of UPQC

Initially there were two types of active power filters (APF) namely shunt APF and series APF. The shunt APF was mainly to tackle current related problems and series APF was manly to tackle voltage related problems. Moran[57] described a system configuration in which both series and shunt APFs were connected back to back with a common DC reactor. Fujita and Akagi[58] implemented the practical application of the topology proposed by Moran with 20 kVA experimental results. They named this device as unified power quality conditioner (UPQC).

Basic classification of UPQC was on physical structure and voltage sag compensation. There were majorly four methods of compensation of voltage sag by UPQC. First method of compensation with active power control. Reference [59]-[63] had represented active power control of UPQC to mitigate the voltage sag. In this method the voltage sag was injected in phase to the system. This inphase component was equal to make the load voltage magnitude to the desired level. The shunt inverter of UPQC draws the necessary active power required by the series inverter plus the losses associated with UPQC so that the effective sag compensation was achieved. The second method of compensation of voltage sag by UPQC was by injecting of the reactive power through series inverter of UPQC [64]–[66]. The injected voltage was by the series inverter of UPQC in quadrature to the source voltage such that the vector sum of source voltage and the injected voltage equals the required voltage of the load. With this method the need of the active power to compensate the voltage sag was eliminated. The injected voltage in this method was shifted to some angle so that the injected voltage is quadrature to the source voltage. The third type of compensation by UPQC was minimum Volt Ampere (VA) loading. In this method of compensation, the series voltage was injected at a certain optimal angle with respect to the source current instead of injecting in quadrature or in-phase [67]-[71]. The fourth method of compensation was simultaneous active and reactive power control. In this method the series inverter injects both real and reactive power. As the control both active and reactive power are involved the complexity in this method was more. This complexity was decreased with use of DSP processor. Hence with the described four methods, the voltage sag is compensated with UPQC. The literature review on DVR is covered in the following section.

## 2.8 Limitations to the DVR and UPQC

From the literature survey it can be concluded that the voltage sag mitigation in the distribution side can be successfully performed with both UPQC and DVR. Both of the devices inject the required voltage and maintains the load voltage to the set value. Hence the power quality at the distribution side of the power system can be improved with utilization of UPQC and DVR. The major limitation for DVR is the energy storage device at the DC link. Whenever the DVR needs to compensate the deeper voltage sags, the requirement of active power to mitigate the deeper sags is very huge. Hence there has to be larger DC links to supply the required active power to the DVR. Even during the multiple voltage sag conditions, the energy storage device is to be quite high to supply the required energy to the DVR. Hence the requirement of large DC links may not be economically good.

The distribution side contains multiple feeder line to which different loads are connected. The sensitivity of the loads are increasing in the modern days. Hence the power quality is to be ensured in all the feeders of the distribution side. For instance the voltage sag has occurred in two feeders which contain the sensitive loads at same time, the compensation of the voltage sag cannot be done with neither UPQC nor DVR, which implies the both UPQC and DVR are restricted to only one feeder. To ensure the power quality in all the feeders several DVRs or UPQCs have to be connected which also an economical problem. The feasible solution to these problems is an extended version of DVR known as Interline Dynamic Voltage Restorer (IDVR).

## 2.9 Interline Dynamic Voltage Restorer

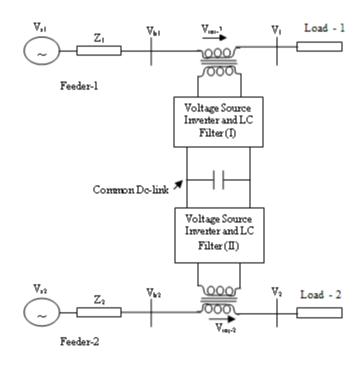

An Interline Dynamic Voltage Restorer (IDVR) comprises of two or more DVRs sharing a common DC link. The ability of IDVR is, it can simultaneously eliminate voltage sag/swells in different feeders at same instance of time with one common DC link and also when one of the DVR is mitigating deeper voltage sag, the required power can be supplied with another DVR. This will reduce the size of DC link which will also benefit economically.

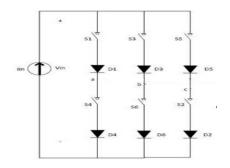

Fig. 2.17: Basic Layout of two line IDVR

A simple two feeder IDVR layout is shown in fig 2.17. It consists of two DVRs sharing a common DC link. The two DVRs of IDVR are connected to two different feeders with aid of series injection transformers. The building block of IDVR consists of a control system, voltage source inverter or current source inverter and the filter. The network shown in fig 2.17 contains two feeders. V<sub>b1</sub> and V<sub>b2</sub> are the bus voltages of feeder 1 and feeder 2 respectively. The two loads, Load 1 and Load 2 are considered as the sensitive loads connected to feeder 1 and feeder 2 respectively. For an instance a

voltage sag is assumed at the load 1, then the DVR 1 injects the voltages  $V_{inj1}$  to maintain the  $V_{l1}$  equal to  $V_{b1}$ .

The main advantage of IDVR over DVR is having low rating DC link. The concept of IDVR is if the primary DVR compensates the voltage sag/swell, the secondary DVR provides the required energy to mitigate the voltage sag. If the secondary DVR cannot supply the required energy to the DC link of IDVR, in such case the stored energy in DC link is utilised the by the primary DVR to mitigate the voltage sag. Hence the DC link energy has to be maintained constant. Therefore the main research on IDVR is focused on the restoration of its DC link energy. Apart from the restoration of DC link, the other contributions of research is on the control system of IDVR. The control system function is to mitigate the voltage sag as well monitor the DC link energy of IDVR. The various research work on IDVR is presented in the next section.

## 2.10 Literature Survey of IDVR

Different authors have proposed different methods for replenishing the energy at the DC link. Vilathgamuwa et.al [72] proposed an Interline Dynamic Voltage Restorer (IDVR) to mitigate voltage sag in a two line power system. The proposed IDVR consists of several DVRs connected to different feeders while sharing a common DC Link. When one of the DVR compensates for voltage sag appearing in that feeder, the other DVRs replenish the energy in the common DC link dynamically. Thus, one DVR in the IDVR system works in voltage-sag compensation mode while the other DVRs in the IDVR system operate in power-flow control mode. The authors designed a novel control strategy in which the phase angle of the reference voltages of the DVR shifts with certain angle. This phase shift increases the active power of the feeder which is used to replenish the DC link energy. They have also proposed a multi loop control systems to provide necessary reference signal voltages for shifting phase angle.

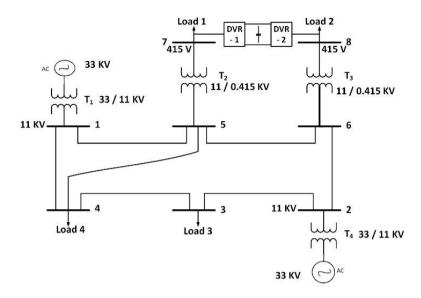

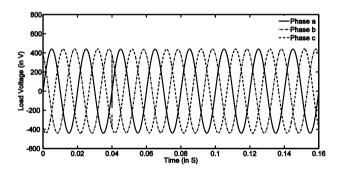

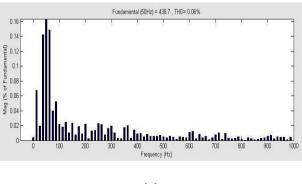

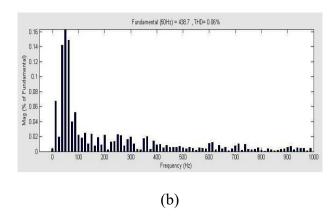

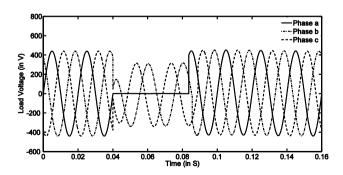

Ahmed Elserougi et.al [6] provided, the in-phase technique for two different types of loads i.e. constant impedance and three phase induction motor. Since the voltage restoration process may need real power injection into the distribution system. The power controller in one of the DVRs of IDVR, injects this power via voltage injection; this voltage injection was simulated by voltage drop across series virtual impedance. A new scheme was proposed to select the impedance value. The impedance value was selected such that the power consumed by this impedance represents the required power to be transferred without perturbing the load voltage. The performance of this system was also studied during voltage swell condition. The same author recently proposed an IDVR model to improve displacement factor by the exchange of real and reactive power between the feeders and IDVR [73].