## High Performance VLSI Architecture for Digital FIR Filter Design

### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

by

## SRINIVASA REDDY K

Under the supervision of

Dr. Subhendu Kumar Sahoo

## BIRLA INSTITUTE OF TECHNOLOGY & SCIENCE PILANI – 333 031 (RAJASTHAN) INDIA

2015

## High Performance VLSI Architecture for Digital FIR Filter Design

### **THESIS**

Submitted in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

by

## SRINIVASA REDDY K

ID.No. 2007PHXF430P

Under the supervision of

Dr. Subhendu Kumar Sahoo

## BIRLA INSTITUTE OF TECHNOLOGY & SCIENCE PILANI – 333 031 (RAJASTHAN) INDIA

2015

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN) INDIA

### **CERTIFICATE**

This is to certify that the thesis entitled "High Performance VLSI Architecture for Digital FIR Filter Design" and submitted by Mr. K Srinivasa Reddy, ID No. 2007PHXF430P for award of Ph.D. degree of the institute embodies original work done by him under my supervision.

Signature of the Supervisor

Name : **Dr. SUBHENDU KUMAR SAHOO**

Designation : Assistant Professor

Department of Electrical & Electronics Engineering

BITS – Pilani, Hyderabad Campus

| Date: |

|-------|

|       |

## Dedicated

to

My Family

## Acknowledgements

I wish to express my heart-felt gratitude and sincere thanks to my thesis supervisor Prof. Subhendu Kumar Sahoo, Department of Electrical and Electronics Engineering, BITS-Pilani, Hyderabad Campus for his able guidance, encouragement and continued support throughout the period of this research work. I have a deep sense of admiration to his innate goodness. It has been a divine grace and my proud privilege for me to work under his guidance.

I am indebted to Prof. V. S. Rao, Vice-Chancellor, Prof. Ashoke Kumar Sarkar, Director, Prof. G Sundar, Director, Off-Campus Programme, Prof. S. K. Verma, Dean, Academic Research Division, BITS, Pilani Campus for giving me an opportunity to carry out research at the Institute.

I wish to express my deep sense of gratitude to the members of Doctoral Advisory Committee (DAC), Prof. S. Gururnarayan and Prof. Sudeept Mohan, BITS-Pilani for their constructive criticism, valuable suggestions and moral support throughout the research work. Their editorial miracles of revision are simply amazing, without which the thesis would have not taken right shape.

My sincere thanks to Prof. Anu Gupta, Head of department Electrical & Electronics Engineering, BITS-Pilani, for her encouragement, and moral support during various phases of research work.

I am grateful for the best wishes and prayers of my friends cum colleagues Prof. V.K Choube, Prof. Surekha Bhanot, Prof. Dheerendra Singh, Prof. H. D. Mathur, Prof. Hari Om Bansal, Prof. Rajneesh Kumar, Prof. Navneet Gupta, Dr. Srinivas Kota, Dr. Rahul Singhal, Dr. Nitin Chaturvedi, Dr. Ananthakrishna Chintanpalli and Mr. Ananda Kumar A.

I express my heart-felt thanks to my friend cum colleague Mr. Pawan Sharma, for his valuable suggestions and support for accessing the OLAB and EDA tools during my research work. Special thanks to Mr. Giridhar Kunkur, Librarian, BITS-Pilani for making timely availability of various books and on-line journals.

A very special and sincere heartfelt gratitude to my parents, Mr. Kotha Hanumantha Rami Reddy and Mrs. Kotha Nagamaneswari, to my son Devesh and to my wife Mrs. Sirisha, whose constant persuasion and moral support have been a source of inspiration to me. No words can adequately express my gratitude to them.

## Abstract

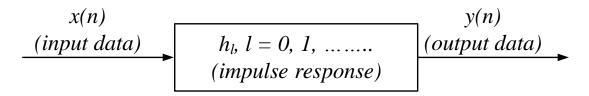

Finite impulse response (FIR) filters are the basic building blocks of many digital signal processing applications. The FIR filter receives a discrete time signal as input and performs the multiplication and addition operations to give the desired filtered discrete time output signal. The real time applications such as radar signal processing and video processing, require dedicated hardware efficient FIR filters to be implemented with higher clock frequencies. Nowadays, many battery operated devices such as hearing aids and mobile phones also use FIR filters as it offers stability and linear phase response. As these devices are power hungry devices, a low power FIR implementation is required for these applications. Hence, to meet the ever demanding high speed and low power devices, new methods for hardware efficient FIR filter architectures are proposed in this thesis. The FIR filter implementations are classified as fixed coefficient and programmable coefficient filter architectures. The hardware implementations of fixed and programmable filter architectures are different from each other. In this thesis, two new approaches for fixed coefficient and one improved architecture for programmable coefficient filter are proposed. In both fixed and programmable filter implementations, multiplier is the most expensive component in terms of hardware. In fixed coefficient filter implementation, replacement of the multiplier with the shift and adder circuits is a well-known technique. The adders in this approach are dependent on the number of one's or signed-power-of-two (SPT) terms present in each filter coefficient.

In the first method proposed in this thesis, differential evolution algorithm is used for reducing the number of SPT terms in filter coefficients. Then, with the help of a common subexpression elimination algorithm the number of adders is further minimized for efficient filter implementation. The performance of the proposed filter shows better results in comparison to some of the recently published work in terms of area, delay and power. One of the proposed filters is found to improve the power delay product gain by 29% as compared to the Remez algorithm.

In the residue number system (RNS), a large number is represented with a set of small numbers. The arithmetic computation using these small numbers reduces the critical path delay. In the second method proposed in this thesis, the advantage of RNS is exploited for fixed coefficient filter implementation. However, in RNS arithmetic, the input binary number is converted into residues using forward conversion circuit. In the proposed method a lookup table based approach is used for FIR filter implementation. This lookup table method eliminates the forward converter as well reduces the partial product generation time. Thus, this RNS based FIR filter improves the clock frequency of the filter. The synthesis results of the proposed RNS based filters have been compared with some recently published works. The results show significant improvement in area, power and delay gain.

In a programmable FIR filter, the filter coefficients are changed depending on the filter frequency response. Hence, shift and add approach is not applicable in programmable FIR filter. Several methods in the past have been reported for the reduction of partial products in a multiplier for filter design. One such method is computation sharing multiplication with pre-computed block. In this method, the coefficient is divided into a group of equal number of bits. For a group, all possible product values of the input are pre-computed. Then, for the coefficient multiplication, the pre-computed partial products of a coefficient are accumulated using carry propagate adder. In this thesis, a simple carry propagation free addition using compressors is proposed. The use of the compressors in place of carry propagate adder offers higher gain in delay, which improves the filter's performance. The proposed filter implementation has been compared with some recently published works and shows significant improvement in delay and power.

## Table of Contents

| List of Figures  List of Tables  List of Acronyms  1 Introduction 1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 1    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|

| List of Acronyms  1 Introduction 1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | iv   |

| List of Acronyms  1 Introduction 1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | ix   |

| 1 Introduction 1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               | xi   |

| 1.1 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | xiii |

| 1.2 Objectives and Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 1    |

| 1.2.1 Objectives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 3    |

| 1.2.2 Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 4    |

| <ul> <li>1.3 Outline of the Thesis</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | 5    |

| <ul> <li>2 FIR Filter Design using Differential Evolution</li> <li>2.1 General Overview of FIR Filter Design</li> <li>2.1.1 Specification of the filter requirements</li> <li>2.1.2 Calculation of the filter coefficients .</li> <li>2.1.3 Implementation of filter architecture</li> <li>2.2 Literature Review of Fixed Coefficient FIR Fixed 2.2.1 Literature Review</li> <li>2.3 Proposed Approach for FIR Filter Design</li> <li>2.3.1 Differential Evolution Algorithm</li> <li>2.3.2 DE algorithm for FIR filter</li> </ul> |               | 5    |

| <ul> <li>2.1 General Overview of FIR Filter Design</li> <li>2.1.1 Specification of the filter requirements</li> <li>2.1.2 Calculation of the filter coefficients .</li> <li>2.1.3 Implementation of filter architecture</li> <li>2.2 Literature Review of Fixed Coefficient FIR Fixed 2.2.1 Literature Review</li> <li>2.3 Proposed Approach for FIR Filter Design</li> <li>2.3.1 Differential Evolution Algorithm</li> <li>2.3.2 DE algorithm for FIR filter</li> </ul>                                                           |               | 7    |

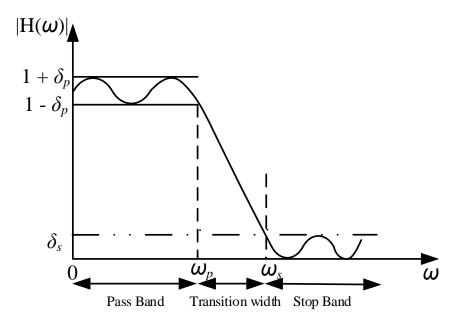

| <ul> <li>2.1.1 Specification of the filter requirements</li> <li>2.1.2 Calculation of the filter coefficients</li> <li>2.1.3 Implementation of filter architecture</li> <li>2.2 Literature Review of Fixed Coefficient FIR F.</li> <li>2.2.1 Literature Review</li> <li>2.3 Proposed Approach for FIR Filter Design</li> <li>2.3.1 Differential Evolution Algorithm</li> <li>2.3.2 DE algorithm for FIR filter</li> </ul>                                                                                                          | ion Algorithm | 8    |

| 2.1.2 Calculation of the filter coefficients .  2.1.3 Implementation of filter architecture  2.2 Literature Review of Fixed Coefficient FIR F.  2.2.1 Literature Review                                                                                                                                                                                                                                                                                                                                                            |               | 8    |

| <ul> <li>2.1.3 Implementation of filter architecture</li> <li>2.2 Literature Review of Fixed Coefficient FIR F.</li> <li>2.2.1 Literature Review</li> <li>2.3 Proposed Approach for FIR Filter Design</li> <li>2.3.1 Differential Evolution Algorithm</li> <li>2.3.2 DE algorithm for FIR filter</li> </ul>                                                                                                                                                                                                                        | s             | 9    |

| <ul> <li>2.2 Literature Review of Fixed Coefficient FIR F.</li> <li>2.2.1 Literature Review</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                              |               | 10   |

| <ul> <li>2.2.1 Literature Review</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               | 11   |

| <ul> <li>2.3 Proposed Approach for FIR Filter Design</li> <li>2.3.1 Differential Evolution Algorithm</li> <li>2.3.2 DE algorithm for FIR filter</li> </ul>                                                                                                                                                                                                                                                                                                                                                                         | Filter        | 12   |

| <ul><li>2.3.1 Differential Evolution Algorithm</li><li>2.3.2 DE algorithm for FIR filter</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                 |               | 14   |

| 2.3.2 DE algorithm for FIR filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 18   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | 19   |

| 2.4 Design Illustration and Simulation Results .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 23   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | 25   |

| 2.4.1 Initialization and Population                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               | 26   |

## TABLE OF CONTENTS

|   |     | 2.4.2  | Mutation                                                  | 26  |

|---|-----|--------|-----------------------------------------------------------|-----|

|   |     | 2.4.3  | Design of FIR Filter using DE Algorithm                   | 30  |

|   | 2.5 | Concl  | usion                                                     | 37  |

| 3 | RN  | S-Base | ed Fixed Coefficient FIR Filters                          | 38  |

|   | 3.1 | Introd | luction on RNS                                            | 39  |

|   |     | 3.1.1  | Forward Conversion                                        | 40  |

|   |     | 3.1.2  | Modulo Addition                                           | 42  |

|   |     | 3.1.3  | Modulo Multiplication                                     | 48  |

|   | 3.2 | RNS I  | Based fixed coefficient FIR Filters                       | 53  |

|   | 3.3 | Select | ion of the Moduli Set                                     | 67  |

|   | 3.4 | Propo  | sed Modular Multiplication                                | 70  |

|   |     | 3.4.1  | Conventional Modular Multiplication ( $\mathit{CMM}$ )    | 70  |

|   |     | 3.4.2  | New Modular Multiplication $(NMM)$                        | 73  |

|   | 3.5 | Archit | tectures of Proposed RNS-FIR Filter                       | 77  |

|   |     | 3.5.1  | Conventional RNS (RNSC) FIR Filter architecture           | 77  |

|   |     | 3.5.2  | Proposed RNS Based FIR Filter Architectures               | 78  |

|   | 3.6 | Imple  | mentation And Results                                     | 92  |

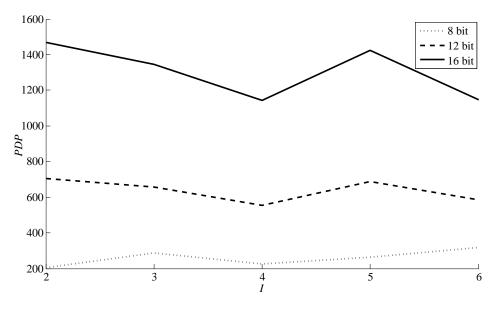

|   |     | 3.6.1  | Selection of optimum grouping size $I$                    | 92  |

|   |     | 3.6.2  | Implementation and Synthesis Results                      | 94  |

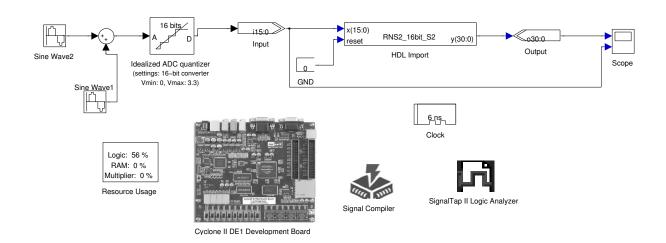

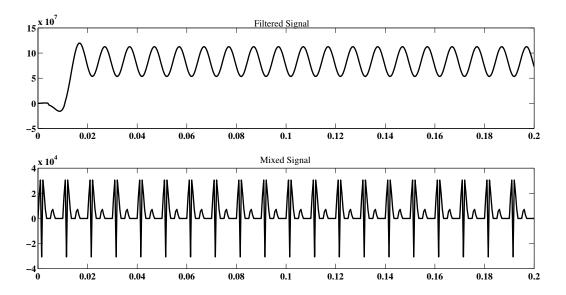

|   |     | 3.6.3  | Functional Verification                                   | 99  |

|   | 3.7 | Concl  | usion                                                     | 101 |

| 4 | Pro | gramn  | nable FIR Filters                                         | 102 |

|   | 4.1 | Introd | luction to Programmable FIR Filter                        | 102 |

|   |     | 4.1.1  | FIR Filter using CSHM Multiplier                          | 103 |

|   |     | 4.1.2  | FIR Filter using Constant Shift Method ( $\mathit{CSM}$ ) | 107 |

|   | 4.2 | Propo  | sed FIR Filter Architecture                               | 110 |

|   |     | 4.2.1  | Modified Processing Element $(MPE)$ Architecture          | 112 |

## TABLE OF CONTENTS

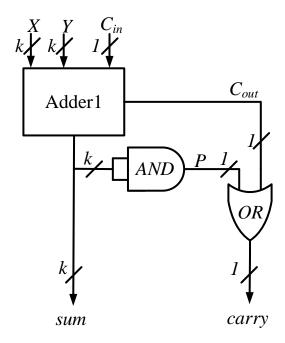

|    |                                   | 4.2.2 Structural Compressors $(SC)$ | 117 |

|----|-----------------------------------|-------------------------------------|-----|

|    | 4.3                               | Experimental Results                | 118 |

|    | 4.4                               | Conclusion                          | 124 |

| 5  | Con                               | clusions and Future Work            | 125 |

|    | 5.1                               | Conclusions                         | 126 |

|    | 5.2                               | Future Work                         | 128 |

| Re | efere                             | nces                                | 130 |

| Li | List of Publications              |                                     | 145 |

| Bı | Brief Biography Of The Candidate  |                                     | 148 |

| Bı | Brief Biography Of The Supervisor |                                     | 149 |

## List of Figures

| 1.1  | A Conventional Digital Filter Representation                                      | 2  |

|------|-----------------------------------------------------------------------------------|----|

| 2.1  | Characteristics of a Low-Pass Filter                                              | 9  |

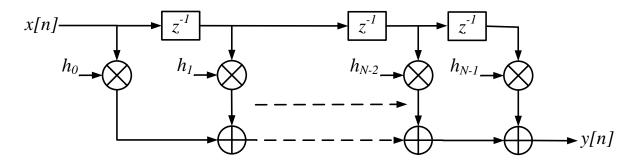

| 2.2  | Direct Form Structure                                                             | 11 |

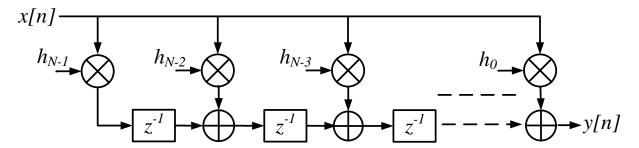

| 2.3  | Transposed Direct Form Structure                                                  | 12 |

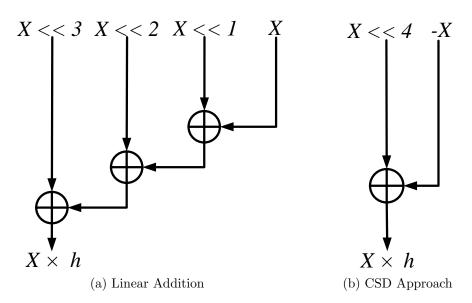

| 2.4  | Coefficient Multiplication with Adders                                            | 14 |

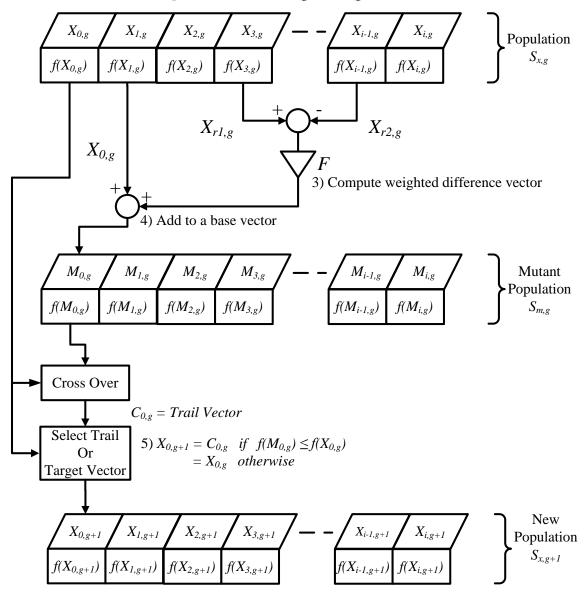

| 2.5  | Flow Chart for DE                                                                 | 20 |

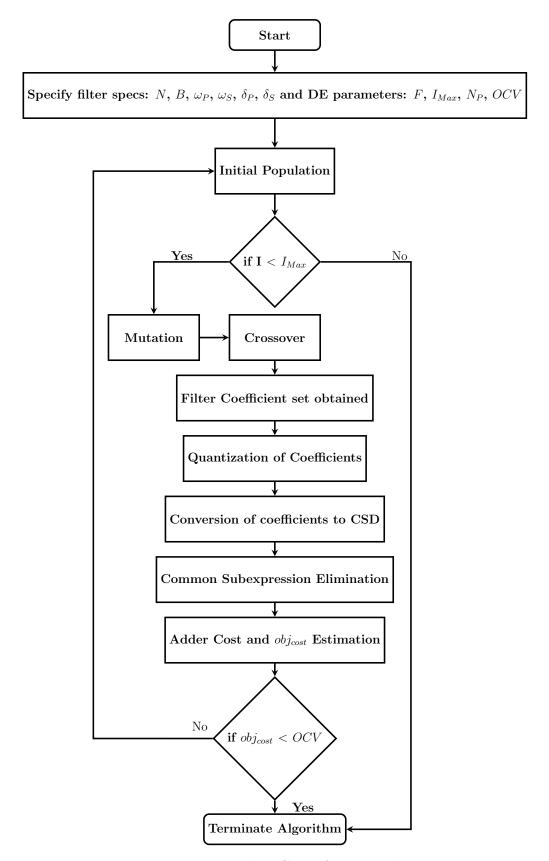

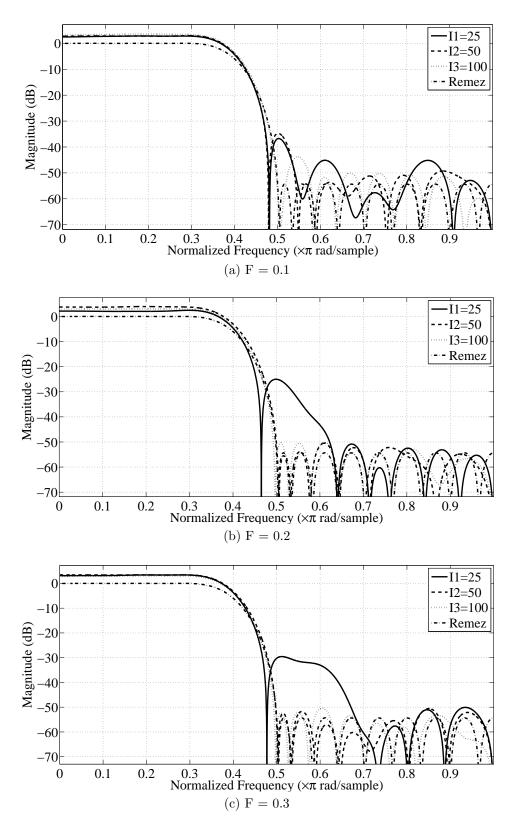

| 2.6  | DE Flow Chart for FIR Filter                                                      | 24 |

| 2.7  | Magnitude Responses of LPF for Mutant Factor 'F = 0.1, 0.2, 0.3'                  | 27 |

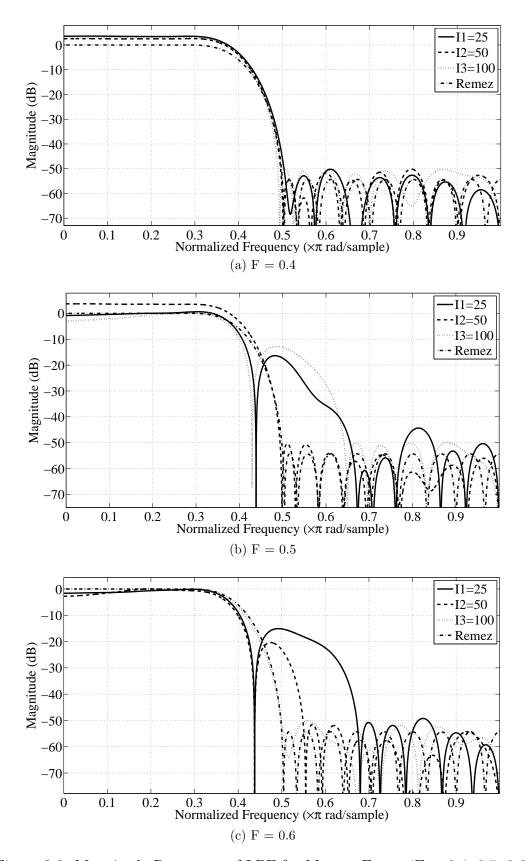

| 2.8  | Magnitude Responses of LPF for Mutant Factor 'F = 0.4, 0.5, 0.6'                  | 28 |

| 2.9  | Magnitude Responses of LPF for Mutant Factor 'F = $0.7,0.8,0.9,1$ '               | 29 |

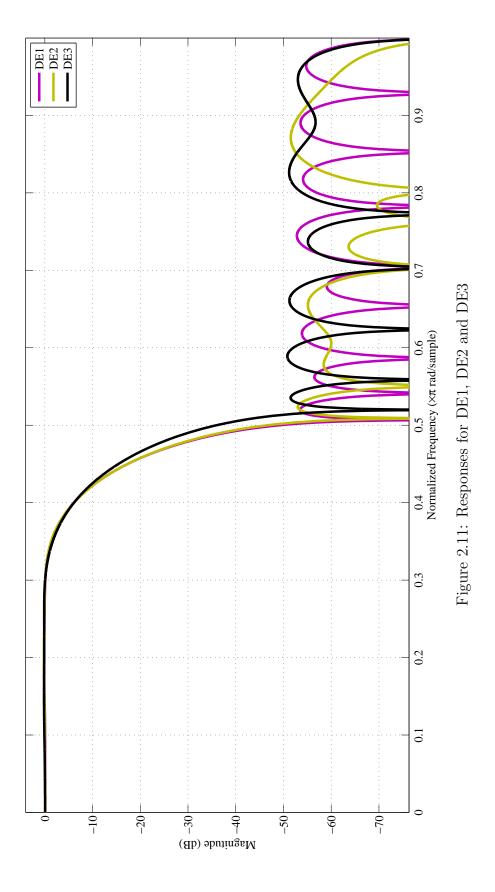

| 2.10 | Responses of Remez, Xu, Yu, Shi, DE1, DE2 and DE3                                 | 33 |

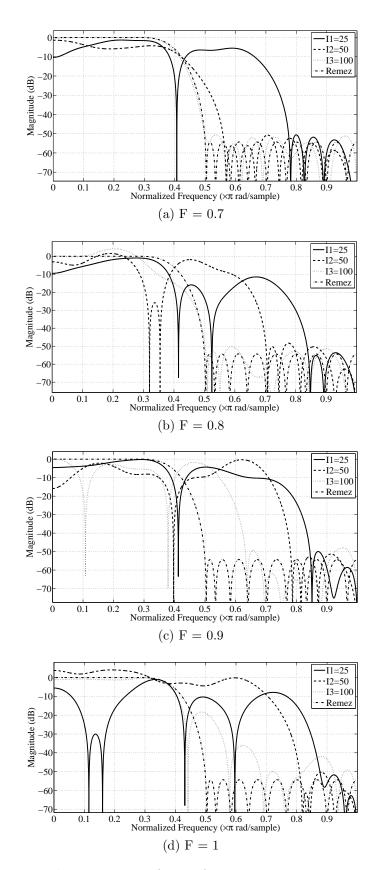

| 2.11 | Responses for DE1, DE2 and DE3                                                    | 34 |

| 3.1  | A Typical RNS based Arithmetic System                                             | 39 |

| 3.2  | Forward Converter                                                                 | 41 |

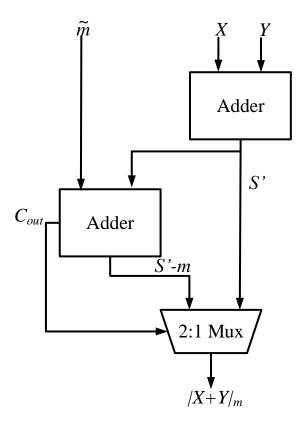

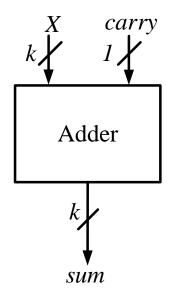

| 3.3  | Basic Modulo Adder                                                                | 42 |

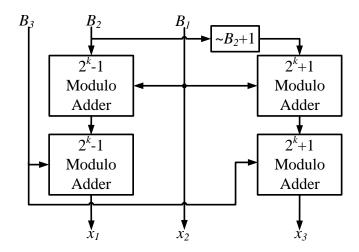

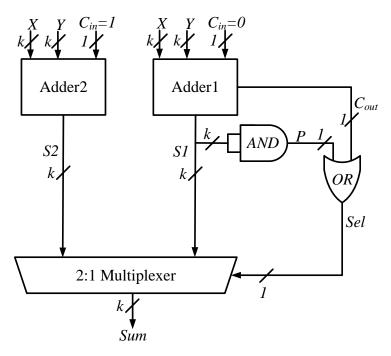

| 3.4  | $2^k-1$ Modulo Adder                                                              | 43 |

| 3.5  | $2^k - 1$ MA Example for Case 1                                                   | 44 |

| 3.6  | $2^k - 1$ MA Example for Case 2                                                   | 44 |

| 3.7  | $2^k - 1$ MA Example for Case 3                                                   | 45 |

| 3.8  | $2^k + 1 \text{ Mod Adder} \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 46 |

| 3.9  | $2^k + 1$ MA Example for Case 1                                                   | 47 |

| 3.10 | $2^k + 1$ MA Example for Case 2                                                   | 47 |

| 3.11 | $2^k + 1$ MA Example for Case 3                                                   | 48 |

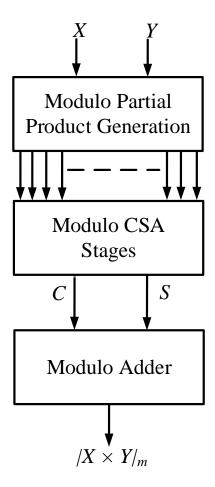

| 3.12 | Basic Modulo Multiplier                                                           | 49 |

## $LIST\ OF\ FIGURES$

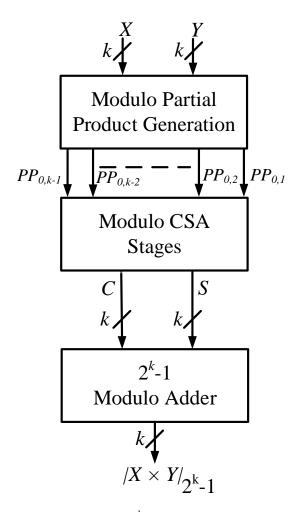

| 3.13 | $k \text{ Bit } 2^k - 1 \text{ Modulo Multiplier } \dots \dots \dots \dots \dots \dots$ | 50  |

|------|-----------------------------------------------------------------------------------------|-----|

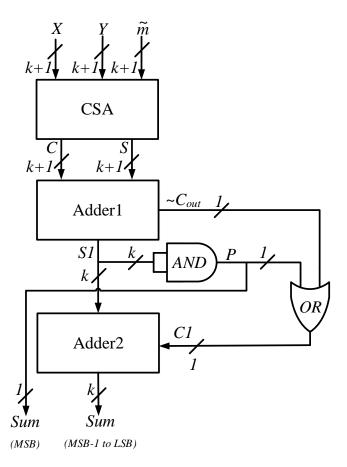

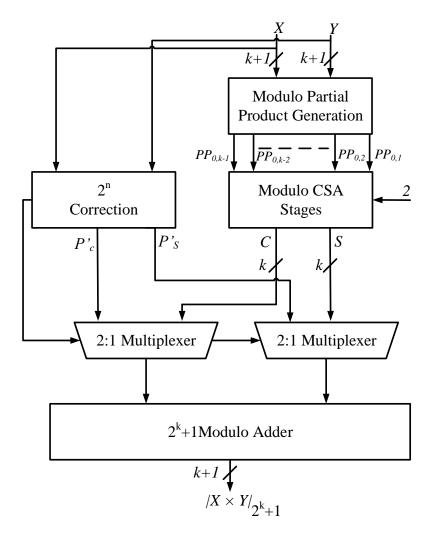

| 3.14 | $k+1$ Bit $2^k+1$ Modulo Multiplier                                                     | 52  |

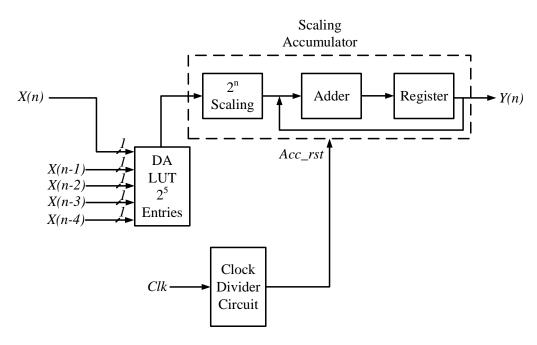

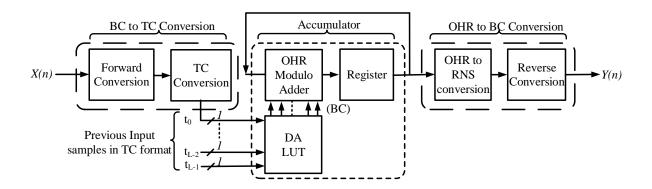

| 3.15 | FIR Filter Implementation using DA LUT                                                  | 56  |

| 3.16 | DA RNS Filter for $N=5$                                                                 | 61  |

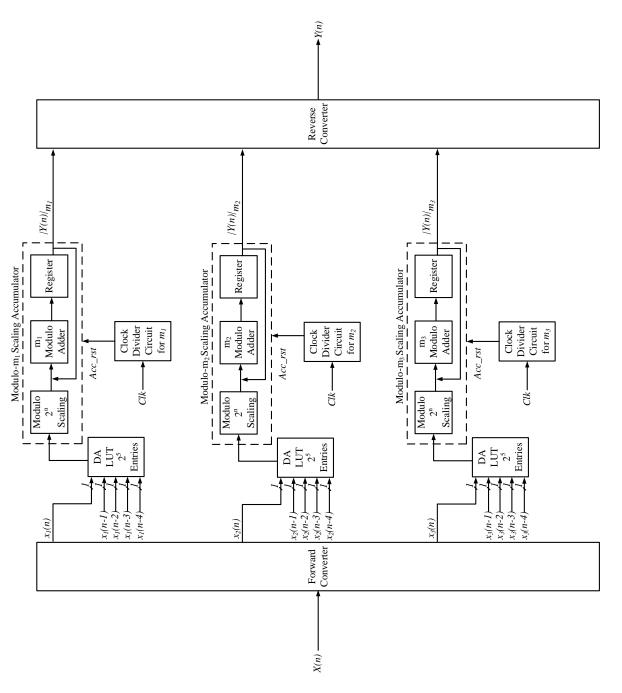

| 3.17 | DA RNS FIR Filter                                                                       | 62  |

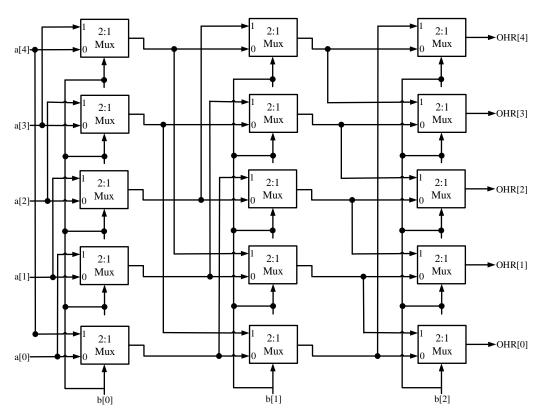

| 3.18 | OHR Modulo adder for modulus 5                                                          | 64  |

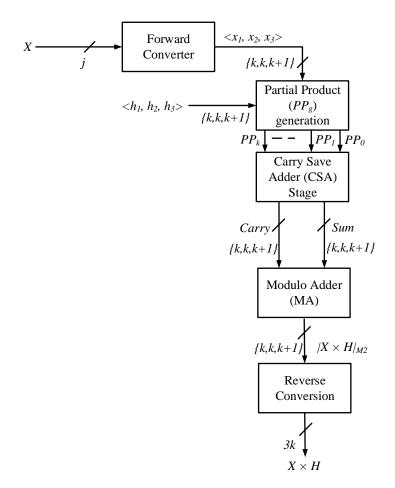

| 3.19 | A Standard Conventional Modular Multiplication                                          | 71  |

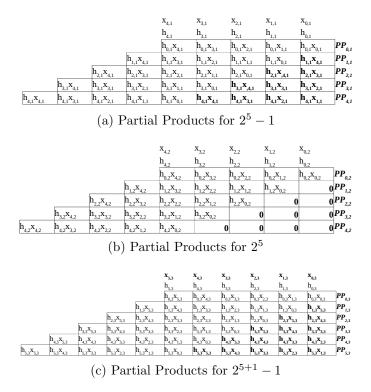

| 3.20 | Partial Products for $\{2^5 - 1, 2^5, 2^{5+1} - 1\}$                                    | 72  |

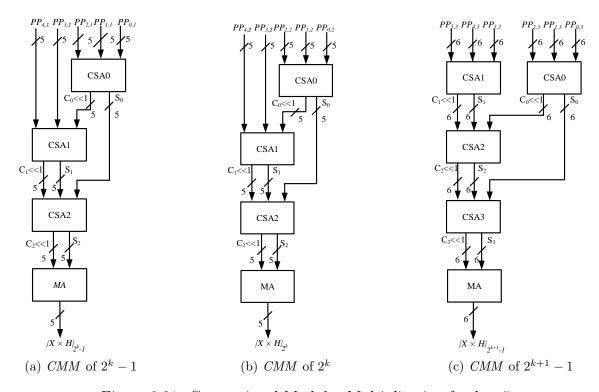

| 3.21 | Conventional Modular Multiplication for $k=5$                                           | 72  |

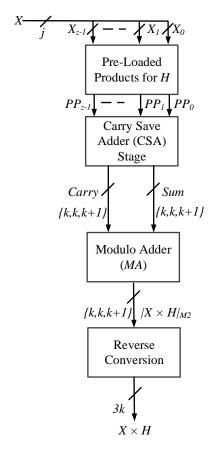

| 3.22 | New Modular Multiplication                                                              | 74  |

| 3.23 | NMM for a $j=8$ and $I=4$                                                               | 75  |

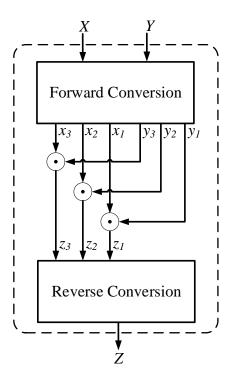

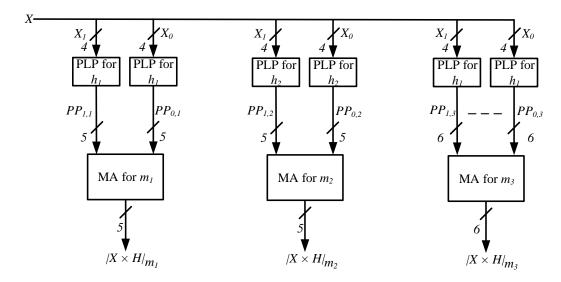

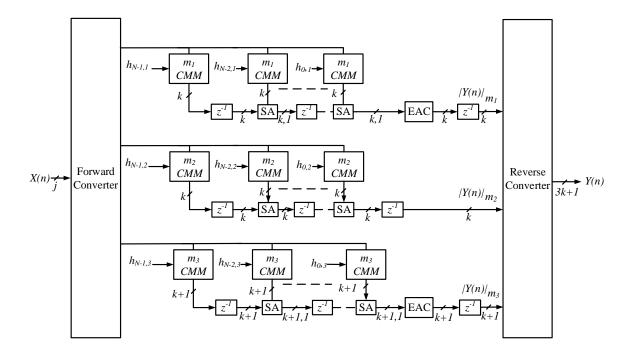

| 3.24 | RNSC Filter Architecture                                                                | 78  |

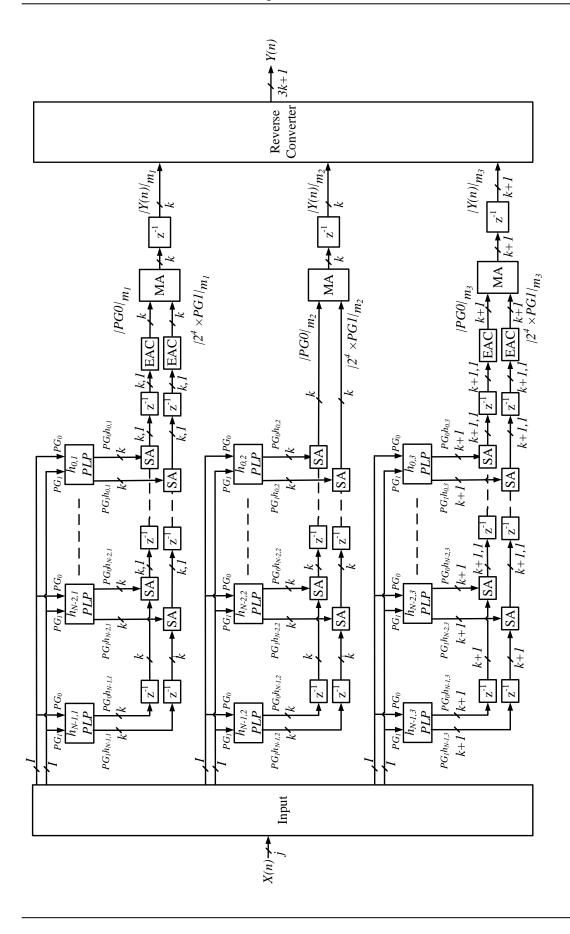

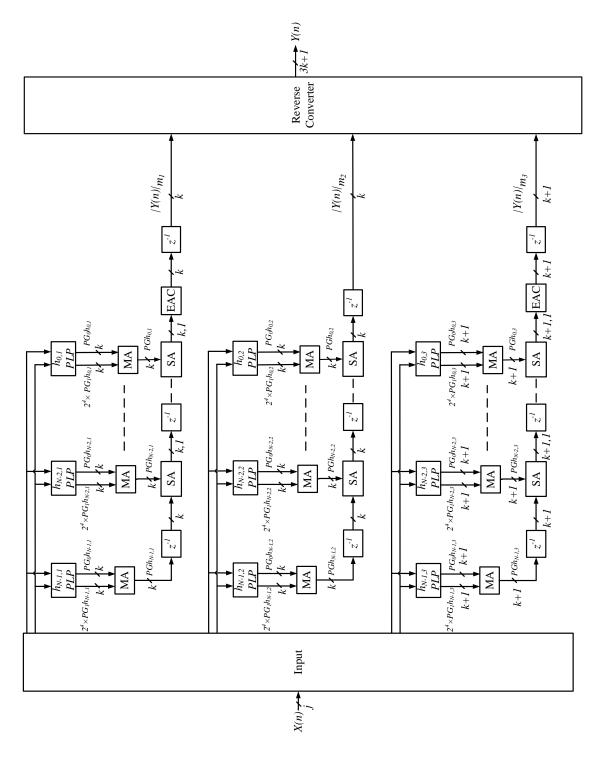

| 3.25 | Proposed Architecture RNS1 for 8-bit $X(n)$                                             | 80  |

| 3.26 | Proposed Architecture RNS2 for 8-bit $X(n)$                                             | 81  |

| 3.27 | Structural Adder (SA) for $2^k - 1$                                                     | 85  |

| 3.28 | End Around Carry (EAC) Adder for $2^k-1$ Modulus                                        | 85  |

| 3.29 | I Vs PDP                                                                                | 94  |

| 3.30 | Filter Implementation in Altera DSP Builder                                             | 99  |

| 3.31 | Input and Output Waveforms of S2 Filter                                                 | 100 |

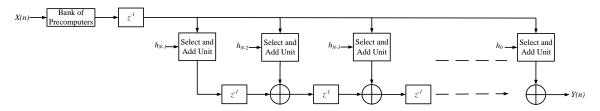

| 4.1  | FIR Filter using CSHM Multiplier                                                        | 103 |

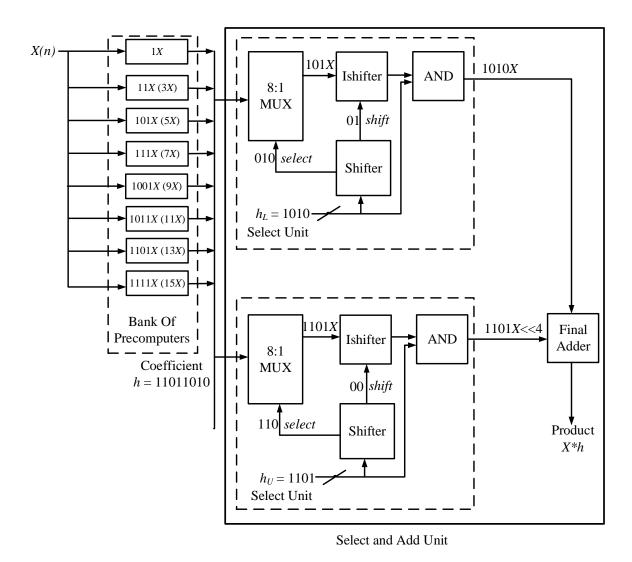

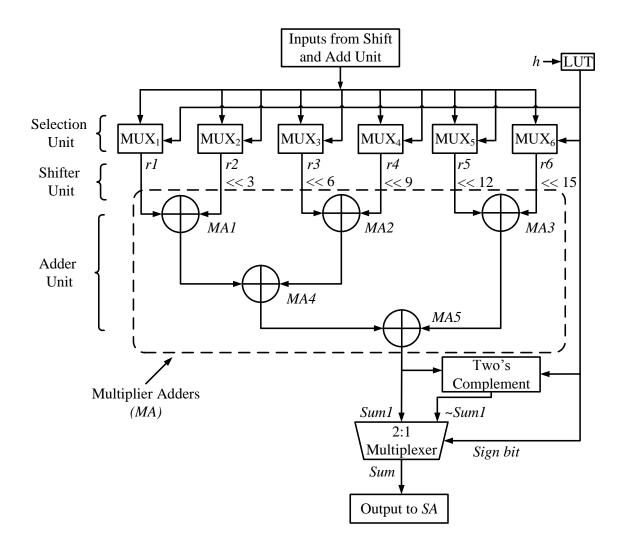

| 4.2  | CSHM Multiplier                                                                         | 104 |

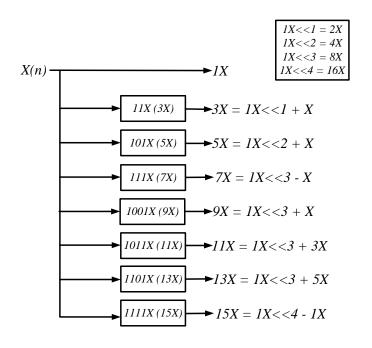

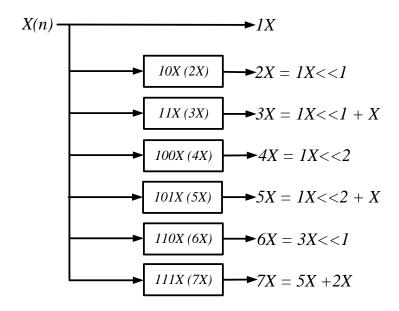

| 4.3  | Bank of Precomputers                                                                    | 105 |

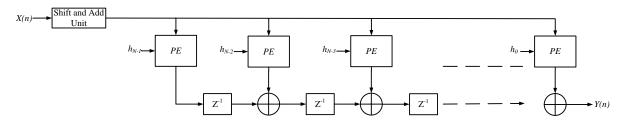

| 4.4  | FIR Filter using CSM                                                                    | 108 |

| 4.5  | Shift and Add Unit                                                                      | 108 |

| 4.6  | Processing Element for a 16 bit Coefficient                                             | 109 |

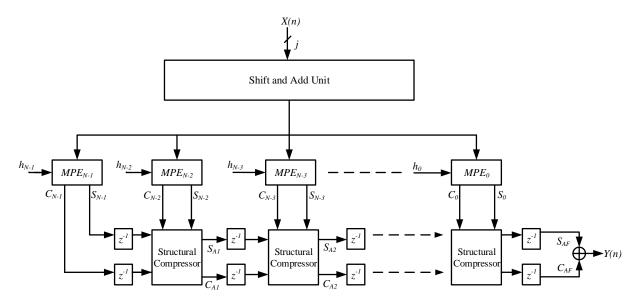

| 4.7  | Proposed FIR Filter Architecture                                                        | 111 |

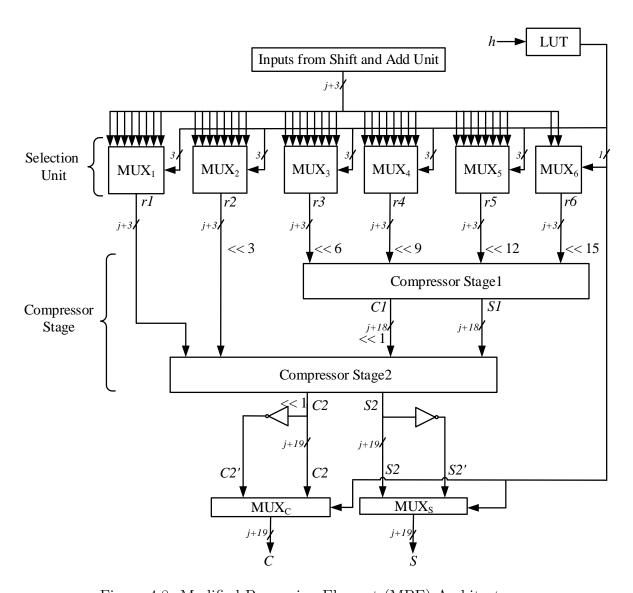

| 4.8  | Modified Processing Element (MPE) Architecture                                          | 113 |

## LIST OF FIGURES

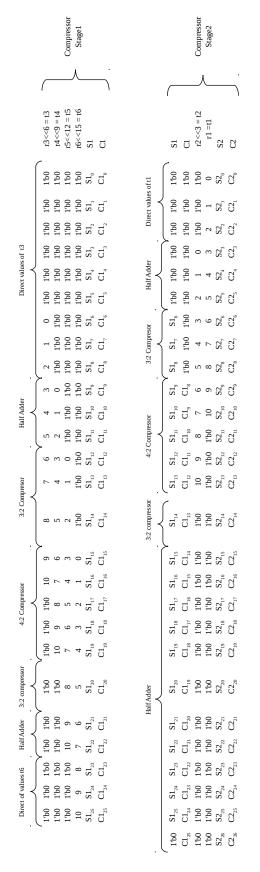

| 4.9  | Sum, Carry generation using Compressor Stages | 115 |

|------|-----------------------------------------------|-----|

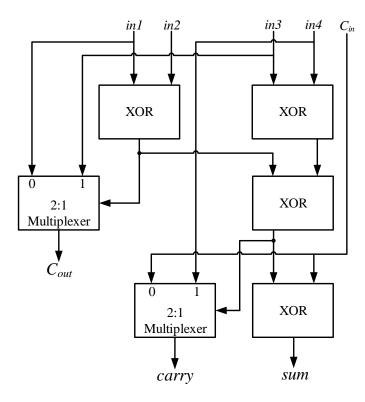

| 4.10 | Logic Diagram of 4:2 Compressor               | 116 |

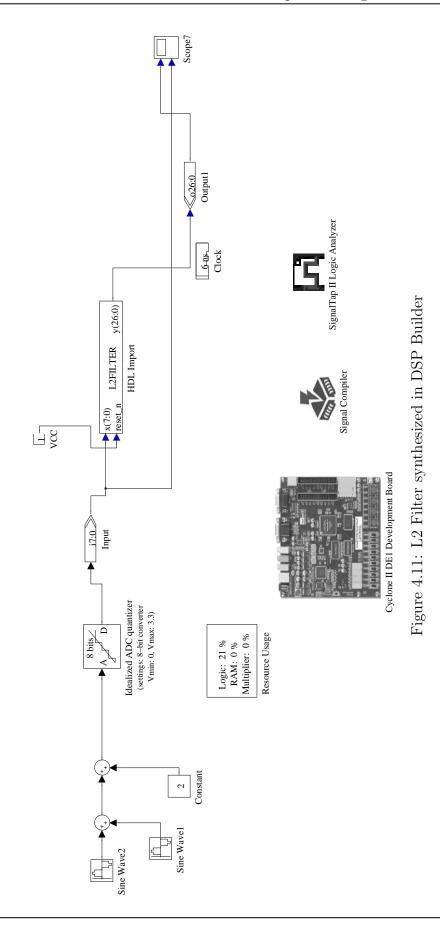

| 4.11 | L2 Filter synthesized in DSP Builder          | 121 |

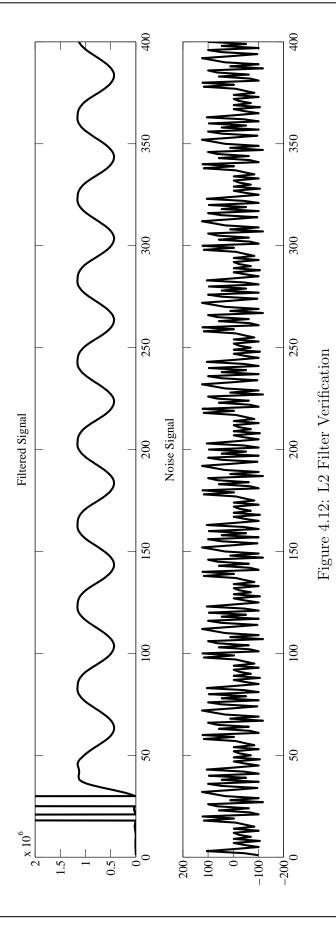

| 4.12 | L2 Filter Verification                        | 122 |

## List of Tables

| 2.1  | FIR filter Coefficients                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Properties of the designed filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32  |

| 2.3  | Synthesis Results of the designed filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36  |

| 3.1  | DA LUT For $N=5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 57  |

| 3.2  | Input Samples For FIR Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 58  |

| 3.3  | Execution of DA FIR Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59  |

| 3.4  | Input Samples for RNS DA FIR Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63  |

| 3.5  | DA LUT For $x_1 = 5$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65  |

| 3.6  | Execution of RNS DA FIR Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 66  |

| 3.7  | Modulo $2^n$ Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 68  |