# A Comparative Study of High Performance CMOS Multipliers, Barrel Shifters and Modeling of NBTI Degradation in Nanometer Scale Digital VLSI Circuits

# THESIS

Submitted in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

by

# **ABHIJIT RAMESHWAR ASATI**

Under the supervision of

# Dr. CHANDRA SHEKHAR

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE

PILANI (RAJASTHAN) INDIA

2009

# A Comparative Study of High Performance CMOS Multipliers, Barrel Shifters and Modeling of NBTI Degradation in Nanometer Scale Digital VLSI Circuits

# THESIS

Submitted in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

by

# **ABHIJIT RAMESHWAR ASATI**

Under the supervision of

# Dr. CHANDRA SHEKHAR

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE

# PILANI (RAJASTHAN) INDIA

2009

### ACKNOWLEDGMENTS

I thank Prof. L. K. Maheshwari, Vice-Chancellor BITS, Pilani and Director, BITS, Pilani (Pilani Campus) for providing me the necessary infrastructure, facilities and constant inspiration.

I wish to convey my sincere gratitude to my supervisor Dr. Chandra Shekhar, Director, CEERI, Pilani, for introducing me to the area of data path exploration, providing me able guidance, helping me understand the concepts and continuously encouraging me and providing moral support.

I sincerely thank Prof. Kewal K. Saluja, professor, department of electrical and computer science engineering, university of Wisconsin Madison, for introducing me to the area of NBTI degradation in CMOS digital logic circuits and supporting me with the suitable degradation models.

I thank my Doctoral Advisory Committee (DAC) members, Prof. S. Gurunarayanan and Dr. Anu Gupta, who spared their valuable time to go through my draft thesis and were audience to my pre-submission seminar in order to provide several valuable suggestions that immensely helped in improving the quality of my PhD thesis report.

I thank Prof. K. E. Raman, Director, BITS, Pilani (Goa Campus), Prof. G. Raghurama, Deputy Director (Academics), Prof. R. K. Mittal Deputy Director (Administration), Prof. Ravi Prakash, Dean (Research and Consultancy Division), Prof. A. K. Sarkar, Dean (Instruction Division), Prof. S. Gurunarayanan, Dean (Faculty Division-II), and Prof. R.N. Saha, Dean (Educational Development Division), Prof. B. V. Babu, Dean (Engineering Hardware Division), Prof. Rajiv Gupta, Dean (Engineering Services Division), for providing necessary administrative help.

I specially thank Prof. B. R. Natarajan, Dean (DLPD), for his sincere help and affectionate enquiries about my work to boost my spirit for the research work.

I wish to express my deep gratitude to Prof. Surekha Bhanot, Unit chief (Instrumentation) for her kind and affectionate enquiries about the work and continuous encouragement.

I express my sincere thanks to Prof. V. K. Choubey, Group Leader (Electrical and Electronics Engineering Group), for giving invaluable suggestions from time to time. I especially wish to express my deep gratitude to Dr. Anu Gupta, BITS, for providing me moral support and help in learning various related software tools. I wish to express my sincere thanks to Dr. Shikha Tripathi, Group Leader (Instrumentation Group) for providing me help in various forms for the completion of the present work.

I wish to express my sincere thanks to Dr. S. C. Bose, Scientist, CEERI, Pilani, for providing me excellent technical suggestions on high-speed, low-power VLSI design techniques.

I wish to express my sincere thanks to Mr. Raj Singh, Scientist, CEERI, Pilani, for providing me help on cell based design approach and physical design related issues.

I thank all the senior faculty members of Electrical and Electronics Engineering Group and Instrumentation Group along with my colleagues for their kind support in completion of this research work.

I thank Dr. Hemanth Jadav, Mr. Dinesh Kumar, Ms. Monica Sharma, Mr. Sharad Shrivastava, Mr. Gunjan Soni, Mr. Amit Kumar and Ms. Sunita Bansal, nucleus members of Research and Consultancy Division, BITS, Pilani, without their cooperation and guidance it would not have been possible for me to pursue such goal oriented research during each of the past few semesters.

I also express my gratitude to the office staff of Research and Consultancy Division whose secretarial assistance helped me in submitting the various evaluation documents in time and give pre-submission seminar smoothly.

I am thankful to Mr. Pawan Sharma, in-charge, OYESTER LAB, BITS, for his invaluable help.

I am thankful to my parents, my brother, my wife and my son for their constant help and moral support.

Lastly, I express my thanks to all those who directly or indirectly contributed to the completion of this work.

Abhijit Rameshwar Asati

### BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE

### PILANI, RAJASTHAN

## **CERTIFICATE**

This is to certify that the thesis entitled "A Comparative Study of High Performance CMOS Multipliers, Barrel Shifters and Modeling of NBTI Degradation in Nanometer Scale Digital VLSI Circuits" and submitted by Mr. ABHIJIT RAMESHWAR ASATI, ID. No. 2002PHXF040, for award of Ph. D. Degree of the Institute, embodies original work done by him under my supervision.

Signature in full of the Supervisor

Dr. CHANDRA SHEKHAR (Name in capital block letters)

Director, Central Electronics Engineering Research Institute

(Designation)

Date:

### ABSTRACT

The objective of this thesis is to explore the design space of two specific data path elements (viz multipliers and barrel shifters) of different bit width at architectural-level, at logic design level, and at transistor size level to select proper architecture, logic design style and physical device sizes; keeping in a view their effects on performance (circuit delay), average power consumption and core area.

The multipliers and barrel shifters are the fundamental data path elements required in high performance 'Standard Digital Signal Processors' and 'ASIC Digital Signal Processors' used for digital signal processing (DSP). Different multiplier and barrel shifter architectures show trade-offs between propagation delay, average power consumption and transistor counts. In deep sub-micron technologies, the simple gate-level analyses are inadequate to validate particular data path architectures. In this thesis we considered the effects of wiring parasitics and MOS parasitics in the assessment of architecture. The selected word widths for different multiplier and barrel shifter architectures are 4-bit, 8-bit, 12-bit and 16-bit; which dominate in DSP applications.

A schematic and physical library consisting of functional cells was defined for static CMOS logic design style, transmission gate (TG) logic design styles, dual rail domino logic design style and true single phase clock (TSPC) logic design style. Versions of the physical libraries were developed using three different sizes of transistors. The layout assemblies for the 4-bit, 8-bit, 12-bit and 16-bit multiplier and barrel shifter circuits were carried out using these cell libraries using automatic place and route tool LEDIT (SPR) from M/s Tanner Research Inc. The circuit delay and average power dissipation then analyzed for each implementation of the multiplier and barrel shifter circuit using the same logic design style but utilizing three different physical libraries differing in their transistor sizes as described above. Maximum instantaneous power, core area, total routing length and number of vias were also analyzed for each implementation for highlighting the very large scale integration (VLSI) implementation characteristics.

Further in nanometer scale digital integrated circuits negative bias temperature instability (NBTI) related circuit performance degradation was studied. The NBTI stress makes P-channel metal oxide semiconductor (PMOS) devices slower over time due to change in their threshold voltages. In deep sub-micron technologies the NBTI degradation decides the lifetime of CMOS circuits; In this thesis we present a novel Verilog HDL based

circuit modeling method that incorporates NBTI degradation dynamically. This technique will help the designers to include NBTI degradation effects in their circuit analysis efforts.

## **TABLE OF CONTENTS**

| iii  |

|------|

| V    |

| vi   |

| viii |

| xii  |

| xiv  |

| xvi  |

|      |

| CHAPTER 1- INTRODUCTION                                     | 1 |

|-------------------------------------------------------------|---|

| 1.1 Background                                              | 1 |

| 1.2 Objective of Thesis                                     | 3 |

| 1.3 Different Data Path Elements Considered For Exploration | 4 |

| 1.3.1 Multipliers                                           | 4 |

| 1.3.2 Barrel Shifter                                        | 5 |

| 1.4 Research Gaps                                           | 5 |

| 1.5 Research Methodology/Work-Plan                          | 7 |

| 1.6 Thesis Structure                                        | 8 |

| 1.7 Chapter Summary                                         | 9 |

### **CHAPTER 2- A DESIGN PHILOSOPHY OF MULTIPLIER AND BARREL**

| SHIFTER CIRCUITS                                                      | 10                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 Array Multiplier                                                  | 11                                                                                                                                                                                                                                                                                                             |

| 2.2 Wallace Tree                                                      | 13                                                                                                                                                                                                                                                                                                             |

| 2.3 Booth's Algorithm                                                 | 15                                                                                                                                                                                                                                                                                                             |

| 2.4 Array of Array Multiplier                                         | 19                                                                                                                                                                                                                                                                                                             |

| 2.5 Different Multiplier Architectures Considered for Exploration     | 19                                                                                                                                                                                                                                                                                                             |

| 2.6 Barrel Shifter Design Philosophy and Architectures Considered for |                                                                                                                                                                                                                                                                                                                |

| Exploration                                                           | 20                                                                                                                                                                                                                                                                                                             |

| 2.7 Chapter Summary                                                   | 20                                                                                                                                                                                                                                                                                                             |

|                                                                       | <ul> <li>2.1 Array Multiplier</li> <li>2.2 Wallace Tree</li> <li>2.3 Booth's Algorithm</li> <li>2.4 Array of Array Multiplier</li> <li>2.5 Different Multiplier Architectures Considered for Exploration</li> <li>2.6 Barrel Shifter Design Philosophy and Architectures Considered for Exploration</li> </ul> |

| CHAPTER 3- | DIFFERENT MULTIPLIER AND BARREL SHIFTER                                 |    |

|------------|-------------------------------------------------------------------------|----|

| P          | ARCHITECTURES                                                           | 21 |

| 3.1        | Baugh Wolley Multiplier                                                 | 21 |

| 3.2        | Booth Encoded Wallace Tree Multiplier                                   | 25 |

|            | 3.2.1 Multiplication Logic                                              | 25 |

|            | 3.2.2 Implementation Technique                                          | 29 |

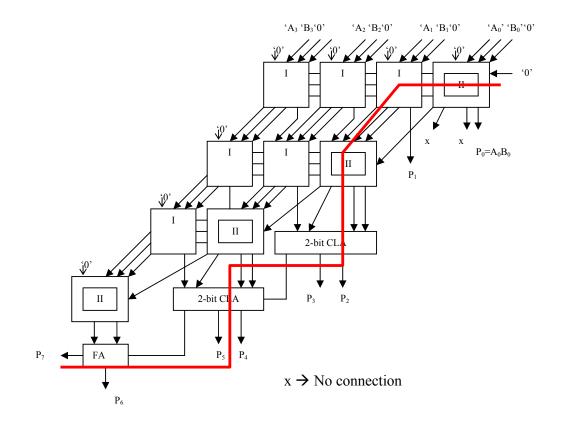

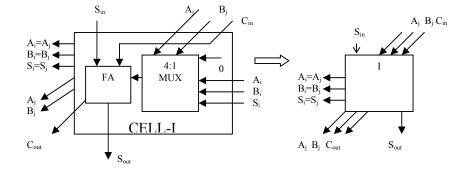

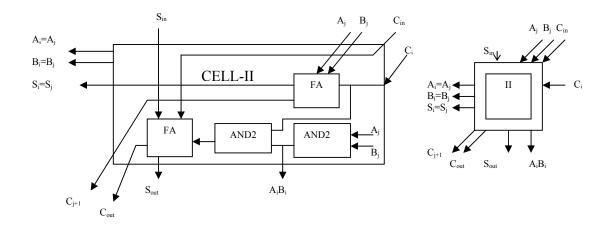

| 3.3        | MUX Based multiplier                                                    | 38 |

|            | 3.3.1 Multiplication Logic                                              | 38 |

|            | 3.3.2 An Illustration of the Multiplication Logic                       | 39 |

|            | 3.3.3 Implementation                                                    | 41 |

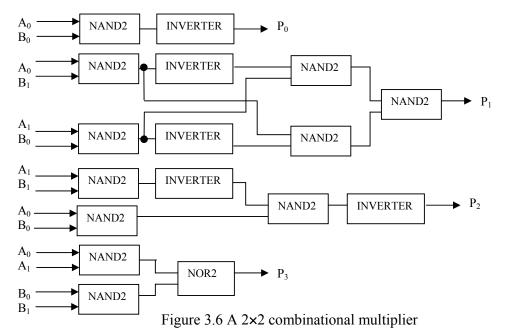

| 3.4        | 2×2 Cell Based Multiplier                                               | 43 |

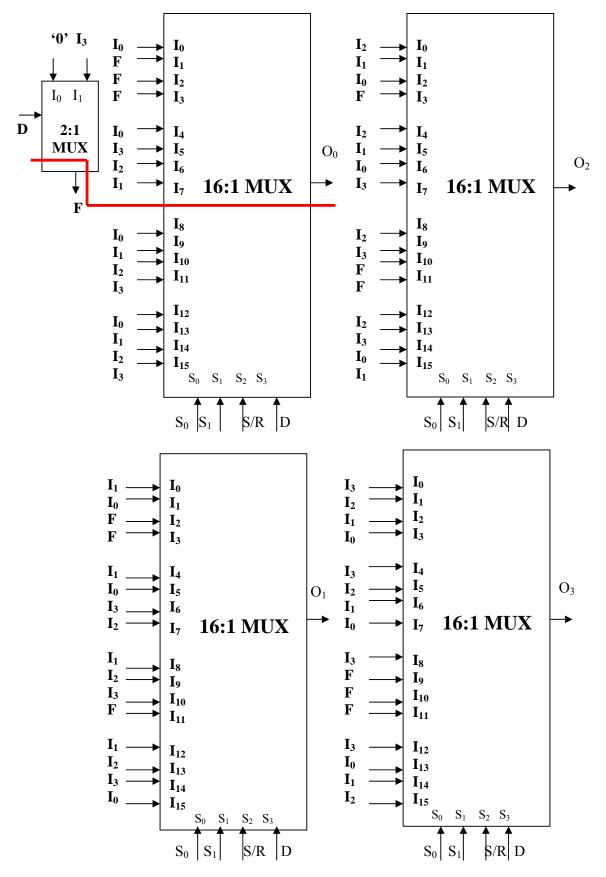

| 3.5        | MUX based Barrel Shifter                                                | 47 |

|            | 3.5.1 Design of 4-bit MUX-based Barrel Shifter                          | 47 |

|            | 3.5.2 Fill Bit Logic                                                    | 48 |

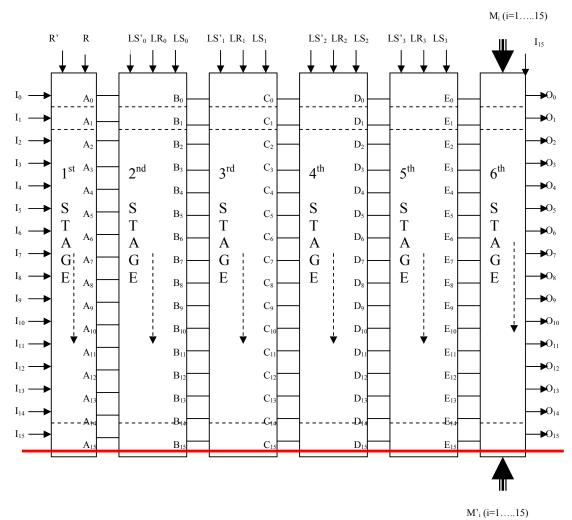

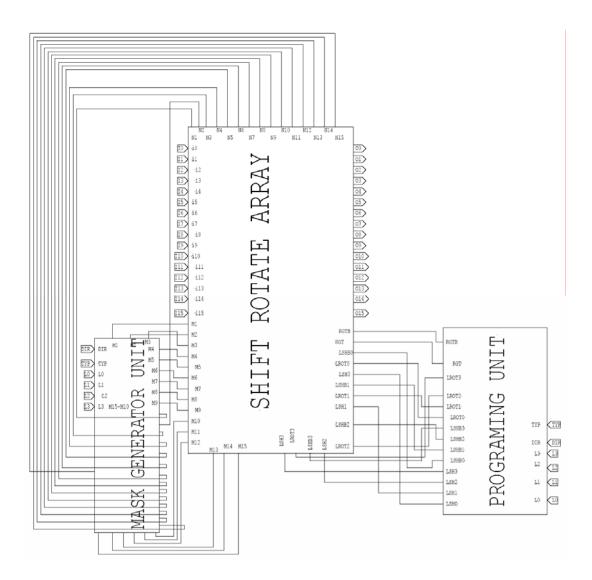

| 3.6        | Pereira's Barrel Shifter                                                | 50 |

|            | 3.6.1 Shift-Rotate array                                                | 50 |

|            | 3.6.2 Programming Unit                                                  | 55 |

|            | 3.6.3 Mask Generator Unit                                               | 55 |

|            | 3.6.4 Schematic and Operation                                           | 56 |

|            | 3.7 Chapter Summary                                                     | 57 |

| CHAPTER 4- | DIFFERENT CMOS LOGIC DESIGN STYLES AND                                  |    |

| ·<br>·     | DETRMINATION OF PMOS/NMOS WIDTH RATIO                                   |    |

|            | FOR HIGH SPEED DESIGN                                                   | 58 |

| 4.1        | Static CMOS Logic Circuits                                              | 58 |

|            | 4.1.1 Static Logic Design Style                                         | 59 |

|            | 4.1.2 TG Logic Design Style                                             | 60 |

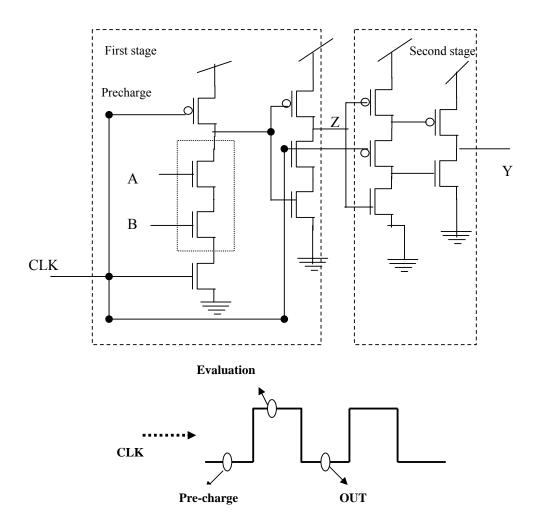

| 4.2        | Dynamic CMOS Logic Circuits                                             | 61 |

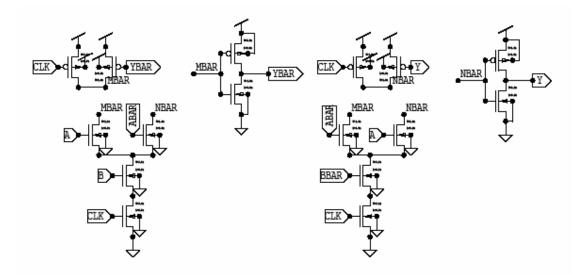

|            | 4.2.1 Domino and Dual Rail Domino Logic Design Style                    | 62 |

|            | 4.2.2 TSPC Logic Design Style                                           | 64 |

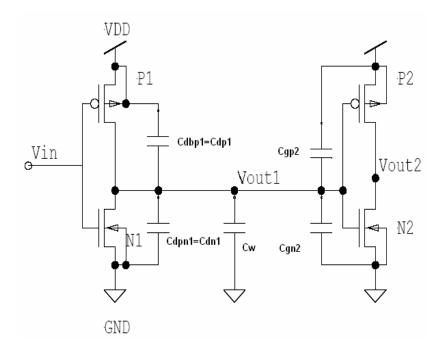

| 4.3        | Determination of $\beta$ Ratio for High-Speed Digital Designs           | 66 |

|            | 4.3.1 Calculation of $\beta$ ratio and V <sub>th</sub>                  | 68 |

|            | 4.3.2 Dependence of $\beta$ Ratio on Other Technological Parameters     | 70 |

|            | 4.3.3 Comparison of Different $\beta$ Ratios for 0.5 $\mu$ m technology | 71 |

|            | 4.3.4 Comparison of $V_{th}$ for Different $\beta$ Ratios               | 71 |

|            |                                                                         |    |

| 4.3.5 Comparison of $\tau_P$ for Different $\beta$ Ratios                      | 73  |

|--------------------------------------------------------------------------------|-----|

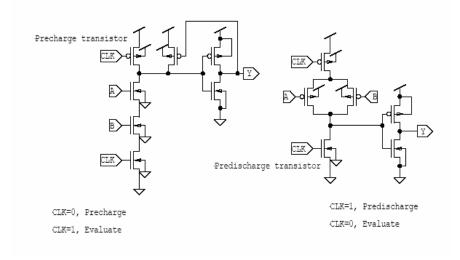

| 4.4 Sizing of Pre-Charge and Pre-Discharge Transistors for Domino Logic Design |     |

| Styles                                                                         | 74  |

| 4.4.1 Load Capacitance Estimation for Pre-charge and Pre-discharge             |     |

| Transistor.                                                                    | 75  |

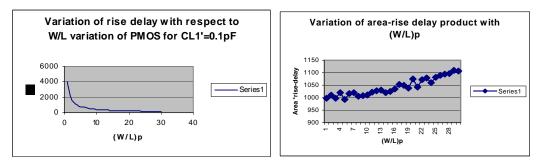

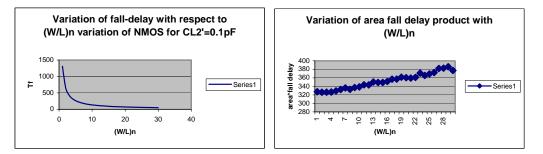

| 4.4.2 Computation of Area Delay Product                                        | 76  |

| 4.4.3 Simulation Result                                                        | 77  |

| 4.5 Chapter Summary                                                            | 79  |

| CHAPTER 5- STUDY OF NBTI DEGRADATION IN DIGITAL LOGIC CIRCUITS                 |     |

| USING VERILOG HDL                                                              | 80  |

| 5.1 Model for NBTI Degradation                                                 | 82  |

| 5.2 Incorporation of NBTI Degradation Model In Verilog Simulation              | 84  |

| 5.3 Verilog Simlation Results Showing NBTI Degradation for 1-bit Full Adder    | 87  |

| 5.4 Chapter Summary                                                            | 89  |

| CHAPTER 6- SIMULATION RESULTS OF DIFFERENT MULTIPLIERS AND                     |     |

| BARREL SHIFTERS                                                                | 90  |

| 6.1 Comparison Between Baugh Wooley Multiplier and Booth Encoded               |     |

| Wallace Tree Multiplier Implementations                                        | 91  |

| 6.2 Comparison Between MUX Based Multiplier and 2×2 cell Based                 |     |

| Multiplier Implementations                                                     | 95  |

| 6.3 Comparison Between MUX Based Barrel Shifter and Pereira's Barrel           |     |

| Shifter Implementations                                                        | 99  |

| 6.4 Comparison of Different Barrel Shifter Architectures                       |     |

| for TSPC Logic Design Style                                                    | 103 |

| 6.7 Chapter Summary                                                            | 104 |

|                                                                                |     |

| <b>CHAPTER 7- CONCLUSION AND SCOPE OF FURTHER WORK</b>                         | 105 |

| 7.1 Conclusion                                                                 | 105 |

| 7.2 Scope of Further Work                                                      | 108 |

| REFERENCES                                                                     | 109 |

| APPENDIX A1                                                                    | 114 |

| APPENDIX A2                                                                    | 117 |

| APPENDIX A3                                                                    | 125 |

| BRIEF BIOGRAPHY OF CANDIDATE  | 129 |

|-------------------------------|-----|

| BRIEF BIOGRAPHY OF SUPERVISOR | 129 |

| LIST OF PUBLICATIONS          | 130 |

# LIST OF TABLES

| Table No. | Title                                                                                | Page No. |

|-----------|--------------------------------------------------------------------------------------|----------|

| 2.1       | Rules for radix-2 Booth encoding                                                     | 16       |

| 2.2       | Rules for radix-4 Booth encoding                                                     | 17       |

| 3.1       | Booth encoder truth table                                                            | 26       |

| 3.2       | Logical operation of a Booth encoded 4×4 multiplier assuming                         |          |

|           | that all of the partial products are negative                                        | 27       |

| 3.3       | Modified logical operation of Booth encoded 4×4 multiplier                           | 28       |

| 3.4       | Modified Booth encoding                                                              | 30       |

| 3.5       | Equivalace between two different patial product generation                           |          |

|           | logics                                                                               | 32       |

| 3.6       | Logic for preprocessing of inputs                                                    | 34       |

| 3.7       | Truth table for a 2×2 combinational multiplier                                       | 44       |

| 3.8       | Design of a 4-bit multiplier using 2×2 combinational multiplier                      | 45       |

| 3.9       | Truth Table for 4-bit barrel shifter operation                                       | 48       |

| 3.10      | Operations performed by AND-OR function                                              | 52       |

| 3.11      | Operations performed by 3 <sup>rd</sup> , 4 <sup>th</sup> and 5 <sup>th</sup> stages | 54       |

| 3.12      | Operation performed by 16-bit barrel shifter                                         | 56       |

| 4.1       | Summary of operation                                                                 | 65       |

| 4.2       | Operation of first stage                                                             | 65       |

| 4.3       | Operation of second stage                                                            | 66       |

| 4.4       | Estimation of $\beta$ ratio using more accurate method                               | 71       |

| 4.5       | Estimation of $\beta$ ratio using conventional method                                | 71       |

| 4.6       | Comparison of $V_{th}$ for three different $\beta$ ratios calculated using           |          |

|           | three different methods                                                              | 72       |

| 4.7       | Comparison of $V_{th}$ using conventional and the more accurate                      |          |

|           | method                                                                               | 72       |

| 4.8       | Comparison of $\tau_P$ using conventional and the more accurate                      |          |

|           | method (for calculated and simulated values)                                         | 73       |

| 5.1       | Degradation in $V_t$ and propagation delay for all PMOS devices                      |          |

|           | in a 1-bit full adder                                                                | 88       |

| 6.1 (a) | Performance and Characteristics of Baugh Wooley and Booth  |     |

|---------|------------------------------------------------------------|-----|

|         | encoded Wallace tree multiplier for W/L=3                  | 92  |

| 6.1 (b) | Performance and Characteristics of Baugh Wooley and Booth  |     |

|         | encoded Wallace tree multiplier for W/L=5                  | 93  |

| 6.1 (c) | Performance and Characteristics of Baugh Wooley and Booth  |     |

|         | encoded Wallace tree multiplier for W/L=7                  | 94  |

| 6.2 (a) | Performance and characteristics of MUX based and 2×2 cell  |     |

|         | based multiplier for W/L=3                                 | 96  |

| 6.2 (b) | Performance and characteristics of MUX based and 2×2 cell  |     |

|         | based multiplier for W/L=5                                 | 97  |

| 6.2 (c) | Performance and characteristics of MUX based and 2×2 cell  |     |

|         | based multiplier for W/L=7                                 | 98  |

| 6.3 (a) | Performance and characteristics of MUX based and Pereira's |     |

|         | barrel shifter for W/L=3                                   | 100 |

| 6.3 (b) | Performance and characteristics of MUX based and Pereira's |     |

|         | barrel shifter for W/L=3                                   | 101 |

| 6.3 (c) | Performance and characteristics of MUX based and Pereira's |     |

|         | barrel shifter for W/L=3                                   | 102 |

| 6.4     | Performance and characteristics of MUX based and Pereira's |     |

|         | barrel shifter for TSPC logic                              | 104 |

| 7.1     | Ready reckoner for high-speed signed multipliers           | 107 |

| 7.2     | Ready reckoner for high-speed unsigned multipliers         | 107 |

| 7.3     | Ready reckoner for high-speed barrel shifters              | 107 |

# LIST OF FIGURES

| Figure No. | Title                                                     | Page No. |

|------------|-----------------------------------------------------------|----------|

| 2.1        | Array multiplier cell                                     | 12       |

| 2.2        | A 4x4 array multiplier showing critical path              | 13       |

| 2.3        | Accumulation of partial product in a Wallace tree         | 15       |

| 3.1        | A 4 ×4 Baugh Wooley multiplier                            | 24       |

| 3.2        | Basic steps in Booth multiplication                       | 29       |

| 3.3        | Block diagram of Booth encoded Wallace tree multiplier    |          |

|            | eliminating limitations                                   | 35       |

| 3.4        | A 4×4 Booth encoded Wallace tree multiplier-eliminating   |          |

|            | limitations                                               | 37       |

| 3.5 (a)    | MUX based multiplier implementation logic                 | 41       |

| 3.5 (b)    | MUX based multiplier implementation                       | 42       |

| 3.5 (c)    | Cell I used in MUX based multiplier implementation        | 42       |

| 3.5 (d)    | Cell II used in MUX based multiplier implementation       | 43       |

| 3.6        | A 2×2 combinational multiplier                            | 44       |

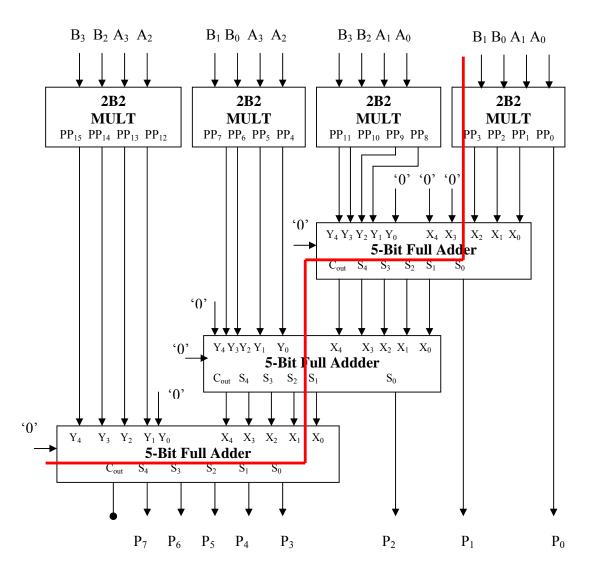

| 3.7        | A 4×4 combinational multiplier                            | 46       |

| 3.8        | A schematic diagram of 4-bit, MUX based barrel shifter    | 49       |

| 3.9        | Schematic of shift-rotate array                           | 51       |

| 3.10       | Complete barrel shifter unit                              | 57       |

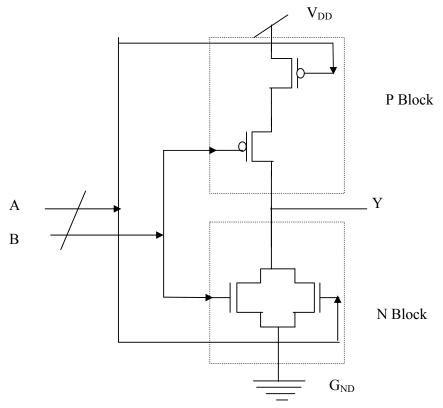

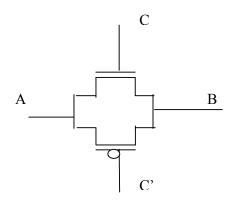

| 4.1        | Static logic gate                                         | 59       |

| 4.2        | CMOS TG switch                                            | 60       |

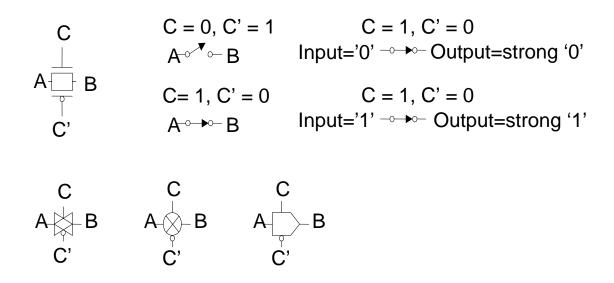

| 4.3        | Different representations of CMOS TG switch               | 61       |

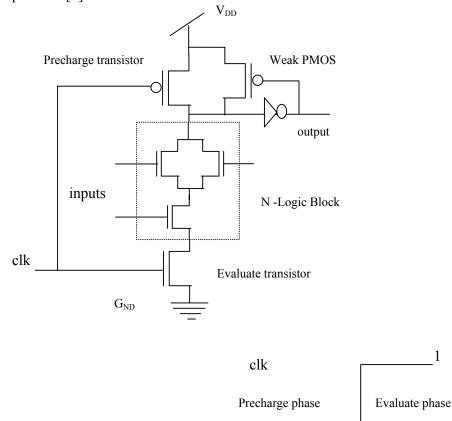

| 4.4        | Domino logic gate                                         | 63       |

| 4.5        | Schematic of a 2input XOR cell designed using dual rail   |          |

|            | domino cell                                               | 64       |

| 4.6        | TSPC logic circuit                                        | 66       |

| 4.7        | A static CMOS inverter driving an identical static CMOS   |          |

|            | inverter                                                  | 68       |

| 4.8        | (a) 2-input AND domino gate (b) another implementation 2- |          |

|            | input AND domino gate                                     | 75       |

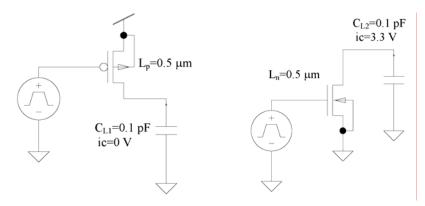

| 4.9  | (a) PMOS driving the estimated capacitance $C_{L1}$ (b) NMOS | 5  |

|------|--------------------------------------------------------------|----|

|      | driving the estimated capacitance $C_{L2}$                   | 76 |

| 4.10 | Variation of rise- delay                                     | 77 |

| 4.11 | Variation of (area×rise-delay) product                       | 77 |

| 4.12 | Variation of fall-delay                                      | 77 |

| 4.13 | Variation of (area × fall-delay) product                     | 77 |

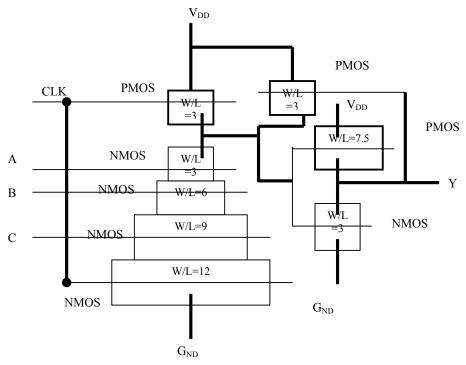

| 4.14 | Design of a domino logic cell                                | 79 |

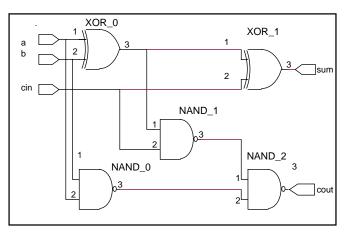

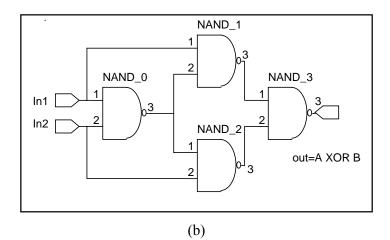

| 5.1  | (a)Full adder schematic (b)XOR gate schematic                | 85 |

# LIST OF ABBREVIATIONS

| ALU  | Arithmetic logic unit                    |

|------|------------------------------------------|

| ASIC | Application specific integrated circuits |

| CLA  | Carry look ahead adder                   |

| CMOS | Complimentary metal oxide semiconductor  |

| CPA  | Carry propogate adder                    |

| CSA  | Carry save adder                         |

| DSP  | Digital signal processing                |

| FIR  | Finite impulse response                  |

| FSM  | Finite state machine                     |

| GPS  | Global positioning system                |

| IIR  | Infinite impulse response                |

| LSB  | Least significant bit                    |

| MAC  | Multiplier-accumulator                   |

| MSB  | Most significant bit                     |

| MUX  | Multiplexer                              |

| NBTI | Negative bias temperature instability    |

| NMOS | N-channel metal oxide semiconductor      |

| PMOS | P-channel metal oxide semiconductor      |

| TG   | Transmission gate                        |

| TSPC | True single phase clock                  |

| VLSI | Very large scale integration             |

|      |                                          |

### CHAPTER 1

### **INTRODUCTION**

#### 1.1 Background

Data-paths of different bit-widths are frequently required in very large scale integrated (VLSI) circuits from processors to application specific integrated circuits (ASICs). The performance of microprocessors and computers heavily depends upon the performance of the various data-paths used. Such data paths include data registers that hold operands and results and combinational logic units that manipulate and process data values [1], [2]. Various combinational logic units are adder, multiplier, divider, barrel shifter and arithmetic logic unit (ALU) circuits. The selection of a particular data-path depends upon the state-of-the-art in digital design. The most important and widely accepted metrics for measuring the quality of data-path designs are propagation delay, area and power [2], [3]. Minimizing area and delay has always been important, but reducing power consumption has also gained importance recently because of increasing levels of integration and the desire for portability. Furthermore, the progress in battery technology is slower as compared to the ever-increasing power requirement due to advances in electronic circuits; the battery technology is unable to provide a solution to the power problem, therefore, an accurate estimation of "average power dissipation" is required to estimate battery life; also, the correct estimate of "peak power dissipation" is required to study circuit reliability. The three major sources of power dissipation in VLSI circuits are: (i) switching component of power, which is increasing due to increase in on-chip clock rates (ii) component of power due to direct-path short-circuit current in circuits, that depends upon the rise and fall times of signals and (iii) component of power due to leakage current which is increasing at an alarming rate due to thin gate oxide and small geometry effects like tunneling and drain induced barrier lowering which are dominating due to device scaling. The short-circuit dissipation of complimentary metal oxide semiconductor (CMOS) inverter with and without load (for equal rise and fall times of input and output signals) is only a fraction (< 20%) of the total dissipation. The *dominant term* in power dissipation is the switching power component, which is given by equation 1.1.

$$P_{dynamic} = C_L \bullet V_{DD}^2 \bullet f_{CLK} \bullet \eta \tag{1.1}$$

Low-power designs, thus, aim at minimizing the power consuming transitions (switching activity factor ' $\eta$ '), power supply (V<sub>DD</sub>), and load capacitance (C<sub>L</sub>) [3], [4]. Since, the largest component of power dissipation is due to the signal transitions at circuit nodes, an accurate estimation of switching activity at the internal circuit nodes is required. Gate delays have impact on switching activity; a delay model is used for computing the Boolean conditions that cause glitches in the circuit. Glitches occur primarily due to mismatch or imbalance in the path lengths in the logic network. Such mismatches in the path lengths result in mismatches of signal timing with respect to the primary inputs [3], [5]. The probability of each gate switching at any particular time is computed from input switching rates, and then the sum of these probabilities over all the gates gives the switching activity in the entire circuit over all the time points in a clock cycle [1], [3], [6], [7]. Such probabilistic methods can't be applied reliably to portable high performance applications, where accurate estimation of power as a compared.

Power dissipation due to leakage currents is gaining utmost importance due to scaling of devices. Many techniques at design and fabrication levels are applied to reduce such leakage. At transistor-level design 'Variable Threshold CMOS Circuits' are used and at fabrication level 'Multiple Threshold CMOS Circuits' and 'HIGH-k gate oxide dielectric' are used to reduce leakage [2], [3], [8], [9].

Portable wireless applications like mobile phones, laptop computers and personal digital assistants (PDA's) require high-speed circuitry consuming low power. Such design requirements are conflicting and involve design tradeoffs. Furthermore the microprocessor on-chip clock rates have already reached GHz range, leading to substantial increase in dynamic (switching) power consumption. As a result in high performance desktops, sinking large amounts of heat through packages is becoming a difficult problem. Therefore, designing low-power processors is also gaining importance for high performance desktops, as well as for portable applications like laptops and palmtops where big heat sinks cannot be used. A low power processor design without greatly loosing computational speed is a technologically challenging requirement.

There are several degrees of freedom available in the design of low-power highperformance circuits and systems at various abstraction levels. These include process technology level, circuit design level, logic design level, architectural level and algorithmic level. CMOS technology, the vehicle for VLSI, offers a combination of large noise margins, ruggedness of design, low power consumption, scalability of technology and validity of the logic design styles at scaled down technologies [9], [10]. Within the CMOS technology, designers have the freedom of choosing the architecture, the logic design style, and the transistor sizes for implementing various arithmetic functions. Besides these, technology scaling including threshold voltage scaling, and supply voltage scaling constitute other techniques that can be used in low-power digital design [11].

#### **1.2 Objective of Thesis**

It has been reported that the time spent in generating data path designs is typically 60% of the overall chip design due to the fact that it is the only major component, which is still handled manually and is a major bottleneck in the design [12]. Automatic layout generation for the data path circuits is possible [12] but 'design space exploration' is still limited. These automatic layout generation tools exploit regularity and avoid the global routing and inter-module channel routing by optimally performing signal alignments between modules during the module generation. The random selection of architecture or logic design style in VLSI design flow may lead to substantial increase in the design time due to complicated VLSI design flow from net list to layout generation in order to meet the specified design constraints. In the present study two data path elements have been considered namely signed/unsigned multipliers and barrel shifters. These data path elements are implemented as purely combinational logic circuits. The objective of this thesis is to explore the design space of these data path elements for different bit-widths at architectural-level, at logic design level (to select proper logic design style), and at transistor-level (to select proper transistor sizes) keeping in view their contributions to performance indices like average switching energy, circuit delay and area.

Presently, wide exploration has been carried out in literature for adder circuits but exploration for other data path elements is still limited. We have explored the design space of multipliers and barrel shifters (at architectural level, at logic design style level and at transistor size level). Such exploration will help the designer in choosing an optimal implementation strategy in terms of the choices of architecture, logic design style and transistor sizes. Various data path elements considered for exploration are listed in section 1.3.

Further, we have also explored one of the most important circuit reliability issues, namely, negative bias temperature instability (NBTI), which has become the deciding factor for the lifetimes of CMOS devices in deep sub-micron technologies.

#### **1.3 Different Data Path Elements Considered for Exploration**

The multiplier and barrel shifters are fundamental building blocks in 'Standard Digital Signal Processors' and 'ASIC Digital Signal Processors' used for digital signal processing (DSP) [13]. The DSP processors are provided with multiplier-accumulators (MACs) in order to perform sum-of-product computations efficiently. The high performance of these processors is achieved by using a high degree of parallelism and faster data-path architectures. Different multiplier and barrel shifter architectures provide trade-offs between gate counts, latency and speed.

### 1.3.1 Multipliers

Classification of various multiplier architectures is described below: [13]

Multiplier architectures are classified broadly into two categories:

- Bit serial multipliers: These multipliers are slower but take much less area and power.

- Bit parallel multiplies: These multiplier are faster but take more area and power.

Bit parallel multipliers are further classified into following two categories:

- (i) Array type multipliers: These multipliers follow regular array structure, thereby simplifying the wiring and layout design [4], [8], [10], [14], [15], [16], [17] [18], [19]

- (ii) Tree based multipliers: These multipliers show irregular structure and therefore take larger wiring area. These multipliers use different column compression techniques namely Ofman tree, Wallace tree and Dadda tree column compression techniques [20], [21], [22], [23], [24], [25], [26], [27]

In this thesis both regular arrays and Wallace tree multipliers have been considered for exploration. Gate-level analyses suggest that Wallace trees are not only faster than array multiplier but they also consume much less power. However these analyses did not take **wiring into account**, resulting in optimistic timing and power estimates [28]. In submicron and deep sub-micron technologies the effect of wiring delays cannot be ignored and therefore wiring parasitics and MOS parasitics must be considered to provide an accurate assessment of a particular architecture. The selected word lengths for multiplier and barrel shifter implementations are 4-bit, 8-bit, 12-bit and 16-bit; which dominate in DSP applications. Different multipliers considered for exploration in this research work are described in section 1.6.

#### **1.3.2 Barrel Shifters**

A barrel shifter [29], [30] is a circuit that allows its input to be shifted or rotated any number of positions in either direction. For example, a 4-bit rotating barrel shifter can shift its inputs I<sub>3</sub>, I<sub>2</sub>, I<sub>1</sub>, I<sub>0</sub> by zero, one, two or three bit positions to the right or left by using the shift control inputs S<sub>1</sub>, S<sub>0</sub>. The direction control bit (DIR) decides the left/right shift direction. Barrel shifter can be implemented as a purely combinational logic circuit, using conventional multiplexers (MUX), decoders, and logic gates. The sequential approach to implement the barrel shifter uses a finite state machine (FSM) and a simpler data-path. Such sequential approaches have not been considered in the present exploration.

Different combinational multiplier and barrel shifter architectures considered for exploration in the present work are described in section 1.6.

Appropriate selection of multiplier and barrel shifter units can be done efficiently by using the data available through such study.

### **1.4 Research Gaps**

Most DSP tasks which are multiplication and shifting intensive must be performed speedily while minimizing cost and power. This requires efficient multipliers and shifters. Different multiplication algorithms differ in the manners of 'partial product generation' and 'partial product addition [21]. The array multipliers have a linear time complexity and therefore their delay increases linearly with operand size n. Also it has poor space complexity O  $(n^2)$ , as it requires approximately  $n^2$  cells to produce multiplication. Therefore as the operand size grows, the circuit takes larger area and power [14], [15], [16]. A radix-y Booth encoding, where  $y=2^x$  reduces the partial product rows by a factor of x. Booth radix-4 ( $y=4=2^2$ ) encoding can reduce the number of partial product rows by a factor of two [22]. Since the number of partial product rows is reduced to half, the hardware required for multiplication is also roughly reduced by a factor of 2 [16]. In Wallace tree multipliers, since ripple effect is reduced they produce products in far less time. The time complexity is reduced to O (log n) but larger routing area is required as compared to regular array multipliers making them less suitable for VLSI implementation [16]. The advantage of reduction in hardware using Booth encoding scheme can be combined with accelerated Wallace tree accumulation of partial products to obtain the reduced time complexity of O (log n), which is well suited for large operand

size multipliers [16], [22]. In sub-micron/deep sub-micron technologies for the multipliers of moderate operand sizes, where tree based architectures may degrade their performance due to larger routing lengths, some hybrid architectures [such as array of array multiplier] may show better performance [10]. These multiplier architectures have moderate routing area requirements and time complexity of  $O(\sqrt{n})$  [10]. Even though there is a body of research studies on multipliers in the literature, a systematic research study of promising high performance multipliers across architectures, logic design styles and transistor sizes does not exist. Such a study can be of great value to multiplier designers.

Similarly different barrel shifter architectures also show tradeoffs between silicon area and speed of operations. Some architectures have a dedicated block for all the operations to be performed by the barrel shifter. They are faster, but consume larger silicon area and power. A significant reduction in area and power required by the barrel shifter circuit is achieved by implementing rightward operations as operations in leftward direction [30]. **Once again, no systematic study of barrel shifter design across architectures, logic design styles and transistor sizes exists in literature.**

In the area of circuit reliability, even though NBTI has been identified as the primary factor limiting the circuit life of CMOS circuits using deep sub-micron technology no published method exists in literature to incorporate and simulate NBTI effects dynamically in digital CMOS circuits. The CAD tools for modeling and simulation of NBTI degradation are not widely available due to this effect's complexity and emerging status [31], [32], [33]. Presently research works on NBTI is actively pursued only within the community of device and reliability physicists and leading industrial companies appear to develop their models and tools only internally to handle this effect [31], [32], [33], [34]. Considering all the above the scope of the research to be carried out under this thesis was determined as follows:

1. To study high performance multipliers (for a range of bit widths from 4-bit to 16-bit) across architectures, logic design styles and transistor sizes to gain an understanding of the optimality of various design approaches for high performance multipliers.

2. To carry out a similar study for barrel shifters.

3. To explore and propose a method of incorporating NBTI effect dynamically in logic/switch level simulation of CMOS circuits.

#### 1.5 Research Methodology/Work-Plan

implementations.

As proposed, the research work started its journey by collecting the various relevant literature items available on the various multiplier and barrel shifter architectures. This helped to understand their algorithms, architectures and their VLSI implementations. Various techniques to achieve optimum performance (i.e. low-power, high-speed and optimum area) were also studied in detail.

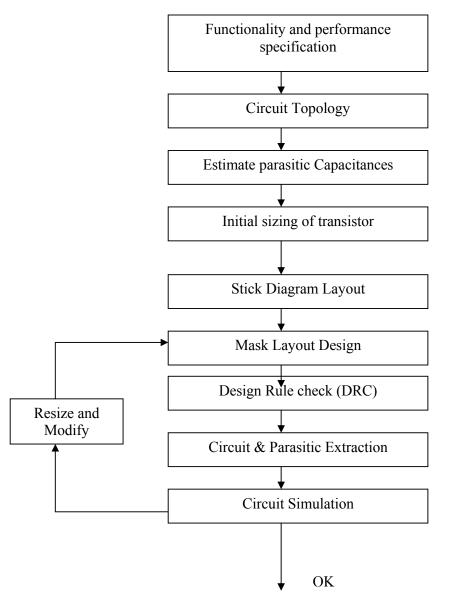

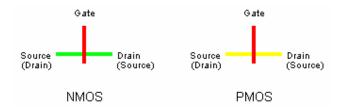

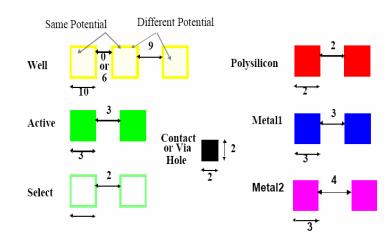

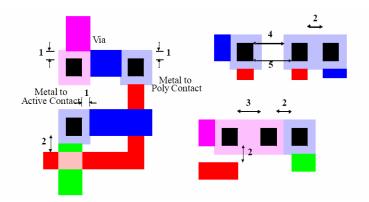

In the second phase, transistor level schematic libraries consisting of a standard sets of functional cells were developed for static logic design style, transmission gate (TG) logic design style, dual-rail domino logic design style and true single phase clock (TSPC) logic design style (used only for the barrel shifters). Corresponding to each schematic library, three different versions of physical library were developed by respectively sizing the W/L ratios of the N-channel metal oxide semiconductor (NMOS) transistor to values of 3, 5 and 7 (W/L values smaller than 3 were also experimented with but not considered further as they resulted in parasitic dominated slower speeds due to weak drives of transistors and were not considered good candidates for high performance). Physical libraries were implemented in 0.5 µm, N-well CMOS process (SCN SUBM, lambda=0.3) of MOSIS. The layout assemblies for the 4-bit, 8-bit, 12-bit and 16-bit multiplier and barrel shifter circuits were carried out using these cell libraries and automatic place and route tool LEDIT (SPR) from M/s Tanner Research Inc. [35], [36]. In the third phase the generated layouts were then simulated after parasitic extraction using circuit simulator, ELDO spice. Supply voltage V<sub>DD</sub> was kept at 3.3V. The product of average switching energy and circuit delay was then computed for each implementation of the selected multiplier and barrel shifter circuit using the same logic design style but utilizing three different physical libraries- differing in their transistor sizes as described above. It was noticed that for all the three logic design styles, the physical library utilizing W/L ratio of 3 for NMOS transistors gave the smallest average switching energy-delay product. A detailed comparative study was carried out for different parameters like propagation delay, transistor count, core area and power dissipation at 20MHz input/clock rate (selected for comparison purposes) across all the

In fourth phase, one of the most important circuit reliability issues, namely, NBTI [31], [32] was considered. We proposed a new technique to study the NBTI degradation using widely available Verilog HDL, which will help many designers to include NBTI effect in

their designs. The NBTI is identified as most critical reliability concern for nanometer scale digital integrated circuits. Degradation occurring in P-channel metal oxide semiconductor (PMOS) devices is most critical as it decides the lifetime of CMOS devices in deep sub-micron technologies. We studied the NBTI degradation for a 1-bit full adder circuit in 90 nm technology using Verilog HDL. The circuit model describes basic static CMOS logic gates using switch-level Verilog description, which also incorporates the model for computing change in the threshold voltage ( $\Delta V_t$ ) and the delay (t<sub>p</sub>) of PMOS devices after every NBTI stress. NBTI stress can be computed by knowing the time for which particular PMOS transistor remains under negative bias (i.e  $V_{es}$ <0).

#### **1.6 Thesis Structure**

In this thesis a total of four multiplier architectures have been chosen for study, out of which two multiplier architectures support signed 2's complement numbers. These are Baugh Wooley multiplier and Booth encoded Wallace tree multiplier. The remaining two multiplier architectures supports unsigned numbers. These are MUX based multiplier and 2×2 cell based multiplier. The barrel shifter architectures chosen for study are Pereira's architecture and MUX-based architecture. The different logic design styles used for VLSI implementation are static CMOS logic, dual rail domino CMOS logic, TG logic and TSPC logic (only for the barrel shifter designs).

The thesis consists of seven chapters. Chapter 2 describe the design philosophy of multiplier and barrel shifter circuits, Chapter 3 explains the different multiplier and barrel shifter architectures, chapter 4 discusses the different CMOS logic design styles and determination of PMOS/NMOS width ratio ( $\beta$ ) for high speed design, chapter 5 presents the study of the dynamics of NBTI degradation in digital logic circuits using Verilog HDL. The VLSI implementation and simulation results for different multiplier and barrel shifter circuits are tabulated and compared in chapter 6. The comparison parameters are propagation delay, average power, maximum power and leakage power, transistor count, core layout area, routing length and number of vias. The complete research work is summarized in chapter 7, which concludes the thesis. The list of references, appendix, and brief bibliography of the candidate as well as the supervisor are appended at the end of the thesis.

### **1.7 Chapter Summary**

In this chapter we discussed about the background of the work and the objectives of the thesis. Further we described the different data path architectures considered for exploration and identified the research gaps based on detailed literature survey. The chapter also lays out the research methodology and chapter wise structure of the thesis.

### CHAPTER 2

# A DESIGN PHILOSOPHY OF MULTIPLIER AND BARREL SHIFTER CIRCUITS

Multiplication is the most widely used operation in many computational systems. Multiplication process is used in many neural computing and DSP applications like instrumentation and measurement, communications, audio and video processing, graphics, image enhancement, 3D rendering, navigation, radar, global positioning system (GPS), and control applications like robotics, machine vision and guidance. It is used mainly to implement algorithms like frequency domain filtering such as finite impulse response (FIR) and infinite impulse response (IIR), frequency-time transformations, correlation etc. Most DSP tasks require real-time processing; it must perform these tasks speedily while minimizing cost and power. The optimizations carried out at different levels of abstraction in the design process are typically at architectural-level, at logic level to select proper logic design style, and at transistor-level to select proper transistor sizes- keeping in view their contributions to performance indices like average power, circuit delay and area.

The multipliers used for various applications can be categorized as unsigned and signed multipliers. The popular 2's complement number representation is considered for signed multipliers. Apart from reducing the length of critical path, the VLSI implementation of multiplier circuit primarily focuses on iterative circuits with uniform interconnection pattern, which also helps in reducing the total interconnect length. The multiplication involves two basic operations i.e. the generation of partial products and their accumulation. Different multiplier algorithms differ in terms of 'partial product generation' and 'partial product accumulation', therefore their time and space complexity also varies. The complexity becomes important when operand size increases (i.e. problem size grows). The speed-up for the multiplication can be achieved using the following two techniques [13], [14], [22], [37]:

- 1. Reduce the number of partial products.

- 2. Accelerate the accumulation of partial products.

The smaller number of partial products reduces the time needed to accumulate the partial products. The accumulation process can be accelerated using faster carry save addition (CSA) technique as discussed in section 2.2.

### 2.1 Array Multiplier [4], [8], [18], [19], [10], [14], [15], [16], [17], [37], [38]

In this scheme, the two dimensional logic can be so organized that the partial product at  $(i+1)^{st}$  stage is the sum of the partial products up to i<sup>th</sup> stage and the left shifted version of  $(i+1)^{st}$  partial product. The partial products in the multiplication process may be independently computed in parallel. For a multiplicand A=A<sub>n-1</sub> A<sub>n-2</sub> .....A<sub>0</sub>, and multiplier B=B<sub>n-1</sub> B<sub>n-2</sub> .....B<sub>0</sub> the product P=A.B is given by equation 2.1.

$$P = \sum_{i=0}^{n-1} B_i \cdot 2^i \cdot A = \sum_{i=0}^{n-1} 2^i \sum_{j=0}^{n-1} B_j \cdot A_j \cdot 2^j$$

(2.1)

The i<sup>th</sup> partial product sum PP<sub>i</sub> can be denoted by equation 2.2

$PP_{0}=0$   $PP_{1}=PP_{0}+B_{0}A$   $PP_{2}=PP_{1}+B_{1}2^{1}A$   $PP_{3}=PP_{2}+B_{2}2^{2}A$  .  $PP_{i+1}=PP_{i}+B_{i}2^{i}A$ (2.2)

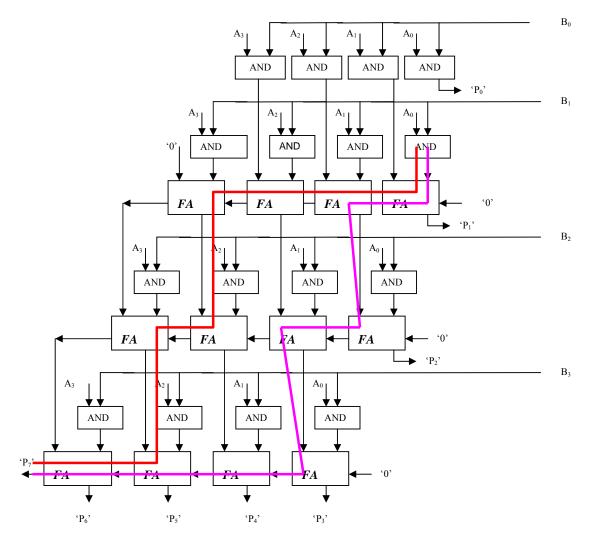

Example 2.1 shows the simple multiplication process. The figure 2.1 shows the simple array multiplier cell. This simple cell is used repetitively and arranged to realize a complete array multiplier circuit as shown in figure 2.2. The critical path in multiplier circuit is also indicated. Reduction in the length of critical path is one of the major objectives in any combinational circuit design.

| Exampl<br>A= Mu<br>B= Mu | ltiplicand |            |   |

|--------------------------|------------|------------|---|

| 1                        | - A:       | 1101=13    |   |

| 1                        | B:         | 1011=11    | į |

| -<br> <br>               |            | 1101       |   |

| <br> <br>                |            | 1101+      |   |

|                          |            | 0000++     |   |

| 1<br> <br>               | 11         | 101+++     | į |

| <br> <br> <br> <br>      | 100        | 001111=143 | - |

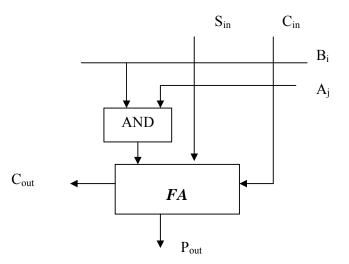

Figure 2.1 Array multiplier cell

### Where,

$S_{in}$  is the incoming sum bit and  $C_{in}$  is the incoming carry bit being summed along with the partial product bit  $B_i A_j$  by the full adder.

#### **Advantages:**

- Regular circuit structure; hence suitable for VLSI implementation.

- The length of interconnects is reduced appreciably.

- Execution is comparatively faster than sequential multiplication.

- Such architecture can be faster for smaller operand size multipliers.

### **Disadvantages:**

- As the operand size grows the circuit takes large area and power due to space complexity O (n<sup>2</sup>).

- Execution is slow due to ripple effect in partial product addition.

- These multipliers have time complexity of O (n).

- Due to linear time complexity, delays may not be acceptable for larger operand size multipliers.

Figure 2 .2 A 4x4 array multiplier showing critical path

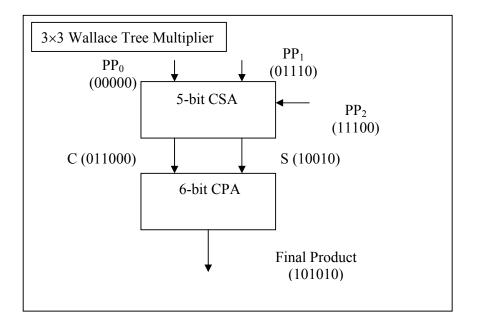

### 2.2 Wallace Tree [22], [37], [39]

A Wallace tree scheme accelerates the accumulation using faster CSA technique. CSA is one of the major speed enhancement techniques used in modern digital multiplier circuits due to its ability to add numbers with minimal carry propagation. Using 3:2 compressors, three numbers can be reduced to two using simple addition while keeping their carries and the sum separate. This means that all of the columns can be added in parallel without waiting for the result of the previous column. The two outputs that the adder generates as sum and carry can be compressed further in next stage. In the last stage, two rows of sum and carry can be added using carry propagate adder (CPA) to obtain final product. Example 2.2 shows accumulation of partial product in a Wallace tree multiplier.

| Example 2.2:            |

|-------------------------|

| 10111001                |

| 00101010                |

| <u>00111001</u>         |

| Sum: 10101010           |

| Carry: <u>00111001X</u> |

| Result:100011100        |

|                         |

|                         |

|                         |

### Advantages:

- Since ripple effect is reduced, it produces the product in far less time.

- The time complexity is reduced to O (log n).

### **Disadvantages:**

- Requires more hardware to accumulate partial product bits as compared to array multipliers (which are regular).

- Takes larger routing area as compared to regular array multipliers; hence less suitable/adaptable for VLSI implementation.

Example 2.3 shows the addition of partial product rows in a Wallace tree multiplier. The addition can be performed using fast CSA as shown in figure 2.3.

| Example 2.3:                  |

|-------------------------------|

| A=111 (7)<br>B=110 (6)        |

|                               |

| <u>11100 (PP<sub>2</sub>)</u> |

| 101010 (Final Sum Calculated) |

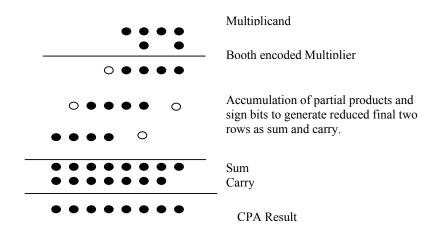

Figure 2.3 Accumulation of partial product in a Wallace tree

#### 2.3 Booth's Algorithm [37], [39]

The motivation of this scheme is to "**speed up**" multiplication process by reducing the number of partial products. It is not essential to execute add and shift for each '1' multiplier bit.

A multiplier (say) B = 001110011110 can be treated as:

| 0 | 0  | 1 | 1 | 1  | 0 | 0  | 1 | 1 | 1 | 1  | 0 |

|---|----|---|---|----|---|----|---|---|---|----|---|

| 0 | +1 | 0 | 0 | -1 | 0 | +1 | 0 | 0 | 0 | -1 | 0 |

Instead of add and shift operation for each bit that is '1' in the multiplier the '0' and '1' multiplier bits can be replaced by +1, 0, or -1 as noted.

- +A or -A with appropriate shift need to be added to the partial product corresponding to +1 or -1.

- Thus the number of ADD operations is reduced from 7 to only 4 ADD/SUB operations.

- Rules for first order Booth encoding are given in table 2.1.

| Bi | B <sub>i-1</sub> | Comments                        | $Y_i$ |

|----|------------------|---------------------------------|-------|

| 0  | 0                | String of zeros                 | 0     |

| 1  | 1                | String of ones                  | 0     |

| 1  | 0                | Beginning of a string with ones | -1    |

| 0  | 1                | End of a string with ones       | 1     |

Table 2.1 Rules for radix-2 Booth encoding

Such encoding is useful for sequential multiplier design, since it reduces the number of addition operations to be performed. The Booth encoding in combinational circuit design can be explained by example 2.4.

Example 2.4:

- A multiplier of 14 (0,1,1,1,0) can be treated as (+1,0,0, -1,0) i.e. (16-2)

- A multiplier of 15 (0,1,1,1,1) can be treated as (+1,0,0,0, -1) i.e. (16-1)

This is called radix-2 Booth encoding. A radix-y Booth encoding, where  $y=2^x$  reduces the number of partial product rows by factor of x. Therefore radix-2 Booth encoding does not reduce the number of partial product rows. Example 2.5 shows that radix-2 Booth multiplier does not show any advantage in combinational multiplier design, since the number of partial product rows remains unreduced and algorithm puts additional burden of negation of a multiplier. Thus radix-2-Booth encoding is costlier than normal multiplier.

| Example 2.5:                                           |  |   |   |   |   |    |   |    |  |  |  |

|--------------------------------------------------------|--|---|---|---|---|----|---|----|--|--|--|

| Multiplicand = $A = -5 = 1011 \implies -A = +5 = 0101$ |  |   |   |   |   |    |   |    |  |  |  |

| Multiplier = B = -3 = 1101                             |  |   |   |   |   |    |   |    |  |  |  |

| Multiplicand (A)                                       |  |   |   |   | 1 | 0  | 1 | 1  |  |  |  |

| Multiplier (B)                                         |  |   |   |   | 1 | 1  | 0 | 1  |  |  |  |

| Recoded multiplier (Y)                                 |  |   |   |   | 0 | -1 | 1 | -1 |  |  |  |

| PP <sub>1</sub>                                        |  | 0 | 0 | 0 | 0 | 1  | 0 | 1  |  |  |  |

| PP <sub>2</sub>                                        |  | 1 | 1 | 1 | 0 | 1  | 1 | -  |  |  |  |

| PP <sub>3</sub>                                        |  | 0 | 0 | 1 | 0 | 1  | - | -  |  |  |  |

| PP <sub>4</sub>                                        |  | 0 | 0 | 0 | 0 | -  | - | -  |  |  |  |

| Sum                                                    |  | 0 | 0 | 0 | 1 | 1  | 1 | 1  |  |  |  |

To get rid of the above problem higher radix Booth algorithms are used. Booth radix-4  $(y=4=2^2)$  encoding can reduce the number of partial product rows by a factor of two. For radix-4 Booth encoding, we are encoding each pair as operation like 0, ±A, ±2A, this will reduce the number of rows of partial products in combinational circuit by a factor of two. In this algorithm B<sub>i</sub> and B<sub>i-1</sub> is recoded as Z<sub>i</sub> and Z<sub>i-1</sub> but taking into account the B<sub>i-2</sub> bit. The algorithm to convert a sequence is given in the table 2.2.

| B <sub>i</sub> | B <sub>i-1</sub> | B <sub>i-2</sub> | Zi | Z <sub>i-1</sub> | Dj | Operation |

|----------------|------------------|------------------|----|------------------|----|-----------|

| 0              | 0                | 0                | 0  | 0                | +0 | +0        |

| 0              | 0                | 1                | 0  | 1                | +1 | +A        |

| 0              | 1                | 0                | 0  | 1                | +1 | +A        |

| 0              | 1                | 1                | 1  | 0                | +2 | +2A       |

| 1              | 0                | 0                | -1 | 0                | -2 | -2A       |

| 1              | 0                | 1                | 0  | -1               | -1 | -A        |

| 1              | 1                | 0                | 0  | -1               | -1 | -A        |

| 1              | 1                | 1                | 0  | 0                | +0 | +0        |

Table 2.2 Rules for radix-4 Booth encoding

For the case of radix-4 Booth encoding a signed binary number in two's complement form is partitioned into overlapping groups of three bits (in general for the radix-y Booth encoding the overlapping group takes x+1 bits) and each group is represented by possible value of 0, +A, -A, +2A, -2A using the rules indicated in the table 2.2. The value of overlapping groups of three bits can also be computed easily using the equation 2.3, which computes digits  $D_j$  as shown in table 2.2. Use of this algorithm reduces the number of partial product rows to half. Example 2.6 shows the grouping of multiplier bits in a radix-4 Booth encoding.

| Example 2.6:<br><b>Multiplier (B) = 11010 = <math>B_4B_3B_2B_1B_0</math></b> |            |            |                       |                       |                       |                |             |   |           |           |  |

|------------------------------------------------------------------------------|------------|------------|-----------------------|-----------------------|-----------------------|----------------|-------------|---|-----------|-----------|--|

| Comments                                                                     |            |            | Μ                     | lultip                |                       | Operation      |             |   |           |           |  |

| Comments                                                                     | <b>B</b> 5 | <b>B</b> 4 | <b>B</b> <sub>3</sub> | <b>B</b> <sub>2</sub> | <b>B</b> <sub>1</sub> | B <sub>0</sub> | <b>B</b> .1 | i | J=(1-1)/2 | Operation |  |

| B is sign extended                                                           | 1          | 1          | 1                     | 0                     | 1                     | 0              | 0           |   | <u></u>   |           |  |

| Group 0                                                                      |            |            |                       |                       | 1                     | 0              | 0           | 1 | 0         | (-2A)     |  |

| Group 1                                                                      |            |            | 1                     | 0                     | 1                     |                |             | 3 | 1         | (-A)      |  |

| Group 2                                                                      | 1          | 1          | 1                     |                       |                       |                |             | 5 | 2         | (0)       |  |

$$coded \quad digit \ D_{j} = -2^{n-1}B_{nj+1} \dots + 2^{1}B_{nj+1} + 2^{0}B_{nj} + 2^{0}B_{nj-1}$$

for  $n=2$ :

$$coded \quad digit \ D_{j} = -2^{1}B_{2j+1} + 2^{0}B_{2j} + 2^{0}B_{2j-1}$$

$$\frac{for \ j=0}{coded \quad digit \ D_{0} = -2^{1}B_{1} + 2^{0}B_{0} + 2^{0}B_{-1}$$

$$\frac{for \ j=1}{coded \quad digit \ D_{1} = -2^{1}B_{3} + 2^{0}B_{2} + 2^{0}B_{1}$$

$$\frac{for \ j=2}{coded \quad digit \ D_{2} = -2^{1}B_{5} + 2^{0}B_{4} + 2^{0}B_{3}$$

(2.3)

Example 2.7 shows the multiplication process for radix-4 Booth algorithm. In this method the number of bits should always be even. If the number of bits is odd then sign bit is extended at the most significant bit (MSB) position. The example shows that the number of partial product rows is reduced by a factor of 2.

Example 2.7: Multiplicand  $A = +13 = 01101 \implies -A = 10011$ Multiplier B = -6 = 11010 = 111010 (sign extended to 6-bit) Modified multiplier bits:  $i = 5 \Rightarrow Z_5 Z_4 = (0 \ 0), i = 3 \Rightarrow Z_3 Z_2 = (0 \ -1) \text{ and } i = 1 \Rightarrow Z_1 Z_0 = (-1 \ 0)$ OR {since,  $i=2j+1 \Rightarrow j=(i-1)/2$ }  $j = 2 \Rightarrow D_2 = 0, j = 1 \Rightarrow D_1 = -1, j = 0 \Rightarrow D_0 = -2$ Operation to be performed = 0, -A, -2A (From Table 2.2) (+13)0 0 1 1 0 1 (-6) 0 0 0 -1 -1 0 1 0 1 (-26) 1 1 1 0 1 0 (-52) 1 1 1 0 0 1 1 ++0 0 0 0 0 ++(0)1 1 0 1 1 0 0 0 (-78) 1 Note: Number of partial product rows have been reduced by a factor of 2

### Advantages:

- Number of partial product rows is reduced to half. This also implies that the hardware required to generate partial products is reduced to  $n^2/2$  cells.

- The advantage of reduction in hardware using Booth encoding scheme can be combined with accelerated Wallace tree accumulation of partial products to obtain the reduced time complexity of O (log n).

- Such Booth encoded tree multipliers are highly suitable for large operand size multipliers.

### **Disadvantages:**

- The Booth encoding requires extra hardware and generation of partial products becomes complex due to increased number of operations on multiplicand A.

- The Booth encoder circuit adds an extra delay to critical path hence for smaller operand-size multipliers the performance may degrade.

#### 2.4 Array of Array Multiplier [10]

As discussed earlier, array multipliers are preferred for smaller operand sizes due to their simpler VLSI implementation, in-spite of their linear time complexity. On the other hand the tree-based multipliers have better time complexity as compared to array based multipliers but are less suitable for VLSI implementation; since being less regular they require larger total routing length, which may degrade their performance. Some hybrid architectures have area and latency characteristics in between the two extremes. These are called array of array based schemes, which have routing area requirements close to an array multiplier and time complexity of  $O(\sqrt{n})$ .

#### 2.5 Different Multiplier Architectures Considered for Exploration

The different multiplier architectures to be studied based on the above points of view are listed below.

- (1) Baugh Wooley Multiplier [8]

- (2) Booth Encoded Wallace Tree Multiplier [22], [40], [41]

- (3) MUX Based Multiplier [16]

- (4) 2×2 Cell Based Multiplier [10], [42]

The multipliers (1) and (2) are signed multipliers while multipliers (3) and (4) are unsigned multipliers. The detailed design implementation for these multiplier

architectures are discussed in chapter 3. These architectures have been considered for exploration in the present study. The performance and characteristic parameters for comparison purposes are propagation delay, average power, maximum power and leakage power, transistor count, core layout area, routing length and number of vias.

#### 2.6 Barrel Shifter Design Philosophy and Architectures Considered for Exploration

Data shifting is a requirement of many key computer operations- from address generation to arithmetic functions. Shifting a single data bit one field at a time can be a slow process; this is where a barrel shifter comes in. A barrel shifter is a combinational logic device/circuit that can shift or rotate a data word by desired number of bits in a single operation. It is another most important block in DSP processor circuits. Intel 80386 and Motorola 68030 chips have also utilized the barrel shifter circuit in their design. It is used for floating-point normalization, word pack/unpack, and field extraction from a bit stream, editing, data modification, and arithmetic manipulation.

Different barrel shifter architectures show tradeoffs between silicon area and speed of operations. Some architectures have a dedicated block for all the operations to be performed by the barrel shifter. They are faster, but consume larger silicon area and power. A significant reduction in area and power required by the barrel shifter circuit is achieved by implementing rightward operations as operations in leftward direction [30]. The barrel shifter architectures to be studied from the above points of view and included in our studies are listed below.

(1) MUX Based Barrel Shifter [43]

(2) Pereira's Barrel Shifter [29]

The detailed design implementation for these barrel shifter architectures are discussed in chapter 3.

#### 2.7 Chapter Summary

In this chapter we present the design philosophy of the multiplier and barrel shifter circuits for achieving high performance. The chapter presents the schematic structure and highlights the associated advantages and disadvantages of array multipliers, Wallace tree multipliers, Booth's algorithm and array of array multipliers. Furthermore, the chapter proposes four high-speed multiplier architectures for further investigation. Similarly, it proposes two high-speed barrel shifter architectures for further investigation.

## CHAPTER 3

# DIFFERENT MULTIPLIER AND BARREL SHIFTER ARCHITECTURES

Basics of multiplier design have been already discussed in chapter 2. In this chapter we present details of architecture and logic implementations in respect of four different multipliers and two different barrel shifters selected for exploration.

The multipliers selected are:

(1) Baugh Wooley Multiplier [8]

- (2) Booth Encoded Wallace Tree Multiplier [22], [40], [41]

- (3) MUX Based Multiplier [16]

- (4) 2×2 Cell Based Multiplier [10], [42]

Multiplier (1) and (2) are signed multipliers and multiplier (3) and (4) are unsigned multipliers. The signed multipliers follow the 2's complement number representation. The barrel shifter architectures considered for explorations are:

- (1) MUX Based Barrel Shifter [43]

- (2) Pereira's Barrel Shifter [29]

All the multipliers as well as barrel-shifter architectures are implemented for 4-bit, 8-bit, 12-bit and 16-bit sizes using four different logic design styles.

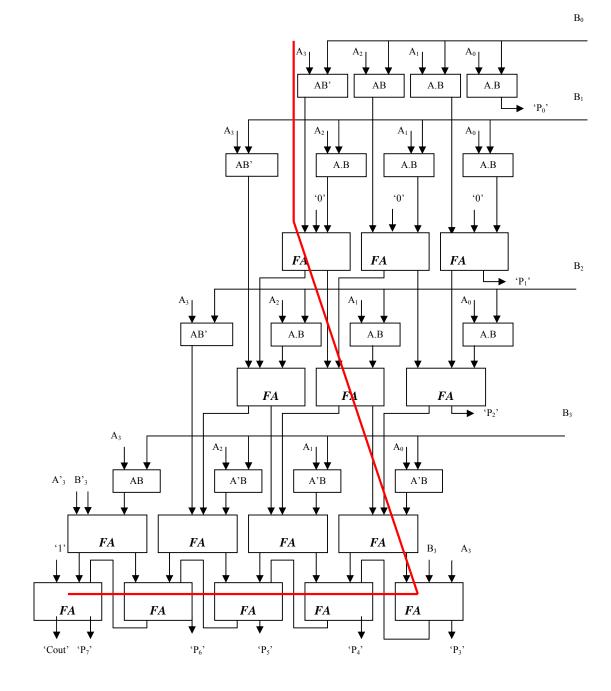

#### 3.1 Baugh-Wooley Multiplier

The Baugh-Wooley multiplier is a signed array multiplier, which utilizes 2's complement number system in the implementation of multiplication algorithm. Partial products are adjusted to maximize regularity of multiplication array. Algorithm moves partial product terms with negative signs to the last steps, where it adds  $(-2^{2N-1})$  to other partial product terms to get sum of partial products as shown in equation 3.4, which is derived using equation 3.1, equation 3.2 and equation 3.3.

<u>Design implementation for a 4×4 multiplier</u>: As explained earlier in a 4×4 multiplier the sign-bit of product carries a weight of  $-2^7$ . The design procedure for a 4×4 multiplier utilizes equation 3.1, equation 3.2 and equation 3.3 and derives the terms T<sub>1</sub>, T<sub>2</sub>, T<sub>3</sub>, T<sub>4</sub>, T<sub>5</sub> and T<sub>6</sub> (where, the first term T<sub>1</sub>= $-2^7$ ) such that their summation generates the final product in 2's complement notation as shown by equation 3.4

$$A = -A_3 2^3 + (A_2 2^2 + A_1 2^1 + A_0 2^0)$$

(3.1)

$$B = -B_3 2^3 + (B_2 2^2 + B_1 2^1 + B_0 2^0)$$

(3.2)

So,

$$P = AB = A_3B_32^6 - A_3(B_22^2 + B_12^1 + B_02^0) \cdot 2^3 - B_3(A_22^2 + A_12^1 + A_02^0)2^3$$

+ $(A_22^2 + A_12^1 + A_02^0)(B_22^2 + B_12^1 + B_02^0)$  (3.3)

Let,

$$-(B_{2}2^{2} + B_{1}2^{1} + B_{0}2^{0}) = -2^{3} + B_{2}'2^{2} + B_{1}'2^{1} + B_{0}'2^{0} + 2^{0}$$

$$[e.g., -111 = -1000 + 000 + 1; -000 = -1000 + 111 + 1]$$

So,  $P = AB = A_{3}B_{3}2^{6} - A_{3}2^{6} + A_{3}(B_{2}'2^{2} + B_{1}'2^{1} + B_{0}'2^{0}) \cdot 2^{3} + A_{3}2^{3}$

$$-B_{3}2^{6} + B_{3}(A_{2}'2^{2} + A_{1}'2^{1} + A_{0}'2^{0}) \cdot 2^{3} + B_{3}2^{3}$$

$$+(A_{2}2^{2} + A_{1}2^{1} + A_{0}2^{0})(B_{2}2^{2} + B_{1}2^{1} + B_{0}2^{0})$$

again,

$$-A_{3}2^{6} = -2^{7} + A_{3}^{'}2^{6} + 0^{'}2^{5} + 0^{'}2^{4} + 0^{'}2^{3} + 0^{'}2^{2} + 0^{'}2^{1} + 0^{'}2^{0} + 1$$

$$= -2^{7} + A_{3}^{'}2^{6} + 2^{5} + 2^{4} + 2^{3} + 2^{2} + 2^{1} + 2^{0} + 1 = -2^{6} + A_{3}^{'}2^{6}$$

$$-B_{3}2^{6} = -2^{7} + B_{3}^{'}2^{6} + +2^{5} + 2^{4} + 2^{3} + 2^{2} + 2^{1} + 2^{0} + 1 = -2^{6} + B_{3}^{'}2^{6}$$

$$\Rightarrow -A_{3}2^{6} - B_{3}2^{6} = -2^{6}(1+1) + (A_{3}^{'} + B_{3}^{'}) \cdot 2^{6}$$

$$\Rightarrow -A_{3}2^{6} - B_{3}2^{6} = -2^{7} + (A_{3}^{'} + B_{3}^{'}) \cdot 2^{6}$$

$$P = AB = -2^{7} \qquad T_{1}$$

$$+ (A_{3}B_{3} + A_{3}^{'} + B_{3}^{'}) \cdot 2^{6} \qquad T_{2}$$

$$+ A_{3}(B_{2}^{'}2^{2} + B_{1}^{'}2^{1} + B_{0}^{'}2^{0}) \cdot 2^{3} \qquad T_{3}$$

$$+ B_{3}(A_{2}^{'}2^{2} + A_{1}^{'}2^{1} + A_{0}^{'}2^{0}) \cdot 2^{3} \qquad T_{4}$$

$$+ (A_{3} + B_{3}) \cdot 2^{3} \qquad T_{5}$$

$$+ (A_{2}2^{2} + A_{1}2^{1} + A_{0}2^{0})(B_{2}2^{2} + B_{1}2^{1} + B_{0}2^{0}) \qquad T_{6}$$

$$(3.4)$$

The final product obtained by adding  $T_1$ ,  $T_2$ ,  $T_3$ ,  $T_4$ ,  $T_5$  and  $T_6$  is then rearranged to produce product bits  $P_0$  to  $P_7$  as shown in equation 3.5, which helps the designer to implement the combinational logic circuit for 4×4 multiplier as shown in figure 3.1. For this multiplier,  $A_i \& B_i$  are two 4-bit input vectors and  $P_k \& C_{out}$  are outputs of 8-bit and 1-bit length respectively. The final carry bit  $C_{out}$  is discarded.

Similar technique is followed in design of 8×8, 12×12 and 16×16 multipliers.

$$P_{0} = +2^{0} (A_{0}B_{0})$$

$$P_{1} = +2^{1} (A_{1}B_{0} + A_{0}B_{1})$$

$$P_{2} = +2^{2} (A_{2}B_{0} + A_{1}B_{1} + A_{0}B_{2})$$

$$P_{3} = +2^{3} (A_{2}B_{1} + A_{1}B_{2} + A_{3} + B_{3} + A_{3}B_{0}' + A_{0}'B_{3})$$

$$P_{4} = +2^{4} (A_{2}B_{2} + A_{3}B_{1}' + B_{3}A_{1}')$$

$$P_{5} = +2^{5} (A_{3}B_{2}' + A_{2}'B_{3})$$

$$P_{6} = +2^{6} (A_{3}B_{3} + A_{3}' + B_{3}')$$

$$P_{7} = -2^{7}$$

(3.5)

Figure 3.1 A 4 ×4 Baugh Wooley multiplier

#### 3.2 Booth Encoded Wallace Tree Multiplier

The basic operation of radix-2 and radix-4 Booth encoding has already been discussed in chapter 2. This section presents design implementation for a  $M \times N$  radix-4 Booth encoded optimized Wallace tree multiplier. In this multiplier design, the partial product at each bit position is compressed into sum and carry signals, which are then added to give the final output as explained later in section 3.2.2.

#### 3.2.1 Multiplication Logic

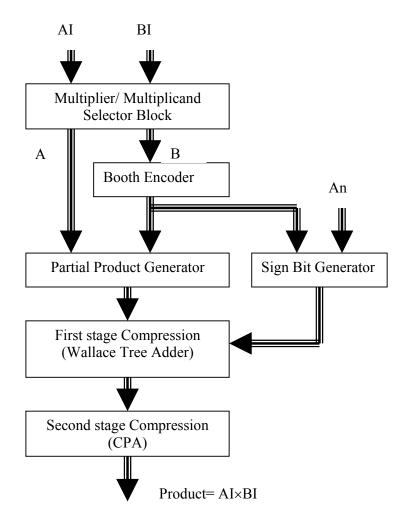

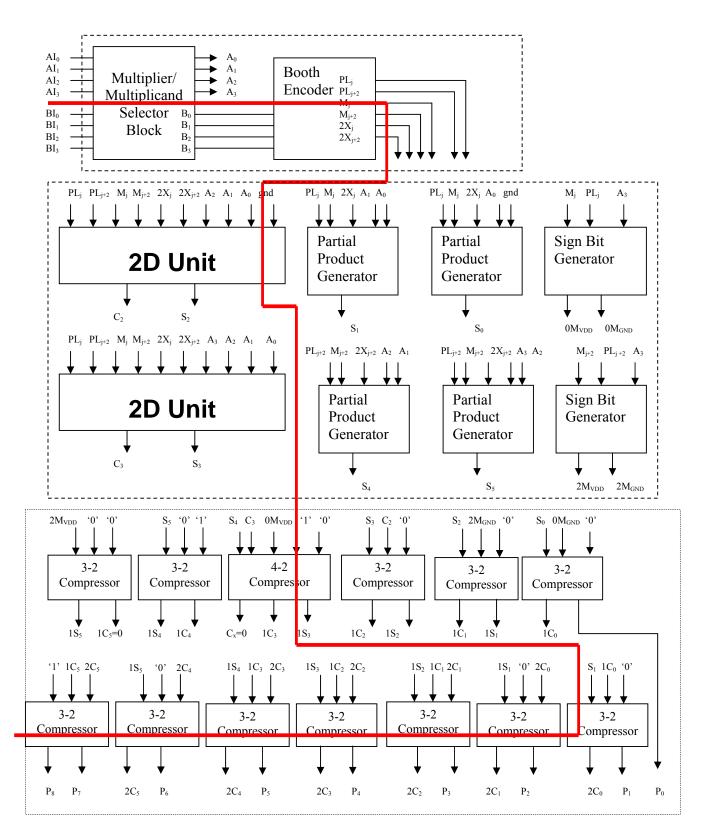

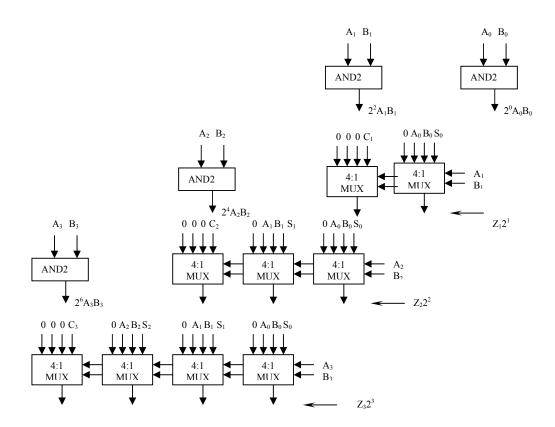

The multiplier's main blocks are multiplier/multiplicand selector block, the modified Booth encoder block, partial product generator block, Wallace tree section (which adds all the partial products simultaneously to produce final two rows of sum and carry). The final two rows of sum and carry are then added using CPA.