## Study on Electronic Behaviour of Nanocrystalline Silicon Thin Film Transistors

### THESIS

Submitted in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY

by

# Prachi Sharma ID No. 2011PHXF408P

Under the Supervision of

## Dr. Navneet Gupta

BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN) INDIA MAY 2016

# BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE PILANI (RAJASTHAN) INDIA

# CERTIFICATE

This is to certify that the thesis entitled **"Study on Electronic Behaviour of Nanocrystalline Silicon Thin Film Transistors"** and submitted by **Ms. Prachi Sharma** ID No. **2011PHXF408P** for award of Ph.D. of the Institute embodies original work done by her under my supervision.

| Signature of the Supervisor | : |                     |

|-----------------------------|---|---------------------|

| Name in Capital Letter      | : | Dr. NAVNEET GUPTA   |

| Designation                 | : | Associate Professor |

:

Date

## **ACKNOWLEDGEMENT**

Taking the opportunities of this page, I would like to express my heartfelt gratitude to those who are involve or have directly or indirectly help me in completing my doctoral work.

First of all let me thank THE ALMIGHTY, whose blessings made me physically and mentally fit to complete my thesis work.

It is my honor to acknowledge my supervisor and also the convener of Doctoral Research Committee, Prof. Navneet Gupta for their guidance throughout this research work. Words won't be enough to express my gratitude for the support he has given to me. His attitude taught me how to handle things calmly, when things went wrong. Heartfelt thanks to you, sir, for spending your valuable time for me.

My sincere thanks are conveyed to my Doctoral Advisory Committee members, Prof. V. K. Chaubey and Dr. Niladri Sarkar, for analyzing my work periodically and giving valuable suggestions.

I am highly thankful to Prof. Chandra Shekhar, Prof. Anu Gupta, Prof Surekha Bhanot, Prof. S. Gurunarayanan, Prof. H. D. Mathur for their encouragement and cooperation during this research work.

I would like to thank all Doctoral Research Committee members of EEE Department for all the useful feedback and suggestions throughout this research work.

I am thankful to Council of Scientific and Industrial Research (CSIR), INDIA, for providing me Senior Research Fellowship (SRF) Award for carrying out my research work.

The major part of fabrication/characterization reported in this thesis was carried out at the Centre of Excellence in Nanoelectronics (CEN), IIT, Bombay under INUP which is sponsored by DIT, MCIT, Government of India. I am extremely grateful to Dr. K Nageswari (INUP Program Manager), Ms. Madhuri Mishra (INUP Project assistant), Mr. Abhijit Rawool (INUP Project assistant) and all technical and non-technical staffs of CEN lab, IIT, Bombay.

I would like to express my earnest gratitude to Dr. V. K. Dubey (Director, PRC, Pilani), Mr. Umakant Goyal (Scientist, SSPL, DRDO), Dr. Uttam Goswami (CEERI, Pilani) for their valuable support and encouragement during this research work.

My strength for doing this research was my family. Special thanks to my mother for always inspiring me and pushing me forward with care and love. This research was simply not possible without her invaluable support and everlasting trust. I would also like to thank my brother, Abhishek Kaushik and my bhabhi, Parul Sharma, for all their love and emotional support.

I would also like to thank my friends, Nishant Tripathi, Prerna Balyan, Nidhi Choudhary, Ambika Shanker Shukla, Ashish Kumar Sharma, V. Balaji, Yogesh B., Jitendra Kumar and Satish Mohanty for standing beside me in all ups and downs during this work.

I want to thank staff members of EEE Department, Mr. Manoj Kumar, Mr. Mahesh Saini and Mr. Amitabh Jangir, for their kind support in teaching assistantship and also like to thank, Mr. Birdi Chand and Mr. Sanjay Bhargava for their help in official work.

#### PRACHI SHARMA

May, 2016

To My Parents Late Shri Kailash Chand Sharma

and

Smt. Rakesh Sharma

### <u>ABSTRACT</u>

Thin film transistor (TFT) works as a switching element and plays an important role for the fabrication of highly functional active matrix (AM) backplanes for large area display applications such as active matrix liquid crystal displays (AMLCDs) and organic light emitting diodes (OLEDs). Nanocrystalline silicon (nc-Si:H) has recently achieved lot of interest over existing hydrogenated amorphous silicon (a-Si:H) and polycrystalline silicon (poly-Si) due to its superior properties which makes it suitable channel material for the fabrication of TFTs. The nc-Si:H material provides high mobility, better stability and high doping efficiency over a-Si:H. In addition, it provides high uniformity and low fabrication cost over poly-Si.

The staggered top-gate n-channel nc-Si:H TFTs structure show higher mobility, better electrical stability and high on-off current ratio. However, the top-gate nc-Si:H TFTs have several issues related to device performance and device stability, on which the thesis focuses. The main goal of the present work is to study the electronic behaviour of nc-Si:H TFT. This goal is achieved by developing device models, performing simulations and experimental work, which will be further useful for the device fabrication.

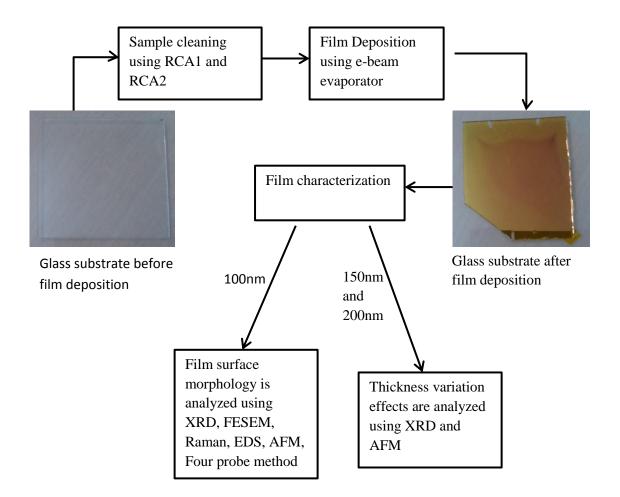

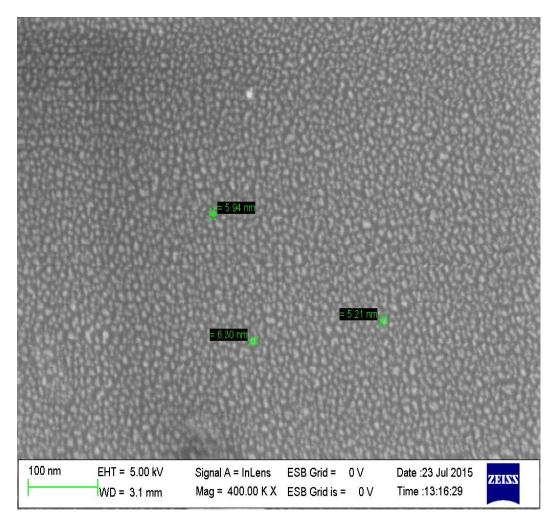

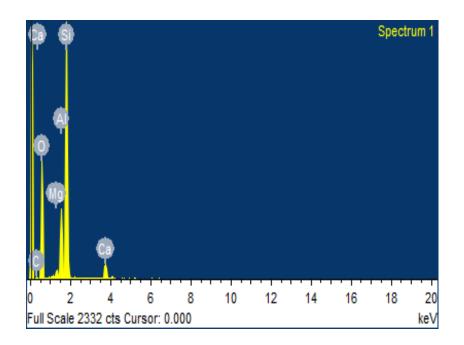

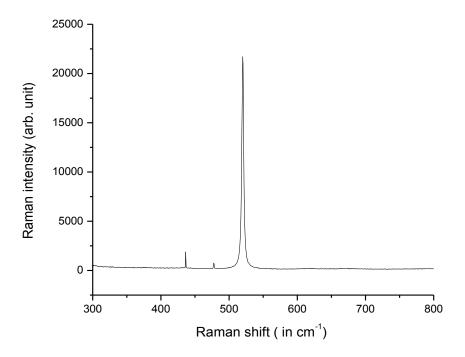

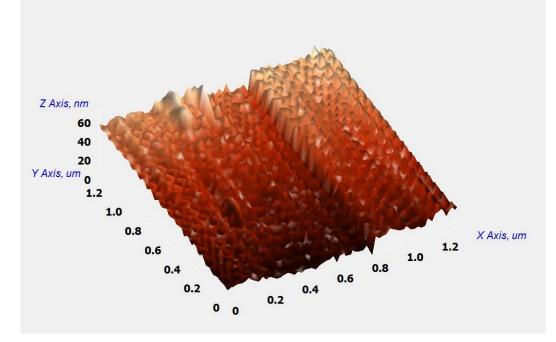

The nc-Si:H film is deposited on Corning glass 1737 substrate using e-beam PVD process to study the structural morphology of nc-Si:H film. The nc-Si:H film having different thicknesses (100nm, 150nm and 200nm) are deposited in the vacuum of 8 x  $10^{-6}$  Torr with controlled beam current of 90mA and deposition rate of 1.2 Å/s. The results show that the optimized nc-Si:H film exhibits high conductivity of the order of 100 S/cm and small grain sizes in the range of 2-15nm. Therefore, this deposited nc-Si:H film is useful as the channel layer for the fabrication of top-gate nc-Si:H TFT and can provide high mobility and hence high on current. The outcome of this study is incorporated in device modeling of nc-Si:H TFT.

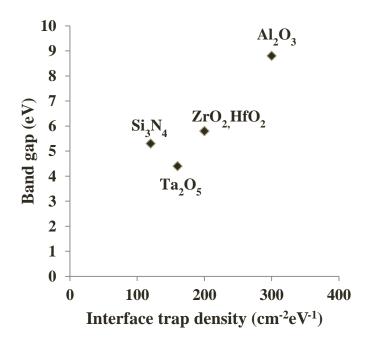

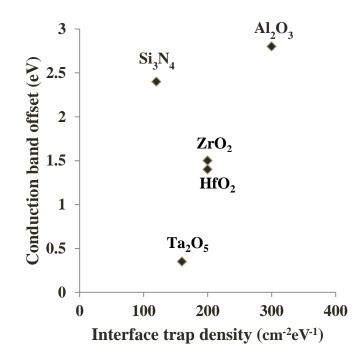

The performance of top-gate nc-Si:H TFT device depends on the material to be used for gate dielectric. Three approaches i.e. Ashby's approach, VIKOR and TOPSIS are used to choose best suitable material for the gate dielectric. Various dielectric materials such as

$Si_3N_4$ ,  $Al_2O_3$ ,  $ZrO_2$ ,  $Ta_2O_5$  and  $HfO_2$  are analyzed. Two performance indices based on four material indices are considered for this analysis. The investigation shows that  $Si_3N_4$ is the best suitable material and can provide high drain current and less leakage current when used for gate dielectric in top-gate nc-Si:H TFT. In this thesis,  $Si_3N_4$  is used as the gate dielectric for the device modeling of top-gate nc-Si:H TFT.

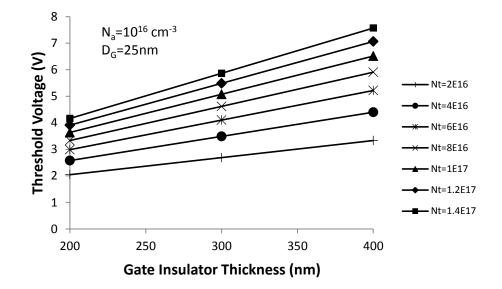

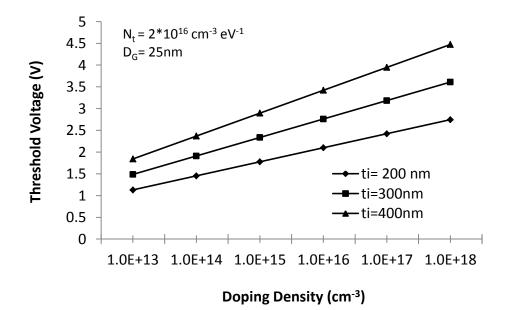

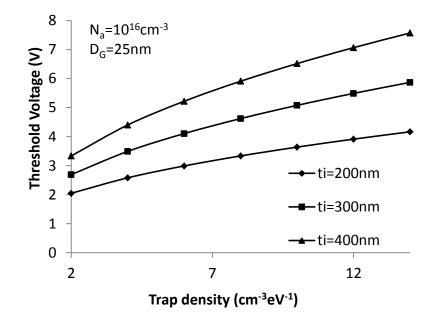

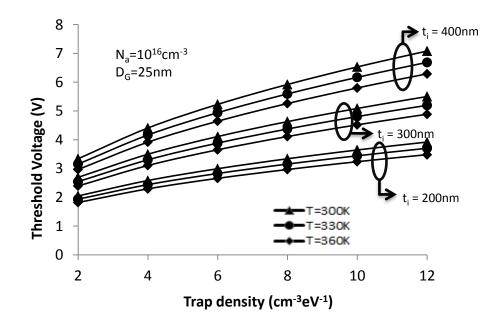

An analytical model for threshold voltage based on physical parameters such as gate insulator thickness, trap density, doping density and temperature, is proposed for top-gate nc-Si:H TFT. The results illustrated that the decrease in gate insulator thickness and the rise in temperature causes the decrease in threshold voltage. The results also show that the threshold voltage increases with increase in trap density and doping concentration. In addition, an analytical model for effective mobility is also proposed by incorporating the effect of grain boundaries. The results show that mobility due to parallel grain boundaries is higher as compared to mobility due to perpendicular grain boundaries. This proposed model is further used for calculating drain current. These proposed models provide the accurate estimation of drain current and thereby can be used for improving the device characteristics.

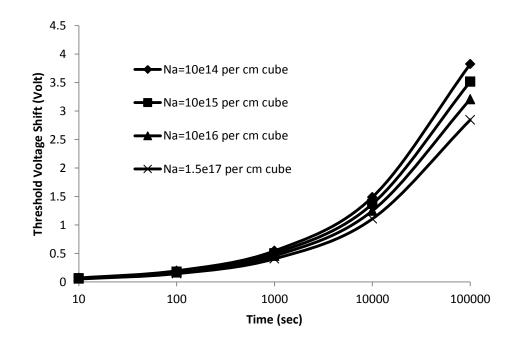

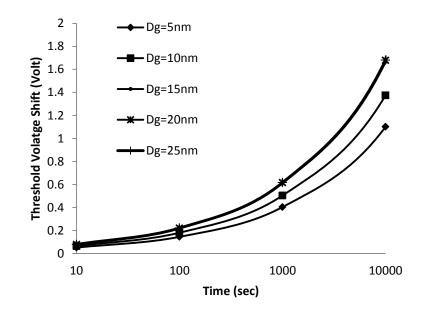

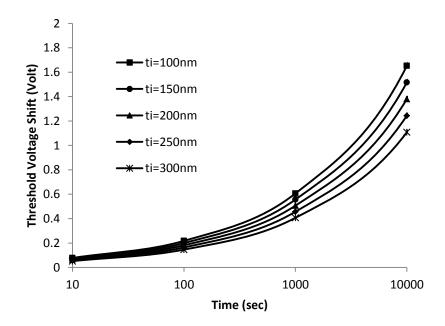

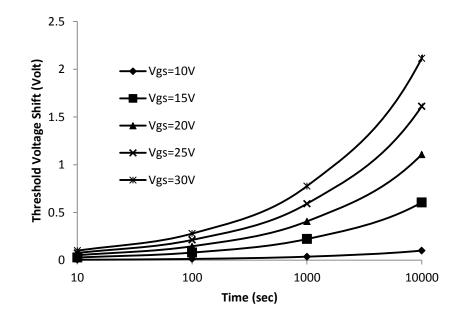

In order to improve the stability of top-gate nc-Si:H TFT, the effects of various physical parameters on threshold voltage shift are also analyzed in this thesis. The model proposed for threshold voltage shift shows that higher trap density, greater doping concentration and larger gate insulator thickness provides stability to top-gate nc-Si:H TFT device. The results also show that for smaller grain sizes ( $D_G < 20$ nm), threshold voltage shift decreases with decrease in grain size. However, for larger grain sizes ( $D_G > 20$ nm), no considerable threshold voltage shift is observed.

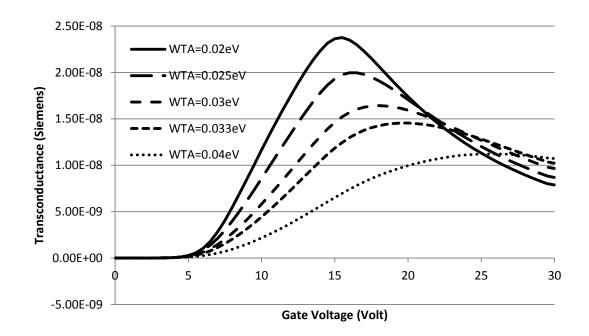

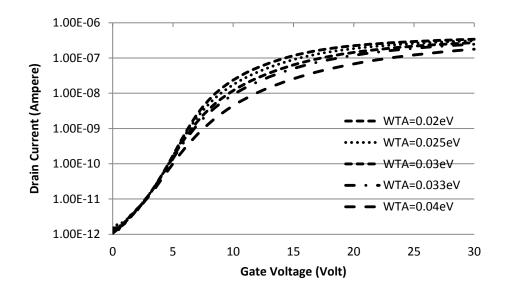

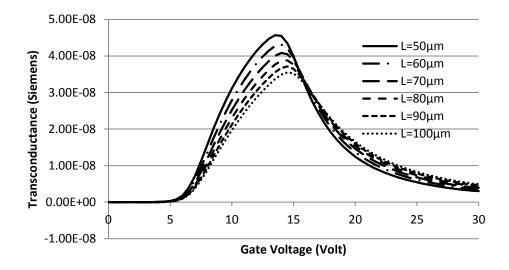

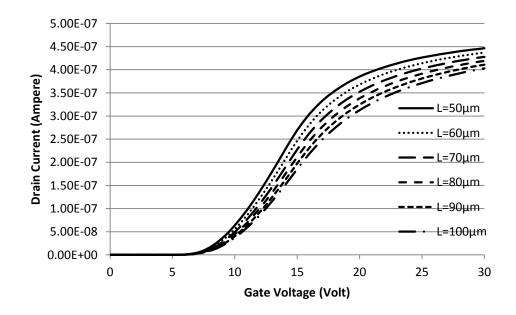

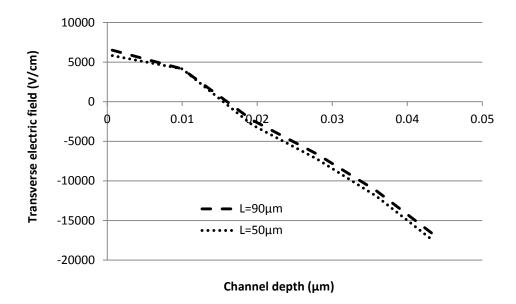

To further get the physical insights about the performance of nc-Si:H TFT, the effects of density of states (DOS) and channel length is analyzed using ATLAS 2D device simulator. The results show that the higher value of characteristic decay energy of channel material causes the degradation in transconductance and drain current. In addition, it is observed that transconductance degradation also occurs with the increase in channel length from 50 to  $100\mu m$  which degrades the device performance.

The physical insight into the device characteristics and device non idealities reported in this thesis provides important step towards TFT backplane and for the production of high performance large area display devices.

# TABLE OF CONTENT

| CERTIFICATE           | i     |

|-----------------------|-------|

| ACKNOWLEDGEMENT       | ii    |

| ABSTRACT              | V     |

| TABLE OF CONTENTS     | viii  |

| LIST OF TABLES        | xi    |

| LIST OF FIGURES       | xii   |

| LIST OF SYMBOLS       | XV    |

| LIST OF ABBREVIATIONS | xviii |

### CHAPTERS

### 1. INTRODUCTION

| 1.1 Background                               | 1  |

|----------------------------------------------|----|

| 1.2 TFT Structure                            | 3  |

| 1.3 Device characteristics                   |    |

| 1.3.1 Density of states (DOS)                | 5  |

| 1.3.2 Threshold voltage $(V_T)$              | 6  |

| 1.3.3 Effective mobility ( $\mu_{eff}$ )     | 6  |

| 1.3.4 Drain current (I <sub>DS</sub> )       | 6  |

| 1.3.5 Parasitic resistance (R)               | 7  |

| 1.3.6 Transconductance (g <sub>m</sub> )     | 7  |

| 1.3.7 Threshold voltage shift $(\Delta V_T)$ | 8  |

| 1.4 Device simulation                        | 8  |

| 1.5 Research motivation and objectives       | 9  |

| 1.6 Organisation of thesis                   | 10 |

### 2. THIN FILM TRANSISTOR: LITERATURE REVIEW

| 2.1 Introduction                                 | 12 |

|--------------------------------------------------|----|

| 2.2 Fabrication of nc-Si:H based TFTs            | 13 |

| 2.3 Conduction models                            | 21 |

| 2.4 Electrical instability in TFTs               | 25 |

| 2.4.1 Models for threshold voltage shift in TFTs | 27 |

| 2.5 Conclusion                                   | 35 |

### 3. DEPOSITION AND CHARACTERIZATION OF nc-Si:H FILM

| 3.1 Introduction       | 36 |

|------------------------|----|

| 3.2 Sample preparation | 40 |

| 3.3 Electron-beam evaporation system | 41 |

|--------------------------------------|----|

| 3.4 Characterization of nc-Si:H film | 43 |

| 3.4.1 Surface morphology             | 43 |

| 3.4.2 Conductivity measurement       | 51 |

| 3.5 Conclusion                       | 52 |

### 4. MATERIAL SELECTION FOR GATE DIELECTRIC

| 4.1. Introduction                    | 53 |

|--------------------------------------|----|

| 4.2 Material selection approaches    |    |

| 4.2.1 Ashby's approach               | 55 |

| 4.2.2 VIKOR approach                 | 57 |

| 4.2.3 TOPSIS approach                | 58 |

| 4.3 Performance and material indices | 60 |

| 4.4 Results and analysis             |    |

| 4.4.1 Ashby's approach               | 63 |

| 4.4.2 VIKOR approach                 | 66 |

| 4.4.3 TOPSIS approach                | 68 |

| 4.5 Conclusion                       | 69 |

|                                      |    |

### 5. ELECTRICAL CHARACTERISTICS

| 5.1 Introduction                           | 70 |

|--------------------------------------------|----|

| 5.2 Analytical device modeling             | 71 |

| 5.2.1 Threshold voltage                    | 73 |

| 5.2.2 Effective mobility and drain current | 78 |

| 5.3 Conclusion                             | 87 |

### 6. NON-IDEALITIES IN nc-Si:H TFT

| 6.1 Introduction                 | 88  |

|----------------------------------|-----|

| 6.2 Threshold voltage shift      | 89  |

| 6.3 Transconductance degradation | 96  |

| 6.4 Conclusion                   | 103 |

### 7. CONCLUSION

| 7.1 Conclusion           | 105 |

|--------------------------|-----|

| 7.2 Future scope of work | 108 |

| REFERENCES                        | 126 |

|-----------------------------------|-----|

| LIST OF PUBLICATIONS              | 142 |

| BRIEF BIOGRAPHY OF THE CANDIDATE  | 144 |

| BRIEF BIOGRAPHY OF THE SUPERVISOR | 145 |

# LIST OF TABLES

| Table No. | Title                                                                     | Page No. |

|-----------|---------------------------------------------------------------------------|----------|

| 1.1       | Comparison between different materials used for the TFT fabrication       | 3        |

| 2.1       | Experimental published data for top-gate nc-Si:H TFT                      | 18       |

| 3.1       | Experimental published data for nc-Si:H film                              | 37       |

| 4.1       | Properties of possible high-k gate dielectric material                    | 64       |

| 4.2       | Ranking of alternatives by VIKOR approach                                 | 67       |

| 4.3       | Ranking of alternatives by TOPSIS approach                                | 68       |

| 5.1       | Parameters used in the calculations                                       | 86       |

| 6.1       | Model parameters used in the calculations                                 | 91       |

| 6.2       | Calculated and experimental threshold volatge shift at different $V_{GS}$ | 94       |

| 6.3       | ATLAS device simulation parameter for nc-Si:H TFT                         | 98       |

# LIST OF FIGURES

| Figure No. | Caption                                                                                                                                                                                                                                                                                                                                                                                                     | Page No. |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.1.       | Illustration of four basic types of TFT structures                                                                                                                                                                                                                                                                                                                                                          | 4        |

| 1.2        | Density of states within the band gap of nc-Si:H                                                                                                                                                                                                                                                                                                                                                            | 5        |

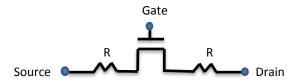

| 1.3        | Parasitic resistance in top-gate staggered nc-Si:H TFT                                                                                                                                                                                                                                                                                                                                                      | 7        |

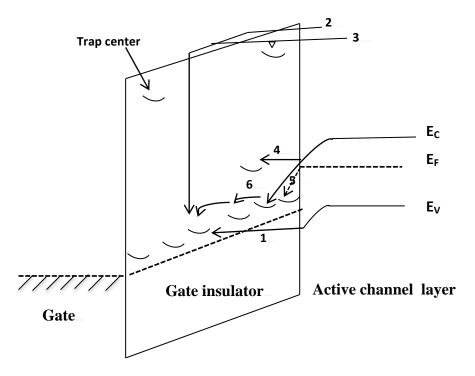

| 2.1        | Charge Trapping Mechanisms: (1) Direct tunneling from valence band (2) Fowler-Nordheim injection, (3) trap assisted injection, (4) constant energy tunneling from silicon conduction band, (5) tunneling from conduction band to $E_f$ (phonon assisted or via surface states), (6) hopping at the fermi level. Chain line represents quasi- Fermi level at t=0. Arrow represents the direction of electron | 26       |

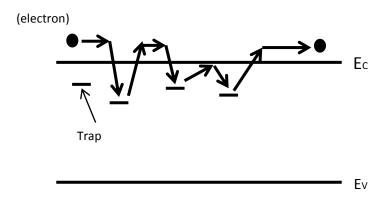

| 2.2        | Trap and release model of electrons from band tail states                                                                                                                                                                                                                                                                                                                                                   | 26       |

| 3.1        | Process flow for deposition and characterization of nc-Si:H film                                                                                                                                                                                                                                                                                                                                            | 40       |

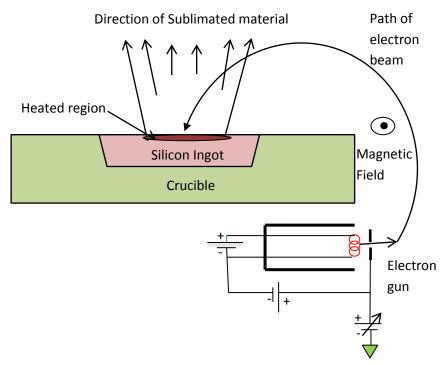

| 3.2        | Schematic of e-beam evaporator                                                                                                                                                                                                                                                                                                                                                                              | 42       |

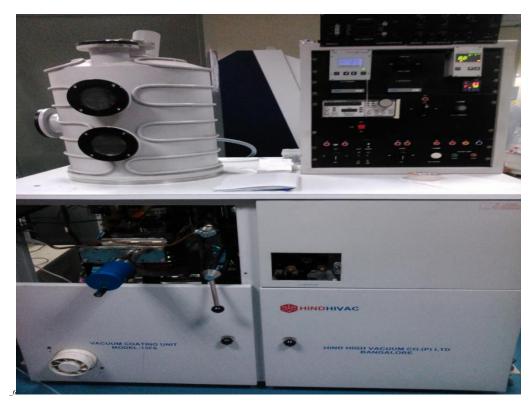

| 3.3        | 4-target e-beam evaporation setup at IIT Bombay (CEN)                                                                                                                                                                                                                                                                                                                                                       | 42       |

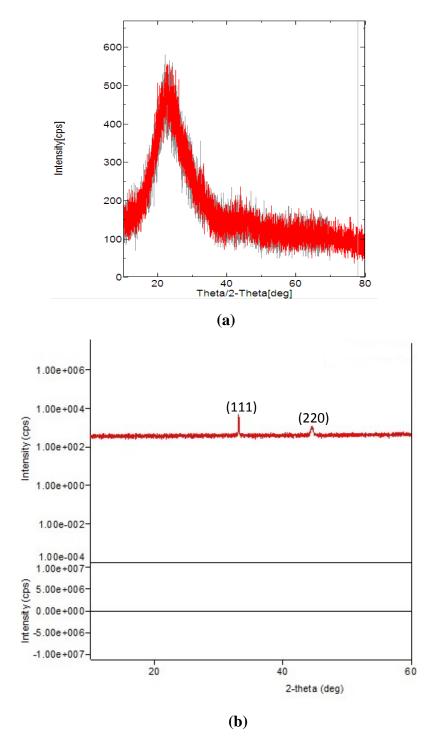

| 3.4        | XRD Results (a) Before annealing (b) After annealing at room temperature                                                                                                                                                                                                                                                                                                                                    | 44       |

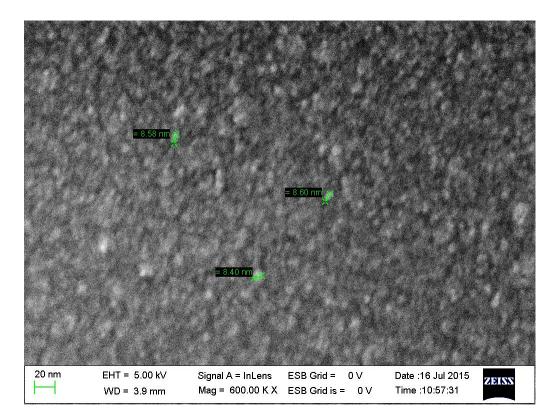

| 3.5        | FESEM Micrograph of 100nm thick nc-Si:H film                                                                                                                                                                                                                                                                                                                                                                | 46       |

| 3.6        | EDS results (a) Analysis graph (b) Elemental data of 100nm thick nc-Si:H film                                                                                                                                                                                                                                                                                                                               | 47       |

| 3.7        | RAMAN Spectra of 100nm thick nc-Si:H film                                                                                                                                                                                                                                                                                                                                                                   | 48       |

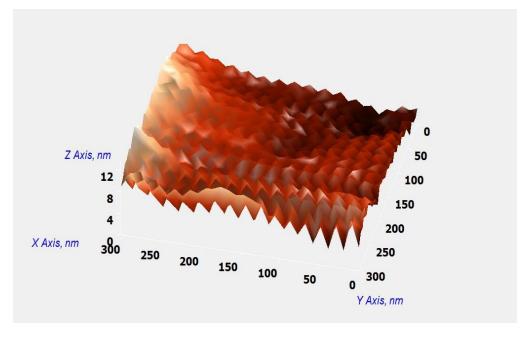

| 3.8        | AFM micrograph of 100nm thick nc-Si:H film                                                                                                                                                                                                                                                                                                                                                                  | 48       |

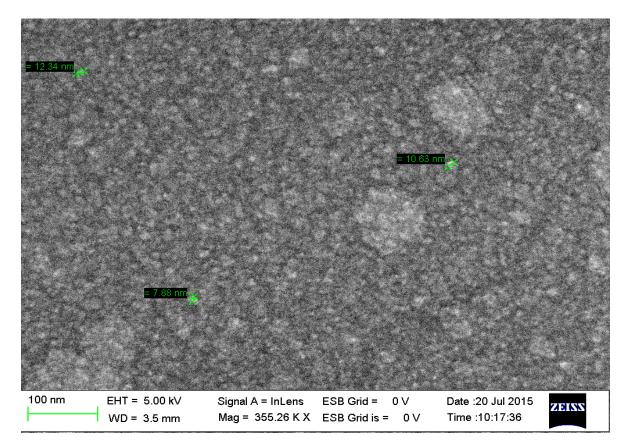

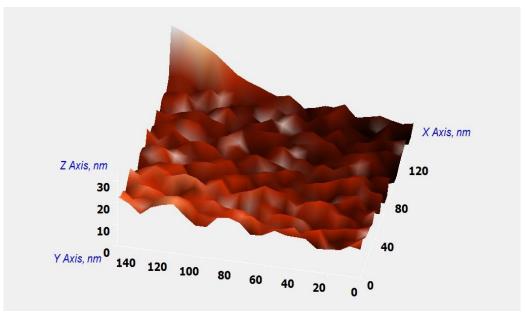

| 3.9        | Results of 150nm thick nc-Si:H film (a) SEM Micrograph (b) AFM Graph                                                                                                                                                                                                                                                                                                                                        | 49       |

| 3.10       | Results of 200nm thick nc-Si:H film (a) SEM Micrograph (b) AFM Graph                                                                                                                                                                                                                                                                                                                                        | 50       |

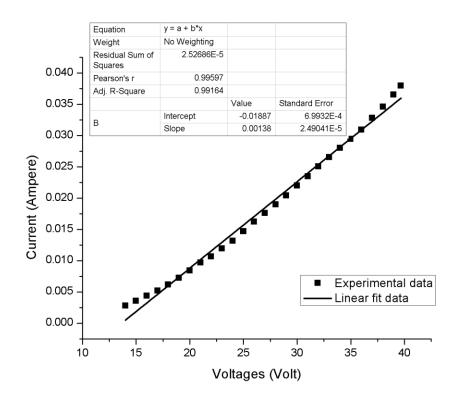

| 3.11       | I-V curve for 100nm thick nc-Si:H film. Square dotted line represents the experimental I-V data extracted using 4-probe method. Solid line shows the fitted data which gives the slope of 0.00138.                                                                                                                                                                                                          | 51       |

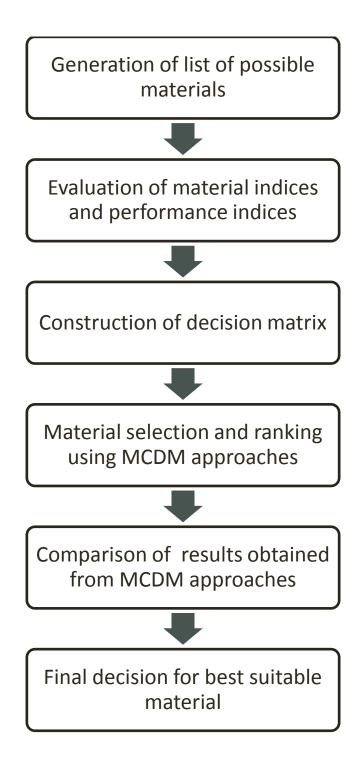

| 4.1        | Flowchart for material selection                                                                                                                                                                                                                                                                                                                                                                            | 56       |

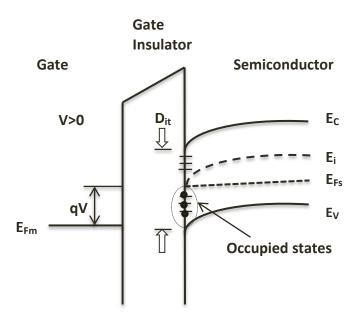

| 4.2        | Location of interface trap charges                                                                                                                                                                                                                                                                                                                                                                          | 62       |

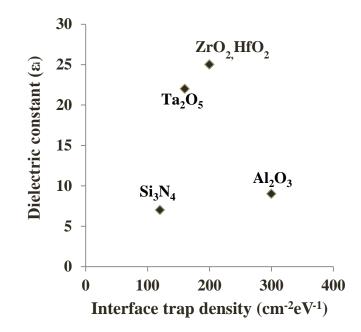

| 4.3        | Variation of dielectric constant vs. interface trap density for different possible high-k gate dielectric material                                                                                                                                                                                                                                                                                          | 65       |

| 4.4        | Variation of band gap vs. interface trap density for different                                                                                                                                                                                                                                                                                                                                              | 65       |

possible high-k gate dielectric material

|      | possible high-k gate dielectric material                                                                                                                                                                                                                                                                                    |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.5  | Variation of conduction band offset vs. interface trap density for different possible high-k gate dielectric material                                                                                                                                                                                                       | 66 |

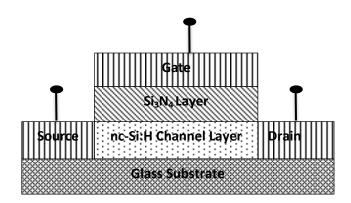

| 5.1  | Schematic view of top-gate nc-Si:H TFTs                                                                                                                                                                                                                                                                                     | 72 |

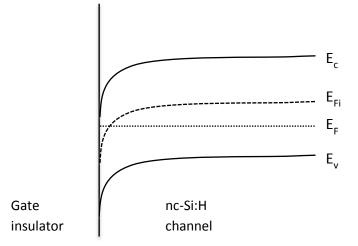

| 5.2  | Energy band diagram of top-gate nc-Si:H TFT under strong inversion condition                                                                                                                                                                                                                                                | 72 |

| 5.3  | Variation of threshold voltage as a function of gate insulator<br>thickness for different values of trap density                                                                                                                                                                                                            | 76 |

| 5.4  | Variation of threshold voltage as a function of doping density<br>for different values of gate insulator thickness                                                                                                                                                                                                          | 76 |

| 5.5  | Variation of threshold voltage as a function of trap density for different values of gate insulator thickness                                                                                                                                                                                                               | 77 |

| 5.6  | Variation of threshold voltage as a function of trap density for<br>different values of gate insulator thickness at different<br>temperatures                                                                                                                                                                               | 77 |

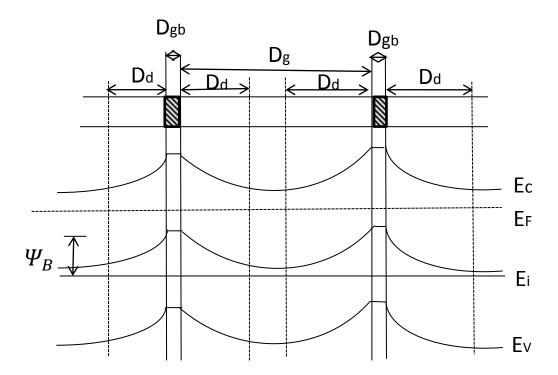

| 5.7  | (top) Cross-section in presence of perpendicular (transverse) grain boundaries. The shaded regions represent the grain boundaries. (below) Energy band diagram along the length of the nc-Si:H film                                                                                                                         | 79 |

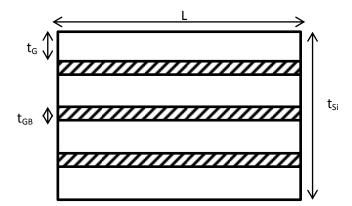

| 5.8  | Channel in presence of parallel (longitudinal) grain boundaries. The shaded regions represent the grain boundaries                                                                                                                                                                                                          | 79 |

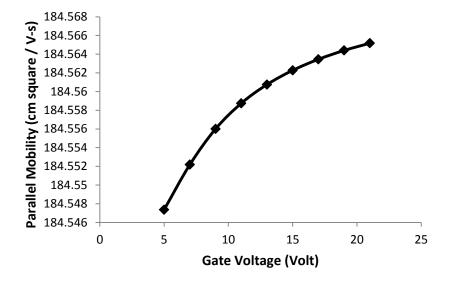

| 5.9  | Computed variation of parallel mobility with gate voltage at room temperature                                                                                                                                                                                                                                               | 84 |

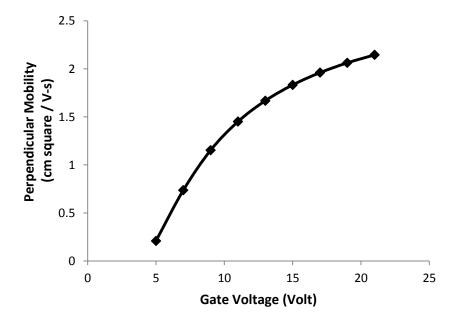

| 5.10 | Computed variation of perpendicular mobility with gate voltage at room temperature                                                                                                                                                                                                                                          | 84 |

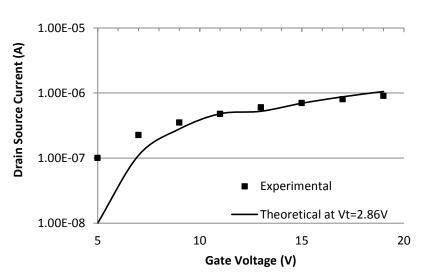

| 5.11 | Plot of the transfer characteristics of n-channel nc-Si:H TFT (W=200 $\mu$ m, L=50 $\mu$ m) calculated at V <sub>DS</sub> =1V for V <sub>T</sub> =2.86V, N <sub>a</sub> =10 <sup>16</sup> cm <sup>-3</sup> and N <sub>t</sub> = 2×10 <sup>16</sup> cm <sup>-3</sup> . Solid dark line shows the result of C. H. Lee et. al. | 85 |

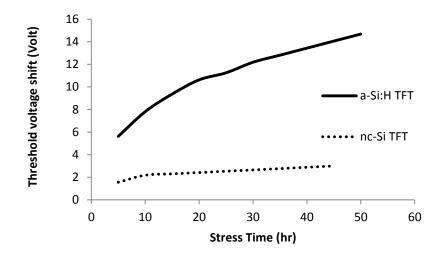

| 6.1  | Comparison between the threshold voltage shift in a-Si:H TFT and nc-Si:H TFT as a function of stress time at temperature $75^{\circ}$ C and stress current of $10\mu$ A                                                                                                                                                     | 90 |

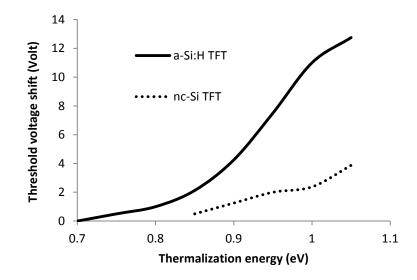

| 6.2  | Comparison between the threshold voltage shift in a-Si:H TFT and nc-Si:H TFT as a function of thermalization energy at temperature $75^{\circ}$ C and stress current $15\mu$ A                                                                                                                                              | 90 |

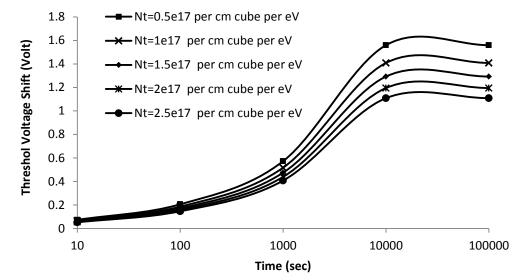

| 6.3  | Computed variations of threshold voltage shift in the top gated<br>nc-Si:H TFTs as a function of time for different trap state<br>densities                                                                                                                                                                                 | 93 |

| 6.4  | Computed variations of threshold voltage shift in the top gated<br>nc-Si:H TFTs as a function of time for different values of<br>doping concentration                                                                                                                                                                       | 93 |

| 6.5  | Computed variations of threshold voltage shift in the top gated $nc-Si:H$ TFTs $D_G$ as a function of time for different grain sizes.                                                                                                                                                | 94  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.6  | Computed variations of threshold voltage shift in the top gated<br>nc-Si:H TFTs as a function of time for different value of gate<br>insulator thickness                                                                                                                             | 95  |

| 6.7  | Computed variations of threshold voltage shift in the top gated<br>nc-Si:H TFTs as a function of time under different gate bias<br>stress                                                                                                                                            | 95  |

| 6.8  | Equivalent circuit of the TFT used for device simulation                                                                                                                                                                                                                             | 97  |

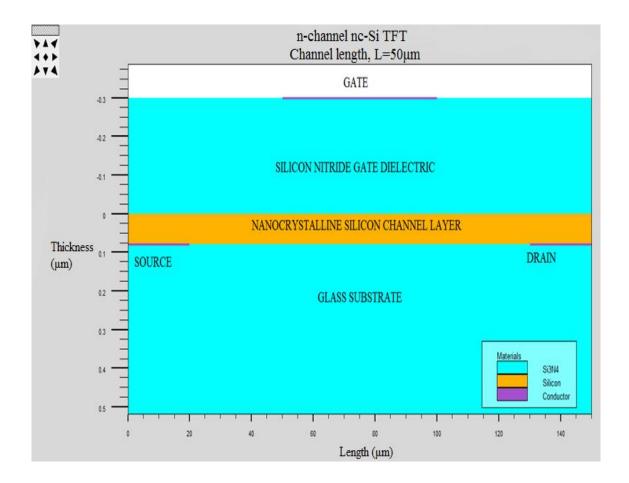

| 6.9  | nc-Si:H TFT structure for ATLAS simulation                                                                                                                                                                                                                                           | 97  |

| 6.10 | Variation of transconductance as a function of gate voltage for different values of tail states                                                                                                                                                                                      | 99  |

| 6.11 | Variation of drain current as a function of gate voltage for different values of tail states                                                                                                                                                                                         | 99  |

| 6.12 | Variation of transconductance as a function of gate voltage for different values of channel length                                                                                                                                                                                   | 101 |

| 6.13 | Variation of drain current as a function of gate voltage for different values of channel length                                                                                                                                                                                      | 101 |

| 6.14 | Variation of transverse electric field versus channel length depth for $L=90\mu m$ and $50\mu m$                                                                                                                                                                                     | 102 |

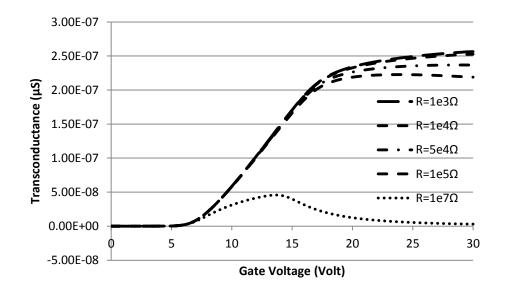

| 6.15 | Variation of transconductance as a function of gate voltage for different values of parasitic resistance                                                                                                                                                                             | 102 |

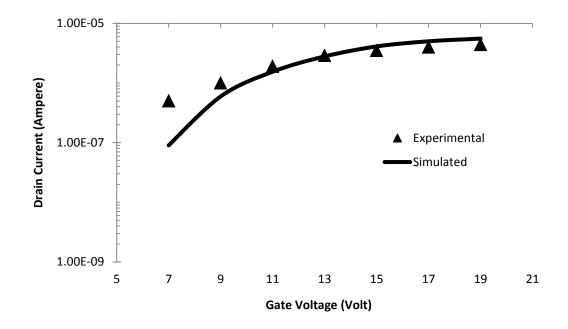

| 6.16 | Plot of the transfer characteristic of nc-Si:H top-gate TFT (W=200 $\mu$ m and L=50 $\mu$ m) simulated at V <sub>DS</sub> =10V for WTA=0.02 and R=10 <sup>7</sup> $\Omega$ . Solid line shows the experimental results of C. H. Lee et. al. and dotted line shows simulated results. | 103 |

# LIST OF SYMBOLS

- $\mu_{eff}$  Effective mobility

- I<sub>DS</sub> Drain current

- C<sub>i</sub> Gate insulator capacitance

- W Channel Width

- L Channel Length

- V<sub>GS</sub> Gate voltage

- V<sub>T</sub> Threshold voltage

- V<sub>DS</sub> Drain voltage

- R Parasitic resistance

- g<sub>m</sub> Transconductance

- B Full width half maxima

- $\lambda$  Wavelength of X-rays

- K Scherrer constant

- $\rho_f$  nc-Si:H film Resistivity

- Rs Sheet resistance of nc-Si:H film

- t<sub>si</sub> nc-Si:H film thickness

- $\sigma_{eff} \qquad \ \ Conductivity of nc-Si:H film$

- F Functional requirements

- G Geometric parameters

- M Material indices

- P Performance of material

- $x_{ij}$  Performance alternative of  $i^{th}$  alternative with respect to the  $j^{th}$  criteria

- X Decision Matrix

- *G<sub>i</sub>* Maximum group utility

- $R_i$  Minimum regret of the opponent

- w<sub>i</sub> Weights of criteria

- $Q_i$  i<sup>th</sup> alternative of VIKOR

- *v* weight of maximum group utility

- *A<sup>i</sup>* Alternative considered

- $S^*$  Euclidean distance from the ideal solution

- A<sup>\*</sup> Ideal solution

- $S^{-}$  Euclidean distance from negative ideal solution

- A<sup>-</sup> Negative ideal solution

- *N<sub>m</sub>* Normalized decision matrix

- $n_{ii}$  Element obtained by the Euclidean normalization

- $V_{ij}$  Product of  $n_{ij}$  and  $w_j$

- V Weighted normalized matrix obtained from  $v_{ij}$

- $Z_i$  Relative closeness to the ideal solution

| I <sub>PFO</sub>                   | Generation current at zero electric field                                 |

|------------------------------------|---------------------------------------------------------------------------|

| I <sub>PF</sub>                    | Leakage current due to Poole-Frenkel emission                             |

|                                    | PF coefficient                                                            |

| $\beta_{PF}$                       | Flat band voltage                                                         |

| $V_{FB}$                           | Dielectric constant of gate insulator                                     |

| $\mathcal{E}_i$                    | -                                                                         |

| $t_i$                              | Thickness of gate insulator                                               |

| $\mathcal{E}_{nc-si}$              | Permittivity of nc-Si:H channel layer                                     |

| k                                  | Boltzmann constant                                                        |

| Т                                  | Temperature                                                               |

| $\mathcal{E}_{o}$                  | Permittivity of free space                                                |

| $E_{g}$                            | Energy band gap                                                           |

| $\mathcal{E}_{i,high-k}$           | Dielectric constant of high-k material                                    |

| $\Delta E_{c}$                     | Conduction band offset                                                    |

| $Q_{it}$                           | Interface trapped charge                                                  |

| $D_{it}$                           | Interface charge density                                                  |

| C <sub>LF</sub>                    | Capacitance measured at the onset of strong inversion at low frequencies  |

| $C_{HF}$                           | Capacitance measured at the onset of strong inversion at high frequencies |

| φ                                  | Electrostatic potential                                                   |

| ρ<br>Da                            | Charge density                                                            |

| $\mathbf{D}_{\mathrm{G}}$<br>$N_t$ | Average grain size<br>Density of trapping states                          |

| E                                  | Electric field                                                            |

| q                                  | Charge                                                                    |

| E <sub>s</sub>                     | Surface electric field                                                    |

| φ <sub>s</sub>                     | Surface potential                                                         |

| Na                                 | Doping density                                                            |

| ni                                 | intrinsic carrier density                                                 |

| h "                                | Planck's constant                                                         |

| $m_{n_{*}}$                        | Effective electrons masses in nc-Si:H                                     |

| m <sub>p</sub>                     | Effective hole masses in nc-Si:H                                          |

| E <sub>i</sub><br>D <sub>GB</sub>  | Gate insulator electric field<br>Size of grain boundary                   |

| $D_{GB}$<br>$D_d$                  | Width of depletion region                                                 |

| ΨB                                 | Potential barrier across grain boundaries                                 |

| R <sub>G</sub>                     | Resistance of single grain                                                |

| R <sub>GB</sub>                    | Resistance of grain boundary                                              |

| ng                                 | Number of grains                                                          |

| $\mu_{G}$                          | Mobility of grain                                                         |

| $\mu_{GB}$               | Mobility of grain boundary                                              |

|--------------------------|-------------------------------------------------------------------------|

| $\sigma_G$               | Conductivity of the grain                                               |

| $\sigma_{GB}$            | Conductivity of the grain boundary                                      |

| А                        | Cross sectional area of channel                                         |

| R <sub>T</sub>           | Total resistance consist of grain and grain boundary resistances        |

| N <sub>d</sub>           | Electron concentration in the bulk of the grain                         |

| n                        | Electron concentration in grain boundaries                              |

| $\mu_{perp}$             | Effective mobility in presence of perpendicular grain boundaries        |

| Ν                        | Total carrier concentration in the strong inversion channel             |

| n <sub>t</sub>           | Density of charged states at the grain boundaries                       |

| $\mu_0$                  | Carrier mobility at the equilibrium condition                           |

| t <sub>G</sub>           | Thickness of single grain                                               |

| t <sub>GB</sub>          | Thickness of grain boundary                                             |

| $A_G$                    | Cross sectional area of grain                                           |

| $A_{GB}$                 | Cross sectional area of grain boundary                                  |

| $\sigma_{eff,perp}$      | Equivalent conductivity of the channel due to perpendicular grain       |

|                          | boundaries                                                              |

| $\mu_{parallel}$         | Effective mobility in presence of parallel grain boundaries             |

| $\sigma_{eff, parallel}$ | Equivalent conductivity of the channel due to parallel grain boundaries |

| М                        | Mobility degradation factor                                             |

| τ                        | Characteristic trapping time                                            |

| β                        | Stretched-exponential exponent                                          |

| E <sub>C</sub>           | Conduction band edge energy                                             |

| $E_V$                    | Valence band edge energy                                                |

| NTA                      | Conduction band edge intercept tail states density                      |

| NTD                      | Valence band edge intercept tail states density                         |

| NGA                      | Conduction band edge intercept deep states density                      |

| NGD                      | Valence band edge intercept deep states density                         |

| EGA                      | Peak energy of deep states as $E=E_C$                                   |

| EGD                      | Peak energy of deep states as $E=E_V$                                   |

| WTA                      | Characteristic decay energy of tail states as E=E <sub>C</sub>          |

| WTD                      | Characteristic decay energy of tail states as $E=E_V$                   |

| WGA                      | Characteristic decay energy of deep states as $E=E_C$                   |

| WGD                      | Characteristic decay energy of deep states as $E=E_V$                   |

|                          |                                                                         |

# LIST OF ABBREVIATIONS

| TFT     | Thin Film Transistor                                            |

|---------|-----------------------------------------------------------------|

| LCDs    | Liquid Crystal Displays                                         |

| OLEDs   | Organic Light Emitting Diodes                                   |

| a-Si:H  | Hydrogenated Amorphous Silicon                                  |

| poly-Si | Polycrystalline Silicon                                         |

| PECVD   | Plasma Enhanced Chemical Vapour Deposition                      |

| CMOS    | Complementary Metal Oxide Semiconductor                         |

| nc-Si:H | Nanocrystalline Silicon                                         |

| HWCVD   | Hot Wire Chemical Vapour Deposition                             |

| DOS     | Density Of States                                               |

| MOSFET  | Metal-Oxide-Semiconductor Field-Effect-Transistor               |

| ICP-CVD | Inductively Coupled Plasma Chemical Vapour Deposition           |

| EBPVD   | Electron-Beam Assisted Physical Vapor Deposition                |

| FESEM   | Field Emission Scanning Electron Microscopy                     |

| AFM     | Atomic Force Microscope                                         |

| XRD     | X-Ray Diffraction                                               |

| EDS     | Electron Diffraction Spectroscopy                               |

| RCA     | Radio Corporation of America                                    |

| MCDM    | Multi-Criteria Decision Making                                  |

| MODM    | Multi-Objective Decision Making                                 |

| MADM    | Multi- Attribute Decision Making                                |

| VIKOR   | VlseKriterijumska Optimizacija I Kompromisno Resenje in Serbian |

| TOPSIS  | Technique for Order Preference by Similarity to Ideal Solution  |

|         |                                                                 |

## **CHAPTER 1**

### INTRODUCTION

### **1.1 BACKGROUND**

Thin film transistor (TFT) is commonly used as a pixel addressing element and is the heart of large area electronic devices over the past few decades [1-3]. Large-area electronics involves various display applications such as liquid crystal displays (LCDs) and organic light emitting diodes (OLEDs). The aim of these applications is to spread electronic components over large area substrate at low fabrication cost.

For the production of new generation large displays, an active matrix addressing scheme is required for display panels where pixels are located at row and column interactions in order to minimize capacitive losses in column and row lines. This addressing scheme basically consists of two TFTs per pixel, of which one is operated under continuous gate bias and hence requires a high electrical stability.

For fabricating TFTs, various materials can be used as an active channel layer. The commonly used materials are hydrogenated amorphous silicon (a-Si:H) and polycrystalline silicon (poly-Si).

The main advantage of a-Si:H is the possibility of direct deposition over large area at relatively low temperature [4]. Plasma Enhanced Chemical Vapour Deposition (PECVD) is commonly used technique for the a-Si:H deposition over large area at low temperatures. The a-Si:H is an amorphous silicon alloy with incorporated hydrogen atoms. However the disadvantages of a-Si:H are low electron mobility and instability due

to low temperature PECVD process which causes the formation of defect states. The a-Si:H has electron mobility as low as  $0.1-1 \text{ cm}^2/\text{Vs}$  [5] and hole mobility is so low that the p-type devices are not used in any application.

Another material commonly used for the fabrication of TFT is poly-Si. It is having low hydrogen atoms in large grained silicon films and thus poly-Si is not called as "hydrogenated". The main advantages of poly-Si are high electron mobility and better stability. Since poly-Si is a network of randomly oriented crystalline grains interconnected by thin grain boundaries, the defects in poly-Si are concentrated in the grain boundaries whereas in a-Si:H materials they are uniformly distributed in the bulk. In case of poly-Si, large grains are preferred, as the larger grain size results in lesser grain boundaries across the channel. This results in lower density of defect states [6] in poly-Si, leading to lesser trapping of carriers at grain boundaries and hence higher mobility (~100 cm<sup>2</sup>/Vs) [7] than a-Si:H materials. Poly-Si TFTs provide sufficient electron and hole mobility in n-type and p-type devices for CMOS (complementary metal oxide semiconductor) operation. The main problem with poly-Si is that the crystallization process requires a much higher temperature (usually higher than 300°C) than the a-Si:H deposition temperature. In addition to this problem, poly-Si also suffers from poor spatial uniformity as random positioning of grain boundaries causes irregularity across the channel. This results in mobility degradation and threshold voltage non-uniformity over large area substrate [7, 8].

Nanocrystalline silicon (nc-Si:H) has been proven as the best alternative material over a-Si:H and poly-Si. The advantages of nc-Si:H over a-Si:H are better stability under bias and light stress and high field effect mobility due to the presence of higher silicon crystallites [9]. For top gated devices, field effect mobility ( $\mu_{FET}$ ) is in range of 40 cm<sup>2</sup>/Vs [10] to 150 cm<sup>2</sup>/Vs [11] and for bottom gate, it is in the range of 0.5-3 cm<sup>2</sup>/Vs [12,13]. Due to the presence of lower hydrogen concentration, nc-Si:H have improved stability under bias and illumination stress [9] than a-Si:H. The benefits of nc-Si:H over poly-Si are low processing temperatures, low manufacturing cost and better uniformity [14]. Hot wire chemical vapour deposition (HWCVD) provide possibility of direct deposition of nc-Si:H at very low temperature over large area and at high deposition rates [14]. The

resulting nc-Si:H film consists of small silicon crystallites than poly-Si, with an average grain size of a few nanometers, embedded into a-Si:H. However, the main problem with nc-Si:H TFT is that it is affected from high drain leakage currents, i.e. off-current.

Table 1.1 illustrates the comparison between a-Si:H, poly-Si and nc-Si:H materials used for TFT fabrication.

### **1.2 TFT STRUCTURE**

The TFTs consist of three electrodes (i.e. source, drain and gate), gate insulator, and thin semiconductor layer.

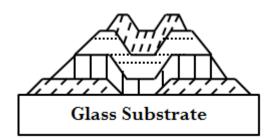

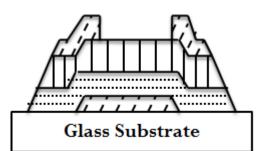

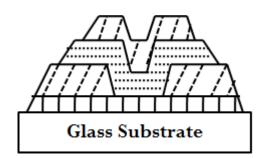

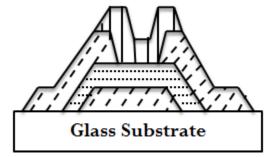

Based on the level of the gate electrode, the TFTs are divided into two types, top gate TFT and bottom gate TFT. In top gate TFT, the gate electrode is located above the semiconductor layer whereas in bottom gate TFT, the gate electrode is located below the semiconductor layer. These two types are further subdivided into coplanar and staggered devices, giving a total of four basic types of TFT structures. The architectural view of these structures is illustrated in Fig. 1.1. The term coplanar/staggered describes the location of source and drain electrodes with respect to the gate electrode. In coplanar case, the source and drain electrodes are located at the opposite side to the gate electrode separated with the semiconductor layer. Further, TFTs can be characterized based on various device characteristics.

Table 1.1: Comparison between different materials used for theTFT fabrication [15, 16]

| Parameters   | a-Si:H      | nc-Si:H                 | Poly-Si   |

|--------------|-------------|-------------------------|-----------|

| Mobility     | Low         | Much higher than a-Si:H | High      |

| Circuit type | NMOS        | NMOS/PMOS               | NMOS/PMOS |

| Stability    | Less stable | More stable than a-Si:H | Stable    |

| Uniformity   | High        | Potentially high        | Poor      |

| Cost         | Low         | Low                     | High      |

Staggered

**Inverted Staggered**

Coplanar

**Inverted Coplanar**

.....

Semiconductor

Electrodes

Insulator

Fig. 1.1. Illustration of four basic types of TFT structures [17]

### **1.3 DEVICE CHARACTERISTICS**

The performance of nc-Si:H TFT can be analyzed on the basis of various device characteristic parameters. These characteristic parameters plays important role in the evaluation of the performance of nc-Si:H TFT. These characteristic parameters are mentioned below:-

#### **1.3.1 Density of States (DOS):**

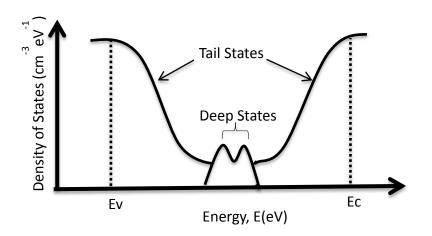

The low temperature process used for nc-Si:H deposition as well as the amorphous nature of non-crystalline substrate (like glass) lead to the formation of material having missing atoms. Deep defect states in the forbidden energy gap of the nc-Si:H are associated with these missing atoms, i.e. dangling bonds. Deep defect states are also associated with the deviation in bond length and angle which results in states below the conduction band, known as band tail states. The density of states (DOS) in nc-Si:H (as depicted in Fig. 1.2) is composed of two Gaussian distributed deep defect states (acceptor-like and donor-like deep states) and two exponentially distributed band tail states (acceptor-like and donor-like tail states). The DOS has a strong relevance on performance of nc-Si:H TFT. In this thesis, the effect of DOS is analyzed in chapter 6.

Fig. 1.2. Density of states within the band gap of nc-Si:H [18]

### **1.3.2** Threshold Voltage $(V_T)$ :

In nc-Si:H TFTs, there is a difference between threshold voltage and the ON voltage. Basically, the threshold voltage is defined as the gate voltage at which the inversion channel begin to appear within the grain and the ON voltage is defined as the knee of the characteristics. Accurate estimation of threshold voltage plays a crucial role for the TFT design as it decides the onset of conduction channel. In this thesis, the model for threshold voltage including the effects of various physical parameters is presented.

### **1.3.3** Effective Mobility ( $\mu_{eff}$ ):

Carrier mobility in a TFT channel is an important parameter that determines the performance of the device. Carrier mobility measures how fast the charge carriers respond to an external electric field. In TFT, various scattering mechanism affect the carrier mobility, such as surface roughness scattering, lattice scattering and imperfection scattering [5]. So, in this thesis for device modeling, effective mobility term is used to incorporate these effects. Using Mathiessen's rule, the effective mobility in the TFT channel layer can be written as

$$\frac{1}{\mu_{eff}} = \sum_{i=1}^{k} \frac{1}{\mu_i} \qquad \text{where } i = 1, 2, 3 \dots, k \qquad (1.1)$$

#### **1.3.4 Drain Current** $(I_{DS})$ :

TFT uses intrinsic layer as a channel layer which causes high DOS in the band gap, therefore in order to operate TFT under inversion region, high gate voltage is required as compared to Metal-oxide-semiconductor field-effect-transistor (MOSFET), for the adequate generation of drain current. In two different regions of operation, the drain current is given by:

$$I_{DS}(linear) = \mu_{eff} C_i \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{V_{DS}^2}{2} \right]$$

(1.2)

$$I_{DS}(saturation) = \mu_{eff} C_i \frac{W}{2L} (V_{GS} - V_T)^2$$

(1.3)

where  $\mu_{eff}$  is the field effect mobility,  $C_i$  is the gate capacitance, W and L are the width and length of the TFT,  $V_{DS}$  is drain voltage,  $V_{GS}$  and  $V_T$  are gate and threshold voltage respectively.

### **1.3.5** Parasitic Resistance (R):

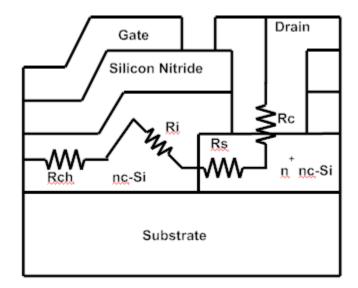

In top gated staggered nc-Si:H TFT, series resistance of active layer, series resistance of contact layers and contact resistance between metal electrode and source/drain contacts form the parasitic resistance [19] which also affects the performance of the nc-Si:H TFT [20]. These resistances are shown in Fig. 1.3. As these resistances are in series, parasitic resistance is given as:

$$\mathbf{R} = \mathbf{R}_{ch} + \mathbf{R}_{i} + \mathbf{R}_{s} + \mathbf{R}_{c} \tag{1.4}$$

Fig. 1.3. Parasitic resistance in top-gated staggered nc-Si:H TFT

### **1.3.6** Transconductance (g<sub>m</sub>):

The transconductance can be obtained from the differentiation of device transfer characteristics and is defined as

$$g_m = \frac{dI_{DS}}{dV_{GS}} \tag{1.5}$$

In this thesis, analyses of transconductance at different channel lengths are investigated using SILVACO device simulator. This analysis is presented by considering the saturation region ( $V_{DS}$ =10V) because at high drain bias, the effect of parasitic resistance is more prominent as compared to linear region (low  $V_{DS}$ ) which in turn degrades the transconductance and causes instability in the device performance.

#### **1.3.7** Threshold Voltage Shift ( $\Delta V_T$ ):

The TFTs suffers from threshold voltage shift under bias stress due to two possible instability mechanisms [21], first one is charge trapping in the gate dielectric and/or in the interface between the gate dielectric and channel and second one is defect state creation in the active layer which causes the increase in total density of defect states and therefore decreases the drain current of TFT device.

### **1.4 DEVICE SIMULATION**

In this thesis, analysis of nc-Si:H TFT is done using ATLAS from SILVACO Corporation. ATLAS simulator predicts the characteristics of the particular device under bias conditions on the basis of their physical structure. This is accomplished by approximating the device operation onto a grid of two or three dimensions. This grid comprises of various grid points known as nodes. The transport of the carriers through the device structure can be simulated by applying Maxwell differential equations onto this grid. This implies that the performance of the device can now be demonstrated in DC, AC or transient operation modes. The fundamental point of preference of physical-based device simulator is that it is much faster and less expensive than carrying out the experiment practically. It additionally gives data related to device characteristics that is hard to quantify. In ATLAS device simulator, the problem which needs to be simulated is stating by defining physical structure of the device, physical models to be used for simulation and the bias conditions under which electrical characteristics need to be simulated.

In this thesis, DOS model, which is available in TFT module in ATLAS tool package, is used to extract the density of defects present in the band gap of nc-Si:H. Further, the two dimensional nc-Si:H TFT structure is virtually fabricated and electrical characteristics are extracted using ATLAS device simulator.

### **1.5 RESEARCH MOTIVATION AND OBJECTIVES**

The nc-Si:H TFTs have bought evolution in the market of large area electronics and leading growth in the utility of new generation displays like LCDs, OLEDS over past few decades. To maintain the development and growth of large area electronics, the production of high performance nc-Si:H TFT is essential.

In past, various techniques have been used for the deposition of nc-Si:H film however each of these techniques has some limitations related to temperature, RF power and hydrogen dilution. Therefore alternative technique for the deposition of nc-Si:H film suitable for top-gated nc-Si:H TFT device needs to be analyzed.

The rapid performance improvement in flat panel displays has been achieved by scaling down the size of TFT. However the reduction in size of TFT and thus of gate dielectric causes two major problems that are leakage current and reliability [10]. The SiO<sub>2</sub> material has been used as a gate dielectric for decades due to its remarkable properties. However prevention of leakage current requires a suitable gate dielectric that must have high dielectric constant must be greater than SiO<sub>2</sub> (~3.9). Various high-k dielectric materials are being investigated for the gate insulator of nc-Si:H TFT. As each of the high-k material possess some practical challenges, therefore selection of best high-k material is necessary in order to improve nc-Si:H TFT device performance.

Many theories and models have been presented for explaining the electrical properties of TFTs based on different conduction mechanism of carriers through nanocrystalline film. But each of these models has their own conditions of validity and also has limited range of applicability. As technology evolves, further model improvement is needed to describe the effect of various physical parameters like temperature, doping density, trapping-state density and grain size on the threshold voltage and therefore on characteristic of the device.

New generation active matrix displays such as OLEDs requires TFT with high stability and therefore the drain current degradation are not acceptable. Although various researchers claimed that nc-Si:H TFTs have better stability than a-Si:H TFT yet electrical instability mechanisms for top-gate nc-Si:H TFT have not been deeply analyzed.

Thus the work presented in this thesis belongs to the nc-Si:H based TFT. This work aims to understand the electronic behavior of nc-Si:H TFTs. Thus in order to fulfill the goal of the research, the **objectives** of the work was divided into following points:

- To deposit and analyze the structural morphology of nc-Si:H film.

- To select best high-k material as a gate insulator for nc-Si:H TFT.

- To develop a physically-based analytical model for threshold voltage, effective mobility and drain current for nc-Si:H TFT.

- To analyze various physical effects on the carrier transport over wide range of channel length, temperature, doping density, trapping-state density and grain size using device modeling and simulation.

- Analysis of the threshold voltage shift and the density of states behavior under prolonged gate bias stress.

### **1.6 ORGANISATION OF THESIS**

This thesis is divided into seven chapters. The organization of this thesis is as follows:

**Chapter 1** starts with an introduction and overview of TFT with the focus on materials commonly used for its channel layer. The next section provides the brief description of various structures and the characteristics of TFT. It is followed by the motivation and objectives of this research. Last section of this chapter explains the structure of the thesis.

**Chapter 2** describes the detailed literature review of nc-Si:H based TFT. This chapter also includes the various models presented in past to explain the conduction mechanism of nc-Si:H TFT. It is followed by the review of the mechanisms which causes the electrical instability in TFT.

**Chapter 3** emphasize on the study of nc-Si:H channel material. In this chapter, the ebeam evaporation technique used for the deposition of nc-Si:H film is explained. It is followed by various characterization results which validates the formation of high quality nc-Si:H film. **Chapter 4** describes the material selection methodology for gate dielectric in nc-Si:H TFT. Various possible materials for the gate dielectric of top-gate nc-Si:H TFT and their material properties like dielectric constant, bandgap, conduction band offset and interface trap density are taken into consideration and by using Ashby's, VIKOR and TOPSIS approaches, the most appropriate material is selected.

**Chapter 5** focuses on the analytical modeling of top-gated nc-Si:H TFT. The model for threshold voltage incorporating various physical parameters like temperature, doping density, trapping-state density and grain size is presented in this chapter. This is followed by the proposed model for effective mobility and drain current.

**Chapter 6** deals with the non-idealities in nc-Si:H TFT. An analytical model for threshold voltage shift is described in next section. It is followed by the transconductance degradation analysis performed using ATLAS two-dimensional device simulator. The analysis is presented in the next section that realizes the effect of channel length and channel material quality on transconductance and thereby on device performance.

**Chapter 7** finally concludes the results and contributions of this research and provides suggestions for future work related to the nc-Si:H TFTs.

## **CHAPTER-2**

### THIN FILM TRANSISTOR: LITERATURE REVIEW

### 2.1. INTRODUCTION

The performance of TFT depends upon the various process parameters used during the fabrication of TFT and also on the conduction and instability mechanisms that occurs under electrical stress. So it is important to look into all these aspects.

When the nc-Si:H film is deposited over the amorphous substrate like glass then its crystallinity is not very high in the initial growth phases because the nc-Si:H is usually grown up in the form of cone-shape that is from bottom to top. The grain size and therefore the crystallinity increases with the increase in nc-Si:H film thickness [22]. This structural difference in top and bottom layers of nc-Si:H film plays crucial role in nc-Si:H TFT designing. In case of bottom-gate structure, the device performance depends on the bottom layer of nc-Si:H film where the channel is formed as compared to top-gate TFT, where the channel is located in highly crystalline part at the top of nc-Si:H film [23]. Owing to this, the top-gate nc-Si:H TFT provides high mobility and also the better performance as compared to bottom-gate TFT.

For this reason, top-gate structure of nc-Si:H TFT is considered in this work. The first section of this chapter explains the important outcomes and the research carried till date in the area of nc-Si:H top-gate TFT. In the second section, models for conduction in nc-Si:H TFT, given by various researchers are reviewed. In third section, the mechanisms which cause the electrical instability in TFT are explained in detail.

### 2.2. FABRICATION OF nc-Si:H BASED TFTs

The key findings of published research in the area of top-gate nc-Si:H TFT are as follows:

R.B.Min et.al. [24] discussed that the nc-Si:H film in ideal condition grow quickly, provide highest mobility in minimum thickness and provide lowest conductivity under electrical stress. The lowest conductivity at room temperature in nc-Si:H film is achieved as low as conductivity of crystalline silicon which is around 10<sup>-7</sup>S/cm. They proposed that as the film thickness increases from 50 to 350nm, the magnitude of film conductivity increased by the order of five. This is due to the increase in magnitude of electron field effect mobility by order of two and also increase in carrier density. The increase of electron mobility with the increase in film thickness is the key point behind the use of top-gate structure of nc-Si:H TFT to avail benefit of carrier mobility which is premier at the top level of the nc- Si film. However authors didn't present any information regarding hole mobility. Authors also discussed that in case of TFT, the leakage current is basically the conduction current which is related to channel layer under flat band situation. Therefore it is necessary to reduce the electron carrier density present in channel in neutral condition. In TFT, the leakage current must be lowest for its possible application as switch, to provide voltage stability or in CMOS circuits to provide minimal power consumption. They have used PECVD technique for the fabrication of top-gate coplanar TFT and proposed that the compensation doping, gettering of water and oxygen content from mixture of base gases, or addition of chlorine content during film deposition can help in reducing the electron carrier density.

I.C. Cheng et. al. [25] presented top-gate staggered nc-Si:H TFT deposited using PECVD at low temperature of about 150°C. They proposed that the quality of the nc-Si:H material can be measured by the mobility of carriers present in the nc-Si:H channel in saturation condition as it directly reveals the capability of nc-Si:H material because saturation current is not influenced by the trapping and detrapping of charge carriers in gate dielectric. In addition to this, there is insufficient activity of doped layer under saturation condition and therefore saturation mobility reflects the lower limit of nc-Si:H channel capability.

In later research [26] they proposed that the structural formation of nc-Si:H film is based on various parameters like hydrogen dilution, temperature during deposition, nc-Si:H film thickness and type of the substrate. They used both glass and plastic (Kapton E polymide) substrates for their study and fabricated both p-type and n-type staggered topgate TFT devices on a single substrate using PECVD. They have achieved sufficient mobilities for realizing CMOS circuit on plastic but fail to achieve low off current and less threshold voltage shift due to poor quality of dielectric and the interface between gate dielectric and channel. They reported that for the better performance of the device, the substrate must have low thermal expansion coefficient, high thermal stability, low surface roughness, high chemical stability and transition temperature of glass, low permeability by oxygen and water and low shrinkage capability to avoid misalignment during photolithography.

C.H.Lee et. al. [27] proposed ambipolar transistor which worked alternatively as p-type and n type transistor by the application of negative and positive gate voltages respectively. The fabrication of ambipolar transistor is not reported earlier as it is difficult to realize high quality contact between metal and semiconductor and also to deposit high quality nc-Si:H film. They have used nc-Si:H/Cr stack as source-drain contacts in place of n+ nc-Si:H for the fabrication of top-gate TFT. They proposed that hydrogen atoms cleans the surface of Cr electrodes, during the initial phase of nc-Si:H film formation and this leads to highly crystalline nc-Si:H film and therefore Cr silicidation provides lower electron as well as hole injection barrier. They reported that at higher gate voltages, leakage current increases exponentially for both p- and n-type TFTs, which validates ambipolar operation. This behavior is due to accumulation of holes and electrons in nchannel and p-channel under reverse gate voltages through injection from Cr drain, this discriminates TFT with Cr silicide contacts from TFT with n<sup>+</sup> nc-Si:H contacts.

C.H.Lee et. al. [11] presented the low temperature (i.e. 260°C) fabrication of top-gate nc-Si:H TFT through 13.56 MHz PECVD by the use of silane diluted with hydrogen. They propose that the hydrogen dilution of silane controls the crystallinity of nc-Si:H layer [28] however, this increase the level of oxygen impurity in nc-Si:H film and at the grain boundaries. The high concentration of hydrogen atoms in the silane plasma is the main requirement for the deposition of low temperature highly crystalline nc-Si:H film. They reported that low dark conductivity can be achieved by providing hydrogen chemical cleaning during the deposition of nc-Si:H film.

In later research C.H. Lee et. al. [29] proposed that the field effect mobility ( $\mu_{FE}$ ) is the ratio of free charge carriers in extended energy states,  $n_{band}$ , to the total number of induced charge carriers (which comprises of trapped carriers,  $n_{trap}$  and free carriers) times the band mobility  $\mu_{band}$ , and is expressed as:-

$$\mu_{FE} = \left[\frac{n_{band}}{n_{band} + n_{trap}}\right] \mu_{band}$$

(2.1)

The grains of nc-Si:H are enclosed by amorphous grain boundaries. Low temperature process provides low oxygen content in nc-Si:H film and thereby reduces probability of defect state creation at grain boundaries. This avoids band bending and thereby offers high mobility. This validates that low temperature is necessary for the deposition of highly crystalline nc-Si:H film.

J. H. Park et. al. [22] presented the fabrication of top-gate nc-Si:H TFT using inductively coupled plasma (ICP) CVD with different channel thicknesses at the temperature of 180 °C. They proposed that ICP-CVD reduces the surface damage usually caused by ion bombardment by generating the remote plasma without causing the bombardment of ions. This reduction in surface damage provides highly crystalline growth of nc-Si:H film and avoids amorphization in Si deposition surface. They proposed that grain size increases with increase in film thickness because of the growth of nc-Si:H layer in form of cone shape i.e. from bottom to top. In addition to this, the surface roughness also increases with increase in nc-Si:H thickness. The formation of isolated grains of nc-Si:H occurs during the initial phase but these grains competed with the nearby grains which results into the formation of grain boundaries due to collisions between the grains. These grain boundaries cause the increase in surface roughness. They reported that the new in-situ process that is used for nc-Si:H TFT fabrication provides reduction in off-current without sacrificing on-current. This is due to the suppression in conduction of off-current through trap-states.

C.H.Lee et. al. [30] proposed that the top-gate nc-Si:H TFT provides better stability and high on/off ratio as compared to bottom-gate nc-Si:H TFT. The high stability of top-gate nc-Si:H TFT makes it highly suitable device for display application like pixel driver in OLED to maintain low line voltages. They have used silicon nitride as the gate dielectric for the fabrication of both top-gate and bottom-gate n-channel nc-Si:H TFT because silicon nitride provides high reliability, high breakdown field and also allow processing at low temperature.

D.W.Kang et al. [31] also presented the effect of film thickness on the nc-Si:H TFT performance. They proposed that as thickness of nc-Si:H film increases, the field effect mobility also increases due to increase in grain size. However this causes the increase in leakage current. According to them, this increase in leakage current is due to the reduction in total resistance present in TFT.

The increase in grain size causes the reduction in resistivity which in turn reduces the channel resistance and also the total resistance of nc-Si:H TFT. They proposed that sheet resistance and contact resistance of drain/source can be reduced by the activation of dopants using excimer laser annealing.

H.J.Lee et al. [32] reported the mechanisms that are responsible for gate leakage current. They proposed that at high gate and low drain bias, thermal emission of charge carriers that are trapped in grain boundary regions is responsible for leakage current whereas Poole-Frenkel emission mechanism in drain depletion state is responsible at high gate bias and high drain bias. Under low gate bias, ohmic conduction via bulk channel layer is responsible mechanism for leakage current. They presented that high leakage current causes loss of signal in pixels and also increases the power consumption of the driving circuitry. They proposed that reduction in leakage current can be attained either by using offset-gated configuration or by employing lightly doped drain regions.

I.C.Cheng et. al. [33] reported the effect of contact resistance on the performance of staggered top-gate nc-Si:H TFT and for this study they have fabricated both n+ and p+ nc-Si:H TFT at various channel lengths. The total resistance of nc-Si:H TFT comprises of channel resistance  $R_{CH}$  and the contact resistance  $R_o$ . They reported that  $R_o \times W$  decreases with increase in gate overdrive voltages. They also proposed that if the channel

length of n-type TFT is below 10 $\mu$ m and of p-type TFT is below 25 $\mu$ m, then the drain current at V<sub>DS</sub>=10V is restricted by the contact resistance.

Y.Djeridane et.a al. [34] proposed that during the growth of nc-Si:H film over the amorphous like substrate, a residual amorphous phase called as incubation layer is formed at the interface between substrate and the film. This incubation layer can be avoided by controlling the deposition plasma parameters. They also reported that silicon nitride provides better stability when used as gate dielectric for the fabrication of n-type nc-Si:H TFT. However, for fabrication of p-type TFT they have used SiO<sub>2</sub> as a gate dielectric due to its wide bandgap, large conduction and valence band off-set.

A. Subramaniam et. al. [35] reported that ambipolar operation can be achieved by reducing the oxygen concentration in the nc-Si:H channel. The ambipolar transistor allows the production of complementary inverter using single type device. They fabricated both n-type and p-type top gate staggered nc-Si:H TFT at submicron dimensions with no short channel effects.

Table 2.1 summarized nc-Si:H top-gate TFT device dimensions and performance parameters of the published experimental works. So based on the literature review, it is clear that n-channel nc-Si:H TFT provides higher mobility compared to p-channel TFT and staggered top-gate structure of TFT provides better stability and high on-off current ratio. So in this thesis, staggered top-gate n-channel nc-Si:H TFT is considered and investigated for its electrical behavior.

| Reference                         | Esmaeili et. al.<br>[23]                                   | Cheng et. al.<br>[25]                                             | Min et. al.<br>[24]        | Lee et. al.<br>[27]                   |

|-----------------------------------|------------------------------------------------------------|-------------------------------------------------------------------|----------------------------|---------------------------------------|

| Gate contact                      | Al<br>300nm                                                | Al<br>200nm                                                       | Al<br>200nm                | Al<br>300nm                           |

| Source/ Drain<br>Contact layer    | -                                                          | Cr<br>50nm                                                        | Cr<br>50nm                 | Cr<br>50nm                            |

| Doped layer                       | n+ nc-Si<br>80nm                                           | n+ nc-Si<br>60nm                                                  | n+ nc-Si:H<br>60nm         | n+ a-Si :H<br>50nm                    |

| Process<br>nc-Si                  | PECVD<br>50nm                                              | VHF PECVD<br>50nm                                                 | VHFPECVD<br>300nm          | PECVD<br>100nm                        |

| Dielectric                        | SiO <sub>2</sub><br>270nm                                  | SiO <sub>2</sub><br>300nm                                         | SiO <sub>2</sub><br>370 nm | a- SiO <sub>x</sub>                   |