## Design of Energy Efficient and Deterministic Memory Subsystem for Uniprocessor and Multicore Systems

## THESIS

Submitted in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

by PATIL GEETA NAYAKAPPA

Under the Supervision of Dr. BIJU K. RAVEENDRAN

and Co-supervision of **Dr. LUCY J. GUDINO**

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

2018

# Declaration

I, Geeta Patil, hereby declare that the work presented here in the thesis titled, 'Design of Energy Efficient and Deterministic Memory Subsystem for Uniprocessor and Multicore Systems ' is a bonafide research work done by me and it has not been submitted previously in part or in full to this University or any other University or Institution for award of any degree. Any literature work cited within this thesis has given due acknowledgement and is listed in bibliography.

Signature of the student

to

Name of the student

Date

: PATIL GEETA NAYAKAPPA

ID number of the student

: 2011PHXF0409G

08/12/2018

## BIRLA INSTITUTE OF TECHNOLOGY AND SCIENCE, PILANI

# Certificate

This is to certify that the thesis entitled 'Design of Energy Efficient and Deterministic Memory Subsystem for Uniprocessor and Multicore Systems' and submitted by PATIL GEETA NAYAKAPPA, ID.No. 2011PHXF0409G for award of Ph.D. of the Institute embodies original work done by her under our supervision.

:

Signature of the Supervisor Name in capital letters Designation Date 135 1 3/12/2018

: Dr. BIJU K. RAVEENDRAN : ASSISTANT PROFESSOR

Signature of the Co-supervisor : Name in capital letters Designation : Date :

Lug

: Dr. LUCY J. GUDINO : ASSISTANT PROFESSOR : 3/12/2018

Dedicated to God, My wonderful huge family Es My best Supervisors.

### Acknowledgement

I would like to acknowledge my sincere thanks to each and everyone who have made this thesis an unforgettable experience and who have influenced this work in some way or the other. Let me begin by thanking the Almighty God for the innumerable blessings he has showered upon me.

Next, I would like to express my deepest gratitude to my supervisor, Dr. Biju K. Raveendran, for giving me an opportunity to work under his guidance. His patience, especially during the initial stages of my PhD, his vast knowledge, excellent supervision, prompt attention, dedicated help, advice, inspiration, encouragement and continuous support have made a deep impression on me. I have been extremely lucky to have Dr. Lucy J. Gudino as my co-supervisor. I have learnt the basics of computer architecture from her motivational classes. She has provided her valuable guidance and consistent support throughout my research work. Her suggestions in completing my thesis are highly appreciated. I would like to thank the members of Doctoral Advisory Committee, Prof. Bharat Deshpande and Prof. Neena Goveas, for their valuable time, guidance, critical suggestions and comments for overall improvement of research work. I am grateful to Prof. Souvik Bhattacharyva, Vice-Chancellor, BITS Pilani, Prof. G. Raghurama, Director, BITS-Pilani, K. K. Birla Goa Campus, Late. Prof. S. K. Agarwal, former Director, BITS-Pilani, K. K. Birla Goa Campus, Prof. S. K. Verma, Dean, Academic Research Division, BITS-Pilani, Prof. P. K. Das, former Associate Dean, Academic Research Division, BITS-Pilani K. K. Birla Goa Campus, Prof. Bharat Deshpande, Associate Dean, Academic Research Division, BITS-Pilani K. K. Birla Goa Campus and the members of Doctoral Research Committee of Department of CS&IS, BITS-Pilani, K. K. Birla Goa Campus for providing administrative support, a conducive atmosphere and adequate facilities to carry out my research efficiently.

I am thankful to any time help of Dr. Ramprasad Joshi, and his initiation in introducing Latex software. A special mention of thanks to my friends in BITS-Goa Aruna Govada, Shubhangi Gawali, Sreejith V, Rajendra Kumar Roul, Mahadev Gawas, Ashu Sharma, Shamanth N. and many more for their timely help, constant support and cooperation.

I acknowledge my students Vijay, Neethu, Manali, Divya, Alen, Kajal, Samriti and Ayushi who made this journey so wonderful and who were ever willing to assist me. On this occasion I cannot forget my past teachers whose teaching at different stages of education has made it possible for me to reach a stage where I could write this thesis.

I owe my deepest gratitude towards my loving husband, Amol, for his eternal support and aspirations. His love and support has always been my strength. His patience and sacrifice will remain my inspiration throughout my life. Without his help, I would not have been able to complete much of what I have done and become who I am. I thank my son Pranil and daughters Sara, Meenali and Manushri for their understanding and support throughout this work. I am thankful to my mother Sukanti, father Nayakappa, mother in law Jayashree, father in law Jayawant, brother Amol, brother in law Sachin, co-sisters Siya, Sangeeta, and my entire family for believing in me and giving me space to explore the world.

Geeta

# Abstract

Energy efficiency is one of the major design considerations of the modern day processor design. Memory subsystem consumes major portion of the on-chip energy. This motivates the designers to come up with cache memory subsystem design with least possible energy consumption without much performance degradation. System performance can be improved by increasing operating frequency of the system. However, increase in operating frequency leads to increase in energy consumption which in turn leads to increase in heat dissipation and leakage current. One of the possible solutions to this problem is to go for multicore systems with reduced frequency. Maintaining data consistency becomes a major challenge in multicore systems. Energy efficient and performance centric protocols are required to maintain data consistently in these system.

In hard real-time embedded systems, along with energy efficiency, deterministic tighter upper bound on the worst case execution time of the task is also a requirement. Deterministic tighter upper bound on worst case execution time can only be ensured by making the entire process of accessing memory system deterministic. The memory access model can be made deterministic by providing a hard upper bound on the number of misses in TLB, L1 Cache, L2 cache and main memory. This thesis addresses static energy consumption and dynamic energy consumption of unicore and multicore system. The thesis also addresses mechanisms to provide tighter upper bound on worst case execution time on memory sub-system performance in order to achieve deterministic memory performance.

To reduce energy consumption and response time of set associative caches, the thesis proposes a novel cache architecture - Way Halted Prediction. This is achieved with the help of halt tag array and prediction circuit. Experimental evaluation of various SPLASH benchmark programs on SESC simulator reveal that way halted prediction architecture offers better energy efficiency over the other architectures analyzed. Way halted prediction offers 46.64%, 6.45% and 4.15% dynamic energy saving and 1.04%, 2.92% and -0.05% saving in response time over the CC, WP and WH respectively.

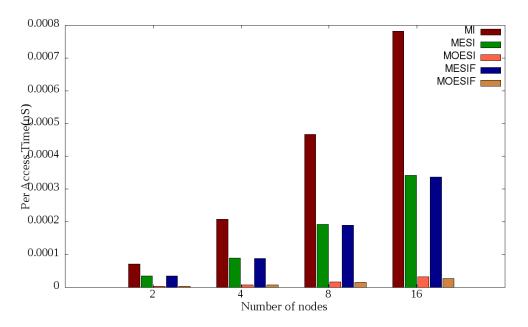

To reduce energy consumption and response time of multicore systems, the thesis proposes a novel cache coherence protocol **M**odified **O**wned **E**xclusive **S**hared **I**nvalid **F**orward - MOESIF - to improve the off chip and on chip bandwidth usage for multicore systems. This is achieved by reducing the number of write backs to next level memory and by reducing the number of responders to a cache miss when multiple copies of data exists in private caches. Reduction in the number of write backs and the number of responders results in reducing time, energy and bandwidth usage. Experimental evaluation of various SPLASH benchmark programs on SESC simulators reveal that the MOESIF protocol outperforms all other hardware based coherence protocols in terms of energy consumption and response time. The energy savings of MOESIF protocol over MESI, MOESI and MESIF protocol is 88.58%, 4.33% and 88.52% respectively. The per response time saving of MOESIF protocol over MESI, MOESI and MESIF protocol is 91.37%, 6.17% and 91.32% respectively.

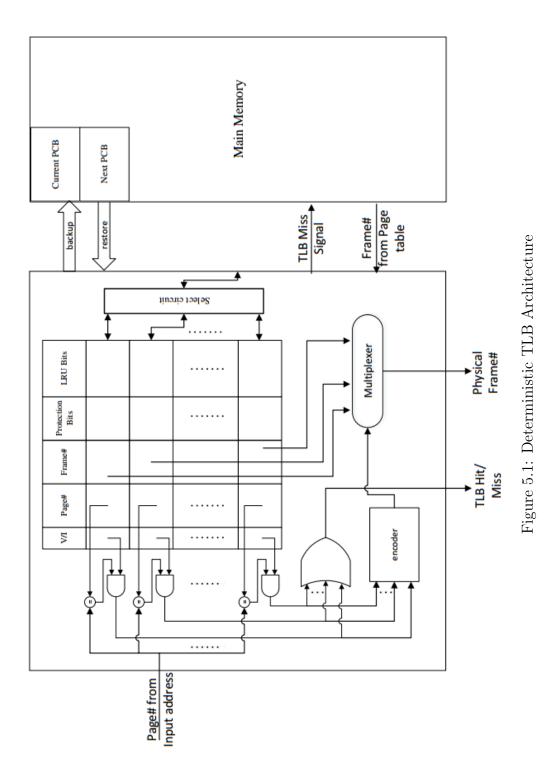

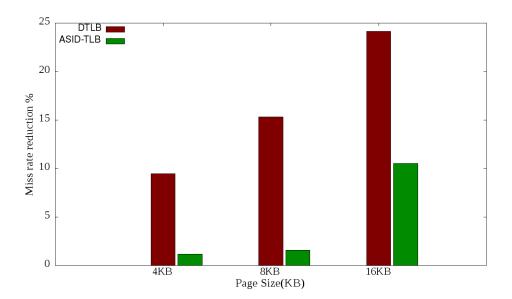

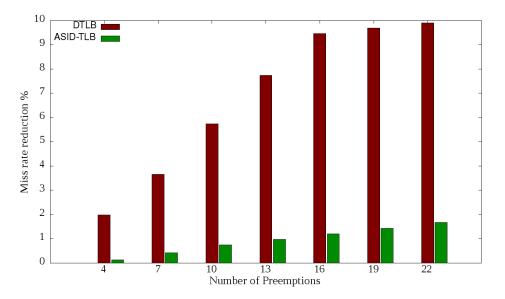

The thesis proposes a novel TLB architecture - Deterministic Translation Lookaside Buffer (DTLB)- to offer tighter upper bound on the worst case execution time . DTLB offers deterministic performance for low priority real-time tasks. DTLB achieves a tighter upper bound on the worst case execution time of real-time tasks by maintaining a copy of the current TLB in PCB of the task before preemption and transferring the contents back to TLB while resumption of the task. DTLB reduces TLB response time, dynamic energy consumption and effective per response time by increasing TLB hit rate. TLB hit rate is increased by 9.46% as compared to conventional TLB for 4KB page size, with 16 preemptions and 32 TLB entries. DTLB offers on an average 6.74% of dynamic energy savings over conventional TLB. Effective per response time of DTLB reduced by 2.97% as compared to conventional TLB.

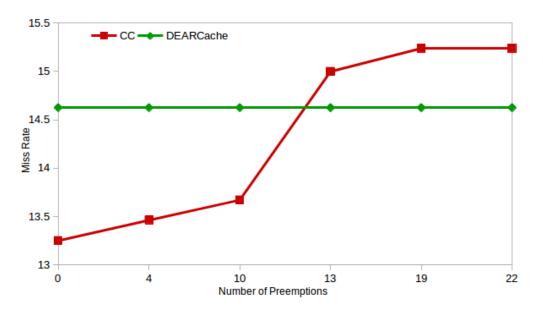

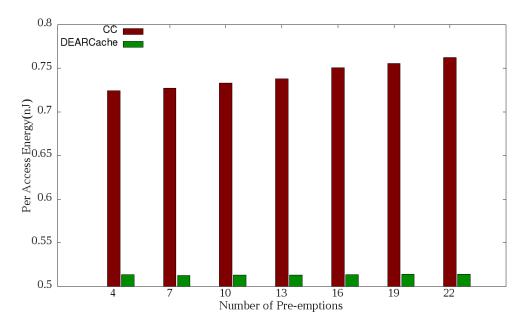

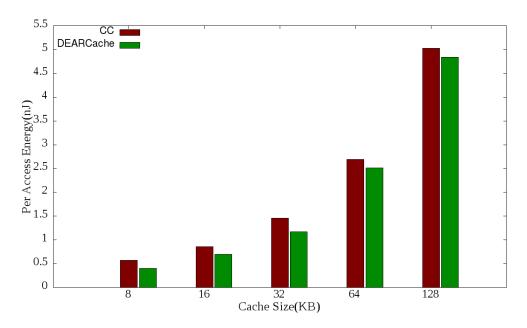

To have a tighter upper bound on the worst case execution time of real time task, the thesis presents a Deterministic Energy efficient process Aware Realtime Cache (DEARCACHE). DEARCACHE ensures deterministic tighter upper bound by eliminating cache related intertask interference. It allocates at least statically identified minimum ways to each job. It obtains tighter upper bound on number of cache misses. DEARCACHE reduces dynamic energy consumption by 38.10% for 4-way set associative cache configuration over CC with 4.39% overhead of static energy. Per response time of DEARCACHE is improved 3.87 times over NO CACHE model and with an additional requirement of 4.37% of per response time as compared to CC.

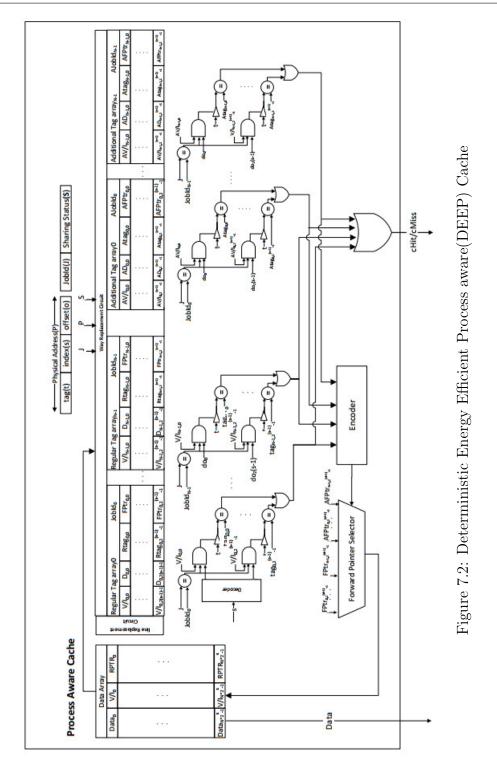

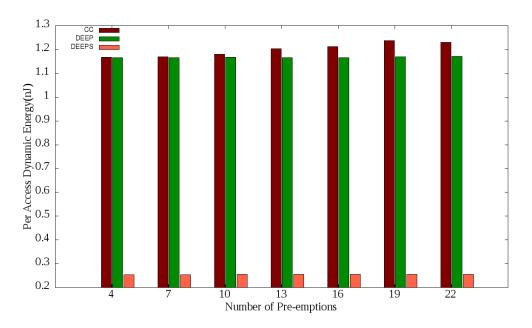

To get deterministic performance of L2 cache, this thesis proposes a Deterministic Energy Efficient Process aware(DEEP) design. DEEP cache is shared among all tasks running on different cores of the processor. It allocates minimum number of ways to each task which is identified as a result of static analysis. The performance of DEEP cache can be improved by using a shared way - DEEPS. On an average per response time, per access dynamic energy and per access static energy of DEEP is higher than conventional cache by 10.48%, 2.13%, 15.78% respectively. The per response time, per access dynamic energy and per access static energy of CC is higher than DEEPS by 38.50%, 71.69% and 50.01% respectively. The thesis proposes an integrated design of deterministic memory named as Deterministic REAl-time Memory system (DREAM). DREAM achieves deterministic performance at TLB and L1 cache by incorporating DTLB and DEARCACHE with DEEP as L2 cache. The per response time, per access dynamic energy and per access static energy of conventional cache is higher than DREAM by 27.85%, 71.40% and 46.75% respectively.

# Contents

| Li       | st of | Figures                                                            | xvi  |

|----------|-------|--------------------------------------------------------------------|------|

| Li       | st of | Tables x                                                           | xiii |

| Li       | st of | Abbreviations x                                                    | xiv  |

| 1        | Intr  | oduction                                                           | 1    |

|          | 1.1   | Background                                                         | 1    |

|          | 1.2   | Motivation                                                         | 4    |

|          | 1.3   | Problem Statement                                                  | 8    |

|          | 1.4   | Research Goals                                                     | 10   |

|          | 1.5   | Contributions                                                      | 10   |

|          | 1.6   | Publications                                                       | 12   |

|          | 1.7   | Thesis Outline                                                     | 13   |

| <b>2</b> | Lite  | erature Survey                                                     | 15   |

|          | 2.1   | Introduction                                                       | 15   |

|          | 2.2   | Uniprocessor / Unicore energy optimisations $\ldots \ldots \ldots$ | 15   |

|          | 2.3   | Cache Coherency Protocols                                          | 22   |

|          | 2.4   | Deterministic Memory                                               | 27   |

|          |       | 2.4.1 Deterministic TLB                                            | 27   |

|          |       | 2.4.2 Deterministic Cache                                          | 30   |

| 3        | WH    | IP:Way Halted Prediction Cache                                     | 33   |

| 3.1 | Introd                                                                      | luction                                                                                                                                                                                                                                                                                                                      | 33                                  |

|-----|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 3.2 | WHP                                                                         | cache architecture                                                                                                                                                                                                                                                                                                           | 34                                  |

| 3.3 | Energ                                                                       | y Model                                                                                                                                                                                                                                                                                                                      | 40                                  |

|     | 3.3.1                                                                       | Conventional Cache                                                                                                                                                                                                                                                                                                           | 40                                  |

|     | 3.3.2                                                                       | Way Predicting Cache                                                                                                                                                                                                                                                                                                         | 43                                  |

|     | 3.3.3                                                                       | Way Halting Cache                                                                                                                                                                                                                                                                                                            | 45                                  |

|     | 3.3.4                                                                       | Way Halted Prediction Cache                                                                                                                                                                                                                                                                                                  | 47                                  |

| 3.4 | Time                                                                        | Model                                                                                                                                                                                                                                                                                                                        | 52                                  |

|     | 3.4.1                                                                       | Conventional Cache                                                                                                                                                                                                                                                                                                           | 53                                  |

|     | 3.4.2                                                                       | Way Predicting Cache                                                                                                                                                                                                                                                                                                         | 54                                  |

|     | 3.4.3                                                                       | Way Halting Cache                                                                                                                                                                                                                                                                                                            | 54                                  |

|     | 3.4.4                                                                       | Way Halted Prediction Cache                                                                                                                                                                                                                                                                                                  | 55                                  |

| 3.5 | Exper                                                                       | imental Setup                                                                                                                                                                                                                                                                                                                | 56                                  |

| 3.6 | Exper                                                                       | imental Analysis                                                                                                                                                                                                                                                                                                             | 57                                  |

|     | 3.6.1                                                                       | Prediction Hit Accuracy                                                                                                                                                                                                                                                                                                      | 58                                  |

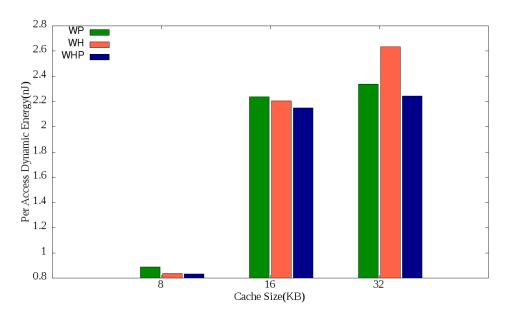

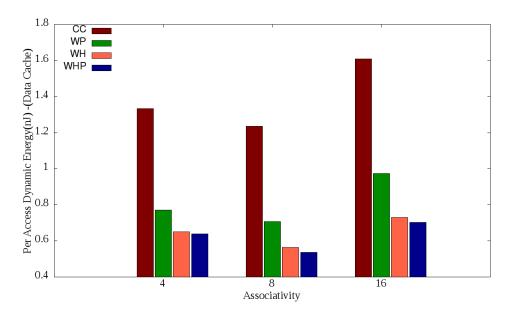

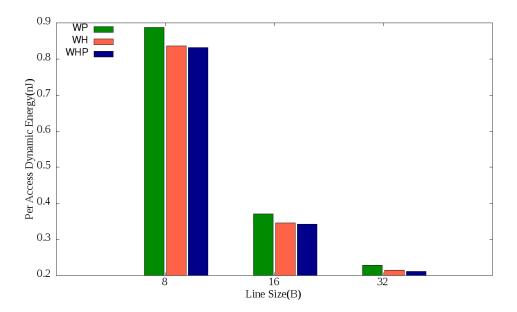

|     | 3.6.2                                                                       | Dynamic Energy per Access                                                                                                                                                                                                                                                                                                    | 58                                  |

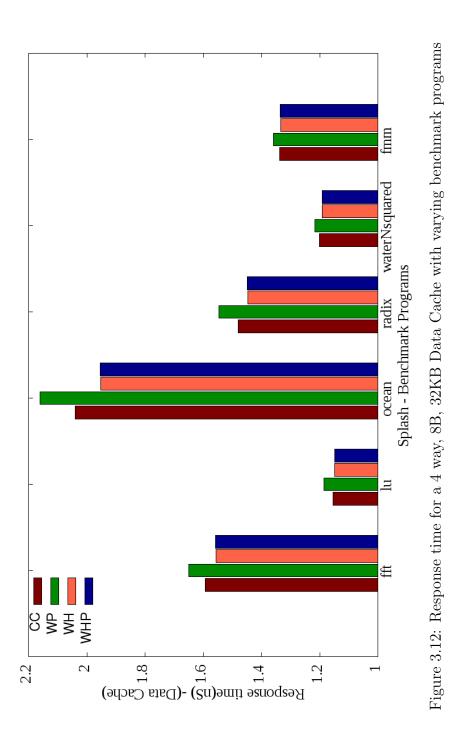

|     | 3.6.3                                                                       | Response Time                                                                                                                                                                                                                                                                                                                | 62                                  |

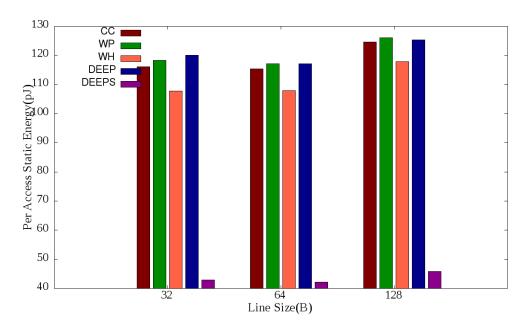

|     | 3.6.4                                                                       | Static Energy Per Access                                                                                                                                                                                                                                                                                                     | 71                                  |

|     | 3.6.5                                                                       | Time and Area Overhead                                                                                                                                                                                                                                                                                                       | 73                                  |

| 3.7 | Concl                                                                       | usion                                                                                                                                                                                                                                                                                                                        | 73                                  |

| MO  | ESIF                                                                        | : Cache Coherency Protocol                                                                                                                                                                                                                                                                                                   | <b>74</b>                           |

| 4.1 | Introd                                                                      | luction                                                                                                                                                                                                                                                                                                                      | 74                                  |

| 1.1 |                                                                             |                                                                                                                                                                                                                                                                                                                              |                                     |

| 4.2 |                                                                             | y Used Cache Coherence Protocols                                                                                                                                                                                                                                                                                             | 75                                  |

|     |                                                                             | y Used Cache Coherence Protocols                                                                                                                                                                                                                                                                                             | 75<br>76                            |

|     | Widel                                                                       | •                                                                                                                                                                                                                                                                                                                            |                                     |

|     | <ul> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> <li>3.7</li> </ul> | <ul> <li>3.3 Energ</li> <li>3.3.1</li> <li>3.3.2</li> <li>3.3.3</li> <li>3.3.4</li> <li>3.4</li> <li>3.4</li> <li>3.4.1</li> <li>3.4.2</li> <li>3.4.3</li> <li>3.4.3</li> <li>3.4.4</li> <li>3.5 Exper</li> <li>3.6</li> <li>3.6.1</li> <li>3.6.2</li> <li>3.6.3</li> <li>3.6.4</li> <li>3.6.5</li> <li>3.7 Concl</li> </ul> | <ul> <li>3.3 Energy Model</li></ul> |

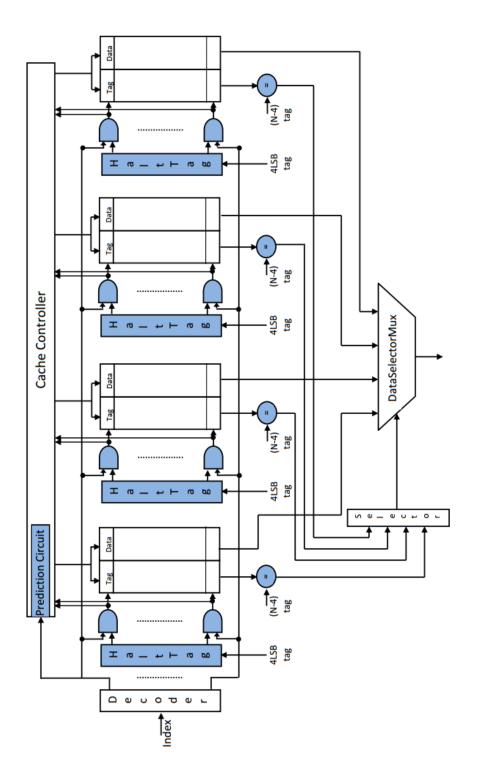

|   | 4.3 | MOESIF Architecture                                                                                                                                 |

|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 4.4 | Energy and Time Model                                                                                                                               |

|   | 4.5 | Experimental Evaluation                                                                                                                             |

|   |     | 4.5.1 Experimental Setup $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 90$                                                        |

|   |     | 4.5.2 Experimental Analysis of Protocols 90                                                                                                         |

|   |     | 4.5.3 Experimental Evaluation                                                                                                                       |

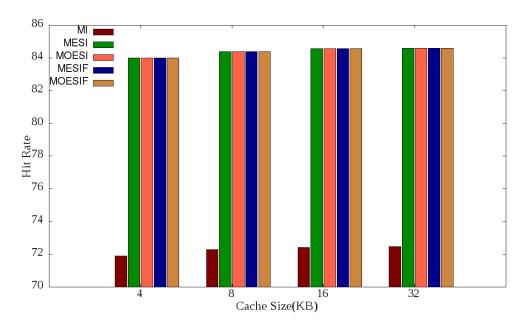

|   |     | 4.5.3.1 Hit rate and Data transfers $\ldots \ldots \ldots $ 92                                                                                      |

|   |     | $4.5.3.2  \text{Energy Consumption}  \dots  \dots  \dots  \dots  95$                                                                                |

|   |     | $4.5.3.3  \text{Response Time}  \dots  \dots  \dots  \dots  \dots  98$                                                                              |

|   | 4.6 | Conclusion                                                                                                                                          |

| - | DTT | D. Deterministic TID for Deal time Scotory 101                                                                                                      |

| 5 |     | B: Deterministic TLB for Real-time System 101                                                                                                       |

|   | 5.1 | Introduction $\ldots \ldots 101$    |

|   | 5.2 | DTLB Architecture                                                                                                                                   |

|   | 5.3 | Energy and Time Modeling                                                                                                                            |

|   |     | 5.3.1 Energy Modeling of TLB                                                                                                                        |

|   |     | 5.3.2 Time Modeling of TLB $\ldots \ldots 107$                                |

|   | 5.4 | Experimental Setup And Evaluation                                                                                                                   |

|   |     | 5.4.1 Experimental Setup                                                                                                                            |

|   |     | 5.4.2 Experimental Evaluation                                                                                                                       |

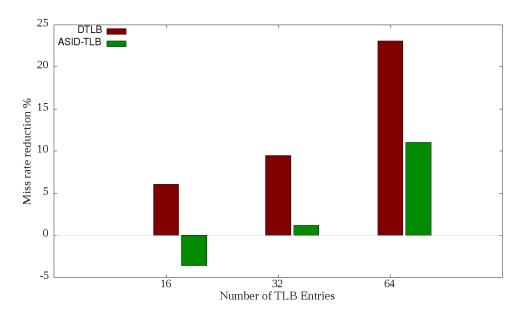

|   |     | 5.4.2.1 TLB Miss Rate $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 110$                                                   |

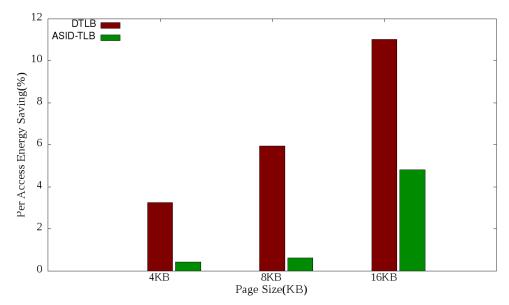

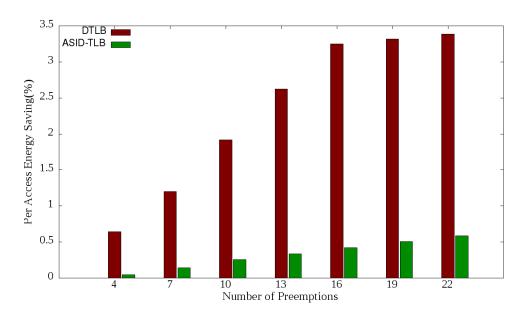

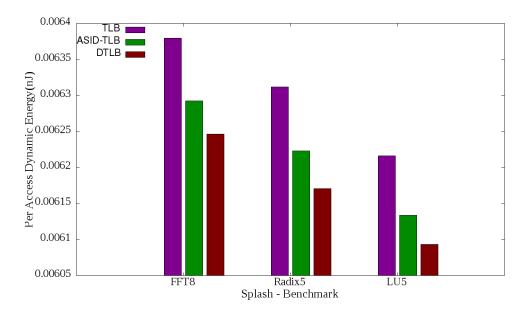

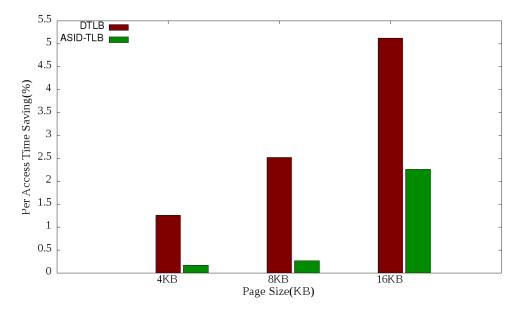

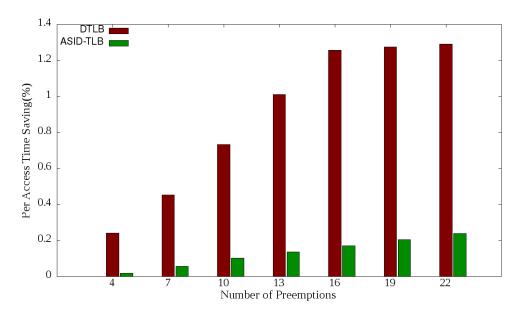

|   |     | 5.4.2.2 Dynamic Energy $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 113$                                                                |

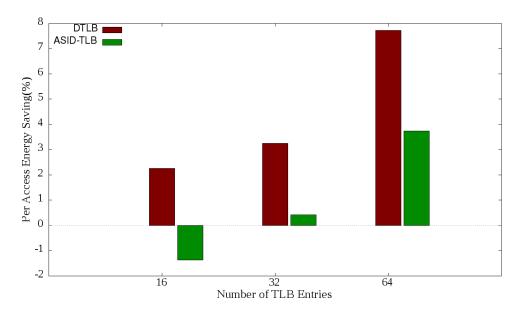

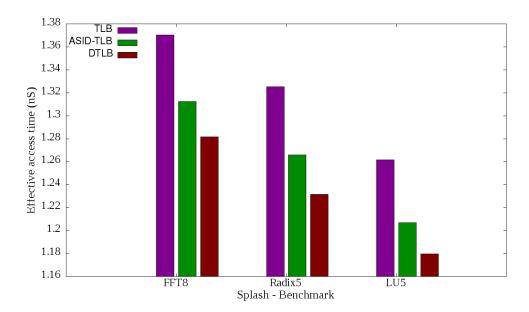

|   |     | 5.4.2.3 Access Time $\ldots \ldots 116$                                              |

|   | 5.5 | Conclusion                                                                                                                                          |

| 6 | ЛБ  | RCACHE - Deterministic Energy Efficient Process Aware                                                                                               |

| U |     |                                                                                                                                                     |

|   |     | -time Cache 121                                                                                                                                     |

|   | 6.1 | Introduction $\ldots \ldots \ldots$ |

|   | 6.2 | DEA    | RCACHE    | Architecture                                                                                                 | 22 |

|---|-----|--------|-----------|--------------------------------------------------------------------------------------------------------------|----|

|   |     | 6.2.1  | DEAR      | CACHE Energy Modeling                                                                                        | 25 |

|   |     | 6.2.2  | DEAR      | CACHE Time Modeling                                                                                          | 26 |

|   | 6.3 | Exper  | imental A | nalysis $\ldots \ldots 1$              | 27 |

|   |     | 6.3.1  | Tighter   | upper bound on WCET $\ldots \ldots \ldots \ldots \ldots \ldots 1$                                            | 27 |

|   |     | 6.3.2  | Energy j  | per Access                                                                                                   | 28 |

|   |     | 6.3.3  | Respons   | e Time $\ldots \ldots 1$ | 32 |

|   |     | 6.3.4  | Energy a  | and Time comparison with energy efficient caches 1                                                           | 34 |

|   | 6.4 | Conclu | usion     |                                                                                                              | 37 |

| 7 | DR  | EAM -  | - Detern  | inistic Memory Subsystem 13                                                                                  | 38 |

|   | 7.1 | Introd | uction .  |                                                                                                              | 38 |

|   | 7.2 | DREA   | M Archit  | ecture                                                                                                       | 39 |

|   | 7.3 | Time,  | Power an  | d Energy Modeling                                                                                            | 42 |

|   |     | 7.3.1  | Energy    | Modeling of DEEP Cache with Shared way -                                                                     |    |

|   |     |        | DEEPS     |                                                                                                              | 45 |

|   |     | 7.3.2  | Energy 1  | Modeling of DREAM system with Shared cache                                                                   |    |

|   |     |        | - DREAD   | MS                                                                                                           | 46 |

|   |     | 7.3.3  | Time M    | odeling of DEEPS $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 1$                   | 46 |

|   |     | 7.3.4  | Time M    | odeling of DREAMS $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots 1$                         | 46 |

|   | 7.4 | Perfor | mance Ev  | valuation $\ldots \ldots 1$                   | 47 |

|   |     | 7.4.1  | Experim   | ental Analysis - L2 as DEEP Cache 1                                                                          | 47 |

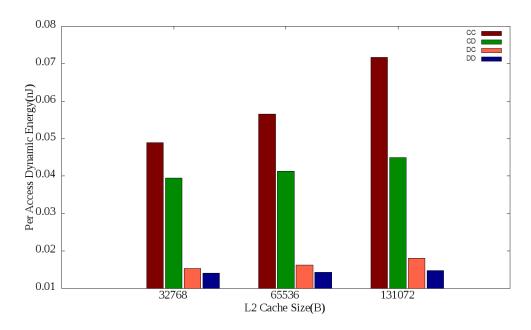

|   |     |        | 7.4.1.1   | Dynamic Energy per Access 1                                                                                  | 47 |

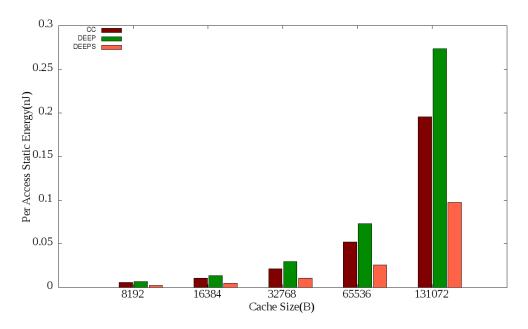

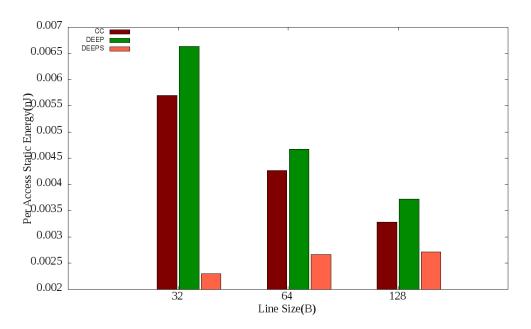

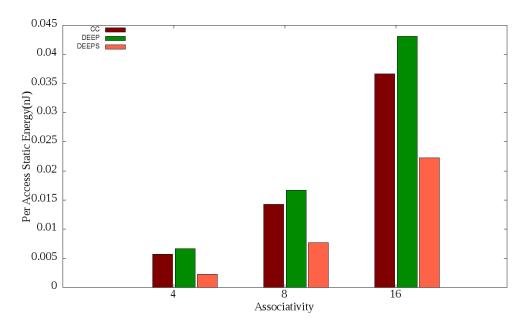

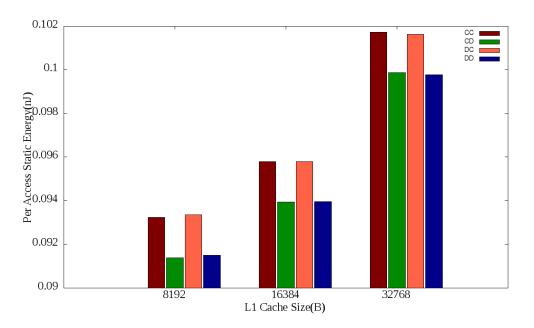

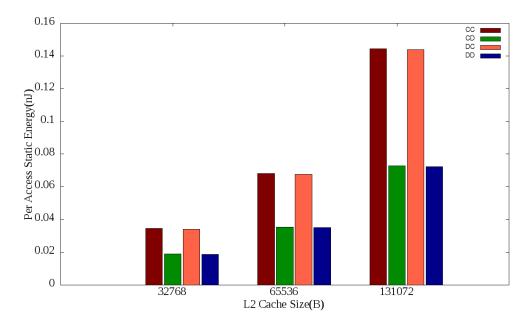

|   |     |        | 7.4.1.2   | Static Energy per Access                                                                                     | 50 |

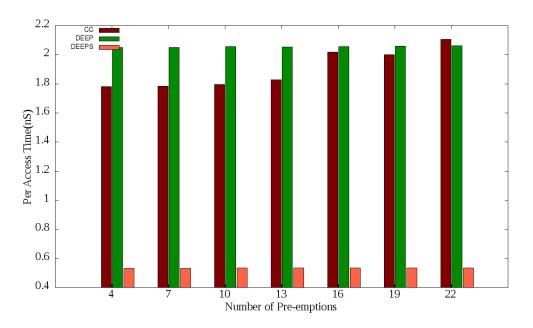

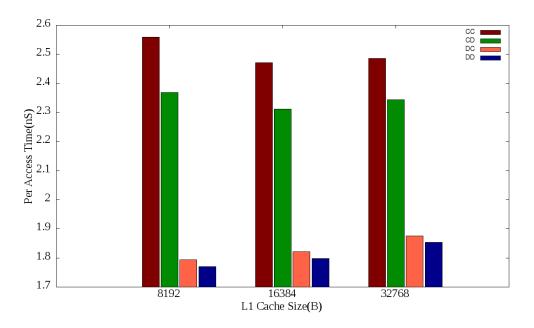

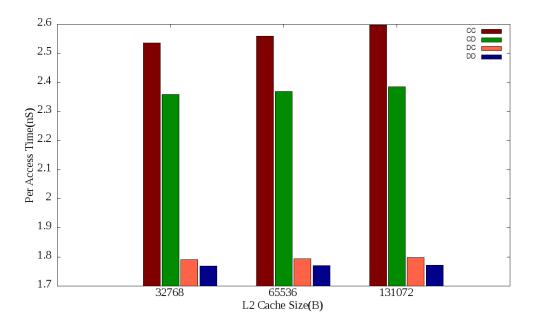

|   |     |        | 7.4.1.3   | Effective per Access Time                                                                                    | 52 |

|   |     |        | 7.4.1.4   | Energy and Time comparison with energy                                                                       |    |

|   |     |        |           | efficient caches                                                                                             | 56 |

|    |        | 7.4.2  | Experim  | ental Analysis - Complete Memory Model | 157   |

|----|--------|--------|----------|----------------------------------------|-------|

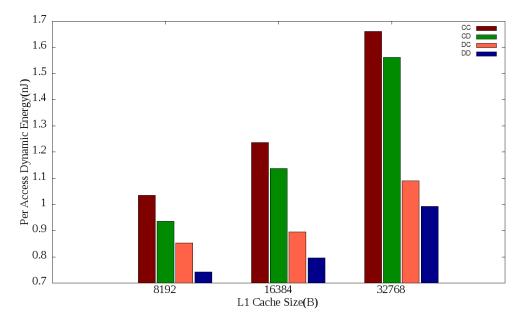

|    |        |        | 7.4.2.1  | Dynamic Energy per Access              | 157   |

|    |        |        | 7.4.2.2  | Static Energy per Access               | 158   |

|    |        |        | 7.4.2.3  | Per Access Time                        | 159   |

|    | 7.5    | Conclu | usion    |                                        | . 162 |

| 8  | Con    | clusio | n and Fu | ture Directions                        | 163   |

| Pι | ıblica | ations |          |                                        | 166   |

| Bi | ogra   | phies  |          |                                        | 167   |

| Bi | bliog  | graphy |          |                                        | 170   |

# List of Figures

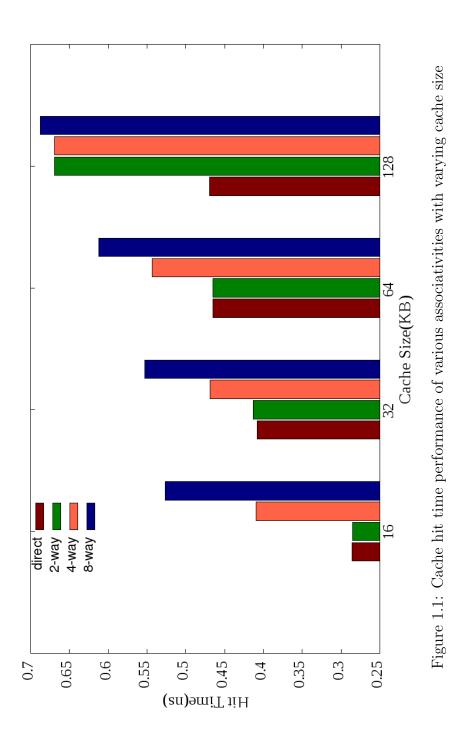

| 1.1 | Cache hit time performance of various associativities with                                                |    |

|-----|-----------------------------------------------------------------------------------------------------------|----|

|     | varying cache size $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$       | 5  |

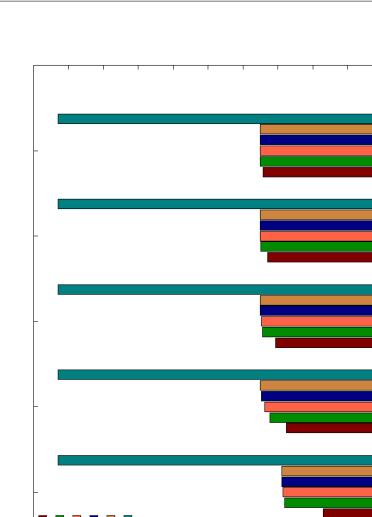

| 1.2 | Cache hit rate performance of various associativities with vary-                                          |    |

|     | ing cache size                                                                                            | 6  |

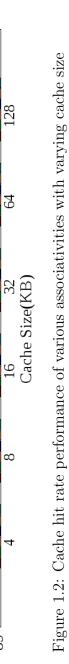

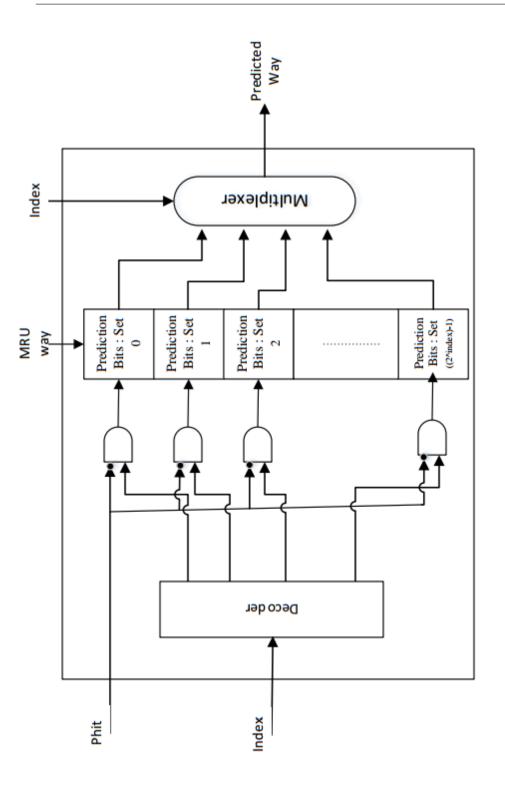

| 3.1 | Way Halted Prediction Cache Architecture                                                                  | 36 |

| 3.2 | Prediction Circuit                                                                                        | 37 |

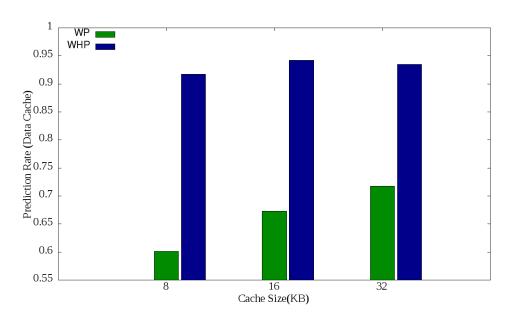

| 3.3 | Prediction Rate for a 4 way, 8B line size with varying Data                                               |    |

|     | Cache size                                                                                                | 57 |

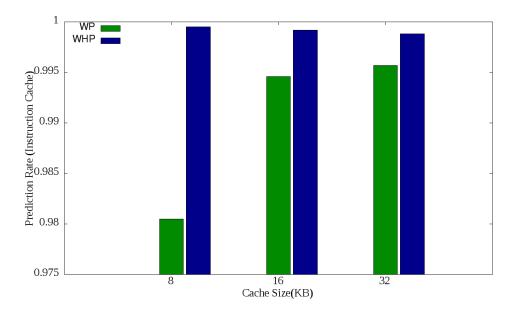

| 3.4 | Prediction Rate for a 4 way, 8B line size with varying Instruc-                                           |    |

|     | tion Cache size $\ldots$ | 58 |

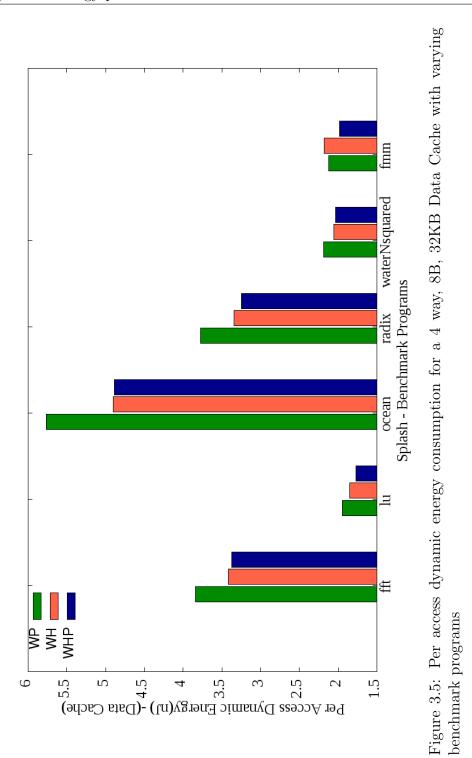

| 3.5 | Per access dynamic energy consumption for a 4 way, 8B, $32$ KB                                            |    |

|     | Data Cache with varying benchmark programs                                                                | 59 |

| 3.6 | Per access dynamic energy consumption for a 2 way, 8B, $32$ KB                                            |    |

|     | Instruction Cache with varying benchmark programs $\ldots$ .                                              | 60 |

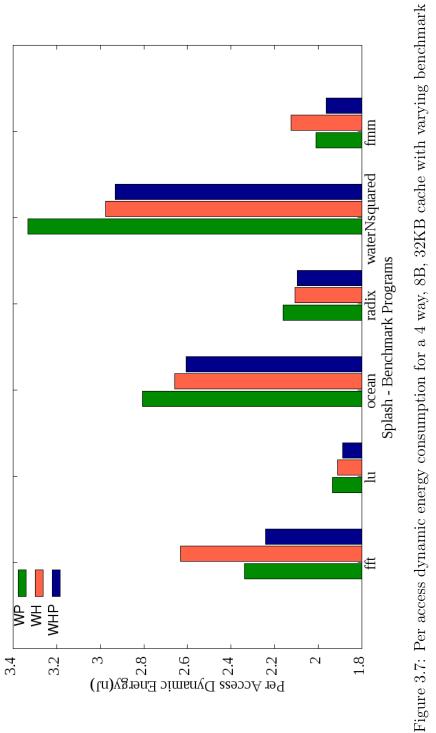

| 3.7 | Per access dynamic energy consumption for a 4 way, 8B, $32$ KB                                            |    |

|     | cache with varying benchmark programs                                                                     | 61 |

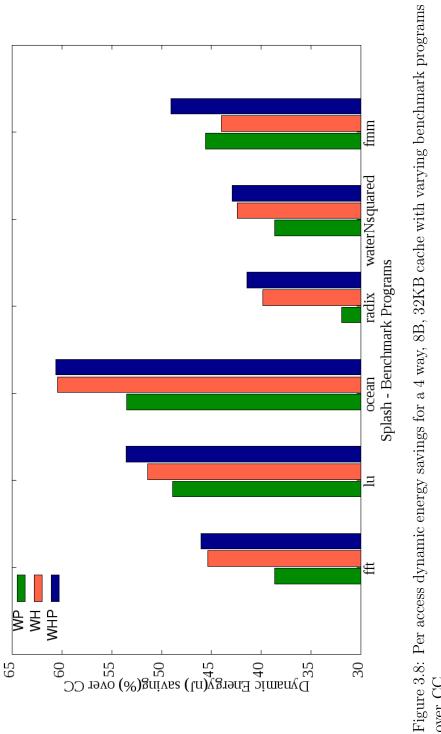

| 3.8 | Per access dynamic energy savings for a 4 way, 8B, 32KB cache                                             |    |

|     | with varying benchmark programs over CC                                                                   | 63 |

| 3.9 | Per access dynamic energy consumption for a 4 way, 8B line                                                |    |

|     | size with varying cache size                                                                              | 64 |

| 3.10 | Per access dynamic energy consumption for a 16B, 8KB Data                                               |    |

|------|---------------------------------------------------------------------------------------------------------|----|

|      | Cache with varying associativities                                                                      | 64 |

| 3.11 | Per access dynamic energy consumption for a 4 way, 8KB cache                                            |    |

|      | with varying line Size                                                                                  | 65 |

| 3.12 | Response time for a 4 way, 8B, 32KB Data Cache with varying                                             |    |

|      | benchmark programs                                                                                      | 66 |

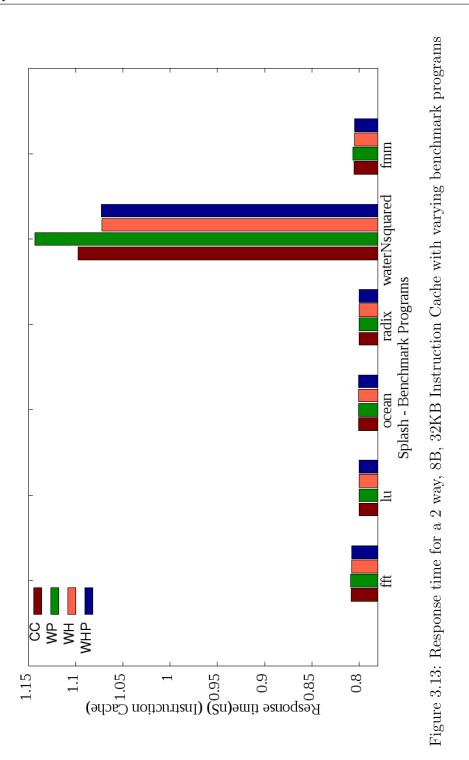

| 3.13 | Response time for a 2 way, 8B, 32KB Instruction Cache with                                              |    |

|      | varying benchmark programs                                                                              | 67 |

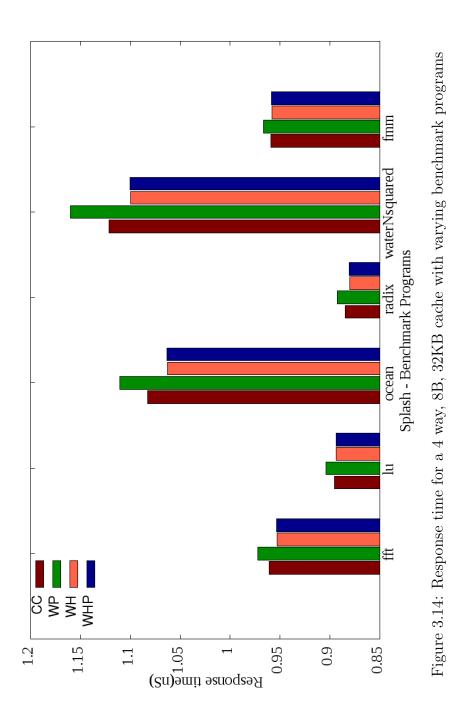

| 3.14 | Response time for a 4 way, 8B, 32KB cache with varying                                                  |    |

|      | benchmark programs                                                                                      | 68 |

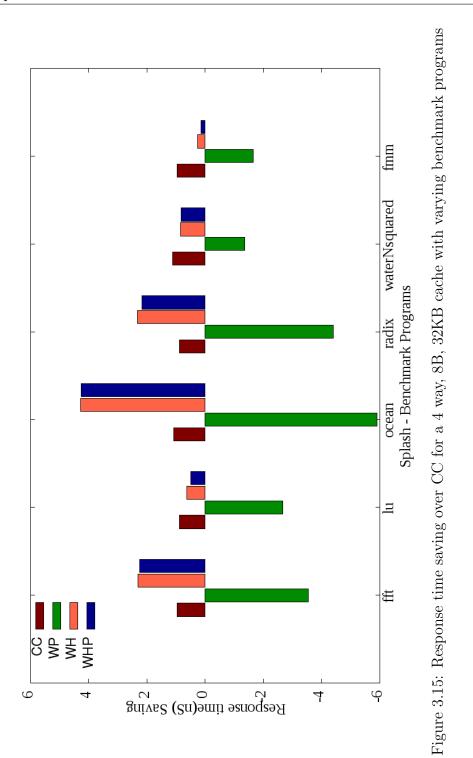

| 3.15 | Response time saving over CC for a 4 way, 8B, 32KB cache                                                |    |

|      | with varying benchmark programs                                                                         | 69 |

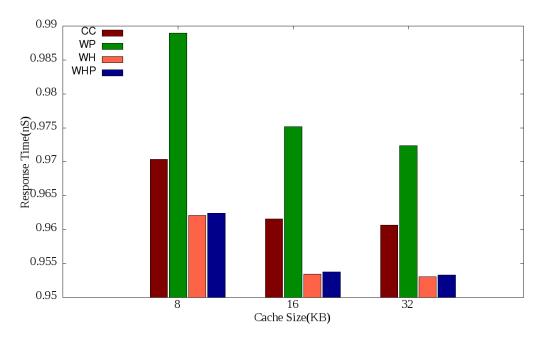

| 3.16 | Response time for a 4 way, 8B line size with varying cache size                                         | 70 |

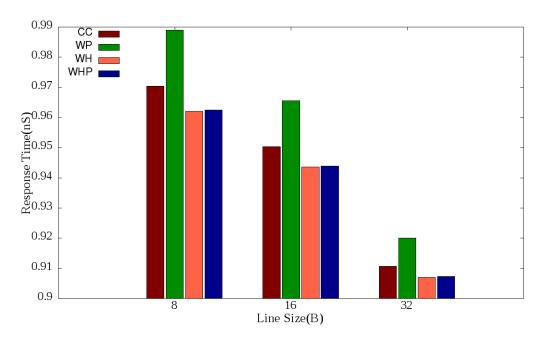

| 3.17 | Response time for a 4 way, 8KB cache with varying line Size $% \left( {{{\rm{A}}_{{\rm{B}}}} \right)$ . | 70 |

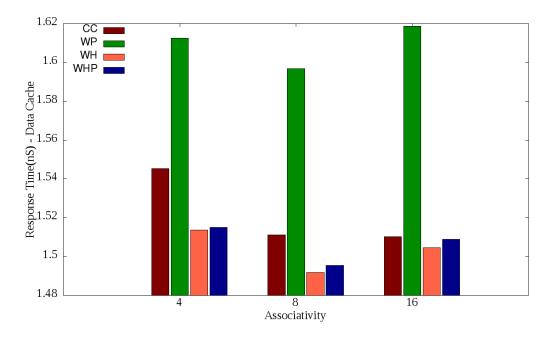

| 3.18 | Response time for a 16B, 8KB Data Cache with varying asso-                                              |    |

|      | ciativity                                                                                               | 71 |

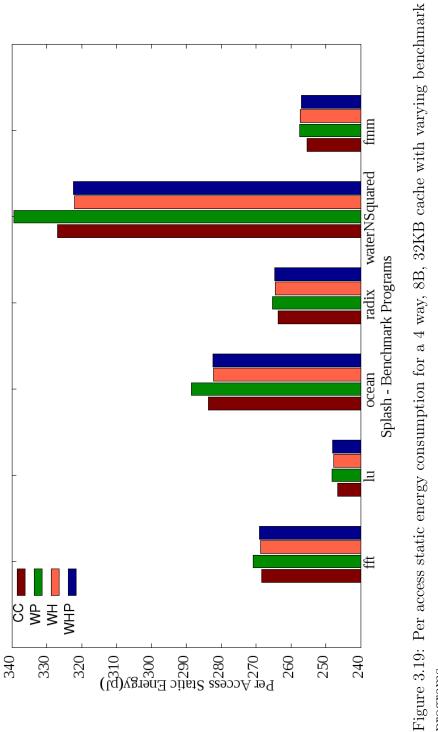

| 3.19 | Per access static energy consumption for a 4 way, 8B, 32KB $$                                           |    |

|      | cache with varying benchmark programs                                                                   | 72 |

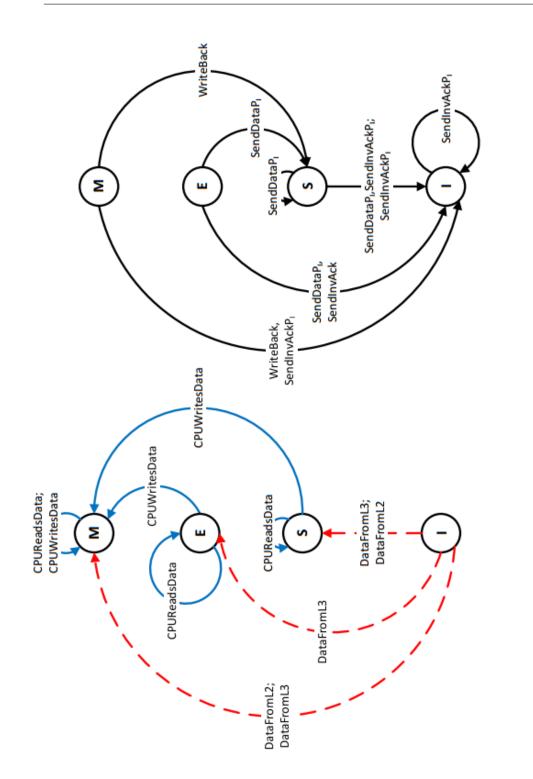

| 4.1  | MESI Access and Snoop State Transitions                                                                 | 77 |

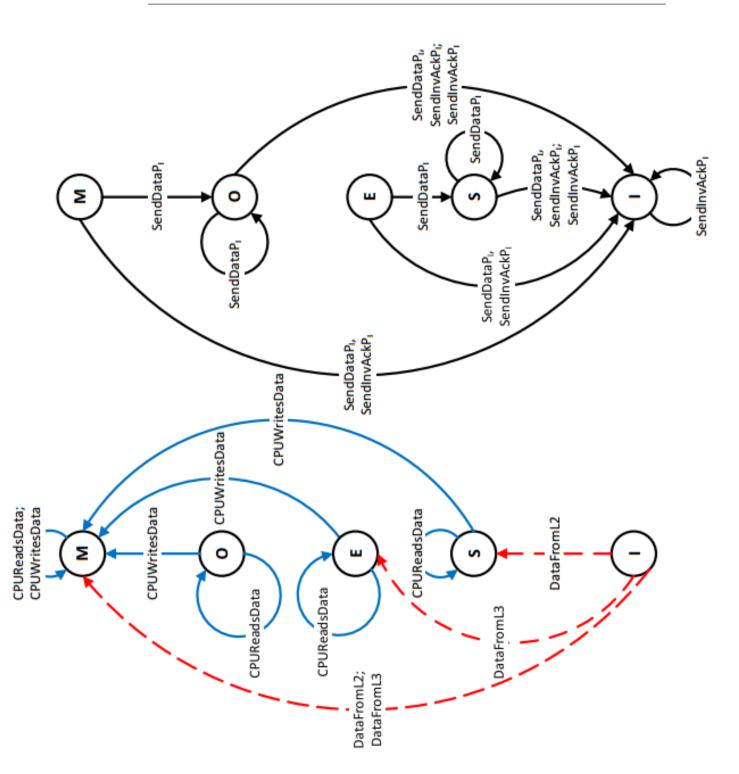

| 4.2  | MOESI Access and Snoop State Transitions                                                                | 79 |

| 4.3  | MESIF Access and Snoop State Transitions $\ . \ . \ . \ .$ .                                            | 80 |

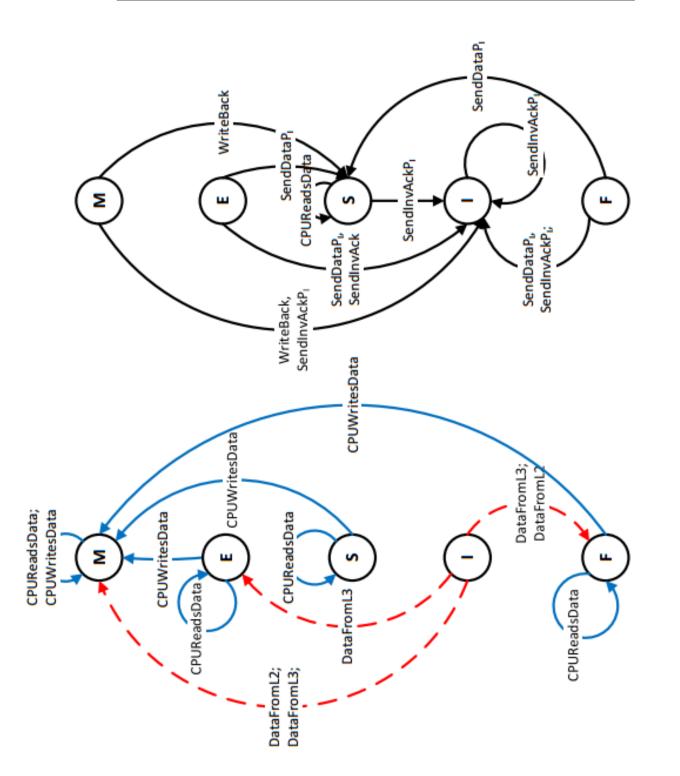

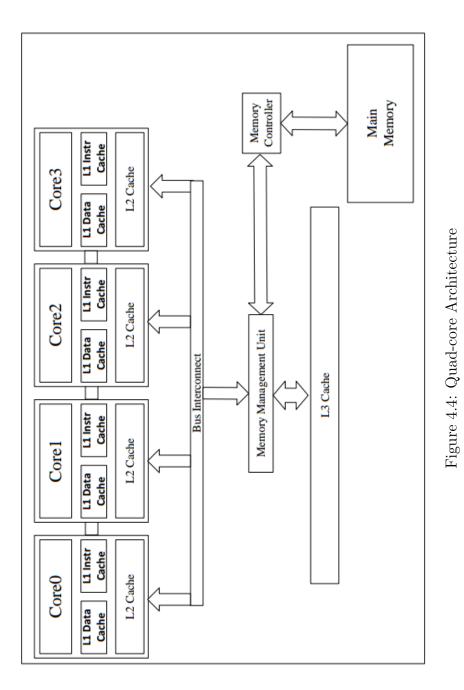

| 4.4  | Quad-core Architecture                                                                                  | 82 |

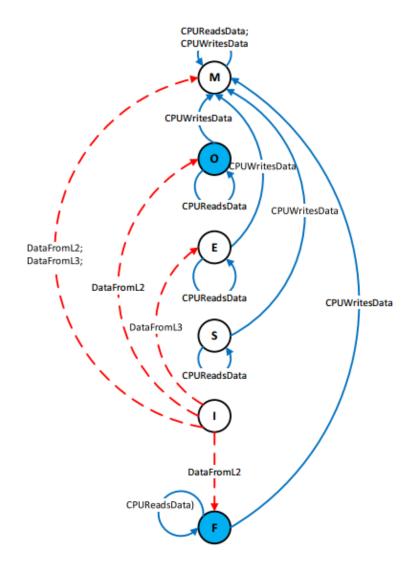

| 4.5  | MOESIF cache access                                                                                     | 83 |

| 4.6  | MOESIF cache snoop                                                                                      | 84 |

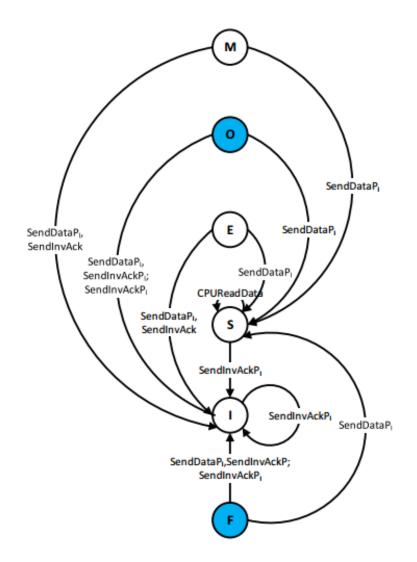

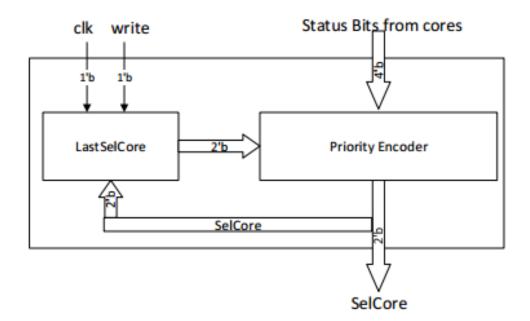

| 4.7  | Design of random generator used for Quad-core Architecture .                                            | 85 |

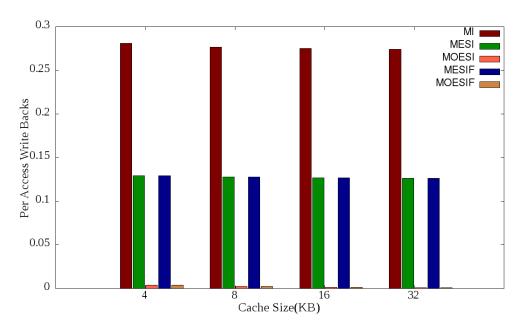

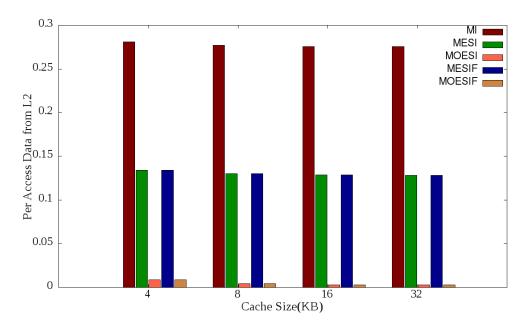

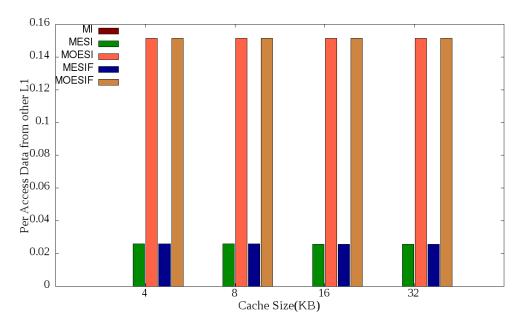

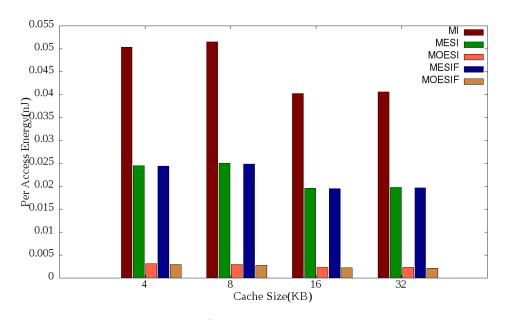

| Per access hit rate for varying cache sizes with 32B line size            |                            |

|---------------------------------------------------------------------------|----------------------------|

| and associativity as 4 way                                                | 93                         |

| Per access write backs for varying cache sizes with 32B line              |                            |

| size and associativity as 4 way                                           | 94                         |

| Per access data from L2 for varying cache sizes with 32B line $$          |                            |

| size and associativity as 4 way                                           | 94                         |

| Per access data from other L1 for varying cache sizes with $32\mathrm{B}$ |                            |

| line size and associativity as 4 way                                      | 95                         |

| Per access energy for varying cache sizes with 32B line size and          |                            |

| associativity as 4 way                                                    | 96                         |

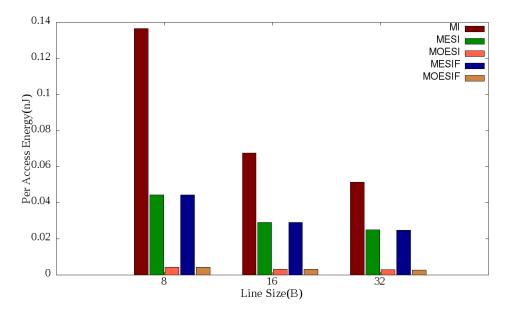

| Per access energy for varying cache line sizes with 8KB cache             |                            |

| size and associativity as 4 way                                           | 96                         |

| Per access energy for varying number of cores with 8KB cache,             |                            |

| 16B line size and associativity as 4 way                                  | 97                         |

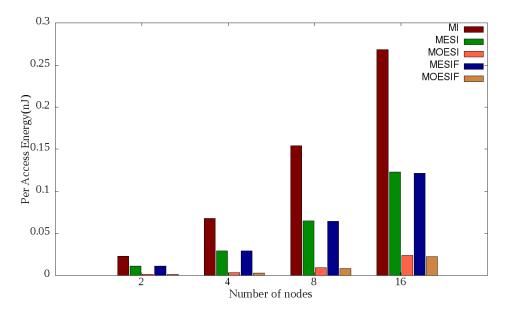

| Per access time for varying cache sizes with 32B line size and            |                            |

| associativity as 4 way                                                    | 98                         |

| Per access time for varying cache line sizes with 8KB cache               |                            |

| size and associativity as 4 way                                           | 99                         |

| Per access time for varying number of cores with 8KB cache,               |                            |

| 16B line size and associativity as 4 way                                  | 99                         |

| Deterministic TLB Architecture                                            | 103                        |

|                                                                           |                            |

|                                                                           |                            |

| and 32 TLB entries                                                        | 110                        |

|                                                                           | and associativity as 4 way |

| 5.3  | Miss rate performance of DTLB and ASID-TLB with respect                                                                    |

|------|----------------------------------------------------------------------------------------------------------------------------|

|      | to conventional TLB for varying preemptions with $4$ KB page                                                               |

|      | size and 32 TLB entries                                                                                                    |

| 5.4  | Miss rate performance of DTLB and ASID-TLB with respect to                                                                 |

|      | conventional TLB for varying TLB entries with 16 preemptions                                                               |

|      | and 4KB page size                                                                                                          |

| 5.5  | Per access dynamic energy with respect to conventional TLB                                                                 |

|      | saving for varying page size with 16 preemptions and 32 TLB $$                                                             |

|      | entries                                                                                                                    |

| 5.6  | Per access dynamic energy with respect to conventional TLB                                                                 |

|      | saving for varying preemptions with 4KB page size and $32$                                                                 |

|      | TLB entries $\ldots \ldots 115$ |

| 5.7  | Per access dynamic energy with respect to conventional TLB                                                                 |

|      | saving for varying TLB entries with 16 preemptions and $4\text{KB}$                                                        |

|      | page size                                                                                                                  |

| 5.8  | Per access dynamic energy for varying Splash benchmark pro-                                                                |

|      | grams                                                                                                                      |

| 5.9  | Per access time saving with respect to conventional TLB for                                                                |

|      | varying page size with 16 preemptions and 32 TLB entries $$ 117 $$                                                         |

| 5.10 | Per access time saving with respect to conventional TLB for                                                                |

|      | varying preemptions with 4KB page size and 32 TLB entries $% 100$ . 118 $$                                                 |

| 5.11 | Effective access time of 32 entry, 64<br>bits TLB for varying Splash $$                                                    |

|      | benchmarks                                                                                                                 |

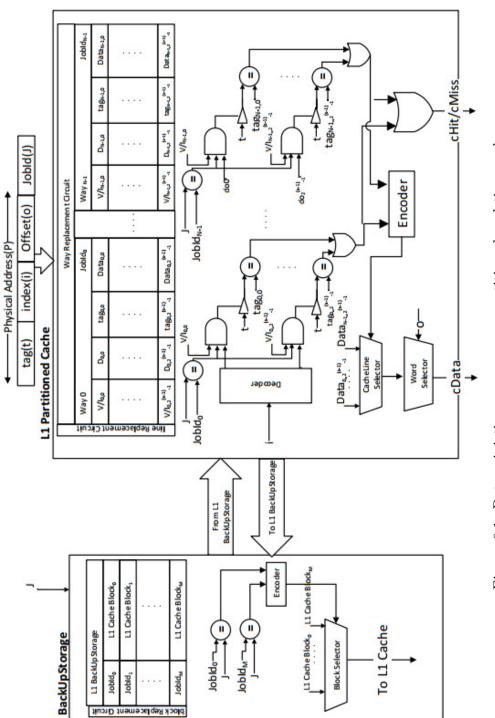

| 6.1  | Deterministic process aware partitioned real-time cache 124                                                                |

| 6.2  | Miss rate of CC and DEARCache by varying number of pre-                                                                    |

|      | emptions                                                                                                                   |

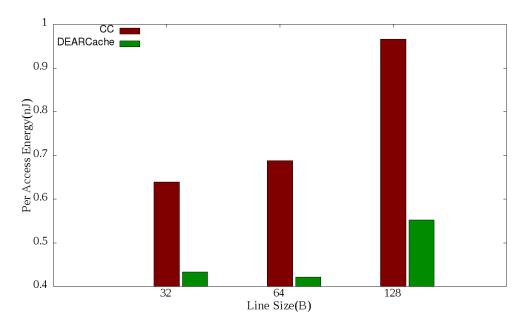

| 6.3  | Per access energy for varying preemption with 8KB cache size,                                              |

|------|------------------------------------------------------------------------------------------------------------|

|      | 32B line size and associativity as 4 way                                                                   |

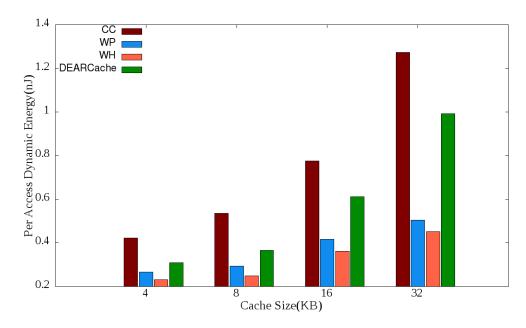

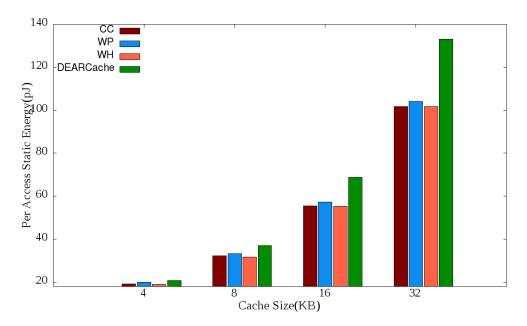

| 6.4  | Per access energy for varying cache size with 10 preemptions,                                              |

|      | 32B line size and associativity as 4 way                                                                   |

| 6.5  | Per access energy for varying line size with 10 preemptions,                                               |

|      | 8KB cache and associativity as 4 way                                                                       |

| 6.6  | Per access energy for varying associativity with 10 preemptions,                                           |

|      | 8KB cache and 32B line size $\ldots$                                                                       |

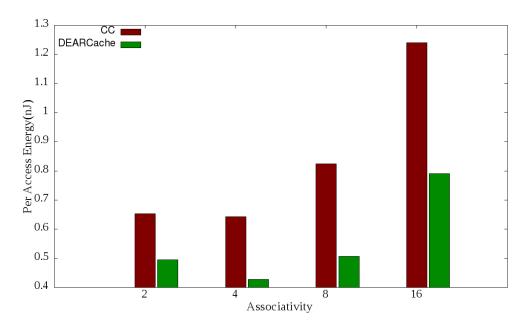

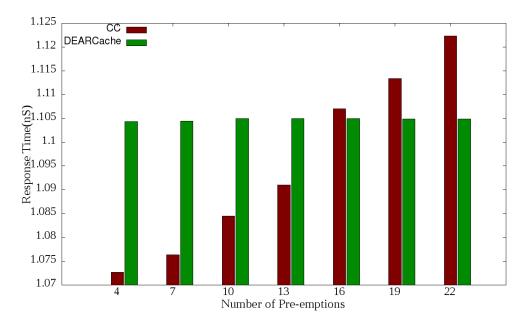

| 6.7  | response time for varying preemption with $8{\rm KB}$ cache size, $32{\rm B}$                              |

|      | line size and associativity as 4 way $\hdots$                                                              |

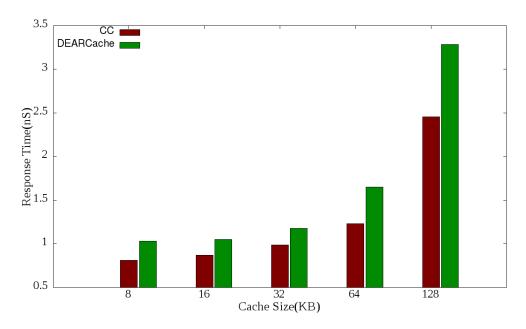

| 6.8  | response time for varying cache size with 10 preemptions, $32B$                                            |

|      | line size and associativity as 4 way $\hdots$                                                              |

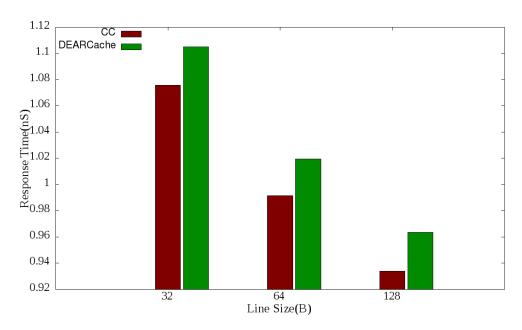

| 6.9  | response time for varying line size with 10 preemptions, $8 \text{KB}$                                     |

|      | cache and associativity as 4 way                                                                           |

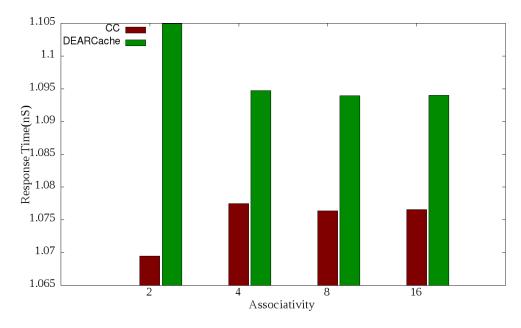

| 6.10 | response time for varying associativity with 10 preemptions,                                               |

|      | 8KB cache and 32B line size $\ldots$                                                                       |

| 6.11 | Per access dynamic energy for varying line size with 10 pre-                                               |

|      | emptions, 8KB cache size and associativity as 4 way 135                                                    |

| 6.12 | Per access Static energy for varying line size with 10 preemp-                                             |

|      | tions, 8KB cache size and associativity as 4 way                                                           |

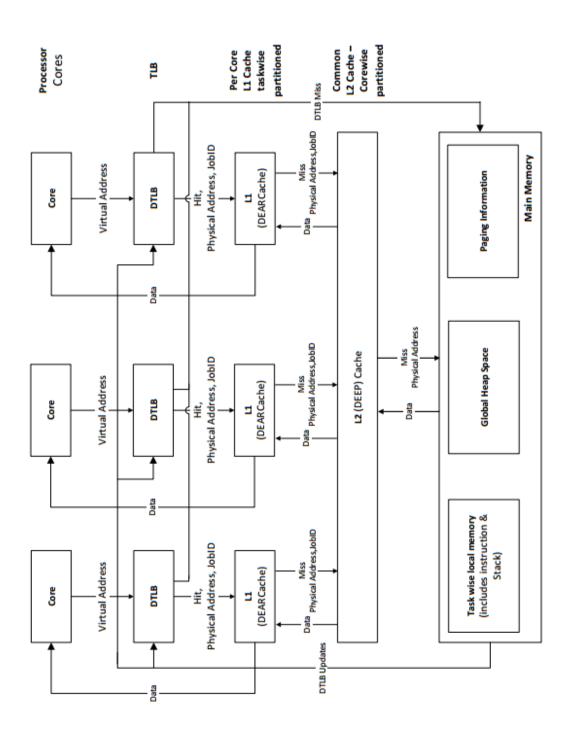

| 7.1  | DREAM Memory Subsystem                                                                                     |

| 7.2  | Deterministic Energy Efficient Process aware<br>(DEEP) Cache $% = 1.0121111111111111111111111111111111111$ |

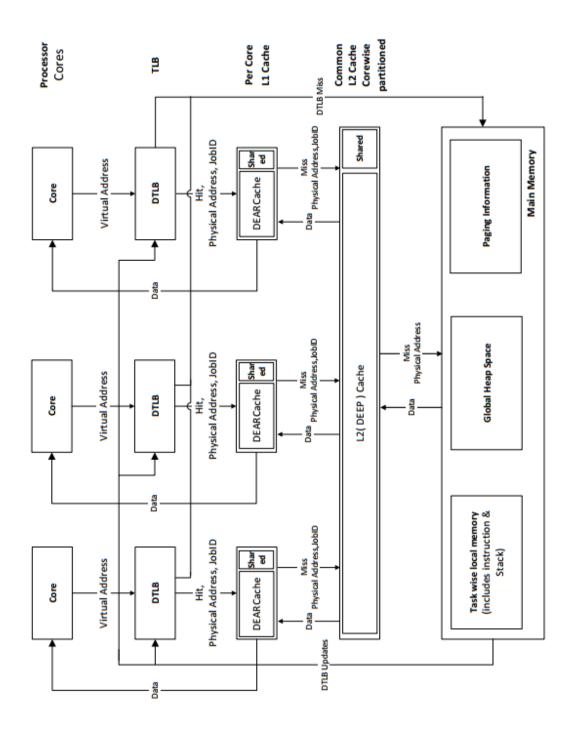

| 7.3  | DREAM Memory Subsystem with shared way $\hdots$                                                            |

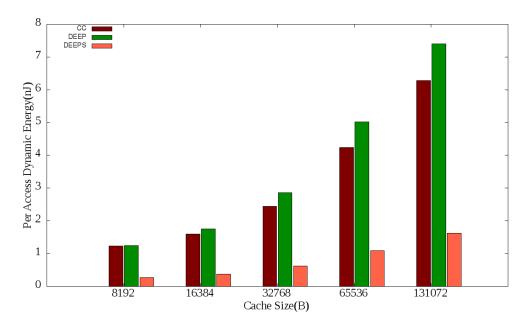

| 7.4  | Per access dynamic energy for a 4 way, 32B, 8KB cache with                                                 |

|      | varying preemptions                                                                                        |

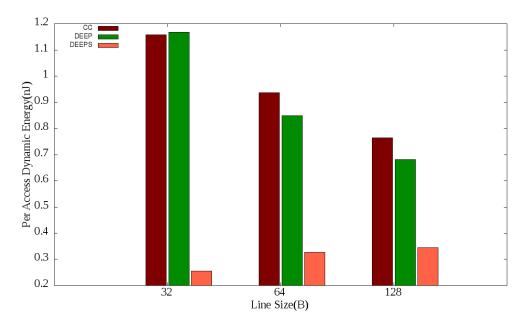

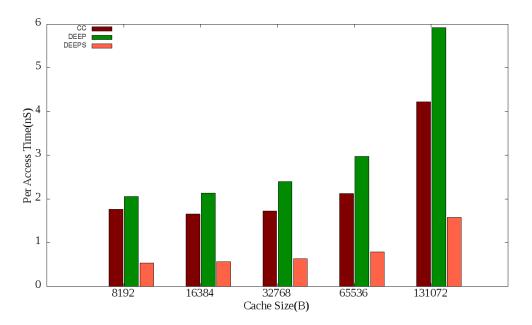

| 7.5  | Per access dynamic energy for a 4 way, 32B line size with                                                                                                  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | varying cache size [#preemptions = 10] $\dots \dots \dots$ |

| 7.6  | Per access dynamic energy for a 4 way, 8KB cache with varying                                                                                              |

|      | line size [#preemptions = 10] $\dots \dots \dots$          |

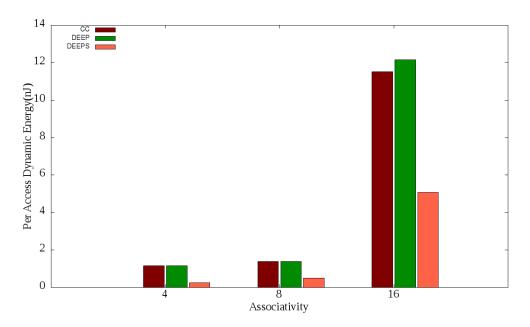

| 7.7  | Per access dynamic energy for a 32B, 8KB cache with varying                                                                                                |

|      | associativity [#preemptions = $10$ ]                                                                                                                       |

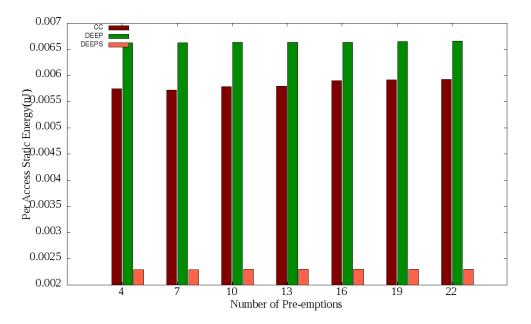

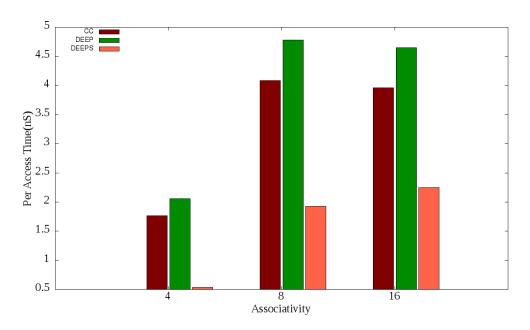

| 7.8  | Per access static energy for a 4 way, 32B, 8KB cache with                                                                                                  |

|      | varying preemptions                                                                                                                                        |

| 7.9  | Per access static energy for a 4 way, 32B line size with varying                                                                                           |

|      | cache size [#preemptions = 10] $\dots \dots \dots$         |

| 7.10 | Per access static energy for a 4 way, 8KB cache with varying                                                                                               |

|      | line size [#preemptions = 10] $\dots \dots \dots$          |

| 7.11 | Per access static energy for a 32B, 8KB cache with varying                                                                                                 |

|      | associativity [#preemptions = 10] $\dots \dots \dots$      |

| 7.12 | Per access time for a 4 way, 32B, 8KB cache with varying                                                                                                   |

|      | preemptions                                                                                                                                                |

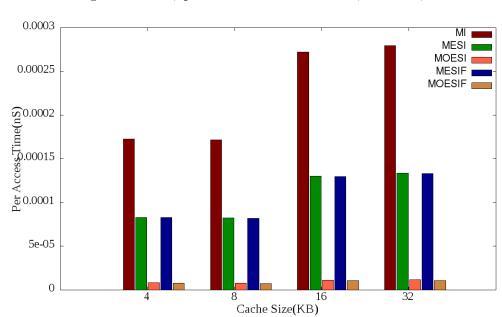

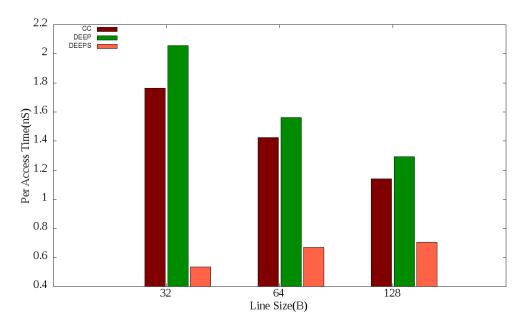

| 7.13 | Per access time for a 4 way, 32B line size with varying cache                                                                                              |

|      | size [#preemptions = 10] $\dots \dots \dots$               |

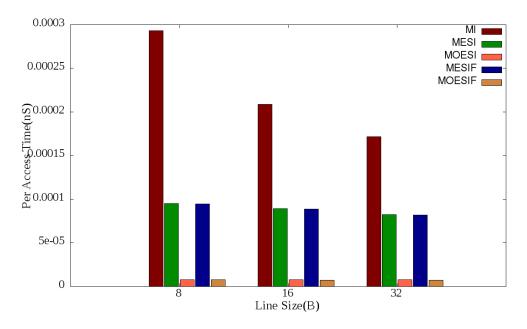

| 7.14 | Per access time for a 4 way, 8KB cache with varying line size                                                                                              |

|      | $[\# preemptions = 10] \dots \dots$                  |

| 7.15 | Per access time for a 32B, 8KB cache with varying associativity $% A^{2}$                                                                                  |

|      | $[\# preemptions = 10] \dots \dots$                  |

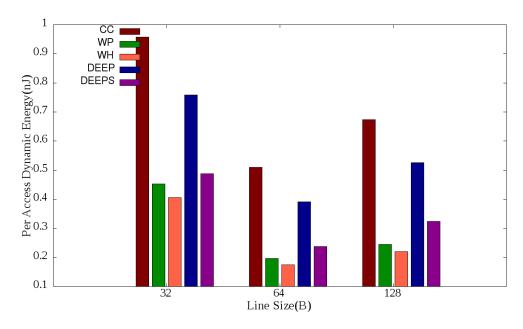

| 7.16 | Per access dynamic energy for varying line size with 10 pre-                                                                                               |

|      | emptions, 8KB cache size and associativity as 4 way 155                                                                                                    |

| 7.17 | Per access Static energy for varying line size with 10 preemp-                                                                                             |

|      | tions, 8KB cache size and associativity as 4 way $\hdots$                                                                                                  |

| 7.18 | Per access dynamic energy for a $64 \text{KB}$ L2 cache with varying                                                             |

|------|----------------------------------------------------------------------------------------------------------------------------------|

|      | L1 cache size $\ldots \ldots 158$            |

| 7.19 | Per access dynamic energy for a 8KB L1 cache with varying                                                                        |

|      | L2 cache size $\ldots \ldots 159$            |

| 7.20 | Per access static energy for a 64KB L2 cache with varying L1 $$                                                                  |

|      | cache size $\ldots \ldots 160$ |

| 7.21 | Per access static energy for a 8KB L1 cache with varying L2 $$                                                                   |

|      | cache size $\ldots \ldots 160$ |

| 7.22 | Per access time for a 64KB L2 cache with varying L1 cache size<br>161 $$                                                         |

| 7.23 | Per access time for a 8KB L1 cache with varying L2 cache size $161$                                                              |

# List of Tables

| 2.1 | Comparison of Replacement Strategies                            | 17  |

|-----|-----------------------------------------------------------------|-----|

| 2.2 | Cache Coherence States and Descriptions                         | 25  |

| 3.1 | SESC Components for Energy and Power Modeling of Cache .        | 41  |

| 3.2 | WHP variables used                                              | 51  |

| 3.3 | SESC Components for Time Modeling of Cache                      | 53  |

| 4.1 | Read, Write and Snoop operations in MOESIF Protocol $\ . \ .$ . | 81  |

| 4.2 | Energy and time modeling for cache operations                   | 89  |

| 5.1 | TLB Components for Energy and Time Modeling                     | 106 |

| 5.2 | Task Set Execution Schedule Format                              | 109 |

## List of Abbreviations

ASID-TLB Address Space Identifier based Translation Lookaside Buffer

${\bf CC}\,$  Conventional Cache

**DEARCache** Deterministic Energy efficient process Aware Real-time Cache

**DEEP** Deterministic Energy Efficient Process aware

**DREAM** Deterministic REAl-time Memory system

**DREAMS** Deterministic REAl-time Memory system with Shared way

**DTLB** Deterministic Translation Lookaside Buffer Buffer

FIFO First In First Out

LFU Least Frequently Used

LFUDA Least Frequently Used Dynamic Aging

LRU Least Recently Used

$\mathbf{MC}$  Multi-core

**MESI** Modified Exclusive Shared Invalid

**MESIF** Modified Exclusive Shared Invalid Forward

**MI** Modified Invalid

**MOESI** Modified Owned Exclusive Shared Invalid

**MOESIF** Modified Owned Exclusive Shared Invalid Forward

- MOSI Modified Owned Shared Invalid

- MRU Most Recently Used

- ${\bf MSB}\,$  Most Significant Bit

- ${\bf MSI}\,$  Modified Shared Invalid

- $\mathbf{PCB}$  Process Control Block

- **PLRU** Pseudo Least Recently Used

- RAND RANDom

- ${\bf RT}\,$  Response Time

- **SA** Set Associative

- ${\bf SESC}$  Super EScalar Simulator

- **TLB** Translation Lookaside Buffer

- $\mathbf{WCET}$  Worst Case Execution Time

- WH Way Halting Cache

- **WHP** Way Halted Prediction

- ${\bf WP}\,$  Way Predicting Cache

# Chapter 1

# Introduction

## 1.1 Background

Technology advancement has helped in increasing the processing speed for almost all the architecture components. Processors speed increases at higher rate than memory speed. Speed mismatch between these components is one of the major performance bottlenecks in modern processors which upto a limit is alleviated by using hierarchical arrangement of cache memories. Memory subsystems improve system performance by taking advantage of locality of reference - both temporal and spatial. Translation lookaside buffer (TLB) helps in converting logical address into physical address and is accessed at least once per instruction cycle. Hence, the TLB and cache plays a major role in determining system performance.

Irrespective of the processor in use, energy efficiency is one of the major design considerations of the modern day processor design. Shrinking size of transistors because of the advancement in fabrication technology increases the transistor density on chip. This improves processing power of the system at the cost of energy consumption. Narrowing of channel width in transistors result in reduced switching current and increased leakage current. This leads to reduction in dynamic energy at the cost of increased static energy. The Dynamic energy consumption of a CMOS circuit is given as :

$$E_{dynamic} = A * V^2 * f * C \tag{1.1}$$

where A, V, f and C are cache activity factor, operating voltage, operating frequency and effective load capacitance respectively. The Static energy consumption of a CMOS circuit is as :

$$E_{static} = V * I_{leak} * N * K_{design} \tag{1.2}$$

where  $I_{leak}$ , N and  $K_{design}$  are the leakage current, number of transistors in the circuit and design dependent parameters respectively. Dynamic energy can be reduced by reducing the voltage or frequency of operation or by reducing the activity factor. Static energy can be reduced by reducing total number of transistors or by shutting down some part of the system.

Memory subsystem consumes major portion of the on-chip energy. This forces the designers to come up with memory subsystem design with least possible energy consumption without much performance degradation.

System performance can be improved by increasing operating frequency of the system. However, increase in operating frequency leads to increase in energy consumption which in turn leads to increase in heat dissipation thus leakage current. One of the possible solution to this problem is to go for Multicore(MC) systems [1]. A shared memory MC system has more than one core where L1 and L2 caches are local to the core. The L3 cache and main memory are shared across all the cores. This results in possibility of having multiple copies of data in different locations. Cores access data from local caches as the data transfer is much faster from/to it in comparison with shared memory. It is possible that the cached data is modified in one of the cores and these modifications are not reflected in other cores, leading to data inconsistency among cores. Thus, maintaining data consistency becomes a major challenge in MC systems. Energy efficient and performance centric protocols are required to maintain data consistently in MC systems.

Deadline misses in hard real-time embedded system results in catastrophic failure. In hard real-time embedded systems, along with energy efficiency, deterministic tighter upper bound on the Worst Case Execution Time (WCET) of the task is also required. Deterministic tighter upper bound on WCET can only be ensured by making the entire process of accessing memory subsystem deterministic. This helps in improving offline and online analysis to incorporate more real-time tasks without deadline misses. One of the major components which make the system non-deterministic is memory. The unpredictability of memory subsystem is mainly because of the global replacement policy where the memory entries can be replaced by other tasks. Global replacement results in increase in memory misses on preemption. The memory access model can be made deterministic by providing a hard upper bound on the number of misses in TLB, all levels of caches and main memory.

### 1.2 Motivation

The cache memory access time is calculated as equation 1.3.

Cache memory access time = Cache memory hit time

+ Miss rate \* Miss penalty

$$(1.3)$$

The cache performance can be optimised by reducing cache hit time, miss rate and miss penalty. The cache misses are categorised as compulsory, capacity, conflict and coherence misses [2]. Figures 1.1 and 1.2 show hit time and hit rate performance with varying cache size and associativity, while executing FFT - Splash benchmark program [3].

As shown in figures 1.1 and 1.2, the cache hit time and hit rate of the direct map cache is the least as compared to the same-sized associative cache organisations. This is because the requested data word is available in output bus before hit/miss decision. Though the hit time of direct-map cache is the least, its average access time is highest due to highest number of conflict misses.

The energy consumption - both static and dynamic - of a cache is proportional to hit energy, block transfer energy and hit rate. Dynamic energy consumption can be reduced by reducing switching activity in cache and static energy consumption can be reduced by shutting down unused part of the cache. Architects have to find the right cache configuration to reduce energy consumption without much performance degradation. Though direct-map cache offers least per access energy consumption and hardware complexity, most of the embedded architectures prefer set associative (SA) cache because of the moderate hit energy and the hit rate.

Hit Rate

91

90.5

8-way 16-way Fully Associative

93

92.5

92

Direct 2-way 4-way

93.5

94

128

64

ω

4

89

89.5

06

For a SA cache, an ideal cache hit scenario is, compare one tag and access one data and an ideal cache miss scenario is to find a miss without accessing tag array and data array. Various cache optimisation strategies like way prediction [4], way halting [5] are proposed to achieve these objectives.

The growing computational demands is satisfied by adding more processors/cores to the system [6]. A coherent view of memory is crucial for these systems. A coherent data in cache is maintained by using cache coherency protocols. Cache coherency circuit, coherency misses and data/signal transfers across the network contributes towards the energy consumption in MC systems. Various coherency protocols are available to maintain data coherency but there exist a requirement of reducing coherency related energy consumption further [7].

In real-time systems, apart from the correct result of computation, the time at which the result is produced is critical [8]. This is true specially when it is used for critical applications like vehicular, aeronautical, military and industrial. Deadline miss of some of these applications lead to system failure and catastrophic consequences. Ensuring deadlines of critical applications is one of the design goals of hard real-time systems. As most of these systems are battery powered, energy efficiency is equally a design consideration along with deadline. Though cache memories are used widely to bridge the speed mismatch between processor and memory, they make the system non-deterministic. This is due to inter-task conflicts during execution. The preempted job's cache lines might get replaced by the cache lines of currently running job. When the preempted job resumes back its execution, many of its cache lines may not be present which increases its execution time. This may result in deadline misses, especially for high priority tasks with memory operations. Design of energy efficient and performance centric hard real-time system requires a tighter upper bound on WCET. To provide tighter upper bound on WCET, memory subsystem needs to be designed with tighter upper bound on misses.

#### **1.3** Problem Statement

This thesis addresses architecture level energy and performance optimisation of uniprocessor / unicore and MC system. With advancement in technology, the static energy consumption became an equally important component in total energy consumption along with the dynamic energy consumption. Static energy can be reduced by increasing cache hit rate and thus reducing operational time or by shutting down unused part of cache memory. Dynamic energy consumption can be reduced by reducing switching activities during cache access. Dynamic energy consumption is mainly due to charging and discharging of wordlines, bitlines, sense amplifiers, precharge circuits and decoders. To reduce dynamic energy consumption, this thesis aims at reducing switching activities of cache memory. This thesis also ensures deterministic tighter upper bound on memory access time in hard real-time systems. Detailed objective of the thesis are as follows:

#### Objective 1: Design of energy efficient unicore cache

The objective is to design an energy efficient cache for unicore system with reduced response time. The optimal cache hit energy can be achieved by accessing a tag array and a data array. The ideal cache miss scenario is achieved by early detection of cache misses. Early detection of cache miss improves system performance. This objective is to achieve performance closer to ideal cache hit and cache miss scenarios. This objective is discussed in chapter 3 of this thesis.

## Objective 2: Design of energy efficient cache coherency protocol for MC systems

The objective is to improve the off-chip and on-chip bandwidth usage. This work aims at designing an energy efficient cache coherency protocol by reducing coherency misses, write backs to next level memory and responders to any request. This objective is discussed in chapter 4 of this thesis.

#### **Objective 3: Design of deterministic TLB**

The objective is to design a TLB which offers tighter upper bound on number of misses and thus achieves a deterministic TLB performance. Details of this objective is discussed in chapter 5.

#### **Objective 4: Design of deterministic L1 cache**

The objective is to provide tighter upper bound on WCET of L1 cache by redesigning L1 instruction and L1 data caches. Inter-task interference makes the system non-deterministic. This issue needs to be addressed to achieve tighter upper bound on cache misses. Deterministic L1 cache design is discussed in chapter 6.

#### **Objective 5: Design of deterministic memory subsystem**

The objective is to provide tighter upper bound on WCET of memory subsystem by redesigning L2 cache and combining it with redesigned TLB and L1 cache. The determinitsic memory subsystem is discussed in chapter 7.

#### 1.4 Research Goals

This research focuses on optimising performance in terms of energy consumption and time for unicore and MC systems. Identified research goals are:

**Research Goal 1:** Identify time and energy impact of major components in memory subsystem.

**Research Goal 2:** Optimise unicore cache architecture with minimum response time and energy consumption.

**Research Goal 3:** Optimise MC cache architecture by minimising coherency misses and network traffic to improve performance in terms of time and energy.

**Research Goal 4:** Eliminate time uncertainty in TLB design to offer a tighter worst case upper bound on TLB accesses.

**Research Goal 5:** Eliminate time uncertainty in L1 private cache design and offer a tighter worst case upper bound on L1 accesses.

**Research Goal 6:** Eliminate time uncertainty in memory subsystem used for hard real-time systems by redesigning TLB, private L1, shared L2 and main memory to offer a tighter worst case upper bound.

## **1.5** Contributions

The major contributions of this thesis are as follows :

#### Contribution 1: Energy efficient unicore cache

Time and energy impact of major components in memory subsystem is identified. A part of this contribution is published in Paper A. An energy efficient cache for unicore system with reduced per access time is designed and implemented. This contribution is discussed in chapter 3 of this thesis and is published in Paper B.

# Contribution 2: Energy efficient cache coherency protocol for MC systems

Identification of various cache coherency related components contributing towards energy consumption is done. A part of this work is published in Paper C. The off-chip and on-chip bandwidth usage is improved. An energy efficient cache coherency protocol is designed and implemented. This work is published in Paper D and is discussed in chapter 4 of this thesis.

#### Contribution 3: Deterministic TLB

This work designed and evaluated a deterministic TLB which offers tighter upper bound on number of misses. This contribution is published in Paper E and is discussed in chapter 5 of this thesis.

#### Contribution 4: Deterministic L1 cache

The tighter upper bound on WCET of L1 cache is obtained by designing and evaluating deterministic L1 cache. This contribution forms chapter 6 of this thesis.

#### Contribution 5: Deterministic memory subsystem

The contribution provides tighter upper bound on WCET of memory subsystem. L2 cache is redesigned and combined with redesigned TLB and L1 cache. The determinities memory subsystem is discussed in chapter 7.

#### **1.6** Publications

**Paper A:** Geeta Patil, Parag Panda and Biju Raveendran, "A Survey on Replacement Strategies in Cache Memory for Embedded Systems," IEEE Conference on Distributed Computing, VLSI, Electrical Circuits and Robotics (DISCOVER), Mangalore, 2016, pp. 12-17.

Paper B: Geeta Patil, Neethu Bal Mallya and Biju Raveendran, "Way Halted Prediction Cache: An Energy Efficient Cache Architecture for Embedded Processors," 28<sup>th</sup> International Conference on VLSI Design, Bangalore, 2015, pp. 65-70

**Paper C:** Geeta Patil, Neethu Bal Mallya and Biju Raveendran, "Simulation based Performance Study of Cache Coherence Protocols," IEEE International Symposium on Nanoelectronic and Information Systems, Indore, 2015, pp. 125-130.

**Paper D:** Geeta Patil, Neethu Bal Mallya and Biju Raveendran, "MOESIF: A MC/MP Cache Coherence Protocol with Improved Bandwidth Utilization," International Journal of Embedded Systems (In Press).

**Paper E:** Geeta Patil, Kajal Varma and Biju Raveendran, "DTLB: Deterministic TLB for Tightly Bound Hard Real-Time Systems," 30<sup>th</sup> International Conference on VLSI Design and 16<sup>th</sup> International Conference on Embedded Systems, Hydrabad, 2017, pp. 207-212.

### 1.7 Thesis Outline

The outline of rest of the dissertation is as follows:

**Chapter 2 - Literature Survey** - This chapter presents a survey of stateof-the-art techniques used for energy optimisation in unicore and multicore cache architectures. The survey also includes various techniques used to obtain tighter upper bound on WCET of real-time tasks.

Chapter 3 - WHP : Way Halted Prediction Cache - This chapter presents an energy efficient set associative cache architecture named Way Halted Prediction (WHP) cache. WHP is designed to obtain reduced energy consumption and response time(RT).

Chapter 4 - MOESIF: Cache Coherency Protocol - This chapter concentrates on improving cache performance by redesigning coherency protocols.

This chapter proposes an energy efficient cache coherency protocol - Modified

Owned Exclusive Shared Invalid Forward - MOESIF. The redundant responses are concisely narrowed down in MOESIF protocol.

Chapter 5 - DTLB : Deterministic TLB for Real-time System - To have a tighter upper bound on WCET of real-time task, this chapter presents a TLB architecture - Deterministic Translation Lookaside Buffer (DTLB) which offers deterministic miss rate.

**Chapter 6 - DEARCACHE: Deterministic Energy Efficient Process Aware Real-time Cache** - To have a tighter upper bound on the WCET of real-time task, this chapter presents a Deterministic Energy efficient process Aware Real-time cache (DEARCACHE). Tighter upper bound on the WCET is achieved by eliminating L1 cache related intertask interference. It allocates at least statically identified minimum ways to each job.

**Chapter 7 DREAM: Deterministic Memory Subsystem** - This chapter presents an integrated design of deterministic memory named as Deterministic REAI-time Memory system (DREAM). DREAM achieves deterministic performance at TLB and L1 cache by incorporating DTLB and DEARCACHE along with deterministic energy efficient process aware L2 cache.

Chapter 8 Conclusion - This chapter concludes the thesis by summarising the results and future directions of the work.

# Chapter 2

# Literature Survey

# 2.1 Introduction

This chapter presents an exhaustive literature survey, analysis and comparison of the state-of-the-art techniques used for energy optimisation in uniprocessor/unicore and multicore memory subsystem architectures. The survey also includes various techniques used to obtain tighter upper bound on WCET of hard real-time tasks. The remainder of the chapter is organised as follows: Section 2.2 describes work done in energy efficient cache architecture. Related work in the field of cache coherency protocols and deterministic cache in real-time system are discussed in section 2.3 and 2.4 respectively.

# 2.2 Uniprocessor / Unicore energy optimisations

The most common approach to improve the cache hit rate with minimum energy consumption is to find the correct configuration of cache size, cache line size and associativity for the applications. Along with the configuration parameters, cache replacement strategy also plays a vital role in optimising cache performance [9]. It helps in reducing the number of cache misses and hence, the energy consumption and effective cache access time. An optimal cache replacement strategy identifies a cache line which will not be accessed in near future as victim cache line for replacement. This is impractical as the future references are unknown [10]. The performance of the cache replacement strategy mainly depends on how accurately system can predict the future reference pattern based on the past references. The selection of a programable replacement strategy for associative caches can have significant impact on the overall system performance. The choice of a replacement strategy is one of the most critical design issues.

Replacement strategies are classified based on time of the future reference (Optimal), time at which the cache line has arrived in cache (Arrival), time of the past reference (Recency), number of past references (Frequency), combination of recency and frequency (Recency + Frequency) or a random pick (Random).

Random (RAND) [11], First In First Out (FIFO) [9], Least Recently Used (LRU) [12], Most Recently Used (MRU) [12], Least Frequently Used (LFU) [13], [14], Least Frequently Used with Dynamic Ageing (LFUDA) [13], [15] and Pseudo-LRU (PLRU) [16] are some of the widely used hardware controlled cache replacement strategies . In order to analyse and compare hardware controlled cache replacement strategies, they are implemented on Xilinx ISE design 12.2. Memory traces of CPU2006 benchmark programs [17] were extracted by using Simplescalar [18] simulator. The memory traces obtained are given as input to the implemented cache replacement strategies.

|                    | Cache miss | Speedup        | Action on cache   | Action on cache   | Hardware                |

|--------------------|------------|----------------|-------------------|-------------------|-------------------------|

| rate w.r.t.<br>LRU | r.t.       |                | hit               | miss              | Components              |

| REFERENCE          | ENCE       | REFERENCE      | Update LRU        | Update LRU        | Nlog2N bits per set     |

|                    |            |                | counters          | counters          | and associated          |

|                    |            |                |                   |                   | circuitry               |

| 20%                | 20         | MIN            | NA                | NA                | NA                      |

| -22%               | 20         | Average $22\%$ | NONE              | Update a register | log2 N bits and         |

|                    |            | slower         |                   |                   | Pseudo Random           |

|                    |            |                |                   |                   | generator               |

| -20%               | 20         | Average $20\%$ | NONE              | Update FIFO       | N log2 N bits per set   |

|                    |            | slower         |                   | counter           | and associated          |

|                    |            |                |                   |                   | circuitry               |